WO2009118999A1 - 半導体装置ならびに多層配線基板および半導体装置の製造方法 - Google Patents

半導体装置ならびに多層配線基板および半導体装置の製造方法 Download PDFInfo

- Publication number

- WO2009118999A1 WO2009118999A1 PCT/JP2009/000719 JP2009000719W WO2009118999A1 WO 2009118999 A1 WO2009118999 A1 WO 2009118999A1 JP 2009000719 W JP2009000719 W JP 2009000719W WO 2009118999 A1 WO2009118999 A1 WO 2009118999A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- insulating layer

- wiring board

- semiconductor device

- multilayer wiring

- pads

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

- H05K1/113—Via provided in pad; Pad over filled via

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0271—Arrangements for reducing stress or warp in rigid printed circuit boards, e.g. caused by loads, vibrations or differences in thermal expansion

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4688—Composite multilayer circuits, i.e. comprising insulating layers having different properties

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05575—Plural external layers

- H01L2224/0558—Plural external layers being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05638—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05644—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/0601—Structure

- H01L2224/0603—Bonding areas having different sizes, e.g. different heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/13111—Tin [Sn] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13144—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/14—Structure, shape, material or disposition of the bump connectors prior to the connecting process of a plurality of bump connectors

- H01L2224/1401—Structure

- H01L2224/1403—Bump connectors having different sizes, e.g. different diameters, heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16237—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bonding area disposed in a recess of the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

- H01L2224/1701—Structure

- H01L2224/1703—Bump connectors having different sizes, e.g. different diameters, heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

- H01L2224/1705—Shape

- H01L2224/17051—Bump connectors having different shapes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/81009—Pre-treatment of the bump connector or the bonding area

- H01L2224/8101—Cleaning the bump connector, e.g. oxide removal step, desmearing

- H01L2224/81011—Chemical cleaning, e.g. etching, flux

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/81053—Bonding environment

- H01L2224/81054—Composition of the atmosphere

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8119—Arrangement of the bump connectors prior to mounting

- H01L2224/81191—Arrangement of the bump connectors prior to mounting wherein the bump connectors are disposed only on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8119—Arrangement of the bump connectors prior to mounting

- H01L2224/81193—Arrangement of the bump connectors prior to mounting wherein the bump connectors are disposed on both the semiconductor or solid-state body and another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/812—Applying energy for connecting

- H01L2224/8121—Applying energy for connecting using a reflow oven

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

- H01L2224/81815—Reflow soldering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/81909—Post-treatment of the bump connector or bonding area

- H01L2224/8191—Cleaning, e.g. oxide removal step, desmearing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8338—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/83385—Shape, e.g. interlocking features

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01022—Titanium [Ti]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01056—Barium [Ba]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0106—Neodymium [Nd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/15786—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2924/15787—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0104—Properties and characteristics in general

- H05K2201/0129—Thermoplastic polymer, e.g. auto-adhesive layer; Shaping of thermoplastic polymer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/06—Thermal details

- H05K2201/068—Thermal details wherein the coefficient of thermal expansion is important

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09009—Substrate related

- H05K2201/09036—Recesses or grooves in insulating substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09372—Pads and lands

- H05K2201/094—Array of pads or lands differing from one another, e.g. in size, pitch or thickness; Using different connections on the pads

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09372—Pads and lands

- H05K2201/09436—Pads or lands on permanent coating which covers the other conductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09709—Staggered pads, lands or terminals; Parallel conductors in different planes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10674—Flip chip

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/06—Lamination

- H05K2203/063—Lamination of preperforated insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49155—Manufacturing circuit on or in base

Definitions

- the present invention relates to a semiconductor device in which a semiconductor chip is mounted on a multilayer wiring board, a multilayer wiring board, and a method for manufacturing the semiconductor device.

- the semiconductor device is configured by wire bonding mounting, TAB (Tape Automated Automated Bonding) mounting, or flip chip mounting.

- TAB Pe Automated Automated Bonding

- flip-chip mounting technology is a technology that enables the highest density mounting of semiconductor devices by reducing the size of the semiconductor device. Many are used.

- a semiconductor chip is mounted on a multilayer wiring board. Specifically, electrode terminals, actually electrode pads, are formed in advance on the back surface of the semiconductor chip, and connection pads corresponding to the electrode pads are provided on the multilayer wiring board. Then, the electrode pad and the connection pad are connected using a conductive bump (see, for example, JP-A-2001-135749).

- the conductive bump is formed of a conductive metal such as gold or solder, and solder is often used from the viewpoint of ease of mounting and stress relaxation at the joint. This solder bump can be formed by a method such as a ball mounting method, a paste printing method, or a plating method.

- connection pads In flip chip mounting, a large number of electrical connections can be made in a small area for surface mounting. However, as the semiconductor device becomes smaller and the number of pins increases, the pitch of connection pads becomes narrower. As the pitch of the connection pads becomes narrower, the height of the solder bumps tends to decrease. In the future, it is considered that semiconductor devices having such a connection form with such a narrow pitch (particularly, a connection pad pitch of 200 ⁇ m or less) will become mainstream.

- solder bumps As a general method for forming solder bumps, the paste printing method has been widely adopted from the viewpoint of productivity and cost. However, in this method, when the pitch of the solder bumps becomes narrow, a short circuit between adjacent bumps occurs during solder printing, and the yield may be extremely reduced. Therefore, for forming narrow pitch solder bumps, a plating method in which solder bumps are formed by electrolytic plating, or a ball mounting method in which solder bumps are formed by mounting solder balls on a pad and reflowing are desirable methods. ing.

- a build-up board manufactured by a build-up method is often used from the viewpoint of high density, light weight, thinning, and low cost of wiring.

- This build-up board is a connection for electrical connection with a semiconductor chip by alternately forming circuit patterns and insulating layers on a glass epoxy board (core board) with glass cloth impregnated with epoxy resin. A pad is formed on the surface.

- a thermosetting insulating resin is used for forming the insulating layer.

- the coefficient of thermal expansion differs greatly between the semiconductor chip and the multilayer wiring board. For this reason, when the semiconductor chip and the multilayer wiring board are subjected to a large temperature change during or after the flip chip mounting, the stress concentrates on the solder bumps that connect the semiconductor chip and the multilayer wiring board, and the solder bumps or the vicinity thereof There was a risk that a crack would occur and a connection failure would occur.

- Patent Document 2 describes that a paste printing method or a paste dispensing method is preferable for realizing this, but these methods are unsuitable for forming narrow pitch solder bumps as described above. Therefore, it is desired to suppress the occurrence of cracks while keeping the volume of the solder bumps at the same level.

- the present invention has been made in view of the above circumstances, and a semiconductor device capable of suppressing the occurrence of cracks while maintaining the same volume of bumps even when the connection pad pitch is 200 ⁇ m or less, and the same It is an object of the present invention to provide a method for manufacturing a multilayer wiring board and a semiconductor device used in the manufacturing process.

- the present invention comprises a semiconductor chip having an electrode pad on the back surface and a multilayer wiring board having a connection pad facing the electrode pad on the surface, the electrode pad having And a first electrode pad including an electrode pad disposed close to each corner of the back surface of the semiconductor chip, and a second electrode pad other than the first electrode pad, wherein the connection pad includes the first electrode.

- the multi-layered wiring board supports the first connection pads.

- the first connection pads are connected to the pads via bumps, and the second connection pads are connected to the second electrode pads via bumps.

- the first insulating region is made of a thermoplastic resin, and the second insulating region is a thermosetting resin. Consists of That, to provide a semiconductor device.

- the first electrode pad is an electrode pad located relatively far from the center of the back surface of the semiconductor chip among the electrode pads, and the second electrode pad is on the center side of the back surface of the semiconductor chip. It is an electrode pad constituting a group of electrode pads.

- the present invention includes a semiconductor chip having an electrode pad on the back surface and a multilayer wiring board having a connection pad facing the electrode pad on the front surface, the electrode pad having the semiconductor pad A first electrode pad including an electrode pad disposed in proximity to each corner of the back surface of the chip and a second electrode pad other than the first electrode pad, wherein the connection pad includes the first electrode pad and a bump And a second connection pad connected to the second electrode pad of the electrode pad via a bump, and the multilayer wiring board includes the first connection pad.

- the present invention is a multilayer wiring board on which a semiconductor chip is mounted on a surface, and a plurality of pads arranged in a rectangular region on the surface, and pads located at at least four corners among the plurality of pads

- a first insulating layer that constitutes a first insulating region that supports the second insulating layer; and a second insulating layer that constitutes a second insulating region that supports pads other than the pads supported by the first insulating layer among the plurality of pads;

- the first insulating layer is made of a thermoplastic resin

- the second insulating layer is made of a thermosetting resin

- the first insulating layer is made of the second insulating layer.

- Provided is a multilayer wiring board laminated thereon.

- the present invention includes a step of forming a circuit pattern on a core substrate including a glass cloth, a step of forming a lower insulating layer with a thermosetting resin on the core substrate on which the circuit pattern is formed, Forming a plurality of pads and circuit patterns electrically connected to the circuit pattern on the core substrate on the lower insulating layer; and on the lower insulating layer on which the circuit pattern is formed, Forming an upper insulating layer with a thermoplastic resin so as to surround the plurality of pads, and forming a plurality of pads electrically connected to the circuit pattern on the lower insulating layer on the upper insulating layer; A method for manufacturing a multilayer wiring board.

- the present invention also provides a multilayer wiring board manufactured by the method for manufacturing a multilayer wiring board and a semiconductor chip provided with electrode pads on the back surface, and solder balls are mounted on the electrode pads for reflow. Solder bumps are formed, and the semiconductor chip is mounted on the surface of the multilayer wiring board so that the connection pads and the electrode pads face each other with the solder bumps sandwiched therebetween, and the reflow is performed in that state.

- a method for manufacturing a semiconductor device wherein the semiconductor chip is mounted on a surface of a multilayer wiring board.

- the first connection pad connected to the bump at a position where stress due to temperature change is particularly concentrated is supported by the first insulating region made of thermoplastic resin. For this reason, when the ambient temperature becomes high, the first insulating region is softened. Such softening of the first insulating region can relieve stress applied to the bump connected to the first connection pad. Therefore, even if bumps having substantially the same volume are used, the generation of cracks can be effectively suppressed.

- the second connection pads connected to the remaining bumps are supported by a second insulating region made of a thermosetting resin. For this reason, even when the ambient environment temperature becomes high, the second connection pad is kept in a fixed position. Therefore, the above-described effect can be obtained while maintaining high bonding strength between the multilayer wiring board and the semiconductor chip.

- the second connection in which the first insulating layer supporting the first connection pad connected to the bump at a position where stress due to temperature change is particularly concentrated is connected to the bump at another position. It is laminated

- FIG. 2 is a plan view of the semiconductor device shown in FIG. 1. It is explanatory drawing explaining the manufacturing method of a multilayer wiring board. It is a top view of the film for 1st insulating layers. It is sectional drawing of a multilayer wiring board. It is sectional drawing of the semiconductor chip which formed the bump in the electrode pad. It is explanatory drawing explaining the manufacturing method of a semiconductor device. It is explanatory drawing explaining the manufacturing method of a semiconductor device. It is sectional drawing of the semiconductor device of a modification. It is a top view of the semiconductor device of another modification. It is sectional drawing of the semiconductor device of a comparative example.

- a semiconductor chip 1 As shown in FIGS. 1 and 2, a semiconductor chip 1 according to an embodiment of the present invention includes a multilayer wiring board 4 and a semiconductor chip 2 mounted on a surface 4 a of the multilayer wiring board 4. .

- the semiconductor chip 2 and an underfill 8 described later are indicated by a two-dot chain line.

- the semiconductor chip 2 has a flat rectangular plate shape.

- a plurality of (for example, 1000 to 2000, for the sake of simplification, 25 are drawn) electrode pads 3 are provided. These electrode pads 3 may be arranged in a matrix or in a staggered manner.

- Each electrode pad 3 has, for example, a circular shape, and is configured such that a UBM (Under Bump Metal) 32 is laminated on an aluminum pad 31.

- UBM Under Bump Metal

- an electroless nickel plating layer having a thickness of 10 ⁇ m may be formed on the aluminum pad 31, and a gold plating layer having a thickness of 0.1 ⁇ m may be further formed thereon.

- the region other than the electrode pad 3 on the back surface 2a of the semiconductor chip 2 is covered with an insulating protective film 21 made of, for example, polyimide resin.

- the electrode pad 3 is composed of a first electrode pad 3a arranged close to each corner (four vertices) of the back surface 2a of the semiconductor chip 2 and other second electrode pads 3b. Yes.

- the size of the first electrode pad 3a is preferably set larger than the size of the second electrode pad 3b.

- the diameter of the first electrode pad 3a may be 140 ⁇ m

- the diameter of the second electrode pad 3b may be 100 ⁇ m.

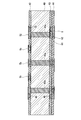

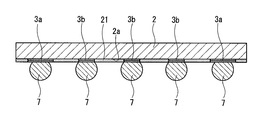

- the multilayer wiring board 4 is an interposer configured by alternately laminating circuit patterns and insulating layers on both the front and back surfaces of the core substrate 40.

- a plurality of connection pads 5 respectively facing the electrode pads 3 are provided on the front surface 4a of the multilayer wiring board 4, and a plurality of external connection pads respectively electrically connected to the connection pads 5 are provided on the back surface 4b. 6 is provided.

- a circuit pattern 51, a second insulating layer (lower insulating layer) 42, a circuit pattern 52, and a first insulating layer (upper insulating layer) 41 are laminated in this order on the surface of the core substrate 40.

- a circuit pattern 61, a third insulating layer 43, a circuit pattern 62, and a fourth insulating layer 44 are laminated in this order.

- the first insulating layer 41 has an opening 41 a that exposes the second insulating layer 42 and faces the back surface 2 a of the semiconductor chip 2.

- the connection pad 5 is supported by the first insulating layer 41 and the second insulating layer 42, and the external connection pad 6 is supported by the fourth insulating layer 44.

- the first insulating layer 41 constitutes a first insulating region that supports a first connection pad 5a described later

- the second insulating layer 42 is a second insulating region that supports a second connection pad 5b described later. Is configured.

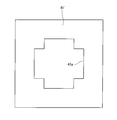

- the opening 41a is formed in a cross shape. That is, the first insulating layer 41 is formed so as to face only the four corners of the back surface 2a of the semiconductor chip 2 through the opening 41a, and the second insulating layer 42 covers the four corners of the back surface 2a of the semiconductor chip 2 through the opening 41a. Opposite the part.

- Each of the insulating layers 41 to 44 includes the pad 5 (or 6) and the circuit patterns 51 and 52 (or 62) or the circuit patterns 51 and 52 (or 61 and 62) through the insulating layers 41 to 44.

- a via hole 48 is formed for conducting each other.

- the core substrate 40 is provided with a through electrode 40 a that electrically connects the circuit patterns 51 and 61 through the core substrate 40.

- the multilayer wiring board 4 has a front side solder resist 45 that covers the first insulating layer 41 and the second insulating layer 42, and a back side solder resist 46 that covers the fourth insulating layer 44.

- the front surface 4 a of the multilayer wiring board 4 is configured by the outer surface of the front side solder resist 45

- the back surface 4 b of the multilayer wiring substrate 4 is configured by the outer surface of the back side solder resist 46.

- the core substrate 40 a ceramic substrate or an organic material substrate can be used. However, from the viewpoint of effective relaxation of stress applied to the joint portion at the time of cost and thermal stress loading, it is possible to use glass cloth. It is preferable to use a glass epoxy substrate impregnated with a thermosetting resin.

- the thickness of the core substrate 40 is 0.4 mm, for example.

- an epoxy resin is suitable, but other resins can also be used.

- one thermosetting resin having high heat resistance such as bismaleimide triazine resin or thermosetting polyphenylene ether may be used, or a mixture of two or more of these may be used.

- connection pads 5 are connected to the electrode pads 3 of the semiconductor chip 2 via solder bumps 7, respectively.

- the solder bumps 7 have substantially the same volume (for example, 5.0 ⁇ 10 ⁇ 4 mm 3 ).

- connection pad 5 includes a first connection pad 5a connected to the first electrode pad 3a and a second connection pad 5b connected to the second electrode pad 3b.

- the first connection pad 5 a is supported by the first insulating layer 41

- the second connection pad 5 b is supported by the second insulating layer 42.

- the first connection pads 5a located at the four corners among the plurality of connection pads 5 arranged in the rectangular region on the surface 4a of the multilayer wiring board 4 are supported by the first insulating layer 41, and the remaining second The connection pad 5 b is supported by the second insulating layer 42.

- a height difference equal to the thickness of the first insulating layer 41 is formed between the first connection pad 5a and the second connection pad 5b, and the first connection pad 5a is connected to the second connection by the height difference. It is located closer to the semiconductor chip 2 than the pad 5b.

- the shape of the first connection pad 5a and the second connection pad 5b is not particularly limited, but may be, for example, a circular shape or a rectangular shape.

- the size of the first connection pad 5a is preferably larger than the size of the second connection pad 5b.

- the first connection pad 5a may have a circular shape with a diameter of 140 ⁇ m

- the second connection pad 5b may have a circular shape with a diameter of 100 ⁇ m.

- the first insulating layer 41 is preferably made of a thermoplastic resin.

- the thermoplastic resin constituting the first insulating layer 41 is not particularly limited, but from the viewpoint of the manufacturing method, adhesion, and workability of the multilayer wiring board, for example, polyphenylene ether (PPE), liquid crystal polymer (LCP) ), Polyetheretherketone (PEEK), polyetherimide (PEI), polyethersulfone (PES), thermoplastic polyimide (PI), etc. Can do.

- the thermoplastic resin constituting the first insulating layer 41 has a melting point of 280 ° C. or higher.

- a temperature for example, 260 ° C.

- the melting point of the solder bump 7 for example, 217 ° C. for a solder bump having a composition of 97.5 wt% tin and 2.5 wt% silver

- the thickness of the first insulating layer 41 is preferably 1.5 times or more the thickness of the circuit pattern 52 immediately below the first insulating layer 41 in the multilayer wiring board. Since the circuit pattern 52 is formed so as to be embedded in the first insulating layer 41, the circuit pattern cannot be formed above and below the first insulating layer 41 if the first insulating layer 41 is thinner than the circuit pattern 52. Further, if the thickness of the first insulating layer 41 is less than 1.5 times the thickness of the circuit pattern 52, the first insulating layer 41 may be processed by etching or the like when forming the circuit pattern, or by surface roughening when forming the insulating layer.

- the thickness of the first insulating layer 41 is preferably less than or equal to one half of the height of the solder bump 7 formed between the second electrode pad 3b and the second connection pad 5b.

- the thickness of the first insulating layer 41 exceeds one half of the height of the solder bump 7 formed between the second electrode pad 3b and the second connection pad 5b, the first connection pad 5a and the second connection are connected. This is because the height difference between the pads 5b becomes too large, and the solder bumps 7 connected to the first connection pads 5a are extremely crushed, which may reduce the connection reliability.

- the thickness of the first insulating layer 41 may be 5 to 50 ⁇ m.

- the second to fourth insulating layers 42 to 44 are preferably made of a thermosetting resin containing an inorganic filler.

- the inorganic filler is added in order to lower the thermal expansion coefficient and improve the elastic modulus while maintaining the insulating properties of the insulating layer, and its blending amount is, for example, 10 to 60% by volume.

- the inorganic filler include spherical silica having an average particle diameter of 5 ⁇ m. In addition to silica, spherical or crushed fillers made of alumina, aluminum hydroxide, barium titanate or the like may be used.

- thermosetting resin an epoxy resin is suitable, but other resins can be used.

- one thermosetting resin having high heat resistance such as bismaleimide triazine resin or thermosetting polyphenylene ether may be used, or a mixture of two or more of these may be used.

- the front side solder resist 45 is provided with openings 45a and 45b (see FIG. 2) for exposing the first connection pad 5a and the second connection pad 5b at positions corresponding to the first connection pad 5a and the second connection pad 5b. ing.

- the size of the opening 45a at the position corresponding to the first connection pad 5a is preferably set larger than the size of the opening 45b at the position corresponding to the second connection pad 5b.

- the size of the opening 45a may be 130 ⁇ m in diameter, and the size of the opening 45b may be 90 ⁇ m in diameter.

- the size of the opening 45a at the position corresponding to the first connection pad 5a may be determined according to the thickness of the first insulating layer 41 and the volume of the solder bump 7.

- the thickness of the front side solder resist layer 45 is, for example, 20 ⁇ m.

- a barrier metal layer 50 is laminated on the first connection pad 5a and the second connection pad 5b exposed through the openings 45a and 45b.

- an electroless nickel plating layer having a thickness of 10 ⁇ m is formed on the first connection pad 5a and the second connection pad 5b, and further a gold having a thickness of 0.1 ⁇ m is formed thereon.

- a plating layer may be formed.

- the first connection pad 5 a and the second connection pad 5 b are connected to the solder bump 7 via the barrier metal layer 50.

- An opening is also formed in the back side solder resist 46 at a position corresponding to the external connection pad 6, and a barrier metal layer 60 is formed in the opening.

- an underfill 8 is filled between the multilayer wiring board 4 and the semiconductor chip 2.

- a polyfunctional epoxy resin is often used from the viewpoint of heat resistance, and in particular, an insulating resin such as a bisphenol A novolac epoxy resin, a bisphenol F novolac epoxy resin, or a cresol novolac epoxy resin. Can be used.

- the solder bumps 7 positioned at the four corners that are most stressed when the semiconductor chip 2 and the multilayer wiring board 4 are connected via the solder bumps 7 are the first insulating layer made of thermoplastic resin.

- the first connection pads 5 a formed on the first connection pads 5 a are connected.

- the stress applied to the solder bumps 7 positioned at the four corners can be alleviated.

- solder bumps 7 are connected to the second connection pads 5b formed on the second insulating layer 42 having a high elastic modulus even during a thermal load, the semiconductor chip 2 and the multilayer wiring board 4 As a whole, the connection can be made rigid and strong. Furthermore, since the cross-sectional area of the solder bump 7 located at the four corners can be greatly expanded by the height difference between the first connection pad 5a and the second connection pad 5b, the stress applied to the solder bump 7 is further reduced. be able to. Therefore, even if the solder bumps 7 having substantially the same volume are used as in this embodiment, the generation of cracks can be effectively suppressed and the bonding strength between the semiconductor chip 2 and the multilayer wiring board 4 is high. A semiconductor device can be obtained.

- solder bumps 7 having substantially the same volume are used as in the present embodiment, the solder bumps 7 can be formed by the ball mounting method, so that even if the connection pad pitch is as narrow as 200 ⁇ m or less, solder is used. The bump 7 can be formed satisfactorily.

- FIG. 3 is a cross-sectional view showing a state before the first insulating layer 41 is formed.

- a metal foil having a thickness of 15 ⁇ m is bonded to both the front and back surfaces of the core substrate 40 by thermocompression bonding.

- a copper foil produced by electrolytic plating can be used.

- a carbon dioxide laser is used to process a through hole that penetrates the core substrate 40 together with the metal foil, and then the inside of the through hole is electroless copper plated.

- the through electrode 40a is formed by filling with electrolytic copper plating.

- the circuit patterns 51 and 61 are formed on the core substrate 40 by etching the metal foil.

- thermosetting resin containing an inorganic filler as described above is bonded to the surface of the core substrate 40 on which the circuit pattern 51 is formed by thermocompression bonding and cured, and the first Two insulating layers 42 are formed.

- the method for forming the second insulating layer 42 is not limited to this.

- an uncured liquid thermosetting resin containing an inorganic filler is applied by screen printing or spin coating, and then heated and cured. Also good.

- a bottomed via hole 48 that penetrates the second insulating layer 42 in the thickness direction and reaches the circuit pattern 51 therebelow is formed in the second insulating layer 42 using a carbon dioxide laser.

- the bottomed via hole 48 may be formed by using a laser processing apparatus such as a third harmonic Nd-YAG laser or a deep ultraviolet excimer laser having a wavelength shorter than 300 nm, in addition to the carbon dioxide gas laser.

- a photosensitive dry film resist is bonded to the surface of the formed copper plating film by a thermocompression press, and a glass mask on which a negative image of a desired conductor pattern is drawn is positioned thereon. Thereafter, exposure and development are performed to form an etching resist that exposes the copper plating film in portions other than the necessary conductor pattern.

- the portion of the copper plating film not covered with the etching resist was dissolved and removed by etching, and then the etching resist was peeled off to be electrically connected to the circuit pattern 51 on the second insulating layer 42.

- a second connection pad 5b and a circuit pattern 52 are formed.

- the third insulating layer 43, the circuit pattern 62 electrically connected to the circuit pattern 61, the fourth insulating layer 44, and the circuit pattern 62 are electrically connected to the back surface of the core substrate 40 in the same manner as described above. External connection pads 6 connected to are formed.

- the opening 41 a made of the thermoplastic resin as described above is formed to cover all portions other than the region where the second connection pad 5 b on the second insulating layer 42 is disposed.

- a film 41 ′ having a shape capable of being prepared is prepared.

- the opening 41a may be formed by cutting out the film with a carbon dioxide laser, for example.

- the first insulating layer 41 is formed so as to surround the second connection pad 5 b by thermocompression bonding after positioning the film 41 ′ on the second insulating layer 42.

- the formation of the first insulating layer 41 can be performed by applying a liquid thermoplastic resin onto the second insulating layer 42. However, considering the ease and cost of the multilayer wiring board manufacturing method, the film 41 ′ is formed. Is preferably used.

- the first connection pad 5 a is formed on the first insulating layer 41 by the same method as the method of forming the second connection pad 5 b on the second insulating layer 42.

- a solder resist resin made of a photosensitive epoxy resin is used on the first insulating layer 41 and the second insulating layer 42 by an exposure process. Then, a front-side solder resist 45 having openings 45a and 45b exposing the first connection pad 5a and the second connection pad 5b is formed. Since there is a step between the first insulating layer 41 and the second insulating layer 42 that form the foundation for forming the front side solder resist 45, when forming the front side solder resist 45, first, a portion on the second insulating layer 42 is formed. Is formed first, and then a portion on the first insulating layer 41 is formed.

- a back side solder resist 46 having an opening exposing the external connection pad 6 is formed on the fourth insulating layer 44. Since the back side has no step on the base, the back side solder resist 46 can be formed by a single process after the front side solder resist 45 is formed.

- the formation of these solder resists 45 and 46 is generally performed by using a photosensitive type solder resist material and patterning by an exposure process, but any method can be used as long as it can be processed into a desired shape. Also good. For example, processing may be performed using a laser processing apparatus such as a carbon dioxide laser, a third harmonic Nd-YAG laser, or a deep ultraviolet excimer laser having a wavelength shorter than 300 nm.

- barrier metal layers 50 and 60 are formed on portions of the first connection pad portion 5a, the second connection pad 5b, and the external connection pad 6 exposed from the openings of the solder resists 45 and 46, respectively.

- a multilayer wiring board 4 as shown in FIG. 5 can be manufactured.

- solder balls having a diameter of 100 ⁇ m are mounted at predetermined positions on the first electrode pad 3a and the second electrode pad 3b of the semiconductor chip 2, and reflow treatment is performed in a nitrogen gas atmosphere. By doing so, the solder bumps 7 are formed.

- flax 71 is attached to the solder bumps 7.

- the method of attaching the flux 71 to the solder bumps 7 is particularly effective when the flux 71 is spread over the entire surface of the solder bumps 7 and the flux 71 does not adhere to the insulating protective film 21 formed on the back surface 2a of the semiconductor chip 2. It doesn't matter.

- the solder bumps 7 formed on the semiconductor chip 2 are immersed in a flux 71 uniformly applied to a flat surface with a film thickness (for example, 50 ⁇ m) thinner than the height of the solder bumps 7.

- the flux 71 can be adhered.