KR20230135175A - 반도체 장치 및 발광 장치 - Google Patents

반도체 장치 및 발광 장치 Download PDFInfo

- Publication number

- KR20230135175A KR20230135175A KR1020237031364A KR20237031364A KR20230135175A KR 20230135175 A KR20230135175 A KR 20230135175A KR 1020237031364 A KR1020237031364 A KR 1020237031364A KR 20237031364 A KR20237031364 A KR 20237031364A KR 20230135175 A KR20230135175 A KR 20230135175A

- Authority

- KR

- South Korea

- Prior art keywords

- film

- oxide semiconductor

- insulating film

- transistor

- low

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 514

- 239000000758 substrate Substances 0.000 claims description 155

- 239000000463 material Substances 0.000 claims description 27

- 239000012535 impurity Substances 0.000 abstract description 106

- 230000006870 function Effects 0.000 abstract description 97

- 229910052739 hydrogen Inorganic materials 0.000 abstract description 66

- 239000001257 hydrogen Substances 0.000 abstract description 60

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 abstract description 41

- 239000010408 film Substances 0.000 description 1519

- 229910052760 oxygen Inorganic materials 0.000 description 159

- 239000001301 oxygen Substances 0.000 description 159

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 155

- 238000000034 method Methods 0.000 description 106

- 239000011701 zinc Substances 0.000 description 98

- 239000007789 gas Substances 0.000 description 87

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 78

- 239000010410 layer Substances 0.000 description 73

- 239000013078 crystal Substances 0.000 description 71

- 125000004429 atom Chemical group 0.000 description 62

- 238000010438 heat treatment Methods 0.000 description 59

- 239000004973 liquid crystal related substance Substances 0.000 description 50

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 44

- 229910052751 metal Inorganic materials 0.000 description 43

- 239000004020 conductor Substances 0.000 description 42

- 230000007547 defect Effects 0.000 description 42

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 41

- 229910052782 aluminium Inorganic materials 0.000 description 41

- 229910052710 silicon Inorganic materials 0.000 description 41

- 239000010703 silicon Substances 0.000 description 41

- 238000004519 manufacturing process Methods 0.000 description 31

- 238000005401 electroluminescence Methods 0.000 description 30

- 238000004544 sputter deposition Methods 0.000 description 27

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 25

- 150000004767 nitrides Chemical class 0.000 description 25

- 239000008188 pellet Substances 0.000 description 23

- 229910052757 nitrogen Inorganic materials 0.000 description 22

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 22

- 239000000523 sample Substances 0.000 description 21

- 229910052581 Si3N4 Inorganic materials 0.000 description 19

- 150000002431 hydrogen Chemical class 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 229910052721 tungsten Inorganic materials 0.000 description 19

- 239000010937 tungsten Substances 0.000 description 19

- 229910052779 Neodymium Inorganic materials 0.000 description 18

- 229910052727 yttrium Inorganic materials 0.000 description 18

- 229910052726 zirconium Inorganic materials 0.000 description 18

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 17

- 229910052684 Cerium Inorganic materials 0.000 description 17

- 238000010586 diagram Methods 0.000 description 17

- 229910052746 lanthanum Inorganic materials 0.000 description 17

- 229910052749 magnesium Inorganic materials 0.000 description 17

- 239000011777 magnesium Substances 0.000 description 17

- 230000003071 parasitic effect Effects 0.000 description 17

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 17

- 230000005669 field effect Effects 0.000 description 16

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 16

- 239000000203 mixture Substances 0.000 description 16

- 230000003287 optical effect Effects 0.000 description 16

- -1 polyethylene terephthalate Polymers 0.000 description 16

- 239000002184 metal Substances 0.000 description 15

- 229910052756 noble gas Inorganic materials 0.000 description 15

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 14

- 229910045601 alloy Inorganic materials 0.000 description 14

- 239000000956 alloy Substances 0.000 description 14

- 238000004364 calculation method Methods 0.000 description 14

- 239000010949 copper Substances 0.000 description 14

- 230000008569 process Effects 0.000 description 14

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 12

- 239000012298 atmosphere Substances 0.000 description 12

- 229910052802 copper Inorganic materials 0.000 description 12

- 230000005684 electric field Effects 0.000 description 12

- 239000010936 titanium Substances 0.000 description 12

- 230000004888 barrier function Effects 0.000 description 11

- 238000012545 processing Methods 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 11

- 239000002356 single layer Substances 0.000 description 11

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 10

- 229910052799 carbon Inorganic materials 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 238000000151 deposition Methods 0.000 description 10

- 239000011521 glass Substances 0.000 description 10

- 239000011347 resin Substances 0.000 description 10

- 229920005989 resin Polymers 0.000 description 10

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 10

- 229910052814 silicon oxide Inorganic materials 0.000 description 10

- 238000003860 storage Methods 0.000 description 10

- 229910052719 titanium Inorganic materials 0.000 description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 9

- 229910052786 argon Inorganic materials 0.000 description 9

- 238000000231 atomic layer deposition Methods 0.000 description 9

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 9

- 230000007704 transition Effects 0.000 description 9

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- 230000008021 deposition Effects 0.000 description 8

- 229910052733 gallium Inorganic materials 0.000 description 8

- 229910052735 hafnium Inorganic materials 0.000 description 8

- 239000011261 inert gas Substances 0.000 description 8

- 150000002500 ions Chemical class 0.000 description 8

- 229910044991 metal oxide Inorganic materials 0.000 description 8

- 150000004706 metal oxides Chemical class 0.000 description 8

- 229910052750 molybdenum Inorganic materials 0.000 description 8

- 239000002159 nanocrystal Substances 0.000 description 8

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 8

- 229910052715 tantalum Inorganic materials 0.000 description 8

- 239000010409 thin film Substances 0.000 description 8

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 7

- 230000004913 activation Effects 0.000 description 7

- 229910021529 ammonia Inorganic materials 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 229910052804 chromium Inorganic materials 0.000 description 7

- 239000011651 chromium Substances 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 7

- 238000005530 etching Methods 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 238000004549 pulsed laser deposition Methods 0.000 description 7

- 229910000077 silane Inorganic materials 0.000 description 7

- 229910052709 silver Inorganic materials 0.000 description 7

- 239000004332 silver Substances 0.000 description 7

- 238000012546 transfer Methods 0.000 description 7

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 7

- 229910001868 water Inorganic materials 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 6

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 6

- 230000001133 acceleration Effects 0.000 description 6

- 238000004458 analytical method Methods 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 238000000576 coating method Methods 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 6

- 229910052748 manganese Inorganic materials 0.000 description 6

- 239000011572 manganese Substances 0.000 description 6

- 238000005259 measurement Methods 0.000 description 6

- 239000011733 molybdenum Substances 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 238000007639 printing Methods 0.000 description 6

- 238000007789 sealing Methods 0.000 description 6

- 238000005477 sputtering target Methods 0.000 description 6

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 6

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 5

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 5

- 229910052783 alkali metal Inorganic materials 0.000 description 5

- 150000001340 alkali metals Chemical class 0.000 description 5

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 5

- 150000001342 alkaline earth metals Chemical class 0.000 description 5

- 229910052801 chlorine Inorganic materials 0.000 description 5

- 239000000460 chlorine Substances 0.000 description 5

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 5

- 238000002003 electron diffraction Methods 0.000 description 5

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 5

- 229910001195 gallium oxide Inorganic materials 0.000 description 5

- 229910000449 hafnium oxide Inorganic materials 0.000 description 5

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- 229910052742 iron Inorganic materials 0.000 description 5

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 229910052725 zinc Inorganic materials 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 4

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 4

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- 239000000853 adhesive Substances 0.000 description 4

- 230000001070 adhesive effect Effects 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 210000004027 cell Anatomy 0.000 description 4

- 239000011248 coating agent Substances 0.000 description 4

- 239000003086 colorant Substances 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 230000001186 cumulative effect Effects 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- 238000002524 electron diffraction data Methods 0.000 description 4

- 239000000284 extract Substances 0.000 description 4

- 229910052731 fluorine Inorganic materials 0.000 description 4

- 239000011737 fluorine Substances 0.000 description 4

- 229910052738 indium Inorganic materials 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 230000001590 oxidative effect Effects 0.000 description 4

- 239000000123 paper Substances 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 230000027756 respiratory electron transport chain Effects 0.000 description 4

- 238000012916 structural analysis Methods 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 3

- 238000003917 TEM image Methods 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 238000002441 X-ray diffraction Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- QKIUAMUSENSFQQ-UHFFFAOYSA-N dimethylazanide Chemical compound C[N-]C QKIUAMUSENSFQQ-UHFFFAOYSA-N 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- 229960001730 nitrous oxide Drugs 0.000 description 3

- 235000013842 nitrous oxide Nutrition 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 239000007800 oxidant agent Substances 0.000 description 3

- 125000004430 oxygen atom Chemical group O* 0.000 description 3

- NFHFRUOZVGFOOS-UHFFFAOYSA-N palladium;triphenylphosphane Chemical compound [Pd].C1=CC=CC=C1P(C=1C=CC=CC=1)C1=CC=CC=C1.C1=CC=CC=C1P(C=1C=CC=CC=1)C1=CC=CC=C1.C1=CC=CC=C1P(C=1C=CC=CC=1)C1=CC=CC=C1.C1=CC=CC=C1P(C=1C=CC=CC=1)C1=CC=CC=C1 NFHFRUOZVGFOOS-UHFFFAOYSA-N 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 230000000737 periodic effect Effects 0.000 description 3

- 229920000728 polyester Polymers 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 2

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical compound CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 230000004075 alteration Effects 0.000 description 2

- 239000004760 aramid Substances 0.000 description 2

- 229920003235 aromatic polyamide Polymers 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 229910002092 carbon dioxide Inorganic materials 0.000 description 2

- 239000001569 carbon dioxide Substances 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000001362 electron spin resonance spectrum Methods 0.000 description 2

- 238000010893 electron trap Methods 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 238000000295 emission spectrum Methods 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 239000011888 foil Substances 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 2

- 150000002835 noble gases Chemical class 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 230000001151 other effect Effects 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 230000001960 triggered effect Effects 0.000 description 2

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 2

- 230000008016 vaporization Effects 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- CHEANNSDVJOIBS-MHZLTWQESA-N (3s)-3-cyclopropyl-3-[3-[[3-(5,5-dimethylcyclopenten-1-yl)-4-(2-fluoro-5-methoxyphenyl)phenyl]methoxy]phenyl]propanoic acid Chemical compound COC1=CC=C(F)C(C=2C(=CC(COC=3C=C(C=CC=3)[C@@H](CC(O)=O)C3CC3)=CC=2)C=2C(CCC=2)(C)C)=C1 CHEANNSDVJOIBS-MHZLTWQESA-N 0.000 description 1

- 210000002925 A-like Anatomy 0.000 description 1

- QTBSBXVTEAMEQO-UHFFFAOYSA-M Acetate Chemical compound CC([O-])=O QTBSBXVTEAMEQO-UHFFFAOYSA-M 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- 244000025254 Cannabis sativa Species 0.000 description 1

- 235000012766 Cannabis sativa ssp. sativa var. sativa Nutrition 0.000 description 1

- 235000012765 Cannabis sativa ssp. sativa var. spontanea Nutrition 0.000 description 1

- 229920000298 Cellophane Polymers 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- 229920000742 Cotton Polymers 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 229910005555 GaZnO Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 229910001252 Pd alloy Inorganic materials 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 229920000297 Rayon Polymers 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 239000007983 Tris buffer Substances 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 229910007541 Zn O Inorganic materials 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 239000002313 adhesive film Substances 0.000 description 1

- 239000003463 adsorbent Substances 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 239000011449 brick Substances 0.000 description 1

- 230000005587 bubbling Effects 0.000 description 1

- 235000009120 camo Nutrition 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 235000005607 chanvre indien Nutrition 0.000 description 1

- 238000005234 chemical deposition Methods 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 150000001879 copper Chemical class 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- ZYLGGWPMIDHSEZ-UHFFFAOYSA-N dimethylazanide;hafnium(4+) Chemical compound [Hf+4].C[N-]C.C[N-]C.C[N-]C.C[N-]C ZYLGGWPMIDHSEZ-UHFFFAOYSA-N 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000010494 dissociation reaction Methods 0.000 description 1

- 230000005593 dissociations Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 229920001971 elastomer Polymers 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000005421 electrostatic potential Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- LIWAQLJGPBVORC-UHFFFAOYSA-N ethylmethylamine Chemical compound CCNC LIWAQLJGPBVORC-UHFFFAOYSA-N 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 239000002657 fibrous material Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 239000011487 hemp Substances 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-O hydridodioxygen(1+) Chemical compound [OH+]=O MYMOFIZGZYHOMD-UHFFFAOYSA-O 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- 239000010985 leather Substances 0.000 description 1

- 230000005291 magnetic effect Effects 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000002071 nanotube Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 229920002620 polyvinyl fluoride Polymers 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 150000003254 radicals Chemical class 0.000 description 1

- 239000002964 rayon Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 239000005361 soda-lime glass Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 239000004575 stone Substances 0.000 description 1

- 238000009662 stress testing Methods 0.000 description 1

- 229920002994 synthetic fiber Polymers 0.000 description 1

- 239000012209 synthetic fiber Substances 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- LXEXBJXDGVGRAR-UHFFFAOYSA-N trichloro(trichlorosilyl)silane Chemical compound Cl[Si](Cl)(Cl)[Si](Cl)(Cl)Cl LXEXBJXDGVGRAR-UHFFFAOYSA-N 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

- MCULRUJILOGHCJ-UHFFFAOYSA-N triisobutylaluminium Chemical compound CC(C)C[Al](CC(C)C)CC(C)C MCULRUJILOGHCJ-UHFFFAOYSA-N 0.000 description 1

- VEDJZFSRVVQBIL-UHFFFAOYSA-N trisilane Chemical compound [SiH3][SiH2][SiH3] VEDJZFSRVVQBIL-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 239000002023 wood Substances 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1251—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs comprising TFTs having a different architecture, e.g. top- and bottom gate TFTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1237—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a different composition, shape, layout or thickness of the gate insulator in different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

Abstract

온 전류가 큰 산화물 반도체를 포함하는 반도체 장치를 제공한다. 반도체 장치는, 구동 회로부에 제공된 제1 트랜지스터와, 화소부에 제공된 제2 트랜지스터를 포함하고, 제1 트랜지스터와 제2 트랜지스터는 상이한 구조를 갖는다. 또한, 제1 트랜지스터와 제2 트랜지스터는 탑-게이트 구조를 갖는 트랜지스터들이다. 트랜지스터들 각각의 산화물 반도체 막에 있어서, 불순물 원소는 게이트 전극과 겹치지 않는 영역에 함유된다. 산화물 반도체 막 중에서 불순물 원소를 함유하는 영역은 저 저항 영역으로서 기능한다. 또한, 산화물 반도체 막 중에서 불순물 원소를 함유하는 영역은, 수소를 함유하는 막과 접한다. 구동 회로부에 제공된 제1 트랜지스터는, 산화물 반도체 막을 개재하여 2개의 게이트 전극을 포함한다.

Description

본 발명의 일 실시예는, 산화물 반도체 막을 포함하는 반도체 장치 및 상기 반도체 장치를 포함하는 표시 장치에 관한 것이다.

본 발명의 일 실시예는, 상기 기술 분야에 제한되지 않는다는 점에 주목해야 한다. 본 명세서 등에 개시된 본 발명의 일 실시예의 기술 분야는, 물건, 방법 또는, 제조 방법에 관한 것이다. 또한, 본 발명은, 공정(process), 기계(machine), 제조물(manufacture), 또는 조성물(composition of matter)에 관한 것이다. 특히, 본 발명의 일 실시예는, 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 기억 장치, 그 구동 방법 또는 그 제조 방법에 관한 것이다.

본 명세서 등에 있어서, 반도체 장치는, 일반적으로 반도체 특성을 이용함으로써 기능할 수 있는 장치를 의미한다. 트랜지스터 등의 반도체 소자, 반도체 회로, 연산 장치 및 기억 장치는, 각각 반도체 장치의 일 실시예이다. 촬상 장치, 표시 장치, 액정 표시 장치, 발광 장치, 전기 광학 장치, 발전 장치(박막 태양 전지, 유기 박막 태양 전지 등을 포함함) 및 전자 장치는, 각각 반도체 장치를 포함할 수 있다.

절연 표면을 갖는 기판 위에 형성된 반도체 박막을 사용하여 트랜지스터(박막 트랜지스터(TFT)라고도 지칭함)를 형성하는 기술이 주목을 받고 있다. 상기 트랜지스터는 집적 회로(IC) 또는 화상 표시 장치(표시 장치) 등의 광범위의 전자 장치에 사용된다. 실리콘으로 대표되는 반도체 재료가, 트랜지스터에 사용될 수 있는 반도체 박막의 재료로서 널리 알려져 있다. 다른 재료로서는, 산화물 반도체가 주목을 받고 있다.

예를 들어, 특허문헌 1은 산화물 반도체로서, In, Zn, Ga, Sn 등을 포함하는 비정질 산화물을 사용하여 트랜지스터를 제조하는 기술을 개시한다.

산화물 반도체 막을 포함하는 트랜지스터로서는, 역 스태거 트랜지스터(inverted staggered transistor)(보텀-게이트 구조를 갖는 트랜지스터라고도 지칭함), 평면 트랜지스터(planar transistor)(탑-게이트 구조를 갖는 트랜지스터라고도 지칭함) 등이 주어진다. 산화물 반도체 막을 포함하는 트랜지스터가 표시 장치에 사용되는 경우에, 평면 트랜지스터보다 역 스태거 트랜지스터가, 그 제조 공정이 비교적 간단하고 그 제조 비용이 낮게 유지될 수 있기 때문에, 더 자주 사용된다. 그러나, 표시 장치의 화면 대형화가 진행되거나, 표시 장치에 고해상도 화상이 제공되는 경우(예를 들어, 4k×2k 화소(수평 방향으로 3840 화소 및 수직 방향으로 2160 화소) 또는 8k×4k 화소(수평 방향으로 7680 화소 및 수직 방향으로 4320 화소)로 대표되는 고해상도 표시 장치인 경우), 역 스태거 트랜지스터의 게이트 전극과, 소스 및 드레인 전극들 사이에 존재하는 기생 용량에 의해 신호 지연 등이 증가하고, 따라서 표시 장치의 화질이 열화된다고 하는 문제가 있었다. 또한, 다른 문제로서, 역 스태거 트랜지스터의 점유 면적은, 평면 트랜지스터의 점유 면적보다 크다. 따라서, 산화물 반도체 막을 포함하는 평면 트랜지스터에 관련하여, 안정된 반도체 특성 및 높은 신뢰성을 갖는 구조를 지니며 간단한 제조 공정으로 형성되는 트랜지스터의 개발이 요망된다.

상기 문제들을 감안하여, 본 발명의 일 실시예는, 산화물 반도체를 포함하는 신규의 반도체 장치를 제공하는 것이고, 특히 산화물 반도체를 포함하는 평면형(planar type) 반도체 장치를 제공하는 것이다. 또한, 산화물 반도체를 포함하는 온 전류가 큰 반도체 장치를 제공하거나, 산화물 반도체를 포함하는 오프 전류가 작은 반도체 장치를 제공하거나, 산화물 반도체를 포함하는 점유 면적이 작은 반도체 장치를 제공하거나, 산화물 반도체를 포함하는 안정된 전기적 특성을 갖는 반도체 장치를 제공하거나, 산화물 반도체를 포함하는 신뢰성이 높은 반도체 장치를 제공하거나, 신규의 반도체 장치를 제공하거나, 신규의 표시 장치를 제공하는 것을 목적으로 한다.

상기 목적에 대한 설명은, 다른 목적의 존재를 배제하지 않는다는 점에 주목해야 한다. 본 발명의 일 실시예에서, 이들 목적 모두를 달성할 필요는 없다. 상기 목적들 외의 다른 목적들은, 명세서 등의 설명으로부터 명확해질 것이며, 이들로부터 유래될 수 있다.

본 발명의 일 실시예는, 구동 회로부에 제공된 제1 트랜지스터 및 화소부에 제공된 제2 트랜지스터를 포함하는 반도체 장치이며; 제1 트랜지스터 및 제2 트랜지스터는 상이한 구조를 갖는다. 또한, 제1 트랜지스터 및 제2 트랜지스터는, 탑-게이트 구조를 갖는 트랜지스터들이다. 상기 트랜지스터들 각각의 산화물 반도체 막에 있어서, 게이트 전극과 겹치지 않는 영역들에 불순물 원소를 함유한다. 상기 불순물 원소를 함유하는 산화물 반도체 막의 영역들은, 저 저항 영역들로서 기능한다. 또한, 산화물 반도체 막의 상기 불순물 원소를 함유하는 영역들은, 수소를 함유하는 막(film containing hydrogen)과 접한다. 또한, 상기 수소를 함유하는 막의 개구부들을 통해 상기 불순물 원소를 함유하는 영역들과 접하는 소스 전극 및 드레인 전극으로서 기능하는 도전막들을, 제공할 수 있다.

구동 회로부에 제공된 제1 트랜지스터는, 산화물 반도체 막을 개재해서 서로 겹치는 2개의 게이트 전극을 포함한다는 점에 주목해야 한다.

불순물 원소로서, 수소, 붕소, 탄소, 질소, 불소, 알루미늄, 실리콘, 인, 염소 또는 희가스 원소가 주어진다.

산화물 반도체 막은, 수소와, 불순물 원소로서 희가스 원소, 붕소, 탄소, 질소, 불소, 알루미늄, 실리콘, 인 및 염소 중 적어도 1개를 함유할 때, 도전성이 높아진다. 따라서, 산화물 반도체 막에 있어서, 게이트 전극과 겹치지 않는 영역에 상기 불순물 원소를 함유하는 영역들이 제공되고, 불순물 원소를 함유하는 영역들이 소스 전극 및 드레인 전극과 접하지 않을 경우, 트랜지스터의 기생 저항 및 기생 용량을 저감할 수 있고, 높은 온 전류를 갖는 트랜지스터가 획득된다.

또한, 구동 회로부에 제공된 제1 트랜지스터 및 화소부에 제공된 제2 트랜지스터는 금속 원소들의 원자비가 상이한 산화물 반도체 막을 포함할 수 있다.

구동 회로부에 제공된 제1 트랜지스터 및 화소부에 제공된 제2 트랜지스터는 각각, 산화물 반도체 막 대신에, 제1 막 및 제2 막을 포함하는 다층막을 포함할 수 있다.

본 발명의 일 실시예는, 산화물 반도체를 포함하는 신규의 반도체 장치를 제공할 수 있다. 특히, 산화물 반도체를 포함하는 평면형 반도체 장치를 제공할 수 있다. 대안적으로, 산화물 반도체를 포함하는 온 전류가 큰 반도체 장치를 제공할 수 있거나, 산화물 반도체를 포함하는 오프 전류가 작은 반도체 장치를 제공할 수 있거나, 산화물 반도체를 포함하는 점유 면적이 작은 반도체 장치를 제공할 수 있거나, 산화물 반도체를 포함하는 안정된 전기적 특성을 갖는 반도체 장치를 제공할 수 있거나, 산화물 반도체를 포함하는 신뢰성이 높은 반도체 장치를 제공할 수 있거나, 신규의 반도체 장치를 제공할 수 있거나, 신규의 표시 장치를 제공할 수 있다.

이들 효과에 대한 설명은, 다른 효과의 존재를 배제하지 않는다는 점에 주목해야 한다. 본 발명의 일 실시예는, 반드시 상기 나열된 효과 모두를 달성할 필요는 없다. 다른 효과들은, 명세서, 도면, 청구항 등의 기재로부터 명확해질 것이며, 이들로부터 유래될 수 있다.

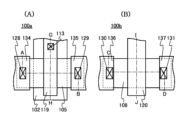

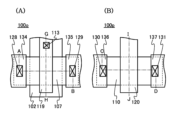

도 1의 (A) 및 도 1의 (B)는 반도체 장치의 일 실시예를 나타내는 상면도.

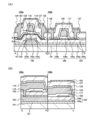

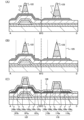

도 2의 (A) 및 도 2의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

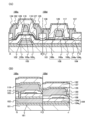

도 3의 (A) 및 도 3의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

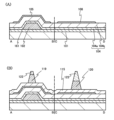

도 4의 (A) 및 도 4의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

도 5의 (A) 및 도 5의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 6의 (A) 내지 도 6의 (C)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 7의 (A) 및 도 7의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 8의 (A) 및 도 8의 (B)는 반도체 장치의 일 실시예를 도시하는 상면도.

도 9의 (A) 및 도 9의 (B)는 반도체 장치의 일 실시예를 도시하는 단면도.

도 10의 (A) 및 도 10의 (B)는 반도체 장치의 일 실시예를 도시하는 단면도.

도 11의 (A) 및 도 11의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 12의 (A) 내지 도 12의 (C)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 13의 (A) 및 도 13의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

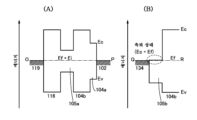

도 14의 (A) 및 도 14의 (B)는 본 발명의 일 실시예의 트랜지스터의 밴드 다이어그램을 도시하는 도면.

도 15의 (A) 및 도 15의 (B)는 본 발명의 일 실시예의 트랜지스터의 밴드 다이어그램을 도시하는 도면.

도 16의 (A) 내지 도 16의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 17의 (A) 내지 도 17의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 18의 (A) 내지 도 18의 (E)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 19의 (A) 및 도 19의 (B)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 20의 (A) 내지 도 20의 (D)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 21의 (A) 및 도 21의 (B)는 트랜지스터의 제조 공정을 설명하는 단면도.

도 22의 (A) 내지 도 22의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 23의 (A) 내지 도 23의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 24의 (A) 내지 도 24의 (E)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 25의 (A) 및 도 25의 (B)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 26 의 (A) 내지 도 26의 (D)는 각각 트랜지스터의 구조를 설명하는 단면도.

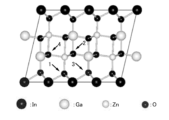

도 27은 계산 모델을 도시하는 도면.

도 28의 (A) 및 도 28의 (B)는 각각 초기 상태와 최종 상태를 도시하는 도면.

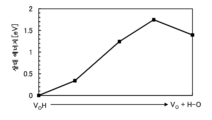

도 29는 활성화 장벽을 도시하는 도면.

도 30의 (A) 및 도 30의 (B)는 각각 초기 상태와 최종 상태를 도시하는 도면.

도 31은 활성화 장벽을 도시하는 도면.

도 32는 VOH의 천이 레벨을 도시하는 도면.

도 33의 (A) 내지 도 33의 (C)는 표시 장치를 나타내는 블록도 및 회로도.

도 34는 표시 장치의 일 실시예를 나타내는 상면도.

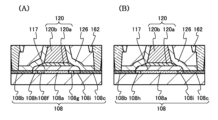

도 35의 (A) 및 도 35의 (B)는 각각 표시 장치의 일 실시예를 나타내는 단면도.

도 36의 (A) 및 도 36의 (B)는 각각 표시 장치의 일 실시예를 나타내는 단면도.

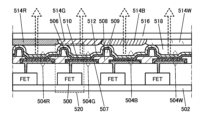

도 37은 발광 장치의 화소부의 구조를 나타내는 단면도.

도 38은 표시 모듈을 나타내는 도면.

도 39의 (A) 내지 도 39의 (G)는 전자 장치를 나타내는 도면.

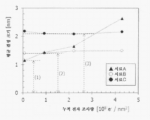

도 40은 비저항의 온도 의존성을 나타내는 도면.

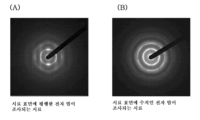

도 41의 (A) 내지 도 41의 (D)는 CAAC-OS의 단면의 Cs 보정 고해상도 TEM 상 및 CAAC-OS의 개략 단면도.

도 42의 (A) 내지 도 42의 (D)는 CAAC-OS의 평면의 Cs 보정 고해상도 TEM 상.

도 43의 (A) 내지 도 43의 (C)는 CAAC-OS 및 단결정 산화물 반도체의 XRD에 의한 구조적 해석을 도시하는 도면.

도 44의 (A) 및 도 44의 (B)는 CAAC-OS의 전자 회절 패턴을 도시하는 도면.

도 45는 In-Ga-Zn 산화물의 전자 조사에 의해 유발된 결정부(crystal part)의 변화를 도시하는 도면.

도 2의 (A) 및 도 2의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

도 3의 (A) 및 도 3의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

도 4의 (A) 및 도 4의 (B)는 반도체 장치의 일 실시예를 나타내는 단면도.

도 5의 (A) 및 도 5의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 6의 (A) 내지 도 6의 (C)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 7의 (A) 및 도 7의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 8의 (A) 및 도 8의 (B)는 반도체 장치의 일 실시예를 도시하는 상면도.

도 9의 (A) 및 도 9의 (B)는 반도체 장치의 일 실시예를 도시하는 단면도.

도 10의 (A) 및 도 10의 (B)는 반도체 장치의 일 실시예를 도시하는 단면도.

도 11의 (A) 및 도 11의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 12의 (A) 내지 도 12의 (C)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 13의 (A) 및 도 13의 (B)는 반도체 장치의 제조 방법의 일 실시예를 나타내는 단면도.

도 14의 (A) 및 도 14의 (B)는 본 발명의 일 실시예의 트랜지스터의 밴드 다이어그램을 도시하는 도면.

도 15의 (A) 및 도 15의 (B)는 본 발명의 일 실시예의 트랜지스터의 밴드 다이어그램을 도시하는 도면.

도 16의 (A) 내지 도 16의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 17의 (A) 내지 도 17의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 18의 (A) 내지 도 18의 (E)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 19의 (A) 및 도 19의 (B)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 20의 (A) 내지 도 20의 (D)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 21의 (A) 및 도 21의 (B)는 트랜지스터의 제조 공정을 설명하는 단면도.

도 22의 (A) 내지 도 22의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 23의 (A) 내지 도 23의 (F)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 24의 (A) 내지 도 24의 (E)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 25의 (A) 및 도 25의 (B)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 26 의 (A) 내지 도 26의 (D)는 각각 트랜지스터의 구조를 설명하는 단면도.

도 27은 계산 모델을 도시하는 도면.

도 28의 (A) 및 도 28의 (B)는 각각 초기 상태와 최종 상태를 도시하는 도면.

도 29는 활성화 장벽을 도시하는 도면.

도 30의 (A) 및 도 30의 (B)는 각각 초기 상태와 최종 상태를 도시하는 도면.

도 31은 활성화 장벽을 도시하는 도면.

도 32는 VOH의 천이 레벨을 도시하는 도면.

도 33의 (A) 내지 도 33의 (C)는 표시 장치를 나타내는 블록도 및 회로도.

도 34는 표시 장치의 일 실시예를 나타내는 상면도.

도 35의 (A) 및 도 35의 (B)는 각각 표시 장치의 일 실시예를 나타내는 단면도.

도 36의 (A) 및 도 36의 (B)는 각각 표시 장치의 일 실시예를 나타내는 단면도.

도 37은 발광 장치의 화소부의 구조를 나타내는 단면도.

도 38은 표시 모듈을 나타내는 도면.

도 39의 (A) 내지 도 39의 (G)는 전자 장치를 나타내는 도면.

도 40은 비저항의 온도 의존성을 나타내는 도면.

도 41의 (A) 내지 도 41의 (D)는 CAAC-OS의 단면의 Cs 보정 고해상도 TEM 상 및 CAAC-OS의 개략 단면도.

도 42의 (A) 내지 도 42의 (D)는 CAAC-OS의 평면의 Cs 보정 고해상도 TEM 상.

도 43의 (A) 내지 도 43의 (C)는 CAAC-OS 및 단결정 산화물 반도체의 XRD에 의한 구조적 해석을 도시하는 도면.

도 44의 (A) 및 도 44의 (B)는 CAAC-OS의 전자 회절 패턴을 도시하는 도면.

도 45는 In-Ga-Zn 산화물의 전자 조사에 의해 유발된 결정부(crystal part)의 변화를 도시하는 도면.

이하, 본 명세서에 개시된 본 발명의 실시예들에 대하여 첨부 도면을 참조하여 설명한다. 본 발명은 이하의 설명에 제한되지 않으며, 본 기술분야의 숙련된 자는, 본 발명의 정신 및 범위에부터 벗어남 없이, 모드 및 상세 내용이 다양한 방식으로 변경될 수 있다는 것을 쉽사리 인식할 것인 점에 주목해야 한다. 따라서, 본 발명은 이하에 실시예들의 내용에 제한되는 것으로 해석되어서는 안 된다.

도면 등에 나타나 있는 각 구조의 위치, 크기, 범위 등은, 단순화를 위해, 정확하게 도시되어 있지 않은 경우가 몇몇 있다는 점에 주목해야 한다. 따라서, 개시된 발명은, 도면 등에 개시된 위치, 크기, 범위 등에 반드시 제한되는 것은 아니다.

본 명세서 등에 있어서, "제1", "제2", "제3" 등의 서수사는, 구성 요소의 혼동을 피하기 위하여 사용되고, 이들 용어는 구성 요소의 개수를 제한하는 것을 의미하지 않는다.

본 명세서 등에 있어서, "위(over)" 또는 "아래(below)" 등의 용어는, 반드시 구성 요소가 다른 구조 요소의 "바로 위" 또는 "바로 아래"에 위치되는 것을 의미하지 않는다는 점에 주목해야 한다. 예를 들어, "게이트 절연막 위의 게이트 전극"이라는 표현은, 게이트 절연막과 게이트 전극 사이에 추가 구성 요소가 존재하는 경우를 의미할 수 있다.

또한, 본 명세서 등에 있어서, "전극" 또는 "배선" 등의 용어는, 구성 요소의 기능을 제한하는 것이 아니다. 예를 들어, "전극"은 "배선"의 일부로서 사용되는 경우가 몇몇 있고, 그 반대도 성립한다. 또한, "전극" 또는 "배선"이라는 용어는, 집적 방식으로 형성된 복수의 "전극" 및 "배선"의 조합을 의미할 수도 있다.

"소스" 및 "드레인"의 기능은, 종종 반대 극성의 트랜지스터를 사용할 때, 또는 회로 동작에 있어서 전류의 방향이 변화될 때, 서로 대체된다. 따라서, 본 명세서 등에 있어서는, "소스" 및 "드레인"이라는 용어는, 각각 드레인 및 소스를 표기하기 위해 사용될 수 있다.

본 명세서 등에 있어서, "전기적으로 접속된"이라는 용어는, 구성 요소들이 임의의 전기적 기능을 갖는 물체를 통해 접속되는 경우를 포함한다는 점에 주목해야 한다. "임의의 전기적 기능을 갖는 물체"에 관해서, 이 물체를 통해 접속되는 구성 요소들 사이에 전기 신호가 송신 및 수신될 수 있는 한, 특별한 제한이 존재하지 않는다. "임의의 전기적 기능을 갖는 물체"의 예는, 전극 및 배선뿐만 아니라, 트랜지스터 등의 스위칭 소자, 저항 소자, 인덕터, 용량소자 및 각종 기능을 갖는 소자이다.

(실시예 1)

본 실시예에서는, 반도체 장치 및 반도체 장치의 제조 방법의 일 실시예에 대하여, 도 1의 (A) 및 도 1의 (B), 도 2의 (A) 및 도 2의 (B), 도 3의 (A) 및 도 3의 (B), 도 4의 (A) 및 도 4의 (B), 도 5의 (A) 및 도 5의 (B), 도 6의 (A) 내지 도 6의 (C), 도 7의 (A) 및 도 7의 (B)를 참조하여 설명한다.

<반도체 장치의 구조 1>

도 1의 (A) 및 도 1의 (B), 및 도 2의 (A) 및 도 2의 (B)에, 반도체 장치에 포함되는 트랜지스터들의 예로서, 각각 탑-게이트 구조를 갖는 트랜지스터들을 도시한다. 여기에서, 반도체 장치의 예로서 표시 장치를 설명한다. 또한, 표시 장치의 구동 회로부 및 화소부에 제공되는 트랜지스터들의 구조를 설명한다. 본 실시예에 설명된 표시 장치에서, 구동 회로부에서의 트랜지스터와 화소부에서의 트랜지스터는, 상이한 구조를 갖는다. 구동 회로부에서의 트랜지스터는, 듀얼-게이트 구조를 갖고, 화소부에서의 트랜지스터는 단일-게이트 구조를 갖는다.

도 1의 (A) 및 도 1의 (B)는, 구동 회로부에 제공되는 트랜지스터(100a) 및 화소부에 제공되는 트랜지스터(100b)의 상면도이다. 도 2의 (A) 및 도 2의 (B)는, 트랜지스터(100a, 100b)의 단면도이다. 도 1의 (A)는, 트랜지스터(100a)의 상면도이고, 도 1의 (B)는, 트랜지스터(100b)의 상면도이다. 도 2의 (A)는, 도 1의 (A)의 일점 쇄선 A-B, 및 도 1의 (B)의 일점 쇄선 C-D를 따른 단면도이다. 도 2의 (B)는 도 1의 (A)의 일점 쇄선 G-H 및 도 1의 (B)의 일점 쇄선 I-J를 따른 단면도이다. 도 1의 (A) 및 도 1의 (B)에서는, 단순화를 위하여, 기판(101), 절연막(104), 절연막(126), 절연막(127) 등은 도시 생략되어 있다는 점에 주목해야 한다. 도 2의 (A)는 트랜지스터(100a 및 100b)의 채널 길이 방향의 단면도이고, 도 2의 (B)는 트랜지스터(100a 및 100b)의 채널 폭 방향의 단면도이다.

이하 설명된 트랜지스터들의 상면도에 있어서, 트랜지스터(100a 및 100b)의 것과 마찬가지 방식으로, 일부 구성 요소들이 도시 생략되는 경우가 몇몇 있다. 또한, 일점 쇄선 A-B의 방향 및 일점 쇄선 C-D의 방향은 채널 길이 방향이라 불릴 수 있고, 일점 쇄선 G-H의 방향 및 일점 쇄선 I-J의 방향은 채널 폭 방향이라 불릴 수 있다.

도 2의 (A) 및 도 2의 (B)에 도시한 트랜지스터(100a)는, 기판(101) 위에 도전막(102)과, 기판(101) 및 도전막(102) 위에 절연막(104)과, 절연막(104) 위에 산화물 반도체 막(105)과, 산화물 반도체 막(105)에 접하는 절연막(116)과, 절연막(116)을 개재해서 산화물 반도체 막(105)과 겹치는 도전막(119)을 포함한다.

도전막(102 및 119)은, 게이트 전극으로서 기능한다. 즉, 트랜지스터(100a)는, 듀얼-게이트 구조를 갖는 트랜지스터이다. 절연막(104 및 116)은, 게이트 절연막으로서 기능한다.

도시 생략되어 있지만, 도전막(102)은 산화물 반도체 막(105)의 전체 영역과 겹칠 수 있다는 점에 주목해야 한다.

산화물 반도체 막(105)은, 도전막(102 및 119)과 겹치는 채널 영역(105a)과, 채널 영역(105a)을 개재하는 저 저항 영역(105b 및 105c)을 포함한다.

트랜지스터(100a)에는, 저 저항 영역(105b, 105c)에 접하는 절연막(126)이 제공된다. 또한, 절연막(126) 위에 절연막(127)이 제공될 수 있다. 또한, 절연막(126 및 127)의 개구부(128 및 129)를 통해, 산화물 반도체 막(105)의 저 저항 영역(105b 및 105c)에 접하는 도전막(134 및 135)들이 제공된다.

기판(101) 위에 질화물 절연막(161)이 제공되는 것이 바람직하다. 질화물 절연막(161)의 예는, 질화 실리콘 막 및 질화 알루미늄 막을 포함한다. 질화물 절연막(161)으로 기판(101)을 덮음으로써, 기판(101)에 포함되는 원소의 확산을 방지하는 것이 가능하게 된다.

트랜지스터(100b)는, 기판(101) 위에 형성된 절연막(104) 위에 산화물 반도체 막(108); 산화물 반도체 막(108)에 접하는 절연막(117); 절연막(117)을 개재해서 산화물 반도체 막(108)과 겹치는 도전막(120)을 포함한다.

도전막(120)은, 게이트 전극으로서 기능한다. 절연막(117)은, 게이트 절연막으로서 기능한다.

산화물 반도체 막(108)은, 도전막(120)과 겹치는 채널 영역(108a)과, 채널 영역(108a)을 개재하는 저 저항 영역(108b 및 108c)을 포함한다.

트랜지스터(100b)에는, 저 저항 영역(108b 및 108c)에 접하는 절연막(126)이 제공된다. 또한, 절연막(126) 위에 절연막(127)이 제공될 수 있다. 또한, 절연막(126 및 127)의 개구부(130 및 131)를 통해, 산화물 반도체 막(108)의 저 저항 영역(108b 및 108c)에 접하는 도전막(136 및 137)이 제공된다.

도전막(134, 135, 136 및 137)을 덮도록 질화물 절연막(162)을 제공하는 것이 바람직하다는 점에 주목해야 한다. 질화물 절연막(162)은, 외부로부터의 불순물의 확산을 방지할 수 있다.

산화물 반도체 막(105)에 있어서, 도전막(119)과 겹치지 않는 영역에는, 산소 결손을 형성하는 원소가 포함된다. 산화물 반도체 막(108)에 있어서, 도전막(120)과 겹치지 않는 영역에는, 산소 결손을 형성하는 원소가 포함된다. 이하, 산화물 반도체 막에 있어서, 이것에 첨가됨으로써 산소 결손을 형성하는 원소들이 불순물 원소로서 설명된다. 불순물 원소의 전형적인 예는, 수소, 붕소, 탄소, 질소, 불소, 알루미늄, 실리콘, 인, 염소, 및 희가스 원소이다. 희가스 원소의 전형적인 예는, 헬륨, 네온, 아르곤, 크립톤 및 크세논이다.

절연막(126)은 수소를 함유하는 막이며, 질화물 절연막이 그 전형적인 예이다. 질화물 절연막의 예는, 질화 실리콘 막, 및 질화 알루미늄 막을 포함한다. 절연막(126)은 산화물 반도체 막(105 및 108)에 접한다. 따라서, 절연막(126)에 함유된 수소가, 산화물 반도체 막(105 및 108) 내에 확산된다. 결과로서, 산화물 반도체 막(105 및 108)에 있어서, 절연막(126)과 접하는 영역에는, 많은 수소가 함유된다.

불순물 원소가 산화물 반도체에 첨가되는 경우, 산화물 반도체 중의 금속 원소와 산소 사이의 결합(bond)이 절단되어, 산소 결손이 형성된다. 불순물 원소의 첨가에 의해 산소 결손이 형성된 산화물 반도체에 수소를 첨가하는 경우, 수소가 산소 결손 장소(site)에 들어가고, 전도대(conduction band) 근방에 도너 준위를 형성하고; 따라서 산화물 반도체의 도전율이 증가한다. 그 결과, 산화물 도전체가 형성될 수 있다. 따라서, 산화물 도전체는 투광성을 갖는다. 여기에서, 도전체가 되는 산화물 반도체를, 산화물 도전체라고 지칭한다.

산화물 도전체는 축퇴 반도체이고, 전도대 에지(conduction band edge)와 페르미 준위(Fermi level)가 동일 또는 실질적으로 동일할 것이 제안된다. 이런 이유로, 산화물 도전체 막과, 소스 전극 및 드레인 전극으로서 기능하는 도전막 간에 오믹 접촉이 이루어지고; 따라서 산화물 도전체 막과, 소스 전극 및 드레인 전극으로서 기능하는 도전막 간에 접촉 저항을 저감할 수 있다.

즉, 저 저항 영역(105b, 105c, 108b 및 108c)은, 소스 영역 및 드레인 영역으로서 기능한다.

도전막(134, 135, 136 및 137)이 텅스텐, 티타늄, 알루미늄, 구리, 몰리브덴, 크롬, 탄탈륨, 혹은 이들 중 어느 것의 합금 등의 산소와 결합하기 쉬운 도전 재료를 사용하여 형성되는 경우에, 산화물 반도체 막에 함유된 산소가 도전막(134, 135, 136 및 137)에 함유된 도전 재료에 결합되고, 산화물 반도체 막(105 및 108)에 있어서 산소 결손이 형성된다. 또한, 도전막(134, 135, 136 및 137)을 형성하는 도전 재료의 구성 원소의 일부가 산화물 반도체 막(105 및 108) 내에 혼입되는 경우가 몇몇 있다. 결과로서, 도전막(134, 135, 136 및 137)과 접하는 저 저항 영역(105b, 105c, 108b 및 108c)은 도전성이 더 높아지고, 소스 영역 및 드레인 영역으로서 기능한다.

불순물 원소가 희가스 원소이며, 산화물 반도체 막(105 및 108)이 스퍼터링 법에 의해 형성되는 경우에, 저 저항 영역(105b, 105c, 108b 및 108c)은 각각 희가스 원소를 포함한다. 또한, 저 저항 영역(105b, 105c, 108b 및 108c)의 희가스 원소 농도가, 채널 영역(105a 및 108a)의 것보다 높다. 이것들은, 산화물 반도체 막(105 및 108)이 스퍼터링 법에 의해 형성되는 경우에, 스퍼터링 가스로서 희가스를 사용하여서, 산화물 반도체 막(105 및 108)이 희가스를 포함하게 되는 것; 및 저 저항 영역(105b, 105c, 108b 및 108c)에 있어서 산소 결손을 형성하기 위하여, 의도적으로 희가스가 저 저항 영역(105b, 105c, 108b 및 108c)에 첨가되는 것이 원인이다. 채널 영역(105a 및 108a)에 첨가되는 것과는 상이한 희가스 원소가 저 저항 영역(105b, 105c, 108b 및 108c)에 첨가될 수 있다는 점에 주목해야 한다.

저 저항 영역(105b 및 105c)은 절연막(126)과 접하기 때문에, 저 저항 영역(105b 및 105c)의 수소 농도는 채널 영역(105a)의 수소 농도보다 높다. 또한, 저 저항 영역(108b 및 108c)은 절연막(126)과 접하기 때문에, 저 저항 영역(108b 및 108c)의 수소 농도는 채널 영역(108a)의 수소 농도보다 높다.

저 저항 영역(105b, 105c, 108b 및 108c)에 있어서, SIMS에 의해 측정된 수소 농도는, 8×1019atoms/㎝3 이상, 1×1020atoms/㎝3 이상, 또는 5×1020atoms/㎝3 이상일 수 있다. 채널 영역(105a 및 108a)에 있어서, SIMS에 의해 측정된 수소 농도는, 5×1019atoms/㎝3 이하, 1×1019atoms/㎝3 이하, 5×1018atoms/㎝3 이하, 1×1018atoms/㎝3 이하, 5×1017atoms/㎝3 이하, 또는 1×1016atoms/㎝3 이하일 수 있다는 점에 주목해야 한다.

저 저항 영역(105b, 105c, 108b 및 108c)은, 채널 영역(105a 및 108a)보다 수소 농도가 높아지고, 희가스 원소의 첨가로 인해 채널 영역(105a 및 108a)보다 산소 결손이 많아진다. 따라서, 저 저항 영역(105b, 105c, 108b 및 108c)은 도전성이 더 높아지고, 소스 영역 및 드레인 영역으로서 기능한다. 저 저항 영역(105b, 105c, 108b 및 108c)의 비저항은, 전형적으로, 1×10-3Ω㎝ 이상 1×104Ω㎝ 미만, 또는 1×10-3Ω㎝ 이상 1×10-1Ω㎝ 미만일 수 있다.

저 저항 영역(105b, 105c, 108b 및 108c)에 있어서, 수소의 양이 산소 결손의 양과 동일하거나 적은 경우, 수소가 산소 결손에 의해 쉽게 포획(capture)되고, 채널 영역(105a 및 108a) 내에 쉽게 확산되지 않는다는 점에 주목해야 한다. 결과로서, 노멀리 오프 트랜지스터를 제조할 수 있다.

또한, 저 저항 영역(105b, 105c, 108b 및 108c)에 있어서, 산소 결손의 양이 수소의 양보다 많은 경우에, 수소의 양을 제어함으로써, 저 저항 영역(105b, 105c, 108b 및 108c)의 캐리어 밀도를 제어할 수 있다. 대안적으로, 저 저항 영역(105b, 105c, 108b 및 108c)에 있어서, 수소의 양이 산소 결손의 양보다 많은 경우에, 산소 결손의 양을 제어함으로써, 저 저항 영역(105b, 105c, 108b 및 108c)의 캐리어 밀도를 제어할 수 있다. 저 저항 영역(105b, 105c, 108b 및 108c)의 캐리어 밀도가 5×1018/㎝3 이상, 또는 1×1019/㎝3 이상, 또는 1×1020/㎝3 이상인 경우, 트랜지스터들에서, 채널 영역(105a)과, 소스 및 드레인 전극들로서 기능하는 도전막(134 및 135) 사이, 및 채널 영역(108a)과, 소스 및 드레인 전극들로서 기능하는 도전막(136 및 137) 사이에서의 저항이 작고, 큰 온 전류가 획득될 수 있다는 점에 주목해야 한다.

본 실시예에 설명된 트랜지스터(100a 및 100b)에 있어서, 채널 영역(105a)과, 소스 및 드레인 전극들로서 기능하는 도전막(134 및 135) 사이에는, 저 저항 영역(105b 및 105c)이 제공되고, 채널 영역(108a)과, 소스 및 드레인 전극들로서 기능하는 도전막(136 및 137) 사이에는, 저 저항 영역(108b 및 108c)이 제공되고; 따라서 트랜지스터들은 작은 기생 저항을 갖는다.

또한, 트랜지스터(100a)에 있어서, 도전막(119)은, 도전막(134 및 135)과 겹치지 않고; 따라서 도전막(119)과, 각각의 도전막(134 및 135) 사이의 기생 용량을 저감할 수 있다. 트랜지스터(100b)에 있어서, 도전막(120)은 도전막(136 및 137)과 겹치지 않고; 따라서, 도전막(120)과, 각각의 도전막(136 및 137) 사이에 기생 용량을 저감할 수 있다.

그 결과, 트랜지스터(100a 및 100b)는, 온 전류가 크고, 전계 효과 이동도가 높다.

트랜지스터(100a)에 있어서, 도전막(119)을 마스크로 사용하여, 불순물 원소가 산화물 반도체 막(105)에 첨가된다. 트랜지스터(100b)에 있어서, 도전막(120)을 마스크로 사용하여, 불순물 원소가 산화물 반도체 막(108)에 첨가된다. 즉, 자기 배향 방식으로 저 저항 영역을 형성할 수 있다.

트랜지스터(100a)에 있어서, 서로 접속되지 않은 도전막(102) 및 도전막(119)에, 상이한 전위를 인가하고; 이로써 트랜지스터(100a)의 임계 전압을 제어할 수 있다. 대안적으로, 도 1의 (A) 및 도 2의 (B)에 도시된 바와 같이, 개구부(113)를 통해 서로 접속된 도전막(102)과 도전막(119)에, 동일한 전위를 공급함으로써, 초기 특성의 변동을 저감할 수 있고, -GBT(negative gate bias-temperature) 스트레스 시험으로 인한 트랜지스터의 열화, 및 상이한 드레인 전압들에 있어서 온 전류의 상승 전압의 변화를 억제할 수 있다. 또한, 도 2의 (B)에 도시된 바와 같이, 도전막(102)과 도전막(119)이 서로 접속되는 경우, 도전막(102 및 119)의 전계가 산화물 반도체 막(105)의 상면 및 측면에 영향을 미치므로, 전체 산화물 반도체 막(105)에 있어서 캐리어가 흐른다. 즉, 캐리어가 흐르는 영역이 막 두께 방향으로 더 커져서, 캐리어 이동량이 증가한다. 결과로서, 트랜지스터(100a)의 온 전류 및 전계 효과 이동도가 증가한다. 트랜지스터(100a)는, 온 전류가 크기 때문에, 평면 면적이 작을 수 있다. 그 결과, 구동 회로부에 의한 점유 면적이 작은 협소화 베젤(narrow bezel)을 갖는 표시 장치를 제조할 수 있다.

또한, 표시 장치에 있어서, 구동 회로부에 포함되는 트랜지스터와, 화소부에 포함되는 트랜지스터는, 상이한 채널 길이를 가질 수 있다.

전형적으로, 구동 회로부에 포함되는 트랜지스터(100a)의 채널 길이는, 2.5㎛ 미만, 또는 1.45㎛ 이상 2.2㎛ 이하일 수 있다. 화소부에 포함되는 트랜지스터(100b)의 채널 길이는, 2.5㎛ 이상, 또는 2.5㎛ 이상 20㎛ 이하일 수 있다.

구동 회로부에 포함되는 트랜지스터(100a)의 채널 길이가, 2.5㎛ 미만, 바람직하게는 1.45㎛ 이상 2.2㎛ 이하인 경우, 화소부에 포함되는 트랜지스터(100b)와 비교하여, 전계 효과 이동도를 증가시킬 수 있고, 온 전류의 양을 증가시킬 수 있다. 그 결과, 고속 동작이 가능한 구동 회로부를 형성할 수 있다. 또한, 구동 회로부에 의한 점유 면적이 작은 표시 장치를 제조할 수 있다.

전계 효과 이동도가 높은 트랜지스터를 사용함으로써, 구동 회로부의 예로서의 신호선 구동 회로에 역다중화 회로를 형성할 수 있다. 역다중화 회로는, 하나의 입력 신호를 복수의 출력에 분배하고; 따라서 역다중화 회로를 사용하여 입력 신호용 입력 단자 수를 삭감할 수 있다. 예를 들어, 하나의 화소가 적색 서브 화소, 녹색 서브 화소 및 청색 서브 화소를 포함하고, 각 화소에 대응하는 역다중화 회로를 제공하는 경우, 입력 신호가 역다중화 회로에 의해 분배되어 각 서브 화소에 입력될 수 있다. 그 결과, 입력 단자 수를 1/3로 삭감할 수 있다.

온 전류가 큰 트랜지스터(100b)를 화소부에 제공하고; 이로써 배선수가 증가되는 대형 표시 장치 또는 고해상도 표시 장치에 있어서도, 배선들에서의 신호 지연을 저감할 수 있고, 표시 불균일을 억제할 수 있다.

상술된 바와 같이, 고속 동작이 가능한 트랜지스터를 사용하여 구동 회로부를 형성하고, 기생 용량이 작고 기생 저항이 작은 트랜지스터를 사용하여 화소부를 형성하는 경우, 더블 프레임 속도 구동(double-frame rate driving)이 가능한 고해상도 표시 장치를 제조할 수 있다.

도 2의 (A) 및 도 2의 (B)에 도시한 구조에 대하여 이하 상세히 설명한다.

기판(101)으로서는, 특별한 제한 없이, 각종 기판 중 어느 것을 사용할 수 있다. 기판의 예는, 반도체 기판(예를 들어, 단결정 기판 또는 실리콘 기판), SOI 기판, 유리 기판, 석영 기판, 플라스틱 기판, 금속 기판, 스테인리스 강 기판, 스테인리스 강 호일을 포함하는 기판, 텅스텐 기판, 텅스텐 호일을 포함하는 기판, 가요성 기판, 부착 필름, 섬유성 재료를 포함하는 종이, 및 기재 필름을 포함한다. 유리 기판의 예는, 바륨 붕규산 유리 기판, 알루미노 붕규산 유리 기판, 및 소다 석회 유리 기판이다. 가요성 기판, 부착 필름, 기재 필름 등의 예는, 이하와 같이, 폴리에틸렌 테레프탈레이트(PET), 폴리에틸렌 나프탈레이트(PEN), 및 폴리에테르술폰(PES)으로 대표되는 플라스틱; 아크릴 등의 합성 수지; 폴리프로필렌; 폴리불화비닐; 폴리염화비닐; 폴리에스테르; 폴리아미드; 폴리이미드; 아라미드; 에폭시; 무기 증착 필름; 및 종이이다. 구체적으로, 반도체 기판, 단결정 기판, SOI 기판 등을 사용하여 트랜지스터를 형성하는 경우, 특성, 크기, 형상 등의 편차가 적고, 전류 공급 능력이 높고, 크기가 작은 트랜지스터를 제조하는 것이 가능하다. 이러한 트랜지스터를 이용하여 회로를 형성함으로써, 회로의 전력 소비를 저감할 수 있거나, 회로의 고집적화를 이루어 낼 수 있다.

기판(101)으로서, 가요성 기판을 사용할 수 있고, 가요성 기판 위에 바로 트랜지스터를 제공할 수 있다. 대안적으로, 기판(101)과 각 트랜지스터 사이에 박리 층을 제공할 수 있다. 박리층은, 해당 박리층 위에 형성된 반도체 장치의 일부 혹은 전부가 기판(101)으로부터 분리되고 다른 기판에 위에 전사되는 경우에, 사용될 수 있다. 그러한 경우에, 트랜지스터는 내열성이 낮은 기판 또는 가요성 기판에도 전사될 수 있다. 상기 박리층을 위해, 예를 들어, 텅스텐막과 산화 실리콘 막인 무기 막들을 포함하는 적층체, 또는 기판 위에 형성된 폴리이미드 등의 유기 수지막이 사용될 수 있다.

트랜지스터가 전사되는 기판의 예는, 또한, 트랜지스터들이 형성될 수 있는 상술한 기판 외에, 종이 기판, 셀로판 기판, 아라미드 필름 기판, 폴리이미드 필름 기판, 석재 기판, 목재 기판, 천 기판(천연 섬유(예를 들어, 견, 면 또는 마), 합성 섬유(예를 들어, 나일론, 폴리우레탄 또는 폴리에스테르), 재생 섬유(예를 들어, 아세테이트, 큐프라, 레이온 또는 재생 폴리에스테르) 등을 포함함), 피혁 기판, 고무 기판 등을 포함한다. 이러한 기판을 사용하는 경우, 특성이 우수한 트랜지스터, 또는 소비 전력이 작은 트랜지스터를 형성할 수 있거나, 내구성이 크고 내열성이 높은 장치를 제공할 수 있거나, 경량화 또는 박형화를 달성할 수 있다.

절연막(104)은, 산화물 절연막 또는 질화물 절연막을 사용하여 단층 또는 적층으로 형성될 수 있다. 산화물 반도체 막(105 및 108)과의 계면 특성을 향상시키기 위하여, 절연막(104) 중에서 적어도 산화물 반도체 막(105 및 108)과 접하는 영역은, 산화물 절연막을 사용하여 형성하는 것이 바람직하다는 점에 주목해야 한다. 가열에 의해 산소가 방출되는 산화물 절연막을 사용하여 절연막(104)이 형성되는 경우, 가열 처리에 의해, 절연막(104)에 함유된 산소를, 산화물 반도체 막(105 및 108)으로 이동시킬 수 있다. 절연막(104) 중에서 도전막(102)과 접하는 영역은, 질화물 절연막을 사용하여 형성하는 것이 바람직하고, 이 경우에, 도전막(102)에 함유된 금속 원소가 산화물 반도체 막(105 및 108)으로 이동하는 것을 방지할 수 있다.

절연막(104)의 두께는, 50nm 이상, 100nm 이상 3000nm 이하, 또는 200nm 이상 1000nm 이하일 수 있다. 절연막(104)의 두께를 증가시킴으로써, 절연막(104)으로부터의 방출되는 산소의 양이 증가될 수 있고, 절연막(104)과, 각각의 산화물 반도체 막(105 및 108)과의 계면에 있어서 계면 상태(interface state) 밀도, 및 산화물 반도체 막(105)에서의 채널 영역(105a) 및 산화물 반도체 막(108)에서의 채널 영역(108a)에 함유된 산소 결손을 저감할 수 있다.

절연막(104)은, 산화 실리콘, 산화질화 실리콘, 질화산화 실리콘, 질화 실리콘, 산화 알루미늄, 산화 하프늄, 산화 갈륨 또는 Ga-Zn 산화물 등 중 1개 이상을 사용하여, 단층 또는 적층으로 형성될 수 있다.

여기에서, 절연막(104)이, 절연막(104a 및 104b)을 적층하여 형성된다. 절연막(104a)으로서 질화물 절연막을 사용하는 경우, 도전막(102)에 함유된 금속 원소의 확산을 방지할 수 있다. 절연막(104b)으로서 산화물 절연막을 사용하는 경우, 예를 들어, 절연막(104)과, 각각의 산화물 반도체 막(105 및 108)과의 계면에서의 계면 상태 밀도를 저감할 수 있다.

산화물 반도체 막(105 및 108)은, 전형적으로, In-Ga 산화물, In-Zn 산화물, 또는 In-M-Zn 산화물(M은, Mg, Al, Ti, Ga, Y, Zr, La, Ce, Nd, 또는 Hf 임) 등의 금속 산화물을 사용하여 형성된다. 산화물 반도체 막(105 및 108)은, 투광성을 갖는다는 점에 주목해야 한다.

산화물 반도체 막(105 및 108)으로서 In-M-Zn 산화물을 사용하는 경우에, In 및 M의 합을 100atomic%로 가정할 때, In과 M의 비율은, 각각 25atomic% 이상 및 75atomic% 미만, 혹은 각각 34atomic% 이상 및 66atomic% 미만으로 설정되는 것이 바람직하다는 점에 주목해야 한다.

산화물 반도체 막(105 및 108)의 에너지 갭은, 각각 2eV 이상, 2.5eV 이상, 또는 3eV 이상이다.

산화물 반도체 막(105 및 108) 각각의 두께는, 3nm 이상 200nm 이하, 또는 3nm 이상 100nm 이하, 또는 3nm 이상 50nm 이하일 수 있다.

산화물 반도체 막(105 및 108)이 In-M-Zn 산화물(M은, Mg, Al, Ti, Ga, Y, Zr, La, Ce, Nd, 또는 Hf 임)을 함유하는 경우에, In-M-Zn 산화물의 막을 형성하기 위해 사용되는 스퍼터링 타겟의 금속 원소들의 원자비는 In≥M 및 Zn≥M을 만족하는 것이 바람직하다. 스퍼터링 타겟의 금속 원소들의 원자비로서, In:M:Zn=1:1:1, In:M:Zn=1:1:1.2, In:M:Zn=2:1:1.5, In:M:Zn=2:1:2.3, In:M:Zn=2:1:3, In:M:Zn=3:1:2 등이 바람직하다. 형성된 산화물 반도체 막(105 및 108)에서 금속 원소들의 원자비는, 상기 스퍼터링 타겟의 금속 원소들의 상기 원자비로부터, 오차로서 ±40% 범위 내에서 변동한다는 점에 주목해야 한다.

산화물 반도체 막(105 및 108)에, 14족에 속하는 원소들 중 하나인 실리콘 또는 탄소가 함유되는 경우, 산화물 반도체 막(105 및 108)에 있어서 산소 결손이 증가되고, 산화물 반도체 막(105 및 108)이 n형 막이 된다. 따라서, 산화물 반도체 막(105 및 108)에 있어서, 특히 채널 영역(105a 및 108a)에서, 실리콘 또는 탄소의 농도(SIMS에 의해 측정되는 농도)는, 2×1018atoms/㎝3 이하, 또는 2×1017atoms/㎝3 이하로 설정될 수 있다. 결과로서, 트랜지스터는 각각 포지티브 임계 전압(노멀리 오프 특성)을 갖는다.

또한, 산화물 반도체 막(105 및 108)에 있어서, 특히 채널 영역(105a 및 108a)에서, SIMS에 의해 측정되는 알칼리 금속 또는 알칼리 토금속의 농도는, 1×1018atoms/㎝3 이하, 또는 2×1016atoms/㎝3 일 수 있다. 알칼리 금속 및 알칼리 토금속은, 산화물 반도체와 결합될 때, 캐리어를 생성하고, 이 경우에 트랜지스터의 오프 전류가 증가될 수 있다. 따라서, 채널 영역(105a 및 108a)에서 알칼리 금속 또는 알칼리 토금속의 농도를 저감하는 것이 바람직하다. 결과로서, 트랜지스터는 각각 포지티브 임계 전압(노멀리 오프 특성)을 갖는다.

또한, 산화물 반도체 막(105 및 108)에 있어서, 특히 채널 영역(105a 및 108a)에 질소가 함유되는 경우, 캐리어로서 기능하는 전자가 발생되고, 캐리어 밀도가 증가되고, 산화물 반도체 막(105 및 108)이 n형 막이 되는 경우가 몇몇 있다. 따라서, 질소를 함유하는 산화물 반도체 막을 포함하는 트랜지스터는, 노멀리 온 특성을 가질 가능성이 있다. 따라서, 산화물 반도체 막에 있어서, 특히 채널 영역(105a 및 108a)에서, 가능한 많이 질소를 저감하는 것이 바람직하다. 예를 들어, SIMS에 의해 측정되는 질소의 농도는, 5×1018atoms/㎝3 이하로 설정될 수 있다.

산화물 반도체 막(105 및 108)에 있어서, 특히 채널 영역(105a 및 108a)에서, 불순물 원소를 저감함으로써, 산화물 반도체 막의 캐리어 밀도를 저감할 수 있다. 산화물 반도체 막(105 및 108)에 있어서, 특히 채널 영역(105a 및 108a)에서, 캐리어 밀도는 1×1017/㎝3 이하, 또는 1×1015/㎝3 이하, 또는 1×1013/㎝3 이하, 또는 8×1011/㎝3 이하, 또는 1×1011/㎝3 이하, 바람직하게는 1×1010/㎝3 미만이고, 1×10-9/㎝3 이상으로 설정될 수 있다.

산화물 반도체 막(105 및 108)을 위해, 불순물 농도가 낮고 결함 준위(defect states) 밀도가 낮은 산화물 반도체 막을 각각 사용할 수 있고, 이 경우에, 트랜지스터는 더 우수한 전기적 특성을 갖는다. 여기에서, 불순물 농도가 낮고 결함 준위 밀도가 낮은 상태(산소 결손의 양이 적음)를, "고순도 진성" 또는 "실질적으로 고순도 진성"이라고 지칭한다. 고순도 진성 또는 실질적으로 고순도 진성 산화물 반도체는, 적은 캐리어 발생원을 갖고, 따라서 낮은 캐리어 밀도를 갖게 되는 경우가 몇몇 있다. 따라서, 채널 영역이 형성된 산화물 반도체 막을 포함하는 트랜지스터는, 포지티브 임계 전압(노멀리 오프 특성)을 가질 가능성이 있다. 고순도 진성 또는 실질적으로 고순도 진성 산화물 반도체 막은, 낮은 결함 준위 밀도를 갖고, 따라서 낮은 트랩 상태 밀도를 갖게 되는 경우가 몇몇 있다. 또한, 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체 막은, 극도로 작은 오프 전류를 갖고; 상기 오프 전류는, 1V 내지 10V의 소스 전극과 드레인 전극 사이의 전압(드레인 전압)에서, 반도체 파라미터 애널라이저의 측정 한계 이하인, 즉 1×10-13A 이하일 수 있다. 따라서, 산화물 반도체 막에 채널 영역이 형성되는 트랜지스터는, 전기적 특성의 변동이 작고, 신뢰성이 높게 되는 경우가 몇몇 있다.

산화물 반도체 막(105 및 108)은 각각, 예를 들어, 비단결정 구조를 가질 수 있다. 비단결정 구조는, 예를 들어, 후술하는 c축 배향 결정 산화물 반도체(CAAC-OS: c-axis aligned crystalline oxide semiconductor), 다결정 구조, 후술하는 미세결정 구조, 또는 비정질 구조를 포함한다. 비단결정 구조 중에서, 비정질 구조는 결함 준위 밀도가 가장 높고, 반면에 CAAC-OS는 결함 준위 밀도가 가장 낮다.

산화물 반도체 막(105 및 108)은, 비정질 구조를 갖는 영역, 미세결정 구조를 갖는 영역, 다결정 구조를 갖는 영역, CAAC-OS 영역, 및 단결정 구조를 갖는 영역 중 2개 이상을 포함하는 혼합막일 수 있다는 점에 주목해야 한다. 혼합막은, 예를 들어 비정질 구조를 갖는 영역, 미세결정 구조를 갖는 영역, 다결정 구조를 갖는 영역, CAAC-OS 영역, 및 단결정 구조를 갖는 영역 중 2개 이상을 포함하는 단층 구조를 갖는 경우가 몇몇 있다. 또한, 혼합막은, 예를 들어 비정질 구조를 갖는 영역, 미세결정 구조를 갖는 영역, 다결정 구조를 갖는 영역, CAAC-OS 영역, 및 단결정 구조를 갖는 영역 중 2개 이상의 적층 구조를 갖는 경우가 몇몇 있다.

산화물 반도체 막(105)에서, 채널 영역(105a)과 저 저항 영역(105b 및 105c)은 상이한 결정성을 가질 수 있다는 점에 주목해야 한다. 산화물 반도체 막(108)에서, 채널 영역(108a)과 저 저항 영역(108b 및 108c)은 상이한 결정성을 가질 수 있다. 이들 경우는, 저 저항 영역(105b, 105c, 108b 및 108c)에 불순물 원소가 첨가될 때, 저 저항 영역(105b, 105c, 108b 및 108c)에 대한 손상이 그들의 결정성을 저하시키는 것이 원인이다.