KR20140117543A - 본딩 장치 및 반도체 장치의 제조 방법 - Google Patents

본딩 장치 및 반도체 장치의 제조 방법 Download PDFInfo

- Publication number

- KR20140117543A KR20140117543A KR1020147022686A KR20147022686A KR20140117543A KR 20140117543 A KR20140117543 A KR 20140117543A KR 1020147022686 A KR1020147022686 A KR 1020147022686A KR 20147022686 A KR20147022686 A KR 20147022686A KR 20140117543 A KR20140117543 A KR 20140117543A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- semiconductor chip

- bonding

- image

- penetrating electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B37/00—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding

- B32B37/0046—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding characterised by constructional aspects of the apparatus

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B41/00—Arrangements for controlling or monitoring lamination processes; Safety arrangements

-

- H10W20/20—

-

- H10W46/00—

-

- H10W90/00—

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B2309/00—Parameters for the laminating or treatment process; Apparatus details

- B32B2309/70—Automated, e.g. using a computer or microcomputer

- B32B2309/72—For measuring or regulating, e.g. systems with feedback loops

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B2313/00—Elements other than metals

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B2457/00—Electrical equipment

- B32B2457/14—Semiconductor wafers

-

- H10W46/301—

-

- H10W46/603—

-

- H10W72/07178—

-

- H10W72/07183—

-

- H10W72/07223—

-

- H10W72/07231—

-

- H10W72/07236—

-

- H10W72/07323—

-

- H10W72/252—

-

- H10W90/297—

-

- H10W90/722—

-

- H10W90/732—

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Wire Bonding (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Pressure Welding/Diffusion-Bonding (AREA)

Abstract

Description

도 2는 제1층의 반도체 칩 표면의 화상과, 제2층의 반도체 칩의 이면의 화상 및 각 층의 반도체 칩의 단면을 나타내는 설명도이다.

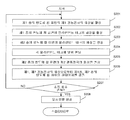

도 3은 본 발명의 실시형태에 있어서의 본딩 장치의 동작을 나타내는 플로우차트이다.

도 4는 본 발명의 실시형태에 있어서의 본딩 장치의 적층 본딩 동작을 나타내는 설명도이다.

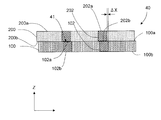

도 5는 티칭시에 적층 본딩에 의해 제1층의 반도체 칩과 제2층의 반도체 칩이 적층된 다층 반도체 장치의 평면과, 단면을 나타내는 설명도이다.

도 6은 본 발명의 본딩 장치에 있어서, 적층 본딩 후에 제2층의 반도체 칩 표면의 화상을 촬상하는 상태를 나타내는 설명도이다.

도 7은 다층 반도체 장치 제조시의 적층 본딩에 의해 제1층의 반도체 칩과 제2층의 반도체 칩이 적층된 다층 반도체 장치의 평면과, 단면을 나타내는 설명도이다.

도 8은 본 발명의 실시형태에 있어서의 본딩 장치의 다른 동작을 나타내는 플로우차트이다.

도 9는 본 발명의 실시형태에 있어서의 본딩 장치의 다른 동작을 나타내는 플로우차트이다.

도 10은 티칭시에 적층 본딩에 의해 제1층과 제2층의 반도체 칩이 적층된 다층 반도체 장치의 단면도이다.

도 11은 다층 반도체 장치 제조시의 적층 본딩에 의해 제1층과 제2층의 반도체 칩이 적층된 상태와, 제1층 내지 제3층의 반도체 칩이 적층된 상태를 나타내는 단면도이다.

12…XY 테이블

13…본딩 스테이지 구동 기구

14…본딩 툴

15…본딩 툴 구동 기구

16…2시야 카메라

20…제1층의 반도체 칩

20a, 22a, 30a, 32a…표면

20b, 22b, 30b, 32b…이면

21a, 31a, 31b…얼라인먼트 마크

22…제1 관통 전극

30…제2층의 반도체 칩

32…제2 관통 전극

40…다층 반도체 장치

41…고착층

50…제어부

51…CPU

52…메모리

53…상대 위치 검출 프로그램

54…제1 촬상 프로그램

55…제1 본딩 프로그램

56…제2 촬상 프로그램

57…오프셋량 설정 프로그램

58…제2 본딩 프로그램

59…제3 촬상 프로그램

60…어긋남량 검출 프로그램

61…오프셋량 보정 프로그램

62…정지 프로그램

63…제어 데이터

64…본딩 툴 구동 기구 인터페이스

65…2시야 카메라 인터페이스

66…본딩 스테이지 구동 기구 인터페이스

70…데이터 버스

100, 200, 300…반도체 칩

100a, 102a, 200a, 202a, 300a, 302a…표면

102, 202, 302…관통 전극

100b, 200b, 300b…이면

500…플립칩 본딩 장치

Claims (15)

- 본딩 장치로서,

반도체 칩의 화상을 촬상하는 카메라와,

상기 카메라가 촬상한 화상의 화상 처리와 제1 관통 전극이 설치되는 제1층의 상기 반도체 칩 위에 상기 제1 관통 전극에 대응하는 위치에 제2 관통 전극이 설치되는 제2층의 상기 반도체 칩을 적층 본딩하는 본딩 제어를 행하는 제어부를 포함하고,

상기 제어부는,

적층 본딩하기 전에 상기 카메라에 의해 촬상한 제1층의 반도체 칩 표면의 상기 제1 관통 전극의 화상과, 적층 본딩한 후에 상기 카메라에 의해 촬상한 제2층의 반도체 칩 표면의 상기 제2 관통 전극의 화상에 기초하여 적층 본딩된 상기 각 층의 반도체 칩의 상대 위치를 검출하는 상대 위치 검출 수단을 포함하는 것을 특징으로 하는 본딩 장치. - 제 1 항에 있어서,

상기 상대 위치는 상기 제1층의 반도체 칩 표면 상의 기준축을 따른 방향 또는 상기 기준축과 직교하는 방향의 상기 제2층의 반도체 칩의 위치 어긋남, 또는 상기 기준축에 대한 상기 제2층의 반도체 칩의 회전 각도의 어느 하나 또는 복수의 조합인 것을 특징으로 하는 본딩 장치. - 제 1 항에 있어서,

상기 제1층의 반도체 칩과 상기 제2층의 반도체 칩은 인접하는 2개의 층의 각 반도체 칩인 것을 특징으로 하는 본딩 장치. - 제 2 항에 있어서,

상기 제1층의 반도체 칩과 상기 제2층의 반도체 칩은 인접하는 2개의 층의 각 반도체 칩인 것을 특징으로 하는 본딩 장치. - 제 1 항에 있어서,

상기 제1층의 반도체 칩은 첫번째 층의 반도체 칩이며, 상기 제2층의 반도체 칩은 상기 첫번째 층의 반도체 칩의 상측에 적층 본딩된 다른 반도체 칩인 것을 특징으로 하는 본딩 장치. - 제 2 항에 있어서,

상기 제1층의 반도체 칩은 첫번째 층의 반도체 칩이며, 상기 제2층의 반도체 칩은 상기 첫번째 층의 반도체 칩의 상측에 적층 본딩된 다른 반도체 칩인 것을 특징으로 하는 본딩 장치. - 제 1 항에 있어서,

상기 제어부는,

적층 본딩하기 전에 상기 카메라에 의해 제1층의 반도체 칩 표면의 상기 제1 관통 전극의 화상을 촬상하는 제1 촬상 수단과,

적층 본딩하기 전에 상기 카메라에 의해 촬상한 제1층의 반도체 칩 표면의 제1 얼라인먼트 마크와 적층 본딩하기 전에 상기 카메라에 의해 촬상한 제2층의 반도체 칩 이면의 제2 얼라인먼트 마크의 위치를 맞추어 상기 제2층의 반도체 칩을 상기 제1층의 반도체 칩 위에 적층 본딩하는 제1 본딩 수단과,

상기 제1 본딩 수단에 의해 적층 본딩한 후에 상기 카메라에 의해 제2층의 반도체 칩 표면의 상기 제2 관통 전극의 화상을 촬상하는 제2 촬상 수단과,

상기 제1 촬상 수단에 의해 촬상한 상기 제1 관통 전극의 화상과 상기 제2 촬상 수단에 의해 촬상한 상기 제2 관통 전극의 화상에 기초하여 상기 각 층의 반도체 칩의 상대 위치를 검출하고, 검출한 상대 위치를 적층 본딩시의 오프셋량으로서 설정하는 오프셋량 설정 수단

을 포함하는 것을 특징으로 하는 본딩 장치. - 제 7 항에 있어서,

상기 제어부는,

상기 제1 얼라인먼트 마크에 상기 제2 얼라인먼트 마크가 맞는 위치로부터 상기 오프셋량 설정 수단으로 설정한 오프셋량만큼 상기 제2층의 반도체 칩을 옮겨 상기 제1층의 반도체 칩 위에 적층 본딩하는 제2 본딩 수단과,

상기 제2 본딩 수단에 의해 적층 본딩한 후에 상기 카메라에 의해 제2층의 반도체 칩 표면의 상기 제2 관통 전극의 화상을 촬상하는 제3 촬상 수단과,

상기 제1 촬상 수단에 의해 촬상한 상기 제1 관통 전극의 화상과 상기 제3 촬상 수단에 의해 촬상한 상기 제2 관통 전극의 화상에 기초하여 상기 각 층의 반도체 칩의 상대 위치의 어긋남량을 검출하는 어긋남량 검출 수단

을 포함하는 것을 특징으로 하는 본딩 장치. - 제 8 항에 있어서,

상기 제어부는,

상기 어긋남량 검출 수단으로 검출한 어긋남량이 제1 역치 미만이며, 제2 역치 이상인 경우에는, 상기 어긋남량의 소정 비율만큼 상기 오프셋량을 보정하는 오프셋량 보정 수단을 포함하는 것을 특징으로 하는 본딩 장치. - 반도체 장치의 제조 방법으로서,

제1 관통 전극이 설치되는 제1층의 반도체 칩 위에 상기 제1 관통 전극에 대응하는 위치에 제2 관통 전극이 설치되는 제2층의 반도체 칩을 적층 본딩하는 본딩 장치를 준비하는 공정과,

적층 본딩하기 전에 카메라에 의해 제1층의 반도체 칩 표면의 상기 제1 관통 전극의 화상을 촬상하는 제1 촬상 공정과,

적층 본딩하기 전에 상기 카메라에 의해 촬상한 제1층의 반도체 칩 표면의 제1 얼라인먼트 마크와 적층 본딩하기 전에 상기 카메라에 의해 촬상한 제2층의 반도체 칩 이면의 제2 얼라인먼트 마크의 위치를 맞추어 상기 제2층의 반도체 칩을 상기 제1층의 반도체 칩 위에 적층 본딩하는 제1 본딩 공정과,

상기 제1 본딩 공정 후에 상기 카메라에 의해 제2층의 반도체 칩 표면의 상기 제2 관통 전극의 화상을 촬상하는 제2 촬상 공정과,

상기 제1 관통 전극의 화상과 상기 제2 관통 전극의 화상에 기초하여 상기 각 층의 반도체 칩의 상대 위치를 검출하고, 검출한 상대 위치를 적층 본딩시의 오프셋량으로서 설정하는 오프셋량 설정 공정

을 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법. - 제 10 항에 있어서,

상기 제1 얼라인먼트 마크에 상기 제2 얼라인먼트 마크가 맞는 위치로부터 상기 오프셋량만큼 상기 제2층의 반도체 칩을 옮겨 상기 제1층의 반도체 칩 위에 적층 본딩하는 제2 본딩 공정과,

상기 제2 본딩 공정 후에 상기 카메라에 의해 제2층의 반도체 칩 표면의 상기 제2 관통 전극의 화상을 촬상하는 제3 촬상 공정과,

상기 제1 촬상 수단에 의해 촬상한 상기 제1 관통 전극의 화상과 상기 제3 촬상 수단에 의해 촬상한 상기 제2 관통 전극의 화상에 기초하여 상기 각 층의 반도체 칩의 상대 위치의 어긋남량을 검출하는 어긋남량 검출 공정

을 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법. - 제 10 항에 있어서,

상기 제1층의 반도체 칩과 상기 제2층의 반도체 칩은 인접하는 2개의 층의 각 반도체 칩인 것을 특징으로 하는 반도체 장치의 제조 방법. - 제 11 항에 있어서,

상기 제1층의 반도체 칩과 상기 제2층의 반도체 칩은 인접하는 2개의 층의 각 반도체 칩인 것을 특징으로 하는 반도체 장치의 제조 방법. - 제 10 항에 있어서,

상기 제1층의 반도체 칩은 첫번째 층의 반도체 칩이며, 상기 제2층의 반도체 칩은 상기 첫번째 층의 반도체 칩의 상측에 적층 본딩된 다른 반도체 칩인 것을 특징으로 하는 반도체 장치의 제조 방법. - 제 11 항에 있어서,

상기 제1층의 반도체 칩은 첫번째 층의 반도체 칩이며, 상기 제2층의 반도체 칩은 상기 첫번째 층의 반도체 칩의 상측에 적층 본딩된 다른 반도체 칩인 것을 특징으로 하는 반도체 장치의 제조 방법.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2012-131510 | 2012-06-11 | ||

| JP2012131510 | 2012-06-11 | ||

| JPJP-P-2013-061589 | 2013-03-25 | ||

| JP2013061589A JP5876000B2 (ja) | 2012-06-11 | 2013-03-25 | ボンディング装置およびボンディング方法 |

| PCT/JP2013/065575 WO2013187292A1 (ja) | 2012-06-11 | 2013-06-05 | ボンディング装置および半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20140117543A true KR20140117543A (ko) | 2014-10-07 |

| KR101630249B1 KR101630249B1 (ko) | 2016-06-14 |

Family

ID=49758118

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147022686A Active KR101630249B1 (ko) | 2012-06-11 | 2013-06-05 | 본딩 장치 및 반도체 장치의 제조 방법 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US9385104B2 (ko) |

| JP (1) | JP5876000B2 (ko) |

| KR (1) | KR101630249B1 (ko) |

| CN (1) | CN104335337B (ko) |

| SG (1) | SG11201408122RA (ko) |

| TW (1) | TWI511215B (ko) |

| WO (1) | WO2013187292A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20210064601A (ko) * | 2019-11-26 | 2021-06-03 | 세메스 주식회사 | 다이 본딩 방법 |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6454283B2 (ja) * | 2013-11-27 | 2019-01-16 | 東レエンジニアリング株式会社 | 3次元実装方法および3次元実装装置 |

| TWI567859B (zh) * | 2014-02-10 | 2017-01-21 | 新川股份有限公司 | 安裝裝置及其偏移量修正方法 |

| JP6363854B2 (ja) * | 2014-03-11 | 2018-07-25 | キヤノン株式会社 | 形成方法、および物品の製造方法 |

| JP6305887B2 (ja) * | 2014-09-16 | 2018-04-04 | 東芝メモリ株式会社 | 半導体装置の製造方法及び半導体製造装置 |

| TWI721960B (zh) * | 2014-12-18 | 2021-03-21 | 日商新力股份有限公司 | 半導體裝置、製造方法及電子機器 |

| US10014272B2 (en) * | 2015-05-11 | 2018-07-03 | Asm Technology Singapore Pte Ltd | Die bonding with liquid phase solder |

| JP6478939B2 (ja) * | 2016-03-31 | 2019-03-06 | 東レエンジニアリング株式会社 | 実装装置および実装方法 |

| JP6731577B2 (ja) * | 2016-06-23 | 2020-07-29 | パナソニックIpマネジメント株式会社 | 部品実装方法および部品実装装置 |

| CN106409724B (zh) * | 2016-09-30 | 2019-05-21 | 西安微电子技术研究所 | 一种PoP自动堆叠系统及方法 |

| US10410892B2 (en) * | 2016-11-18 | 2019-09-10 | Taiwan Semiconductor Manufacturing Company Ltd. | Method of semiconductor wafer bonding and system thereof |

| US12261070B2 (en) * | 2018-08-31 | 2025-03-25 | Bondtech Co., Ltd. | Component mounting system and component mounting method |

| CN109643700B (zh) | 2018-11-21 | 2019-09-10 | 长江存储科技有限责任公司 | 用于接合界面处的接合对准标记的方法、器件和结构 |

| KR102759370B1 (ko) | 2020-01-06 | 2025-01-24 | 삼성전자주식회사 | 반도체 패키지 및 그의 제조 방법 |

| DE102020126211A1 (de) | 2020-05-28 | 2021-12-02 | Taiwan Semiconductor Manufacturing Co. Ltd. | Photolithographie-Ausrichtungsprozess für gebondete Wafer |

| US11362038B2 (en) * | 2020-05-28 | 2022-06-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Photolithography alignment process for bonded wafers |

| TWI756881B (zh) * | 2020-10-27 | 2022-03-01 | 均華精密工業股份有限公司 | 黏晶機之定位系統、黏晶機之定位裝置以及黏晶機置放晶粒方法 |

| CN114981936B (zh) * | 2020-12-21 | 2025-09-12 | 株式会社新川 | 接合装置及接合方法 |

| JP2023087200A (ja) | 2021-12-13 | 2023-06-23 | 三星電子株式会社 | 実装装置及び実装方法 |

| JP2024017814A (ja) * | 2022-07-28 | 2024-02-08 | キヤノン株式会社 | 接合装置、接合方法、および物品の製造方法 |

| JP2024080318A (ja) | 2022-12-02 | 2024-06-13 | 三星電子株式会社 | 実装装置及び実装方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002110742A (ja) | 2000-10-02 | 2002-04-12 | Hitachi Ltd | 半導体装置の製造方法および半導体製造装置 |

| JP2009253185A (ja) * | 2008-04-10 | 2009-10-29 | Shinkawa Ltd | ボンディング装置およびボンディング装置に用いられるボンディング領域の位置認識方法及びプログラム |

| JP2010272707A (ja) * | 2009-05-22 | 2010-12-02 | Panasonic Corp | アライメント接合方法 |

| JP4642565B2 (ja) | 2005-06-29 | 2011-03-02 | 東レエンジニアリング株式会社 | 実装方法および実装装置 |

| JP2011124523A (ja) * | 2010-02-02 | 2011-06-23 | Napura:Kk | 電子デバイス用基板、電子デバイス用積層体、電子デバイス及びそれらの製造方法 |

| WO2011087003A1 (ja) * | 2010-01-15 | 2011-07-21 | 東レエンジニアリング株式会社 | 3次元実装方法および装置 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4899921A (en) * | 1988-10-28 | 1990-02-13 | The American Optical Corporation | Aligner bonder |

| US5654204A (en) * | 1994-07-20 | 1997-08-05 | Anderson; James C. | Die sorter |

| JP3530517B2 (ja) * | 2001-12-28 | 2004-05-24 | 日本アビオニクス株式会社 | アライメント補正機能付きフリップチップ実装装置 |

| JP2004146776A (ja) * | 2002-08-29 | 2004-05-20 | Shinko Electric Ind Co Ltd | フリップチップ実装装置及びフリップチップ実装方法 |

| JP4074862B2 (ja) * | 2004-03-24 | 2008-04-16 | ローム株式会社 | 半導体装置の製造方法、半導体装置、および半導体チップ |

| JP2006041006A (ja) * | 2004-07-23 | 2006-02-09 | Matsushita Electric Ind Co Ltd | 半導体チップのボンディング方法及び装置 |

| TW200628029A (en) * | 2004-12-06 | 2006-08-01 | Matsushita Electric Industrial Co Ltd | Component mounting apparatus and component mounting method |

| JP5024369B2 (ja) * | 2007-03-28 | 2012-09-12 | 富士通株式会社 | 超音波接合装置 |

| JP5259211B2 (ja) * | 2008-02-14 | 2013-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5503208B2 (ja) * | 2009-07-24 | 2014-05-28 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8987896B2 (en) * | 2009-12-16 | 2015-03-24 | Intel Corporation | High-density inter-package connections for ultra-thin package-on-package structures, and processes of forming same |

| JP5515024B2 (ja) * | 2010-11-24 | 2014-06-11 | 株式会社日本マイクロニクス | チップ積層デバイス検査方法及びチップ積層デバイス再配列ユニット並びにチップ積層デバイス用検査装置 |

| JP2012222161A (ja) * | 2011-04-08 | 2012-11-12 | Elpida Memory Inc | 半導体装置 |

| US8710654B2 (en) * | 2011-05-26 | 2014-04-29 | Kabushiki Kaisha Toshiba | Semiconductor device and manufacturing method thereof |

| JP2013065835A (ja) * | 2011-08-24 | 2013-04-11 | Sumitomo Bakelite Co Ltd | 半導体装置の製造方法、ブロック積層体及び逐次積層体 |

| WO2013069798A1 (ja) * | 2011-11-11 | 2013-05-16 | 住友ベークライト株式会社 | 半導体装置の製造方法 |

| SG11201405431TA (en) * | 2012-03-07 | 2014-10-30 | Toray Industries | Method and apparatus for manufacturing semiconductor device |

| JP6207190B2 (ja) * | 2013-03-22 | 2017-10-04 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2014187185A (ja) * | 2013-03-22 | 2014-10-02 | Renesas Electronics Corp | 半導体装置の製造方法 |

| US9093549B2 (en) * | 2013-07-02 | 2015-07-28 | Kulicke And Soffa Industries, Inc. | Bond heads for thermocompression bonders, thermocompression bonders, and methods of operating the same |

| JP6189181B2 (ja) * | 2013-11-06 | 2017-08-30 | 東芝メモリ株式会社 | 半導体装置の製造方法 |

-

2013

- 2013-03-25 JP JP2013061589A patent/JP5876000B2/ja active Active

- 2013-06-05 CN CN201380027777.0A patent/CN104335337B/zh active Active

- 2013-06-05 WO PCT/JP2013/065575 patent/WO2013187292A1/ja not_active Ceased

- 2013-06-05 KR KR1020147022686A patent/KR101630249B1/ko active Active

- 2013-06-05 SG SG11201408122RA patent/SG11201408122RA/en unknown

- 2013-06-11 TW TW102120660A patent/TWI511215B/zh active

-

2014

- 2014-12-05 US US14/561,572 patent/US9385104B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002110742A (ja) | 2000-10-02 | 2002-04-12 | Hitachi Ltd | 半導体装置の製造方法および半導体製造装置 |

| JP4642565B2 (ja) | 2005-06-29 | 2011-03-02 | 東レエンジニアリング株式会社 | 実装方法および実装装置 |

| JP2009253185A (ja) * | 2008-04-10 | 2009-10-29 | Shinkawa Ltd | ボンディング装置およびボンディング装置に用いられるボンディング領域の位置認識方法及びプログラム |

| JP2010272707A (ja) * | 2009-05-22 | 2010-12-02 | Panasonic Corp | アライメント接合方法 |

| WO2011087003A1 (ja) * | 2010-01-15 | 2011-07-21 | 東レエンジニアリング株式会社 | 3次元実装方法および装置 |

| JP2011124523A (ja) * | 2010-02-02 | 2011-06-23 | Napura:Kk | 電子デバイス用基板、電子デバイス用積層体、電子デバイス及びそれらの製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20210064601A (ko) * | 2019-11-26 | 2021-06-03 | 세메스 주식회사 | 다이 본딩 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5876000B2 (ja) | 2016-03-02 |

| SG11201408122RA (en) | 2015-01-29 |

| US9385104B2 (en) | 2016-07-05 |

| TWI511215B (zh) | 2015-12-01 |

| CN104335337B (zh) | 2017-05-10 |

| KR101630249B1 (ko) | 2016-06-14 |

| TW201413843A (zh) | 2014-04-01 |

| JP2014017471A (ja) | 2014-01-30 |

| CN104335337A (zh) | 2015-02-04 |

| US20150087083A1 (en) | 2015-03-26 |

| WO2013187292A1 (ja) | 2013-12-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101630249B1 (ko) | 본딩 장치 및 반도체 장치의 제조 방법 | |

| TWI593046B (zh) | Bonding device and bonding method | |

| TWI603424B (zh) | Plate with alignment mark | |

| KR102207674B1 (ko) | 3차원 실장 방법 및 3차원 실장 장치 | |

| JP2009071069A (ja) | 接合材貼付検査装置、実装装置、電気部品の製造方法 | |

| US10383231B2 (en) | Component-embedded board and method of manufacturing same | |

| TWI846064B (zh) | 半導體結構及其製造方法 | |

| WO2006118018A1 (ja) | フリップチップ実装ずれ検査方法および実装装置 | |

| KR20170121464A (ko) | 기판 상의 결함을 검사하는 방법 및 장치 | |

| JP2004146776A (ja) | フリップチップ実装装置及びフリップチップ実装方法 | |

| KR102354344B1 (ko) | 반도체 소자 접착 기기 | |

| JP4829813B2 (ja) | 電子部品の実装装置及び実装方法 | |

| JP5157364B2 (ja) | 接合対象物のアライメント方法、これを用いた部品接合方法および部品接合装置 | |

| JP2012243987A (ja) | 半導体装置の製造方法 | |

| JP2013197278A (ja) | 半導体製造装置 | |

| JP6167412B2 (ja) | 積層パッケージの製造システムおよび製造方法 | |

| KR102085886B1 (ko) | Fpcb 가접 장치 및 그 제어 방법 | |

| KR20250163772A (ko) | 다이 본딩 장치 및 이를 이용한 다이 본딩 방법 | |

| JP4660178B2 (ja) | 電子部品の実装装置 | |

| KR101507145B1 (ko) | 위치인식홀을 이용한 실리콘관통전극 플립칩 얼라인먼트 검사 장치 및 방법 | |

| KR20220022682A (ko) | 실리콘 관통 전극 반도체 칩 얼라인먼트 방법 | |

| JP2002314249A (ja) | 多層基板の製造方法 | |

| WO2018198196A1 (ja) | 検査装置、搭載装置、検査方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0105 | International application |

St.27 status event code: A-0-1-A10-A15-nap-PA0105 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U12-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| R11 | Change to the name of applicant or owner or transfer of ownership requested |

Free format text: ST27 STATUS EVENT CODE: A-5-5-R10-R11-ASN-PN2301 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| R13 | Change to the name of applicant or owner recorded |

Free format text: ST27 STATUS EVENT CODE: A-5-5-R10-R13-ASN-PN2301 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| R11 | Change to the name of applicant or owner or transfer of ownership requested |

Free format text: ST27 STATUS EVENT CODE: A-5-5-R10-R11-ASN-PN2301 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R14-asn-PN2301 |

|

| R14 | Transfer of ownership recorded |

Free format text: ST27 STATUS EVENT CODE: A-5-5-R10-R14-ASN-PN2301 (AS PROVIDED BY THE NATIONAL OFFICE) |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |