KR20140105584A - 마이크로 컴퓨터 및 그 동작 방법 - Google Patents

마이크로 컴퓨터 및 그 동작 방법 Download PDFInfo

- Publication number

- KR20140105584A KR20140105584A KR1020147019919A KR20147019919A KR20140105584A KR 20140105584 A KR20140105584 A KR 20140105584A KR 1020147019919 A KR1020147019919 A KR 1020147019919A KR 20147019919 A KR20147019919 A KR 20147019919A KR 20140105584 A KR20140105584 A KR 20140105584A

- Authority

- KR

- South Korea

- Prior art keywords

- cpu

- reset

- reset signal

- signal

- register

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0703—Error or fault processing not based on redundancy, i.e. by taking additional measures to deal with the error or fault not making use of redundancy in operation, in hardware, or in data representation

- G06F11/0793—Remedial or corrective actions

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/24—Resetting means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/24—Handling requests for interconnection or transfer for access to input/output bus using interrupt

Abstract

마이크로 컴퓨터의 CPU가, 외부의 노이즈, 전원 전압의 불안정, 다른 원인으로 그 프로그램의 실행이 불능이 되어, 이른바 폭주등의 치명적 에러를 일으켜도, 지극히 단시간으로 견딜 수 있을 수 있도록 시스템 전체의 초기화를 하지 않고 원 상태로 복귀하는 것을 목적으로 한다.

통상의 소프트웨어 처리의 실행중에, 인터럽트 신호와 리셋 신호를 임의의 타이밍에 출력하고 마이크로 컴퓨터의 CPU가 폭주 상태가 되었다고 판정했을 때는, 복귀 정보로서 RAM에 저장된 데이터를 읽어내고, CPU를 폭주전 상태로 복귀시킨다.

이에 의해 실행중의 소프트웨어는 단시간에 치명적 에러로부터 복귀하기 때문에, 마치 치명적 에러가 발생하고 있지 않는 것처럼 소프트웨어 처리를 계속할 수 있다.

통상의 소프트웨어 처리의 실행중에, 인터럽트 신호와 리셋 신호를 임의의 타이밍에 출력하고 마이크로 컴퓨터의 CPU가 폭주 상태가 되었다고 판정했을 때는, 복귀 정보로서 RAM에 저장된 데이터를 읽어내고, CPU를 폭주전 상태로 복귀시킨다.

이에 의해 실행중의 소프트웨어는 단시간에 치명적 에러로부터 복귀하기 때문에, 마치 치명적 에러가 발생하고 있지 않는 것처럼 소프트웨어 처리를 계속할 수 있다.

Description

본 발명은 마이크로 컴퓨터의 동작 방법에 관한 것이다. 보다 상세하게는 마이크로 컴퓨터의 중앙 처리장치(CPU)에 있어서, 이른바 폭주 등의 에러가 발생했을 경우에, CPU를 자동적으로 복귀시키는 회로와 그 사용 방법에 관한 것이다.

마이크로 컴퓨터의 CPU에 있어서, 외부의 전기적인 노이즈, 정전기, 전원 전압의 불안정 및 그 외의 원인으로 치명적인 에러가 발생한다. 이것에 의해, 그 CPU가 프로그램을 실행하지 못하는 경우가 있다. 그러한 치명적인 에러 상태의 예로서는, 이른바 CPU의 폭주 등을 들 수 있다. 이 마이크로 컴퓨터의 CPU의 치명적인 에러에 대한 대책으로서는, 워치 독(watch dog)으로써 알려진 방법이 일반적이다. 이 방법은 소프트웨어의 처리의 반복(루프) 시간보다 충분히 긴 타이머를 마련해 소프트웨어 처리의 루프에 있어서 이 타이머를 리셋한다. CPU에 치명적인 에러가 발생했을 경우, 소프트웨어 처리가 정상적으로 동작하지 않기 때문에 타이머는 리셋되지 않고 종료하고, 타이머의 종료를 트리거로서 마이크로 컴퓨터 전체적으로 리셋이 주어진다. 한편, CPU가 정상적으로 동작하고 있는 경우(치명적인 에러가 발생하고 있지 않는 경우), 타이머는 종료하기 전에 리셋 되므로, 마이크로 컴퓨터는 리셋되지 않는다.

그러나 이 방법에서는 CPU의 치명적인 에러 상태가 타이머의 시작부터 종료까지의 오랫동안 계속할 가능성이 있다. 따라서, CPU의 치명적인 에러 발생으로부터 타이머가 종료할 때까지의 시간이 마이크로 컴퓨터의 사용에 악영향을 미치는 환경이나, 그 시간중의 마이크로 컴퓨터의 오동작에 의해서 사용자에 위험이 미치는 환경에서는 워치 독은 반드시 유효하지 않지만 그 밖에 수단이 없어 채용되고 있다.

게다가, 워치 독을 이용한 CPU의 치명적인 에러의 대책에서는, CPU에 있어서 치명적인 에러가 발생한 후, 그 CPU 상태를 그러한 에러가 발생하기 직전 상태에 되돌리는 것은 곤란하다. 그 이유는, CPU의 치명적인 에러가 검출되기까지 시간이 걸리기 때문에, CPU의 치명적인 에러가 검출된 시점의 CPU 레지스터의 정보 등의 상태가 치명적인 에러가 발생한 직전 상태와는 다르기 때문이다.

종래, 마이크로 컴퓨터는 CPU의 치명적인 에러를 검출하면, CPU의 치명적인 에러를 검출한 시점의 CPU 레지스터의 정보 등을 파기하고, 마이크로 컴퓨터 전체를 초기화하고 있었다. 따라서, 종래 CPU를 치명적인 에러로부터 복귀시키기 위해서는 그 CPU의 치명적인 에러를 검출하기 위한 시간에 더해서 마이크로 컴퓨터 전체를 초기화하기 위한 시간이 필요했었다. 그리고 마이크로 컴퓨터를 CPU에서 치명적인 에러가 발생하기 전의 상태로 되돌리기 위해서, 그 에러가 발생하기 전의 실행중의 처리(응용 프로그램(애플리케이션 프로그램)의 처리)를 CPU의 초기화 후에 재현해야 한다. 실행중이었던 처리를 재현하는 것은 용이하지 않고, 게다가 그 재현을 실행하기 위한 처리 시간이 필요하다. 따라서, 마이크로 컴퓨터를 사용하고 있는 환경에 의해서, CPU의 치명적인 에러로부터 마이크로 컴퓨터를 복귀시키는 것은 큰 문제가 될 가능성이 있다. 예를 들면, CPU의 치명적인 에러로부터 초기화까지의 시간에 기계를 정지하지 못하고 사고가 일어날 수 있다. 또, 금전의 계산이 없어지는 등의 심각한 사태도 일어날 수 있다.

일반적으로, 마이크로 컴퓨터를 이용한 원칩(one-chip) 마이크로컴퓨터에는 초기화를 위한 신호는 1개 밖에 이용되지 않고 있다. 이 때문에, 초기화는 마이크로 컴퓨터 전체에 대하여 행해진다. 따라서, 마이크로 컴퓨터의 초기화는 전체를 초기화하는데 상당한 중대한 에러의 경우에 실시하는 것이 상정되고 있다. 따라서, CPU의 치명적인 에러로부터의 복귀에 시간이 걸리는 것이나, 그 치명적인 에러가 발생할 때까지의 정보 등이 상실되는 것은 종래, 어쩔 수 없다고 생각되고 있었다.

게다가 다른 방법으로서는, 특허문헌 1에 기재되어 있는 것처럼, 주기적인 인터럽트 대신에 리셋을 주기적으로 CPU에만 주는 방법도 있다. 이 방법을 이용했을 경우, CPU상에서 실행되는 응용 프로그램의 실행 시작부터 종료까지의 시간은 리셋의 주기내가 아니면 안된다. 왜냐하면, 응용 프로그램의 실행중에 CPU가 리셋되었을 경우, 프로그램 카운터나 스택등의 CPU 레지스터의 정보도 리셋되어 응용 프로그램중의 명령에 대한 어드레스가 소거되기 때문이다. 따라서, CPU만을 주기적으로 리셋하는 경우, 응용 프로그램은 처리 시작부터 종료까지의 시간이 CPU의 리셋의 주기의 간격내에 들어가는 지극히 작은 사이즈로 할 필요가 있다. 그 때문에, 일반적인 프로그램에 비해, 필요한 응용 프로그램의 사이즈는 작아진다. 이것에 의해, 그 응용 프로그램의 수는 방대한 수가 된다. 또, 응용 프로그램의 작성자는 응용 프로그램의 처리 내용 뿐만 아니고, 리셋의 주기를 의식해 응용 프로그램의 작성을 실시하지 않으면 안 된다고 하는 문제가 있다.

본 발명은 마이크로 컴퓨터의 CPU에서 치명적인 에러가 발생했을 경우, 마이크로 컴퓨터 전체의 초기화 또는 리셋을 실시하는 일 없이 CPU만을 리셋함으로써, 마이크로 컴퓨터의 CPU를 치명적인 에러 상태로부터 지극히 단시간에 복귀시키는 것을 목적으로 한다. 또, 본 발명은 마이크로 컴퓨터상에서 실행중의 응용 프로그램에 영향을 주는 일 없이 CPU를 리셋하는 것을 목적으로 한다.

본 발명에 의한 마이크로 컴퓨터는 CPU와 상기 CPU와 CPU 버스를 통하여 접속된 RAM와 인터럽트 처리의 실행 시작을 요구하기 위한 인터럽트 요구 신호를 CPU에 출력하는 인터럽트 요구 신호 출력 수단과, 상기 인터럽트 요구 신호 출력 수단이 인터럽트 요구 신호를 출력한 후, CPU 리셋 처리의 시작을 요구하기 위한 CPU 리셋 신호를 CPU로 출력하는 CPU 리셋 신호 출력 수단을 구비하고, CPU는 인터럽트 요구 신호를 수신하면, 상기 CPU상에서 실행되고 있는 응용 프로그램의 처리를 중단하는 것과 동시에, CPU 레지스터의 정보를 복귀 정보로서 RAM에 저장하고, 게다가 CPU 리셋 신호를 수신하면, CPU는 리셋되는 것과 동시에, RAM에 저장되고 있는 복귀 정보를 CPU 레지스터에 복사할 수 있다.

본 발명에 의한 마이크로 컴퓨터는 CPU 리셋 신호 및 인터럽트 요구 신호를 주기적으로 발생시키는 타이머 카운터 회로를 더 구비할 수 있다.

본 발명에 의한 마이크로 컴퓨터에 있어서, 타이머 카운터 회로는 부가 타이머를 구비하고 CPU는 CPU 레지스터의 정보가 정상인지를 판정하고, 상기 CPU 레지스터의 정보가 정상이라고 판정되었을 경우에만, 부가 타이머는 CPU 리셋 신호가 CPU로 공급되는 동안 작동하고, CPU 리셋 처리의 실행을 금지할 수 있다.

본 발명에 의한 마이크로 컴퓨터는 마이크로 컴퓨터 전체를 리셋하기 위한 시스템 리셋 신호원과 논리합 회로를 더 구비하고, CPU 신호 출력 수단 및 시스템 리셋 신호원은 논리합 회로의 입력측에 접속되어, CPU는 논리합 회로의 출력측에 접속되도록 구성할 수 있다.

본 발명에 의한 마이크로 컴퓨터의 동작 방법은 인터럽트 처리의 실행 시작을 요구하기 위한 인터럽트 요구 신호를 타이머 카운터 회로로부터 CPU로 출력하는 단계와, 상기 CPU에 의해서, 인터럽트 요구 신호를 수신하고 CPU상에서 실행되고 있는 응용 프로그램의 처리를 중단하는 단계와, CPU에 의해서 상기 CPU 레지스터의 정보를 복귀 정보로서 RAM에 저장하는 단계와, 인터럽트 요구 신호가 출력된 후 CPU 리셋 처리의 시작을 요구하기 위한 CPU 리셋 신호를 CPU로 출력하는 단계와, CPU에 있어서, CPU 리셋 신호를 수신하고 CPU를 리셋하는 단계와, 그 CPU에 의해서 RAM에 저장된 복귀 정보를 CPU 레지스터로 복사하는 단계를 포함하도록 할 수 있다.

본 발명에 의한 마이크로 컴퓨터의 동작 방법은 CPU 리셋 신호 및 인터럽트 요구 신호를 타이머 카운터 회로에 의해서 주기적으로 발생시킬 수 있다.

본 발명에 의한 마이크로 컴퓨터의 동작 방법은, CPU에 의해서, CPU 레지스터의 정보가 정상인지를 판정하고, CPU 레지스터의 정보가 정상이라고 판정되었을 경우에만, CPU 리셋 신호가 CPU에 공급되는 동안, CPU를 리셋하는 단계의 실행을 금지하는 단계를 더 포함하도록 할 수 있다.

마이크로 컴퓨터의 CPU에서 치명적인 에러가 발생하고 있는 것을 조기에 검출하고 치명적인 에러로부터의 복귀를 가능하게 함으로써, 마이크로 컴퓨터를 이용한 응용 장치가 비정상적인 동작, 때로는 위험하기도 한 오동작을 대폭으로 줄일 수 있다.

특히, 자동차, 비행기, 선박, 산업용 로봇 등의 분야에서 이용되는 기계 시스템을 제어하는 기기에 있어서, 그것들 기기의 오동작은 대사고로 연결될 우려가 있다(예를 들면, 자동차의 브레이크 제어나 스티어링 제어 등). 본 발명에 의한 마이크로 컴퓨터의 CPU의 치명적인 에러로부터의 복귀에 필요한 시간은 기계 시스템을 제어하는 기기에 있어서의 오동작의 검출 및 그 오동작으로부터의 복귀에 필요한 시간과 비교해서 훨씬 짧다. 따라서, 마이크로 컴퓨터의 CPU의 치명적인 에러에 기인하는 이들 기기의 오동작의 검출 및 그 오동작으로부터 복귀시키기 위한 처리를 기기가 아니고 마이크로 컴퓨터로 실시하는 것은 유용하다.

또, 상기 분야에 있어서, 전기적인 노이즈 등이 치명적인 에러를 일으키게 하는 원인은 다른 분야의 기기와 비교해서 보다 많이 발생한다. 따라서, 기계 시스템을 제어하는 기기에 본 발명을 이용하는 것에 의해서, 전기적인 노이즈 등을 위한 종전의 많은 대책을 대폭으로 경감할 수 있고, 게다가 종전보다 강고한 대책을 실시할 수 있기 위해, 비용 저하와 신뢰성의 향상을 아울러 도모할 수 있다. 또, 마이크로 컴퓨터의 CPU에 있어서 치명적인 에러가 계속적으로 발생하고 있는 경우, 계속적인 CPU의 치명적인 에러를 검출하고, 그 검출 결과에 근거하여, 기기의 오동작을 경고하기 위한 정보를 입출력 인터페이스를 통하여 제공할 수도 있다.

또한, 본 발명은 마이크로 컴퓨터의 CPU에서 치명적인 에러가 발생했을 경우, 마이크로 컴퓨터 전체를 리셋하는 것이 아니라, CPU만을 리셋함으로써, 치명적인 에러로부터의 복귀를 지극히 짧은 시간에 실시할 수 있다. 또, 본 발명은 CPU에서 치명적인 에러가 발생했을 때에 실행되고 있던 응용 프로그램을 중단한 후, CPU를 리셋하고, 그 치명적인 에러가 발생하기 전의 시점으로부터 응용 프로그램의 실행을 재개할 수 있다.

본 발명의 활용이 기대되는 분야에 있어서의 일례를 들면, 엘리베이터가 동작중에, 낙뢰, 전원의 노이즈, 설계상의 불비에 의한 노이즈에 의해서, 엘리베이터의 제어를 실시하는 마이크로 컴퓨터의 CPU에 치명적인 에러가 발생하고, 그 CPU에 의해서 엘리베이터가 오동작했을 경우라도, 엘리베이터의 마이크로 컴퓨터에 본 발명에 따른 마이크로 컴퓨터를 채용함으로써, 엘리베이터를 안정된 상태의 동작으로 지극히 짧은 시간에 복귀시킬 수 있다.

도 1은 본 발명의 일실시예에 따른 마이크로 컴퓨터의 전체를 도시한 블럭도이다.

도 2는 도 1의 클록 발생 회로, 타이머 카운터 회로 및 CPU를 보다 상세하게 도시한 블럭도이다.

도 3은 제1의 실시예에 의한 마이크로 컴퓨터의 동작을 도시한 플로우 차트이다.

도 4는 제2의 실시예에 의한 마이크로 컴퓨터의 동작을 도시한 플로우 차트이다.

도 5는 인터럽트 처리의 동작을 도시한 플로우 차트이다.

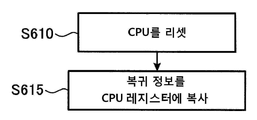

도 6은 CPU 리셋 처리의 동작을 도시한 플로우 차트이다.

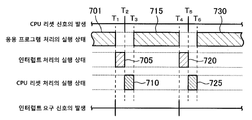

도 7은 CPU가 정상적으로 동작하고 있는 경우의 제1의 실시예에 대한 타임 차트이다.

도 8은 CPU에 있어서 치명적인 에러가 발생했을 경우의 제1의 실시예에 대한 타임 차트이다.

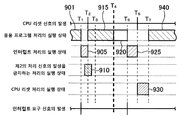

도 9는 CPU에 있어서 치명적인 에러가 발생했을 경우의 제2의 실시예에 대한 타임 차트이다.

도 2는 도 1의 클록 발생 회로, 타이머 카운터 회로 및 CPU를 보다 상세하게 도시한 블럭도이다.

도 3은 제1의 실시예에 의한 마이크로 컴퓨터의 동작을 도시한 플로우 차트이다.

도 4는 제2의 실시예에 의한 마이크로 컴퓨터의 동작을 도시한 플로우 차트이다.

도 5는 인터럽트 처리의 동작을 도시한 플로우 차트이다.

도 6은 CPU 리셋 처리의 동작을 도시한 플로우 차트이다.

도 7은 CPU가 정상적으로 동작하고 있는 경우의 제1의 실시예에 대한 타임 차트이다.

도 8은 CPU에 있어서 치명적인 에러가 발생했을 경우의 제1의 실시예에 대한 타임 차트이다.

도 9는 CPU에 있어서 치명적인 에러가 발생했을 경우의 제2의 실시예에 대한 타임 차트이다.

도 1은 본 발명의 일실시예와 관련된 마이크로 컴퓨터의 전체를 도시한 블록도이다. 여기서, 마이크로 컴퓨터(100)는 중앙 처리장치(CPU)(101), 주기억장치(RAM)(105), ROM(110), 통신용 회로(115), 유니버셜 카운터 타이머(120), 입출력 포트(125), 논리합 회로(OR회로)(130), 시스템 리셋 신호원(135), 클록 발생 회로(140), 타이머 카운터 회로(145), 부가 타이머(150), 워치 독 회로(155), 위법 명령 검출 회로 및 정역외 액세스 검출 회로(160), 시스템 리셋용 버스(165), CPU 버스(170)를 구비한다.

시스템 리셋 신호원(135)은, 전원이 투입되었을 때 등에, 시스템 리셋용 신호를 발생시켜 시스템 리셋용 버스(165)를 통하여 시스템 리셋용 신호를 송신한다. 시스템 리셋용 신호는 마이크로 컴퓨터 전체를 리셋시키기 위한 신호이다. 시스템 리셋용 신호는, CPU(101)만이 아니고, 예를 들면, 입출력 포트(125), 통신 회로(115), 유니버셜 카운터 타이머(120) 등을 리셋하기 위해서도 이용된다.

워치 독 회로(155), 위법 명령 검출 회로 및 정역외 액세스 검출 회로(160)는 각각 CPU(101)가 정상적으로 동작하고 있는지 아닌지를 판정한다. CPU(101)가 정상적으로 동작하고 있지 않다고 판정되었을 경우, 워치 독 회로(155) 또는 위법 명령 검출 회로 및 정역외 액세스 검출 회로(160)는 시스템 리셋용 버스(165)를 통하여 CPU(101)나 통신 회로(115) 등에 시스템 리셋용 신호를 송신하고 마이크로 컴퓨터(100) 전체를 리셋한다.

클록 발생 회로(140)는 시스템의 클록 신호를 발생시키는 회로이다. 타이머 카운터 회로(145)는 제1의 처리 신호(인터럽트 요구 신호) 및 제2의 처리 신호(CPU 리셋 신호)를 발생시키는 회로이다. 논리합 회로(130)는 타이머 카운터 회로(145)로부터의 CPU 리셋 신호가 시스템 리셋용 버스(165)로 송신되는 것을 방지하고, CPU 리셋 신호를 CPU(101)로만 공급하기 위한 회로이다. 논리합 회로에는 CPU 리셋 신호 및 시스템 리셋용 신호가 입력으로서 공급된다. 따라서, CPU 리셋 신호는 CPU(101) 이외의 통신용 회로(115)나 유니버셜 카운터 타이머(120) 등으로는 공급되지 않는다. CPU(101)는 마이크로 컴퓨터(100)을 위한 제어 및 연산을 실행하는 회로이다.

도 2는 도 1의 클록 발생 회로(140), 타이머 카운터 회로(145) 및 CPU(101)를 보다 상세하게 도시한 블록도이다. CPU(101)는 CPU 레지스터(235)를 구비한다. 클록 발생 회로(140)는 클록 발생기(210), 분주기(215)를 포함한다. 타이머 카운터 회로(145)는 카운터(220), 부가 타이머(225), 비교기(230), 레지스터(255), CPU 리셋 신호용 플립플롭 회로(240), 인터럽트 요구 신호용 플립플롭 회로(245), 시스템 리셋용 플립플롭 회로(250)를 포함한다.

CPU(101)는 CPU 버스(170)를 통하여 레지스터(255) 및 시스템 리셋용 플립플롭 회로(250)에 접속된다. 클록 발생기(210)는 시스템의 클록 신호를 발생시키는 회로이다.

클록 발생기(210)가 발생시킨 제1의 클록 신호는 CPU(101)와 분주기(215)로 공급된다. 분주기(215)는 제1의 클록 신호의 주파수를 적당한 주파수인 제2의 클록 신호로 변경한다. 분주기(215)는 제2의 클록 신호를 카운터(220)로 공급한다.

카운터(220)는 제2의 클록 신호를 카운트한다. 제2의 클록 신호는 제2의 클록 신호의 카운트 값이 카운트 상한치에 도달할 때까지 카운트된다. 여기서, 제2의 클록 신호의 카운트 값은 카운터(220)가 제2의 클록 신호를 카운트한 값이다. 제2의 클록 신호의 카운트 값이 카운트 상한치에 도달했을 경우, 카운터(220)는 CPU 리셋 신호를 발생시켜, CPU 리셋 신호용 플립플롭 회로(240)를 세트하고, CPU를 리셋 하는데 충분한 수 클록 후에 플립플롭 회로(240)를 리셋한다. 게다가 카운터(220)는 제2의 클록 신호의 카운트 값이 카운트 상한치에 도달한 후, 제2의 클록 신호의 카운트 값을 리셋하고 카운트를 재개한다. 다른 실시예로서 상기 카운트 상한치를 CPU(101)가 초기화 처리 등에 있어서 설정하도록 구성할 수 있다. 또한, 전기적인 노이즈 등의 영향에 의해서 제2의 클록 신호의 카운트 값이 변경되었을 경우라도 프리 런닝 카운터(free-running counter)인 카운터(220)는 제2의 클록 신호의 카운트를 정지할 일은 없다.

다른 실시예로서 클록 발생기(210)는 분주기(215)를 이용하는 일 없이, 제1의 클록 신호를 카운터(220)로 공급할 수 있다. 이 경우, 카운터(220)는 클록 신호로서 제2의 클록 신호 대신에 제1의 클록 신호를 이용한다.

CPU 리셋 신호용 플립플롭 회로(240)는 카운터(220)로부터 수신한 CPU 리셋 신호를 짧은 펄스 폭인 펄스 신호로 파형 정형(waveform-shape)하고, CPU(101)로 공급한다. 다른 실시예로서 카운터(220)가 CPU 리셋 신호를 짧은 펄스폭인 펄스 신호로서 발생시킬 수 있는 경우, 카운터(220)는 CPU 리셋 신호용 플립플롭 회로(240)를 통하지 않고 CPU 리셋 신호를 CPU(101)로 직접 공급할 수 있다.

CPU(101)에는 전원 투입시 등에 시스템 리셋용 버스(165)를 통하여 시스템 리셋용 신호가 공급된다. CPU(101)는 시스템 리셋용 신호를 수신하면 시스템 리셋용 플립플롭 회로(250)를 리셋한다. 다른 실시예로서 전원 투입시 등에 시스템 리셋 신호원(135)가 시스템 리셋용 버스를 통하여 시스템 리셋용 플립플롭 회로(250)를 리셋할 수도 있다. 다른 실시예로서 CPU(101)는 시스템 리셋용 신호를 타이머 카운터 회로(145)로 공급하고 타이머 카운터 회로(145)내의 요소의 전부 또는 일부를 리셋할 수도 있다.

그 후, CPU(101)는 초기화 처리에 있어서, 시스템 리셋용 플립플롭 회로(250)를 세트한다. 카운터(220)는 시스템 리셋용 플립플롭 회로(250)가 리셋인 동안, 제2의 클록 신호를 카운트 하지 않는다. 초기화 처리에 있어서, 시스템 리셋용 플립플롭 회로(250)가 세트되면, 카운터(220)는 제2의 클록 신호의 카운트를 시작한다.

초기화 처리에 있어서, CPU(101)는 소정의 수치인 비교 대상치를 CPU 버스(170)를 통하여 레지스터(255)로 공급한다. 레지스터(255)는 그 비교 대상치를 저장한다.

비교기(230)는 제2의 클록 신호의 카운트 값과 레지스터(255)에 저장된 비교 대상치를 비교한다. 제2의 클록 신호의 카운트 값과 비교 대상치가 일치했을 경우, 비교기(230)는 인터럽트 요구 신호를 발생시켜, 인터럽트 요구 신호용 플립플롭 회로(245)로 공급한다.

인터럽트 요구신호용 플립플롭 회로(245)는 비교기(230)로부터 수신한 인터럽트 요구 신호를 짧은 펄스폭인 펄스 신호로 조정하고, CPU(101)로 공급한다. 다른 실시예로서 비교기(230)가 인터럽트 요구 신호를 짧은 펄스폭인 펄스 신호로서 발생시킬 수 있는 경우, 비교기(230)는 인터럽트 요구 신호용 플립플롭 회로(245)를 통하지 않고, 인터럽트 요구 신호를 CPU(101)로 직접 공급할 수 있다.

다른 실시예로서 카운터(220)는 부가 타이머(225)를 구비할 수 있다. 부가 타이머(225)는 미리 설정된 시간만 타이머를 작동시킨다. 부가 타이머(225)는 타이머가 작동하고 있는 동안 카운터(220)를 제어하는 것에 의해서, 카운터(220)가 CPU 리셋 신호용 플립플롭 회로(240)로 CPU 리셋 신호를 공급하는 것을 금지할 수 있다. 다른 실시예로서 부가 타이머(225)는 타이머가 작동하고 있는 동안, CPU 리셋 신호용 플립플롭 회로(240)를 리셋하고, CPU 리셋 신호용 플립플롭 회로(240)가 CPU 리셋 신호를 CPU(101)로 공급하는 것을 금지한다.

(실시예 1)

이하, 도 2의 회로의 동작을 설명한다.

우선 전원이 투입되었을 때에, 시스템 리셋 신호원(135)은 타이머 카운터 회로(145)내의 카운터(220) 및 모든 플립플롭 회로(240, 245, 250)를 리셋한다. 다른 실시예로서 시스템 리셋용 플립플롭 회로(250)는 CPU(101)에 의해서 리셋되도록 할 수 있다. 전원이 투입된 후, CPU(101)는 초기화 처리를 실시한다. 초기화 처리에 있어서, CPU(101)는 우선 레지스터(255)에 적당한 비교 대상치를 설정한다.

비교 대상치는 비교기(230)가 인터럽트 요구 신호를 발생시킬 때 이용하는 값이다. 비교기(230)는 제2의 클록 신호의 카운트 값과 비교 대상치를 비교해, 일치했을 경우에 인터럽트 요구 신호를 발생시킨다. 그리고 CPU(101)는 인터럽트 요구 신호를 수신하고 인터럽트 처리를 실행한다. 따라서, 인터럽트 처리는 제2의 클록 신호의 카운트가 시작된 후 제2의 클록 신호의 카운트 값이 비교 대상치에 도달할 때까지 카운트 되는 동안의 시간(비교 대상 시간)이 경과할 경우에 실행된다. 따라서, 소정의 시간 간격 마다, 인터럽트 요구 신호가 발생한다. 이것에 의해, CPU(101)는 소정의 시간 간격으로 인터럽트 요구 신호를 수신하고 인터럽트 요구 처리를 실행한다. 여기서, 비교 대상 시간은 제2의 클록 신호의 카운트 값이 비교 대상치에 이를 때까지 카운트 되는 동안의 시간이며, (제2의 클록 신호의 주기)×(비교 대상치)에 의해서 얻을 수 있다.

여기서, 인터럽트 처리란, 처리의 우선 순위가 적어도 응용 프로그램보다 높은 처리이다. 그리고 인터럽트 처리가 트리거 되면, CPU(101)는 응용 프로그램의 처리를 중단하는 동시에 인터럽트 처리를 시작한다.

시스템 리셋용 플립플롭 회로(250)는 마이크로 컴퓨터(100)의 전원 투입시 등에 시스템 리셋용 신호가 발생되었을 경우에게만, CPU(101) 또는 시스템 리셋 신호원(135)에 의해서 리셋된다. 그 후, 초기화 처리에 있어서 CPU(101)는 시스템 리셋용 플립플롭 회로(250)를 세트한다. 카운터(220)는 시스템 리셋용 플립플롭 회로(250)가 세트 된 후, 제2의 클록 신호의 카운트를 시작한다. 소프트웨어로부터 리셋하는 수단을 마련하지 않는 이유는 CPU에서 치명적인 에러가 발생했을 경우에 시스템 리셋용 플립플롭 회로(250)가 리셋되지 않게 하기 위해서이다. CPU에서 치명적인 에러가 발생했을 때, 시스템 리셋용 플립플롭 회로(250)가 리셋되지 않게 동작하는 것이 보증되는 경우, 소프트웨어가 시스템 리셋용 플립플롭 회로(250)를 리셋하는 수단을 구비할 수 있다.

비교기(230)는 제2의 클록 신호의 카운트 값과 레지스터(255)에 저장된 비교 대상치를 비교한다. 즉, 제2의 클록 신호의 카운트가 시작 또는 재개되고 나서 비교 대상 시간이 경과하고 있지 않은지를 확인한다. 제2의 클록 신호의 카운트 값과 비교 대상치가 일치했을 경우, 비교기(230)는 인터럽트 요구 신호를 발생시켜, 인터럽트 요구신호용 플립플롭 회로(245)를 세트하고, 수 클록 후에 리셋한다. 인터럽트 요구신호용 플립플롭 회로(245)는 인터럽트 요구 신호를 짧은 펄스폭인 펄스 신호로 파형 정형한다. 펄스 신호에 정형된 인터럽트 요구 신호는 CPU(101)로 공급된다.

다른 실시예로서 비교기(230)가 인터럽트 요구 신호를 짧은 펄스폭인 펄스 신호로서 발생시킬 수 있는 경우 비교기(230)는 인터럽트 요구신호용 플립플롭 회로(245)를 통하는 일 없이 CPU(101)로 인터럽트 요구 신호를 공급할 수 있다. CPU(101)는 인터럽트 요구 신호를 수신하면 인터럽트 처리를 실행한다.

카운터(220)는 제2의 클록 신호의 카운트 값이 카운트 상한치에 이른 것인지 아닌지를 확인한다. 즉, 카운터(220)는 제2의 클록 신호의 카운트가 시작 또는 재개되고 나서, 카운터 상한 시간이 경과하고 있지 않은지를 확인한다. 여기서, 카운터 상한 시간은 제2의 클록 신호의 카운트 값이 카운트 상한치에 이를 때까지 카운트 되는 동안의 시간이며 (제2의 클록 신호의 주기)×(카운트 상한치)에 의해서 얻을 수 있다.

카운터(220)는 제2의 클록 신호의 카운트 값이 카운트 상한치에 도달한 것을 확인하면, CPU 리셋 신호를 발생시켜, CPU 리셋 신호용 플립플롭 회로(240)를 세트한다. CPU 리셋 신호용 플립플롭 회로(240)는 CPU 리셋 신호를 짧은 펄스폭인 펄스 신호로 파형 정형한다. 펄스 신호에 정형된 CPU 리셋 신호는 CPU(101)에 공급된다.

다른 실시예로서 카운터(220)가 CPU 리셋 신호를 짧은 펄스폭인 펄스 신호로서 발생시킬 수 있는 경우, 카운터(220)는 CPU 리셋 신호용 플립플롭 회로(240)를 통하는 일 없이 CPU(101)로 CPU 리셋 신호를 공급할 수 있다.

CPU(101)는, CPU 리셋 신호를 수신하면, CPU 리셋 처리를 실행한다. CPU 리셋 신호용 플립플롭 회로(240)은 세트 된 직후 카운터(220)등에 의해서 리셋된다.

인터럽트 요구 신호를 수신한 것에 의해서 실행되는 인터럽트 처리의 실행 시작부터 종료까지의 시간(인터럽트 처리의 실행 시간)에 대하여 설명한다. 여기서, 비교 대상 시간은 카운터 상한 시간보다 짧은 시간이다. 그리고, 인터럽트 처리는 카운터(220)가 제2의 클록 신호의 카운트를 시작 또는 재개할 때인 카운트 시작시부터 비교 대상 시간에 도달했을 때에 실행된다. CPU 리셋 처리는 그 카운트 시작시 또는 재시작부터 카운터 상한 시간에 도달했을 때에 실행된다. 그리고 인터럽트 처리는 CPU 리셋 처리의 실행전에 종료하고 있을 필요가 있다. 그 이유는 후술 한다. 따라서, 카운터 상한 시간에서 비교 대상 시간을 뺀 시간은 인터럽트 처리의 실행 시간보다 긴 시간이 아니면 안된다. 구체적으로는 인터럽트 처리의 실행에 필요로 하는 시간이 50 마이크로 세컨드인 경우, (카운터 상한 시간)-(비교 대상 시간)는 50 마이크로 세컨드보다 길 필요가 있다. 따라서, 카운터 상한 시간이 5 밀리 세컨드인 경우, 비교 대상 시간은 4950 마이크로 세컨드보다 짧지 않으면 안 된다. 인터럽트 처리의 실행 시간은 카운터(220)의 상한 시간의 2~5%정도의 시간으로 설정되는 것이 바람직하다.

(실시예 2)

타이머 카운터 회로(145)는 게다가 부가 타이머(225)를 구비할 수 있다. 부가 타이머(225)는 인터럽트 처리에 있어서 CPU(101)등에 의해서 기동이 시작된다. 부가 타이머(225)는 CPU 리셋 신호가 발생할 때에(카운트 시작 또는 재시작부터 카운터 상한 시간에 도달했을 때에) CPU 리셋 신호의 발생을 금지한다. 부가 타이머(225)는 CPU 리셋 신호용 플립플롭 회로(240)가 세트되는 것을 금지하는 신호인 CPU 리셋 금지 신호를 이 플립플롭 회로(240)로 공급한다. 다른 실시예로서 부가 타이머(225)는 카운터(220)를 제어하는 것에 의해서 카운터(220)에 의한 CPU 리셋 신호의 발생을 금지할 수도 있다. 제2의 실시예에 의한 마이크로 컴퓨터(100)는 CPU 리셋 처리를 정기적으로 실행하지 않기 때문에, 제1의 실시예에 의한 마이크로 컴퓨터(100)과 비교해 CPU(101) 등에의 부담을 경감할 수 있다.

도 3은 제1의 실시예에 의한 마이크로 컴퓨터(100)의 동작을 도시한 플로우 차트이다. 최초로 마이크로 컴퓨터(100)에 전원이 투입된다(단계 305). 그리고 초기화 처리에 있어서, 마이크로 컴퓨터(100)의 초기화를 한다(단계 310). 초기화 처리의 종료후, 카운터(220)는 공급되는 클록 신호를 카운트 한다(단계 315).

비교기(230)는 클록 신호의 카운트 값이 비교 대상치에 도달했는지 아닌지를 판정한다(단계 320). 여기서, 클록 신호의 카운트 값는 카운터(220)가 클록 신호를 카운트한 값이다. 클록 신호의 카운트 값이 비교 대상치에 이르지 않은 경우, 비교기(230)는 클록 신호의 카운트 값이 비교 대상치가 될 때까지 대기한다. 클록 신호의 카운트 값이 비교 대상치에 이르렀을 경우, 비교기(230)는 인터럽트 요구 신호를 발생시켜, CPU(101)로 공급한다(단계 325).

CPU(101)는 인터럽트 요구 신호를 수신하면, 실행중의 응용 프로그램의 처리를 중단하는 것과 동시에 인터럽트 처리를 실행한다(단계 330). 인터럽트 처리에 대해서는 후술한다.

인터럽트 처리가 종료하면 카운터(220)는 클록 신호의 카운트 값이 카운트 상한치에 이를 때까지 대기한다(단계 335). 클록 신호의 카운트 값이 카운트 상한치에 이른 후, 카운터(220)는 CPU 리셋 신호를 발생시켜 CPU(101)로 공급한다(단계 340). 게다가 카운터(220)는 클록 신호의 카운트 값을 리셋 하는 것과 동시에 클록 신호의 카운트를 다시 시작한다.

CPU(101)는 CPU 리셋 신호를 수신하면, CPU 리셋 처리를 실행한다(단계 345). CPU 리셋 처리에 대해서는 후술 한다.

도 4는 제2의 실시예에 의한 마이크로 컴퓨터(100)의 동작을 도시한 플로우 차트이다. 도 4의 플로우 차트는 일부가 도 3의 플로우 차트와 같다. 도 4의 단계(405, 410, 415, 420, 425, 430, 450, 455 및 460)은 각각 도 3의 단계(305, 310, 315, 320, 325, 330, 335, 340 및 345)에 상당한다.

도 4의 플로우 차트는 이 플로우 차트의 단계(445, 450, 및 455)를 도 3의 플로우 차트에 추가한 것에 상당한다. 이하, 도 3과 도 4와의 차이에 대해서 설명한다. CPU(101)는 CPU 레지스터(235)의 정보를 취득한다(단계 435). CPU(101)는 취득한 정보가 정상인지 아닌지를 판정한다(단계 440). CPU 레지스터(235)의 정보가 정상인지 아닌지는 CPU 레지스터(235)의 값이 정상적인 범위에 들어가고 있는지, 적절한 값이 되어 있을지 등에 의해서 판정할 수 있다.

취득한 정보가 정상이지 않다고 판단되었을 경우, 도 3에 있어서의 플로우 차트의 단계(335, 340, 및 345)에 각각 상당하는 단계(450, 455, 및 460)가 실행된다. 취득한 정보가 정상이라고 판단되었을 경우, 부가 타이머(225)가 CPU 리셋 신호의 발생을 금지한다(단계 445). 덧붙여 CPU(101)가 부가 타이머(225)를 기동하도록 할 수도 있다. 따라서 CPU(101)에 치명적인 에러가 발생했을 경우, 부가 타이머(225)가 기동되지 않기 때문에, 부가 타이머(225)는 CPU 리셋 신호의 발생을 금지할 수 없다. 이것에 의해, CPU 리셋 신호가 CPU에 공급되어 CPU 리셋 처리가 실행된다. 부가 타이머(225)가 기동되지 않는 경우의 예로서는, CPU(101)에 치명적인 에러가 발생하고 있기 때문에 CPU(101)가 부가 타이머(225)를 기동하는 처리인 인터럽트 처리를 받아들이지 않을 때 등이 있다.

도 5는 인터럽트 처리의 동작을 도시한 플로우 차트이다. 인터럽트 처리는 CPU(101)가 인터럽트 요구 신호를 수신함으로써 실행된다(도 3의 단계(325및 330) 또는 도 4의 단계(425및 430) 참조). 최초로 CPU(101)는 인터럽트 시작시점(응용 프로그램 중단 시점)의 CPU 레지스터(235)의 정보를 RAM(105)에 저장한다(단계 505). 그리고 CPU(101)는 이 인터럽트 처리가 정상적인 동작인지 아닌지를 판정한다(단계 510).

정상적인 동작인지 아닌지는 CPU(101)가 RAM(105)에 저장된 특정의 정보가 올바른 것인지를 확인함으로써 판정된다. 예를 들면, 초기화 처리에 있어서 CPU(101)는 1 또는 2이상의 소정의 값을 미리 RAM(105)에 저장하고 그리고, 인터럽트 처리에 있어서 그 값이 변경되어 있지 않은 것을 확인한다. 여기서, 그들 소정의 값은 CPU(101)가 정상적으로 동작하고 있는 경우 초기화 처리 이외에 있어서 변경되지 않지만, CPU(101)로 치명적인 에러가 발생했을 경우, 예를 들면, CPU(101)의 오동작에 의해 그들 소정의 값이 변경될 가능성이 있다. 소정의 값이 변경되었을 경우 치명적인 에러가 생긴 것이 된다.

게다가, 전회의 인터럽트 처리 두고 CPU(101)가 그 인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보를 복귀 정보로서 RAM(105)에 저장하고, 그리고 현재 실행되고 있는 인터럽트 처리에 있어서, CPU(101)가 RAM(105)에 저장된 현재의 인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보와 RAM(105)에 저장된 전회의 인터럽트 처리 시점의 복귀 정보와를 비교해, 소정의 데이터가 정상인지 아닌지를 판정한다.

게다가, CPU(101)가 소정의 플래그가 온이 되어 있는지 아닌지를 확인하고 소정의 데이터가 정상인지 아닌지를 판정한다. 소정의 플래그의 예로서는 인터럽트 처리 종료 플래그를 RAM(105)에 마련할 수 있다. 인터럽트 처리 종료 플래그가 온이 되어 있는 경우, CPU(101)는 RAM(105)에 저장된 정보가 올바르다고 판정한다. 인터럽트 처리 종료 플래그를 이용하는 경우, CPU(101)는 단계(510)의 다음에, 인터럽트 처리 종료 플래그를 오프로 하고, 인터럽트 처리의 종료시에 온으로 되돌린다. 이것에 의해, 전회의 인터럽트 처리가 실행되고 있는 동안에 치명적인 에러가 생겼을 경우, 현재의 인터럽트 처리시의 단계( 510)에 있어서, 인터럽트 처리 종료 플래그가 오프이기 때문에, CPU(101)는 RAM(105)에 저장된 특정의 정보가 올바르지 않다고 판정한다.

게다가, 전회의 인터럽트 처리에 있어서, CPU(101)는 상기 CPU 레지스터(235)의 정보 및/또는 상기 소정의 플래그를 RAM(105)의 영역의 1개소 만이 아니고, 2개소 이상에 저장할 수 있다. 그리고, 현재 실행되고 있는 인터럽트 처리에 있어서, CPU(101)는 RAM(105)에 보존되고 있는 전회의 인터럽트 처리 시점의 상기 2이상의 CPU 레지스터(235)의 정보 각각 및/또는 상기 2이상의 소정의 플래그 각각이 같은지 아닌지를 확인한다. 그리고 그것들 정보 및/또는 플래그가 같은 경우 CPU(101)는 소정의 데이터가 정상이라고 판정한다. 이것에 의해, 소정의 데이터가 정상인지 아닌지의 판정이 보다 정확하게 실행된다. 하나의 실시예로서 상기 저장되는 정보 또는 플래그의 수를 3개로 할 수도 있다. 이것에 의해, 그것들 3개의 정보 또는 플래그중 1개가 다른 경우여도, CPU(101)는 나머지 2개의 정보 또는 플래그를 올바른 것으로서 이용할 수 있다. 이것에 의해 RAM(105)상의 데이터가 일부 파손했을 경우라도, CPU(101)는 소정의 데이터가 정상인지 아닌지의 판정을 실시할 수 있다. 이것들 판정에 대한 실시예는 예시이며, 다른 실시예에 의해서 똑같이 판정할 수도 있다.

인터럽트 처리가 정상적인 동작이라고 판정되었을 경우, CPU(101)는, RAM(105)에 저장된 인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보가 정상인지 아닌지를 판정한다(단계 515).인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보가 정상인지 아닌지는, CPU 레지스터(235)의 정보의 값이 정상적인 범위에 들어 있는지, 적절한 값이 되는지 등에 의해서 판정할 수 있다.

인터럽트 처리 시작 시점의 CPU 레지스터(235)의 정보가 정상이라고 판정되었을 경우, CPU(101)는 정상이라고 판정된 CPU 레지스터(235)의 정보를 복귀 정보로서 RAM(105)의 다른 영역에 저장한다(단계 520). 다른 실시예로서 CPU(101)는 이전의 세치기 처리에 있어서 RAM(105)에 이미 저장된 복귀 정보를 RAM(105)의 다른 장소에 복사하고 복귀 정보의 이력을 관리할 수 있다. 한층 더 다른 실시예로서 인터럽트 처리 종료 플래그를 이용하고 있는 경우, 인터럽트 처리 종료 플래그를 온으로 한다.

단계 510에 있어서, 인터럽트 처리가 정상적인 동작이 아니라고 판정되었을 경우, CPU(101)는 RAM(105)에 저장된 정보가 정상인지 아닌지를 판정한다(단계 525). 단계 525의 판정은, 전술의 RAM(105)에 저장된 특정의 정보 등을 이용해 실행된다.

단계 525에 있어서, RAM(105)에 저장된 정보가 정상적이지 않다고 판정되었을 경우, 마이크로 컴퓨터(100) 전체를 리셋하기 위해 시스템 리셋을 한다(단계 530). 시스템 리셋을 한 후, 단계 530이후의 처리가 중지되어 마이크로 컴퓨터(100)는 초기화된다. 다른 실시예에서는, 단계 530에 있어서, 입출력 포트(125) 등의 CPU의 치명적인 에러의 영향을 받기 어려운 요소는 리셋되지 않게 할 수 있다.

단계 515에 있어서, RAM(105) 레지스터(235)에 저장된 정보가 정상이지 않다고 판정되었을 경우 또는 단계 525에 있어서 인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보가 정상적이라고 판정되었을 경우, CPU(101)는 RAM(105)에 이력으로서 저장된 복귀 정보 등을 이용하고, CPU 레지스터(235)의 정보의 복구 처리를 실시한다(단계 535). 다른 실시예로서 단계 535의 뒤에 단계 510이 실행하도록 구성할 수 있다. 복구 처리의 하나의 실시예로서 CPU(101)는, 이력으로서 RAM(105)에 저장된 복귀 정보를 이용하고, CPU 레지스터(235)를 복구할 수 있다.

다른 실시예로서 인터럽트 처리는 단계 505 및 단계 520만으로 이루어지도록 구성할 수도 있다.

도 6은 CPU 리셋 처리의 동작을 도시한 플로우 차트이다. CPU 리셋 처리는 CPU(101)가 CPU 리셋 신호를 수신하는 것에 의해서 실행된다(도 3의 단계(340 및 345) 또는 도 4의 단계(455 및 460) 참조).

최초로, CPU(101)의 리셋을 한다(단계 610). 이것에 의해, CPU 레지스터(235)의 정보도 클리어 된다. CPU 리셋 처리(단계 345 또는 단계 460)를 실행하기 위한 트리거가 되는 CPU 리셋 신호는, 타이머 카운터로부터 주기적으로 반드시 주어진다. 따라서, CPU 리셋 처리(단계 345 또는 단계 460)는, 인터럽트 처리(단계 330 또는 단계 430)가 직전에 실행되어 있지 않아도 실행된다. 따라서, CPU(101)에 있어서 치명적인 에러가 발생한 것에 의해서, 인터럽트 처리가 실행되지 않는 경우여도 CPU 리셋 처리는 인터럽트 처리에 의존하는 일 없이 실행된다.

CPU(101)는 RAM(105)에 저장된 복귀 정보를 CPU 레지스터(235)에 복사한다(단계 615). 이것에 의해, CPU 레지스터(235)의 정보는 인터럽트 처리에 있어서 저장된 정보(도 5의 단계 520)이기 위해, 인터럽트 처리가 실행되기 전에 실행되고 있던 응용 프로그램은 CPU(101)를 리셋하는 것에 의한 영향을 받는 일 없이 재개된다.

*다른 실시예로서 CPU(101)는 복귀 정보를 CPU 레지스터(235)에 복사하기 전에 복귀 정보가 정상적인 값인지 또는 복귀 정보가 타당한지 등을 체크하도록 구성할 수 있다. 이것에 의해 복귀 정보가 정상 또는 타당한 값이 아닌 경우, 시스템 리셋 등이 행해지도록 할 수 있다.

또, CPU(101)에 있어서 치명적인 에러가 발생한 후에 그 CPU(101)가 리셋 되었을 경우, 단계 615의 처리에 의해서 CPU 레지스터(235)의 정보가 RAM(105)에 저장된 시점의 복귀 정보로 덮어 써진다(overwrite). 따라서, 복귀 정보가 CPU(101)에 있어서의 치명적인 에러에 의한 영향을 받지 않은 경우, CPU(101)로 치명적인 에러가 발생했다고 해도, 본 발명은 CPU(101)를 치명적인 에러로부터 회복시킬 수 있다.

여기서, 전술한 인터럽트 처리가 CPU 리셋 처리의 실행전에 종료하고 있을 필요가 있는 이유는 CPU(101)에 치명적인 에러가 발생하고 있지 않는 경우, CPU 리셋 처리의 단계 615에 있어서, RAM(105)에 저장된 복귀 정보를 CPU 레지스터(235)에 복사하기 위해서, 미리, 복귀 정보가 RAM(105)에 저장될(도 5의 단계 520 참조) 필요가 있어 인터럽트 처리가 정상적으로 종료하고, CPU(101)는 CPU 리셋 처리를 실행하기 위해서 대기에 들어가 있을 필요가 있기 때문이다.

다른 실시예로서 CPU 레지스터(235) 또는 RAM(105)에 CPU 리셋 처리 실행 가능 플래그가 저장되도록 할 수 있다. 예를 들면, 인터럽트 처리에 있어서 복귀 정보가 RAM(105)에 저장될 때에, CPU(101)가 CPU 리셋 처리 실행 가능 플래그를 온으로 한다. 그리고 CPU 리셋 처리 실행 가능 플래그가 온인 경우만 CPU 리셋 처리를 실행하고 CPU 리셋 처리 완료시에, CPU(101)가 CPU 리셋 처리 실행 가능 플래그를 오프로 한다. 이것에 의해, CPU에 치명적인 에러가 발생하고 인터럽트 처리에 있어서 복귀 정보가 RAM(105)에 갱신되지 않는 경우, CPU 리셋 처리에 있어서, 치명적인 에러가 발생하기 전에 저장된 복귀 정보를 계속 사용하는 것을 회피할 수 있다. 인터럽트 처리에 있어서 복귀 정보가 RAM(105)에 갱신되지 않는 경우, 마이크로 컴퓨터(100) 전체를 리셋하는 등 다른 수단에 의해 CPU(101)의 치명적인 에러를 회피할 수 있다.

다른 실시예로서 CPU 리셋 처리는, CPU의 리셋 이후(단계 610 이후), RAM(105)에 저장되고 있는 복귀 정보가 정상이지 않은 경우, 복귀 정보를 회복시키는 단계를 포함할 수 있다. 여기서, 복귀 정보가 정상인지 아닌지는 복귀 정보의 값이 정상적인 범위에 들어가고 있는지 적절한 값이 되는지 등에 의해서 CPU(101)가 판정할 수 있다. 복귀 정보를 회복시키는 처리의 예로서 CPU(101)는 RAM(105)에 저장된 복귀 정보의 이력으로부터 정상인 복귀 정보를 선택하고 선택한 복귀 정보를 CPU 레지스터(235)에 복사할 수 있다.

한층 더 다른 실시예로서 인터럽트 처리는, CPU의 리셋 이후(단계 610 이후) 마이크로 컴퓨터를 정상적으로 동작시킬 수 없는 경우, 시스템 리셋을 실시하는 단계를 포함할 수 있다. 여기서, 마이크로 컴퓨터를 정상적으로 동작시킬 수 있는지 아닌지는, CPU(101)가 RAM(105)에 저장되는 특정의 정보가 올바른 지를 확인하는 것에 의해서 판정할 수 있다. 여기서, 특정의 정보가 올바른지 아닌지는 초기화 처리만으로 변경되는 특정의 정보가 치명적인 에러가 발생했던 것에 기인하고 초기화 처리 이외의 처리에 의해서 변경되고 있는지 아닌지를 판정함으로써 행해진다. 게다가 마이크로 컴퓨터를 정상적으로 동작시킬 수 있는지 아닌지는, CPU(101)가 이력으로서 RAM(105)에 저장되고 있는 복수의 복귀 정보로부터 정상적인 범위 또는 적절한 값인 복귀 정보가 있는지 아닌지를 확인함으로써 판정할 수 있다. 정상적인 범위 또는 적절한 값인 복귀 정보가 하나도 없는 경우, 마이크로 컴퓨터는 정상적으로 동작할 수 없다고 판단된다.

도 7은, CPU(101)가 정상적으로 동작하고 있는 경우의 제1의 실시예(도 3 참조)에 대한 타임 차트이다. 그 타임 차트는 시각 T1, T2···T5, T6의 순서에 시간이 진행되고 있는 것을 도시한다. 상태 701, 715 및 730은 응용 프로그램의 처리가 실행되고 있는 것을 나타낸다. 상태 705 및 720은 인터럽트 처리가 실행되고 있는 것을 도시한다. 상태 710 및 725는 CPU 리셋 처리가 실행되고 있는 것을 도시한다.

시각 T1보다 전에 있어서 응용 프로그램의 처리가 실행되고 있다(상태 701). 시각 T1에 있어서, CPU(101)는 인터럽트 요구 신호를 수신한다. CPU(101)는 인터럽트 요구 신호의 수신을 트리거로서 응용 프로그램의 처리를 중단하고 인터럽트 처리를 시작한다(상태 705).인터럽트 처리에 있어서, CPU(101)는 인터럽트 처리 시작시점의 CPU 레지스터(235)의 정보를 복귀 정보로서 RAM(105)에 저장한다.

시각 T2에 있어서 인터럽트 처리가 종료하고, CPU(101)는 CPU 리셋 신호를 수신한다. CPU(101)는 CPU 리셋 신호의 수신을 트리거로서 CPU 리셋 처리를 시작한다(상태 710). CPU 리셋 처리에 있어서, CPU(101)가 리셋 된 후, CPU(101)는, RAM(105)에 저장되고 있는 복귀 정보를 CPU 레지스터(235)에 복사한다. 이것에 의해 시각 T3에 있어서, CPU(101)는 중단된 응용 프로그램을 T1 시점의 처리로부터 재개한다. 시각 T4, T5 및 T6에 있어서, 시각 T1, T2 및 T3와 같게 응용 프로그램의 중단, 인터럽트 처리 및 CPU 리셋 처리가 실행된다.

도 8은 CPU(101)에 있어서 치명적인 에러가 발생했을 경우의 제1의 실시예(도 3 참조)에 대한 타임 차트이다. 시각 T1, T2, T3에 있어서, 응용 프로그램의 처리, 인터럽트 처리, CPU 리셋 처리가 실행된다(상태 801, 805 및 810). 상태 805의 인터럽트 처리에 있어서, CPU(101)는, 시각 T1에 있어서의 CPU 레지스터(235)의 정보인 복귀 정보를 RAM(105)에 저장한다.

응용 프로그램의 처리 실행중의(상태 815) T4에 있어서, CPU(101)에 치명적인 에러가 발생했다고 한다. 이것에 의해, CPU(101)는 정상적으로 처리를 실행하지 못하는 것으로부터 상태 820은 응용 프로그램의 처리가 실행되지 않은 것을 나타낸다. 게다가 상태 825는 인터럽트 처리가 실행되지 않은 것을 나타낸다.

시각 T6에 있어서, CPU(101)는 CPU 리셋 신호를 수신한다. CPU(101)는 CPU 리셋 신호의 수신을 트리거로서 CPU 리셋 처리를 시작한다(상태 830). CPU 리셋 처리에 있어서, CPU(101)가 리셋된 후, CPU(101)는 RAM(105)에 저장되고 있는 복귀 정보를 CPU 레지스터(235)에 복사한다. 이것에 의해, 시각 T7에 있어서 CPU(101)는 중단된 응용 프로그램을 T1 시점의 처리로부터 재개한다(상태 835).

도 9는 CPU(101)에 있어서 치명적인 에러가 발생했을 경우의 제2의 실시예(도 4 참조)에 대한 타임 차트이다. 시각 T1, T2에 있어서, 응용 프로그램의 처리, 인터럽트 처리가 실행된다(상태 901및 905). 상태 905의 인터럽트 처리에 있어서, CPU(101)는 시각 T1에 있어서의 CPU 레지스터(235)의 정보인 복귀 정보를 RAM(105)에 저장한다.

시각 T2에 있어서, CPU 리셋 신호의 발생을 금지하는 처리가 실행된다(상태 910). 이것에 의해, CPU 리셋 처리가 실행되지 않는다. CPU 리셋 처리가 실행되지 않기 때문에, 인터럽트 처리가 종료한 후, 시각 T2에 있어서, 응용 프로그램의 처리가 재개된다(상태 915).

응용 프로그램의 처리 실행중의(상태 915) T4에 있어서, CPU(101)에 치명적인 에러가 발생했다고 한다. 이것에 의해, CPU(101)는 정상적으로 처리를 실행하지 못하는 것으로부터 상태 920의 응용 프로그램의 처리 및 상태 925의 인터럽트 처리는 실행되지 않고, 게다가 시각 T2에 있어서 실행되고 있던 CPU 리셋 신호의 발생을 금지하는 처리도 실행되지 않는다.

시각 T6에 있어서, CPU 리셋 신호의 발생을 금지하는 처리가 실행되지 않기 때문에, CPU(101)는 CPU 리셋 신호를 수신한다. CPU(101)는 CPU 리셋 신호의 수신을 트리거로서 CPU 리셋 처리를 시작한다(상태 930). CPU 리셋 처리에 있어서, CPU(101)가 리셋 된 후, CPU(101)는 RAM(105)에 저장되고 있는 복귀 정보를 CPU 레지스터(235)에 복사한다. 이것에 의해, CPU(101)는 시각 T7에 있어서, 중단된 응용 프로그램을 T1 시점의 처리로부터 재개한다(상태 940).

본 발명에 의해, CPU에 있어서, 이른바 폭주등이 치명적인 에러가 발생했을 경우, 마이크로 컴퓨터 전체를 리셋하는 일 없이, CPU만을 리셋하는 것에 의해서, 치명적인 에러로부터 마이크로 컴퓨터를 복귀시킬 수 있다. 이것에 의해, 산업계에서 넓게 사용되고 있는 편성용 마이크로 컴퓨터의 CPU로 발생하는 치명적인 에러에의 대책을 보다 고속으로, 한편, 간단하게 실현될 수 있다. 메카트로닉스, 로봇, 파칭코, 파치슬로대를 포함한 게임기기, 자동차의 엔진 컨트롤, 브레이크의 컨트롤, 엘리베이터의 컨트롤 등의 분야에 있고, 마이크로 컴퓨터에 있어서의 CPU의 치명적인 에러는 사고나 위험 내지는 금전의 손해를 일으키게 할 가능성이 있다. 따라서, 이러한 분야에 있어서 본 발명에 의한 마이크로 컴퓨터를 이용하는 것에 의해서, 사고나 손해를 대폭으로 경감할 수 있다.

100 마이크로 컴퓨터

101 중앙처리장치(CPU)

105 주기억장치(RAM)

110 ROM

115 통신용 회로

120 유니버셜 카운터 타이머

125 입출력 포트

130 논리합 회로(OR회로)

135 시스템 리셋 신호원

140 클록 발생 회로

145 타이머 카운터 회로

150 부가 타이머

155 워치 독 회로

160 위법 명령 검출 회로 및 정역외 액세스 검출 회로

165 시스템 리셋용 버스

170 CPU 버스

210 클록 발생기

215 분주기

220 카운터

225 부가 타이머

230 비교기

235 CPU 레지스터

240 CPU 리셋 신호용 플립플롭 회로

245 인터럽트 요구 신호용 플립플롭 회로

250 시스템 리셋용 플립플롭 회로

255 레지스터

101 중앙처리장치(CPU)

105 주기억장치(RAM)

110 ROM

115 통신용 회로

120 유니버셜 카운터 타이머

125 입출력 포트

130 논리합 회로(OR회로)

135 시스템 리셋 신호원

140 클록 발생 회로

145 타이머 카운터 회로

150 부가 타이머

155 워치 독 회로

160 위법 명령 검출 회로 및 정역외 액세스 검출 회로

165 시스템 리셋용 버스

170 CPU 버스

210 클록 발생기

215 분주기

220 카운터

225 부가 타이머

230 비교기

235 CPU 레지스터

240 CPU 리셋 신호용 플립플롭 회로

245 인터럽트 요구 신호용 플립플롭 회로

250 시스템 리셋용 플립플롭 회로

255 레지스터

Claims (7)

- CPU와,

상기 CPU와 CPU 버스를 통하여 접속된 RAM와,

클록 신호를 카운트하는 타이머 카운터 회로이고, 카운트한 값이 카운트 상한치에 도달한 경우, 당해 카운트 값을 리셋하고, 카운트를 재개하는 타이머 카운터 회로와,

상기 카운트 값이 소정의 값과 일치한 경우, 인터럽트 처리의 실행 시작을 요구하기 위한 인터럽트 요구 신호를 상기 CPU에 출력하는 인터럽트 요구 신호 출력 수단과,

상기 카운트 값이 상기 소정의 값보다 큰 값인 상기 상한치에 도달한 경우, CPU 리셋 처리의 시작을 요구하기 위한 CPU 리셋 신호를 상기 CPU로 출력하는 CPU 리셋 신호 출력 수단을 포함하고,

상기 CPU는, 상기 인터럽트 요구 신호를 수신하면, 상기 CPU상에서 실행되고 있는 응용 프로그램의 처리를 중단하는 것과 동시에, 상기 CPU의 CPU 레지스터의 정보를 복귀 정보로서 상기 RAM에 저장하고, 상기 CPU 리셋 신호를 수신하면, 상기 CPU는, 리셋되는 것과 동시에, 상기 RAM에 저장되고 있는 상기 복귀 정보를 상기 CPU 레지스터에 복사하는 것을 특징으로 하는 마이크로 컴퓨터.

- 청구항 1에 있어서,

상기 CPU 리셋 신호 및 상기 인터럽트 요구 신호는 상기 타이머 카운터 회로에 의해 주기적으로 발생하는 것을 특징으로 하는 마이크로 컴퓨터.

- 청구항 2에 있어서,

상기 타이머 카운터 회로는 부가 타이머를 포함하고,

상기 CPU는 상기 CPU 레지스터의 정보가 정상인지를 판정하고, 상기 CPU 레지스터의 정보가 정상이라고 판정되었을 경우에만, 상기 부가 타이머는 상기 CPU 리셋 신호가 상기 CPU로 공급되는 동안 작동하고, 상기 CPU 리셋 처리의 실행을 금지하는 것을 특징으로 하는 마이크로 컴퓨터.

- 청구항 1 내지 청구항 3 중 어느 한 항에 있어서,

마이크로 컴퓨터 전체를 리셋하기 위한 시스템 리셋 신호원과,

논리합 회로를 더 포함하고,

상기 CPU 리셋 신호 출력 수단 및 상기 시스템 리셋 신호원은 상기 논리합 회로의 입력 측에 접속되고, 상기 CPU는 논리합 회로의 출력측에 접속되는 것을 특징으로 하는 마이크로 컴퓨터.

- 타이머 카운터 회로에 의해, 클록 신호를 카운트하고, 카운트한 값이 카운트 상한치에 도달한 경우, 당해 카운트 값을 리셋하며, 카운트를 재개하는 단계와,

상기 카운트 값이 소정의 값과 일치한 경우, 인터럽트 처리의 실행 시작을 요구하기 위한 인터럽트 요구 신호를 CPU로 출력하는 단계와,

상기 CPU에 의해서, 상기 인터럽트 요구 신호를 수신하여, 해당 CPU상에서 실행되고 있는 응용 프로그램의 처리를 중단하는 단계와,

상기 CPU에 의해서, 상기 CPU의 CPU 레지스터의 정보를 복귀 정보로서 RAM에 저장하는 단계와,

상기 카운트 값이 상기 소정의 값보다 큰 값인 상기 상한치에 도달한 경우, CPU 리셋 처리의 시작을 요구하기 위한 CPU 리셋 신호를 상기 타이머 카운터 회로로부터 상기 CPU로 출력하는 단계와,

상기 CPU에 있어서, 상기 CPU 리셋 신호를 수신하여, 해당 CPU를 리셋하는 단계와,

상기 CPU에 의해서, 상기 RAM에 저장된 상기 복귀 정보를 상기 CPU 레지스터로 복사하는 단계를 포함하는 마이크로 컴퓨터의 동작 방법.

- 청구항 5에 있어서,

상기 CPU 리셋 신호 및 상기 인터럽트 요구 신호는 상기 타이머 카운터 회로에 의해서 주기적으로 발생하는 것을 특징으로 하는 마이크로 컴퓨터의 동작 방법.

- 청구항 6에 있어서,

상기 CPU에 의해서, 상기 CPU 레지스터의 정보가 정상인지를 판정하고, 상기 CPU 레지스터의 정보가 정상이라고 판정되었을 경우에만, 상기 CPU 리셋 신호가 상기 CPU로 공급되는 동안, 상기 CPU를 리셋하는 단계의 실행을 금지하는 단계를 더 포함하는 것을 특징으로 하는 마이크로 컴퓨터의 동작 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2009-238742 | 2009-10-15 | ||

| JP2009238742 | 2009-10-15 | ||

| PCT/JP2010/068203 WO2011046217A1 (ja) | 2009-10-15 | 2010-10-15 | マイクロコンピュータ及びその動作方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020127012574A Division KR20120085810A (ko) | 2009-10-15 | 2010-10-15 | 마이크로 컴퓨터 및 그 동작 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20140105584A true KR20140105584A (ko) | 2014-09-01 |

Family

ID=43876266

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147019919A KR20140105584A (ko) | 2009-10-15 | 2010-10-15 | 마이크로 컴퓨터 및 그 동작 방법 |

| KR1020127012574A KR20120085810A (ko) | 2009-10-15 | 2010-10-15 | 마이크로 컴퓨터 및 그 동작 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020127012574A KR20120085810A (ko) | 2009-10-15 | 2010-10-15 | 마이크로 컴퓨터 및 그 동작 방법 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US8954801B2 (ko) |

| EP (1) | EP2490125A1 (ko) |

| JP (2) | JP5244981B2 (ko) |

| KR (2) | KR20140105584A (ko) |

| CN (1) | CN102656568B (ko) |

| AU (1) | AU2010307632B2 (ko) |

| BR (1) | BR112012008687A2 (ko) |

| IN (1) | IN2012DN03088A (ko) |

| RU (1) | RU2520399C2 (ko) |

| WO (1) | WO2011046217A1 (ko) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2010307632B2 (en) | 2009-10-15 | 2013-12-05 | L E Tech Co., Ltd. | Microcomputer and operation method thereof |

| JP5540697B2 (ja) * | 2009-12-25 | 2014-07-02 | 富士通株式会社 | 演算処理装置、情報処理装置および演算処理装置の制御方法 |

| DE102012209712A1 (de) * | 2012-06-11 | 2013-12-12 | Robert Bosch Gmbh | Aktive Funktionseinschränkung eines Mikrocontrollers |

| GB2503459A (en) * | 2012-06-26 | 2014-01-01 | Nordic Semiconductor Asa | Multiple hardware registers for watchdog timer preventing erroneous microprocessor system reset |

| US10040447B2 (en) * | 2012-10-05 | 2018-08-07 | Ford Global Technologies, Llc | Control strategy for an electric machine in a vehicle |

| CN103809717B (zh) * | 2012-11-09 | 2017-04-12 | 华为技术有限公司 | 复位方法和网络设备 |

| JP6266239B2 (ja) * | 2013-07-11 | 2018-01-24 | ルネサスエレクトロニクス株式会社 | マイクロコンピュータ |

| JP2016181055A (ja) * | 2015-03-23 | 2016-10-13 | 株式会社東芝 | 情報処理装置 |

| US9857975B2 (en) | 2015-06-26 | 2018-01-02 | International Business Machines Corporation | Non-volatile memory drive partitions within microcontrollers |

| JP6722010B2 (ja) * | 2016-03-16 | 2020-07-15 | ソニー・オリンパスメディカルソリューションズ株式会社 | 医療用観察システム |

| CN105954636A (zh) * | 2016-04-21 | 2016-09-21 | 张顺 | 一种短路和接地故障指示器 |

| KR102406740B1 (ko) * | 2020-08-28 | 2022-06-08 | 주식회사 엘씨엠에너지솔루션 | 태양광 라이팅 시스템용 컨트롤러 및 태양광 라이팅 시스템의 리셋 방법 |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4234870A (en) * | 1979-01-11 | 1980-11-18 | General Signal Corporation | Vital electronic code generator |

| JPS5616248A (en) * | 1979-07-17 | 1981-02-17 | Matsushita Electric Ind Co Ltd | Processing system for interruption |

| JPS63221437A (ja) * | 1987-03-11 | 1988-09-14 | Alps Electric Co Ltd | Cpuの暴走検出方式 |

| US5109506A (en) * | 1989-06-19 | 1992-04-28 | International Business Machines Corp. | Microcomputer system including a microprocessor reset circuit |

| JPH04160438A (ja) * | 1990-10-23 | 1992-06-03 | Mitsubishi Electric Corp | 半導体装置 |

| US5551033A (en) * | 1991-05-17 | 1996-08-27 | Zenith Data Systems Corporation | Apparatus for maintaining one interrupt mask register in conformity with another in a manner invisible to an executing program |

| JPH05155295A (ja) | 1991-12-03 | 1993-06-22 | Fuji Heavy Ind Ltd | 車輌用電子制御システムの制御方法 |

| JP2658697B2 (ja) * | 1991-12-11 | 1997-09-30 | 富士通株式会社 | ウォッチ・ドック・タイマ回路 |

| JP3135714B2 (ja) | 1992-10-29 | 2001-02-19 | 株式会社東芝 | チェックポイントリスタート方式 |

| JPH06161797A (ja) * | 1992-11-24 | 1994-06-10 | Mitsubishi Electric Corp | データ処理装置 |

| US5752073A (en) | 1993-01-06 | 1998-05-12 | Cagent Technologies, Inc. | Digital signal processor architecture |

| JP3130536B2 (ja) | 1993-01-21 | 2001-01-31 | アップル コンピューター インコーポレーテッド | 多数のネットワークされたコンピュータ記憶装置からデータを転送し記憶する装置ならびに方法 |

| JP3045888B2 (ja) | 1993-02-23 | 2000-05-29 | 株式会社日立製作所 | データ処理装置 |

| KR970008188B1 (ko) * | 1993-04-08 | 1997-05-21 | 가부시끼가이샤 히다찌세이사꾸쇼 | 플래시메모리의 제어방법 및 그것을 사용한 정보처리장치 |

| JPH06102099B2 (ja) | 1993-08-06 | 1994-12-14 | 株式会社大一商会 | パチンコ機の制御装置 |

| GB2281986B (en) | 1993-09-15 | 1997-08-06 | Advanced Risc Mach Ltd | Data processing reset |

| JPH07191579A (ja) * | 1993-12-27 | 1995-07-28 | Minolta Co Ltd | 画像形成装置 |

| JPH07219796A (ja) | 1994-02-04 | 1995-08-18 | Kofu Nippon Denki Kk | 情報処理装置 |

| JP3276782B2 (ja) * | 1994-08-18 | 2002-04-22 | 本田技研工業株式会社 | 電動補助自転車 |

| US6738894B1 (en) * | 1995-02-07 | 2004-05-18 | Hitachi, Ltd. | Data processor |

| JPH09237076A (ja) | 1995-12-27 | 1997-09-09 | Omron Corp | 画像表示システム |

| JP3425838B2 (ja) | 1996-04-30 | 2003-07-14 | 日本電気株式会社 | データ退避読み出し方法 |

| JPH09319602A (ja) | 1996-05-31 | 1997-12-12 | Toshiba Corp | コンピュータシステム及びリセット制御方法 |

| JP3094924B2 (ja) | 1996-10-31 | 2000-10-03 | 日本電気株式会社 | 通信装置制御回路 |

| JPH10240620A (ja) | 1996-12-26 | 1998-09-11 | Toshiba Corp | コンピュータシステムおよび同システムにおけるチェックポイントイメージ保存方法 |

| KR100352023B1 (ko) * | 1999-09-03 | 2002-09-11 | 가야바코교 가부시기가이샤 | 페일세이프기구 |

| JP4146045B2 (ja) | 1999-09-10 | 2008-09-03 | 株式会社東芝 | 電子計算機 |

| JP2001188687A (ja) | 2000-01-05 | 2001-07-10 | Matsushita Electric Ind Co Ltd | マイクロコンピュータ |

| JP3981234B2 (ja) * | 2000-02-21 | 2007-09-26 | 松下電器産業株式会社 | マイクロコンピュータ |

| JP2001243211A (ja) * | 2000-02-29 | 2001-09-07 | Mitsubishi Electric Corp | マイクロコンピュータ |

| JP2002108835A (ja) * | 2000-09-29 | 2002-04-12 | Mitsubishi Electric Corp | 車載電子制御装置 |

| DE10049441B4 (de) * | 2000-10-06 | 2008-07-10 | Conti Temic Microelectronic Gmbh | Verfahren zum Betrieb eines von einem Prozessor gesteuerten Systems |

| US6779065B2 (en) * | 2001-08-31 | 2004-08-17 | Intel Corporation | Mechanism for interrupt handling in computer systems that support concurrent execution of multiple threads |

| JP2004086451A (ja) | 2002-08-26 | 2004-03-18 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP4294503B2 (ja) * | 2003-07-31 | 2009-07-15 | 富士通マイクロエレクトロニクス株式会社 | 動作モード制御回路、動作モード制御回路を含むマイクロコンピュータ及びそのマイクロコンピュータを利用した制御システム |

| RU2265240C2 (ru) * | 2003-11-27 | 2005-11-27 | Общество с ограниченной ответственностью Научно-производственная фирма "КРУГ" (ООО НПФ "КРУГ") | Модуль системного контроля |

| JP4522799B2 (ja) * | 2004-09-08 | 2010-08-11 | ルネサスエレクトロニクス株式会社 | 半導体回路装置及び暴走検出方法 |

| US7610462B2 (en) | 2004-09-16 | 2009-10-27 | Wms Gaming Inc. | Gaming machine with secure fault-tolerant memory |

| JP2006172316A (ja) * | 2004-12-17 | 2006-06-29 | Nec Corp | コンテキスト維持方法、情報処理装置及び割り込み発生装置 |

| TW200625083A (en) | 2005-01-14 | 2006-07-16 | Farstone Tech Inc | Backup/recovery system and method thereof |

| US7328315B2 (en) | 2005-02-03 | 2008-02-05 | International Business Machines Corporation | System and method for managing mirrored memory transactions and error recovery |

| CN100363904C (zh) * | 2005-03-05 | 2008-01-23 | 鸿富锦精密工业(深圳)有限公司 | 中央处理器温度侦测与校正装置及方法 |

| US7457928B2 (en) * | 2005-10-28 | 2008-11-25 | International Business Machines Corporation | Mirroring system memory in non-volatile random access memory (NVRAM) for fast power on/off cycling |

| JP2007323631A (ja) * | 2006-05-01 | 2007-12-13 | Shinko Electric Ind Co Ltd | Cpu暴走判定回路 |

| JP4893427B2 (ja) * | 2006-06-30 | 2012-03-07 | 株式会社デンソー | マイクロコンピュータシステム |

| JP2008152594A (ja) * | 2006-12-19 | 2008-07-03 | Hitachi Ltd | マルチコアプロセッサ計算機の高信頼化方法 |

| GB2455344B (en) * | 2007-12-06 | 2012-06-13 | Advanced Risc Mach Ltd | Recovering from control path errors |

| JP4691170B2 (ja) | 2008-03-04 | 2011-06-01 | 株式会社ジョブ | X線照射装置 |

| US8381032B2 (en) | 2008-08-06 | 2013-02-19 | O'shantel Software L.L.C. | System-directed checkpointing implementation using a hypervisor layer |

| AU2010307632B2 (en) | 2009-10-15 | 2013-12-05 | L E Tech Co., Ltd. | Microcomputer and operation method thereof |

| US20130055017A1 (en) | 2010-03-30 | 2013-02-28 | L E Tech Co., Ltd. | Device and method for restoring information in a main storage unit |

-

2010

- 2010-10-15 AU AU2010307632A patent/AU2010307632B2/en not_active Ceased

- 2010-10-15 JP JP2011536199A patent/JP5244981B2/ja active Active

- 2010-10-15 BR BR112012008687A patent/BR112012008687A2/pt not_active IP Right Cessation

- 2010-10-15 EP EP10823485A patent/EP2490125A1/en not_active Withdrawn

- 2010-10-15 CN CN201080057356.9A patent/CN102656568B/zh not_active Expired - Fee Related

- 2010-10-15 KR KR1020147019919A patent/KR20140105584A/ko not_active Application Discontinuation

- 2010-10-15 WO PCT/JP2010/068203 patent/WO2011046217A1/ja active Application Filing

- 2010-10-15 US US13/501,718 patent/US8954801B2/en not_active Expired - Fee Related

- 2010-10-15 RU RU2012119785/08A patent/RU2520399C2/ru not_active IP Right Cessation

- 2010-10-15 KR KR1020127012574A patent/KR20120085810A/ko active IP Right Grant

-

2012

- 2012-04-10 IN IN3088DEN2012 patent/IN2012DN03088A/en unknown

-

2013

- 2013-04-08 JP JP2013080600A patent/JP5705258B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013137835A (ja) | 2013-07-11 |

| AU2010307632B2 (en) | 2013-12-05 |

| RU2520399C2 (ru) | 2014-06-27 |

| JP5705258B2 (ja) | 2015-04-22 |

| AU2010307632A1 (en) | 2012-05-17 |

| JPWO2011046217A1 (ja) | 2013-03-07 |

| WO2011046217A1 (ja) | 2011-04-21 |

| CN102656568B (zh) | 2015-09-02 |

| US8954801B2 (en) | 2015-02-10 |

| US20120254658A1 (en) | 2012-10-04 |

| RU2012119785A (ru) | 2013-11-20 |

| EP2490125A1 (en) | 2012-08-22 |

| CN102656568A (zh) | 2012-09-05 |

| JP5244981B2 (ja) | 2013-07-24 |

| IN2012DN03088A (ko) | 2015-07-31 |

| KR20120085810A (ko) | 2012-08-01 |

| BR112012008687A2 (pt) | 2016-04-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20140105584A (ko) | 마이크로 컴퓨터 및 그 동작 방법 | |

| JP5951429B2 (ja) | ウォッチドッグ回路、電源ic、及びウォッチドッグ監視システム | |

| EP0679981B1 (en) | Reset circuit of electronic device | |

| US7966528B2 (en) | Watchdog mechanism with fault escalation | |

| US7716524B2 (en) | Restarting an errored object of a first class | |

| US7711985B2 (en) | Restarting an errored object of a first class | |

| JP5579257B2 (ja) | 主記憶装置における情報を復元するための装置及び方法 | |

| JP2009003663A (ja) | 電源制御装置 | |

| KR20070012351A (ko) | 전자 회로 장치 및 이 전자 회로 장치를 사전결정된 상태에이르게 하는 방법 | |

| JPH11259340A (ja) | コンピュータの再起動制御回路 | |

| WO2019012996A1 (ja) | 車両制御装置 | |

| US7246206B2 (en) | Method and device for storing a computer program in a program memory of a control unit | |

| JP2001242901A (ja) | プログラマブルコントローラの異常検出装置 | |

| JP2001350643A (ja) | マイクロコンピュータの制御方法及び異常監視装置 | |

| JP2002210093A5 (ko) | ||

| JPH0477854A (ja) | マイクロコンピュータ回路 | |

| JPH05189258A (ja) | マイクロコンピュータ | |

| JPH01293448A (ja) | マイクロコンピュータ | |

| JP2001197654A (ja) | ディジタル形保護継電装置 | |

| WO2009016187A2 (en) | Watchdog mechanism with fault recovery | |

| JPH10254789A (ja) | 駆動制御装置および駆動制御方法 | |

| JPH10161887A (ja) | 割込み信号同期化方法及び割込み信号同期化装置 | |

| JPH06222804A (ja) | ディジタル制御装置 | |

| JPH05158750A (ja) | マイクロコンピュータの誤動作防止回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |