JP6332680B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP6332680B2 JP6332680B2 JP2014122705A JP2014122705A JP6332680B2 JP 6332680 B2 JP6332680 B2 JP 6332680B2 JP 2014122705 A JP2014122705 A JP 2014122705A JP 2014122705 A JP2014122705 A JP 2014122705A JP 6332680 B2 JP6332680 B2 JP 6332680B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- insulating layer

- wiring layer

- metal plane

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0044—Mechanical working of the substrate, e.g. drilling or punching

- H05K3/0047—Drilling of holes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4857—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3157—Partial encapsulation or coating

- H01L23/3185—Partial encapsulation or coating the coating covering also the sidewalls of the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49833—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers the chip support structure consisting of a plurality of insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5386—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/552—Protection against radiation, e.g. light or electromagnetic waves

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0655—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/60—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation

- H01L2021/60007—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation involving a soldering or an alloying process

- H01L2021/60022—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation involving a soldering or an alloying process using bump connectors, e.g. for flip chip mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15192—Resurf arrangement of the internal vias

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/095—Conductive through-holes or vias

- H05K2201/096—Vertically aligned vias, holes or stacked vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/422—Plated through-holes or plated via connections characterised by electroless plating method; pretreatment therefor

Description

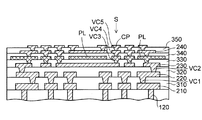

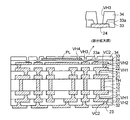

図2〜図12は実施形態の配線基板の製造方法を示す図、図13は実施形態の配線基板を示す図である。以下、配線基板の製造方法を説明しながら、配線基板の構造について説明する。

図7(a)に示すように、まず、図5の第2層間絶縁層32及び第2ビア導体VC2の上にシード層24aを形成する。シード層24aの好適な一例としては、スパッタ法により、厚みが20nm〜50nmのチタン(Ti)層24xを形成した後に、チタン層24xの上に無電解めっきにより厚みが0.5μmの銅(Cu)層24yを形成する。

Claims (11)

- 配線間隔が狭い配線部と、前記配線部よりも配線間隔が広い配線部とを備えた第1配線層と、

前記第1配線層の上に形成された第1絶縁層と、

前記配線間隔が狭い配線部上の第1絶縁層の上に形成された金属プレーン層と、

前記第1絶縁層及び前記金属プレーン層の上に形成された第2絶縁層と、

前記第2絶縁層の上面から前記第1配線層に到達する第1ビアホールと、

前記第1ビアホールに形成された第1ビア導体と、

前記第2絶縁層に形成され、前記金属プレーン層に到達する第2ビアホールと、

前記第2ビアホールに形成された第2ビア導体と、

前記第2絶縁層の上に形成され、前記第1ビア導体を介して前記第1配線層に接続される第2配線層と、

前記第2絶縁層の上に形成され、前記第2ビア導体を介して前記金属プレーン層に接続された第3配線層と、

前記第2配線層の上に形成された第3絶縁層と、

前記第3絶縁層に形成され、前記第2配線層に到達する第3ビアホールと、

前記第3ビアホールに形成された第3ビア導体と、

前記第3絶縁層の上に形成され、前記第3ビア導体を介して前記第2配線層に接続された第4配線層とを有し、

前記第2配線層はビア受けパッドであり、前記第2配線層の上下に配置された前記第1ビア導体と前記第3ビア導体とによってスタックドビア構造が構築されていることを特徴とする配線基板。 - 前記第1ビアホールが配置された領域において、前記第1絶縁層に開口部が形成されており、前記第1ビアホールは、前記第1絶縁層の開口部の内側に配置されていることを特徴とする請求項1に記載の配線基板。

- 前記配線基板は、

第1の多層配線層と、

前記第1の多層配線層の上に形成され、前記第1の多層配線層よりも配線ピッチが狭い第2の多層配線層とを備え、

前記第2の多層配線層が、前記第1配線層、前記金属プレーン層、前記第2配線層及び前記第3配線層を含むことを特徴とする請求項1又は2に記載の配線基板。 - 前記第2ビアホールの深さは、前記第1ビアホールの深さより浅いことを特徴とする請求項1乃至3のいずれか一項に記載の配線基板。

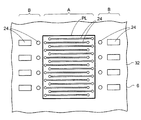

- 前記配線基板に複数の半導体素子搭載部が設けられており、前記第1配線層又は前記第2配線層が複数の半導体素子間を接続する配線を有することを特徴とする請求項1に記載の配線基板。

- 配線間隔が狭い配線部と、前記配線部よりも配線間隔が広い配線部とを備えた第1配線層を含む配線部材を用意する工程と、

前記第1配線層の接続部上に開口部が配置された第1絶縁層を形成する工程と、

前記配線間隔が狭い配線部上の第1絶縁層の上に金属プレーン層を形成する工程と、

前記第1絶縁層及び前記金属プレーン層の上に、前記第1絶縁層の開口部に第1ビアホールが配置され、前記金属プレーン層の上に第2ビアホールが配置された第2絶縁層を形成する工程と、

前記第2絶縁層の上に、前記第1ビアホール内の第1ビア導体を介して前記第1配線層に接続される第2配線層と、前記第2ビアホール内の第2ビア導体を介して前記金属プレーン層に接続される第3配線層とを形成する工程と

を有することを特徴とする配線基板の製造方法。 - 前記第2絶縁層を形成する工程において、

前記第1ビアホールは、前記第1絶縁層の開口部の内側に配置されることを特徴とする請求項6に記載の配線基板の製造方法。 - 前記第2配線層と前記第3配線層とを形成する工程の後に、

前記第2配線層及び第3配線層の上に第3絶縁層を形成する工程と、

前記第2配線層に到達する第3ビアホールを前記第3絶縁層に形成する工程と、

前記第3絶縁層の上に、前記第3ビアホール内の第3ビア導体を介して前記第2配線層に接続される第4配線層を形成する工程と

を有し、

前記第2配線層はビア受けパッドであり、前記第2配線層の上下に配置された前記第1ビア導体と前記第3ビア導体とによってスタックドビア構造が構築されることを特徴とする請求項6又は7に記載の配線基板の製造方法。 - 前記配線部材を用意する工程において、前記配線部材は前記第1配線層の下に第1の多層配線層を備えており、

前記第1配線層、前記金属プレーン層、前記第2配線層及び前記第3配線層を含んで第2の多層配線層が構築され、

前記第2の多層配線層は、前記第1の多層配線層よりも配線ピッチが狭いことを特徴とする請求項6又は7に記載の配線基板の製造方法。 - 前記第1配線層を形成する工程、及び前記第2配線層と前記第3配線層とを形成する工程において、シード層を異方性ドライエッチングによって除去するセミアディティブ法が使用され、

前記金属プレーン層を形成する工程は、

前記第1絶縁層の上に金属層を形成する工程と、

前記金属層をパターニングして下地層を形成する工程と、

無電解めっきにより前記下地層の上に金属めっき層を形成する工程とを含むことを特徴とする請求項6乃至9のいずれか一項に記載の配線基板の製造方法。 - 前記配線基板に複数の半導体素子搭載部が設けられ、前記第1配線層又は前記第2配線層が複数の半導体素子間を接続する配線を有することを特徴とする請求項6に記載の配線基板の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014122705A JP6332680B2 (ja) | 2014-06-13 | 2014-06-13 | 配線基板及びその製造方法 |

| US14/734,395 US9412687B2 (en) | 2014-06-13 | 2015-06-09 | Wiring substrate and method of manufacturing the same |

| US15/170,313 US9646926B2 (en) | 2014-06-13 | 2016-06-01 | Wiring substrate and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014122705A JP6332680B2 (ja) | 2014-06-13 | 2014-06-13 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016004833A JP2016004833A (ja) | 2016-01-12 |

| JP2016004833A5 JP2016004833A5 (ja) | 2017-02-09 |

| JP6332680B2 true JP6332680B2 (ja) | 2018-05-30 |

Family

ID=54836784

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014122705A Active JP6332680B2 (ja) | 2014-06-13 | 2014-06-13 | 配線基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9412687B2 (ja) |

| JP (1) | JP6332680B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6341714B2 (ja) | 2014-03-25 | 2018-06-13 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP6527420B2 (ja) * | 2015-07-31 | 2019-06-05 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| EP3430646B1 (en) * | 2016-03-16 | 2021-11-10 | INTEL Corporation | Stairstep interposers with integrated shielding for electronics packages |

| JP2019062092A (ja) * | 2017-09-27 | 2019-04-18 | イビデン株式会社 | プリント配線板 |

| CN110504275B (zh) * | 2018-05-17 | 2021-11-12 | 京东方科技集团股份有限公司 | 阵列基板及其制作方法、显示面板和显示装置 |

| US10888001B2 (en) | 2018-06-08 | 2021-01-05 | Unimicron Technology Corp. | Circuit carrier board structure and manufacturing method thereof |

| US11032917B2 (en) | 2018-06-08 | 2021-06-08 | Unimicron Technology Corp. | Circuit carrier board and manufacturing method thereof |

| TWI734945B (zh) * | 2018-12-12 | 2021-08-01 | 欣興電子股份有限公司 | 複合基板結構及其製作方法 |

| JP7142774B2 (ja) * | 2019-05-20 | 2022-09-27 | 三井金属鉱業株式会社 | キャリア付金属箔並びにその使用方法及び製造方法 |

| KR20220001568A (ko) * | 2020-06-30 | 2022-01-06 | 삼성전기주식회사 | 인쇄회로기판 |

| US20220051989A1 (en) * | 2020-08-12 | 2022-02-17 | Advanced Micro Devices, Inc. | Mixed density interconnect architectures using hybrid fan-out |

| WO2022264378A1 (ja) * | 2021-06-17 | 2022-12-22 | 昭和電工マテリアルズ株式会社 | 配線基板の製造方法及び積層板 |

| US20230073823A1 (en) * | 2021-09-09 | 2023-03-09 | Qualcomm Incorporated | Package comprising a substrate with high-density interconnects |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2998237B2 (ja) * | 1991-03-07 | 2000-01-11 | ソニー株式会社 | ブラインド孔の加工方法 |

| US5510758A (en) * | 1993-04-07 | 1996-04-23 | Matsushita Electric Industrial Co., Ltd. | Multilayer microstrip wiring board with a semiconductor device mounted thereon via bumps |

| US5635761A (en) * | 1994-12-14 | 1997-06-03 | International Business Machines, Inc. | Internal resistor termination in multi-chip module environments |

| JP3199592B2 (ja) * | 1995-01-27 | 2001-08-20 | 株式会社日立製作所 | 多層印刷回路基板 |

| JP2001203470A (ja) * | 2000-01-21 | 2001-07-27 | Toshiba Corp | 配線基板、半導体パッケージ、および半導体装置 |

| JP3582460B2 (ja) * | 2000-06-20 | 2004-10-27 | 株式会社村田製作所 | 高周波モジュール |

| JP2003023252A (ja) | 2001-07-10 | 2003-01-24 | Ibiden Co Ltd | 多層プリント配線板 |

| JP5191074B2 (ja) | 2001-07-10 | 2013-04-24 | イビデン株式会社 | 多層プリント配線板 |

| JP2002329976A (ja) * | 2001-04-26 | 2002-11-15 | Kyocera Corp | 多層配線基板 |

| JP4195883B2 (ja) * | 2004-02-04 | 2008-12-17 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 多層モジュール |

| JP2007165642A (ja) * | 2005-12-14 | 2007-06-28 | Mitsubishi Electric Corp | 部品実装用基板 |

| US7820233B2 (en) * | 2006-09-27 | 2010-10-26 | Unimicron Technology Corp. | Method for fabricating a flip chip substrate structure |

| JP4978269B2 (ja) * | 2007-03-27 | 2012-07-18 | 日本電気株式会社 | 多層配線基板 |

| JP5649490B2 (ja) * | 2011-03-16 | 2015-01-07 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| KR102134933B1 (ko) * | 2012-08-31 | 2020-07-16 | 소니 주식회사 | 배선 기판 및 배선 기판의 제조 방법 |

| JP6013960B2 (ja) * | 2013-03-28 | 2016-10-25 | 京セラ株式会社 | 配線基板 |

| JP2014229698A (ja) * | 2013-05-21 | 2014-12-08 | イビデン株式会社 | 配線板及び配線板の製造方法 |

-

2014

- 2014-06-13 JP JP2014122705A patent/JP6332680B2/ja active Active

-

2015

- 2015-06-09 US US14/734,395 patent/US9412687B2/en active Active

-

2016

- 2016-06-01 US US15/170,313 patent/US9646926B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016004833A (ja) | 2016-01-12 |

| US9412687B2 (en) | 2016-08-09 |

| US20150364405A1 (en) | 2015-12-17 |

| US9646926B2 (en) | 2017-05-09 |

| US20160276259A1 (en) | 2016-09-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6332680B2 (ja) | 配線基板及びその製造方法 | |

| JP6539992B2 (ja) | 配線回路基板、半導体装置、配線回路基板の製造方法、半導体装置の製造方法 | |

| JP6358431B2 (ja) | 電子部品装置及びその製造方法 | |

| TWI670803B (zh) | 中介層、半導體裝置、中介層的製造方法及半導體裝置的製造方法 | |

| JP6418757B2 (ja) | 配線基板及びその製造方法と半導体装置 | |

| JP2014154800A (ja) | 配線基板及びその製造方法 | |

| JP5547615B2 (ja) | 配線基板、半導体装置及び配線基板の製造方法 | |

| TWI543676B (zh) | 印刷電路板及其製造方法 | |

| JP6566726B2 (ja) | 配線基板、及び、配線基板の製造方法 | |

| US9392684B2 (en) | Wiring substrate and method for manufacturing wiring substrate | |

| JP6316609B2 (ja) | 配線基板及び半導体装置と配線基板の製造方法及び半導体装置の製造方法 | |

| US9324580B2 (en) | Process for fabricating a circuit substrate | |

| JP5509508B2 (ja) | 電子部品及び電子部品の製造方法 | |

| JP6660850B2 (ja) | 電子部品内蔵基板及びその製造方法と電子部品装置 | |

| JP2015165533A5 (ja) | ||

| JP4841806B2 (ja) | キャパシタ装置とそれを備えた半導体装置、及びキャパシタ装置の製造方法 | |

| JP6619294B2 (ja) | 配線基板及びその製造方法と電子部品装置 | |

| KR20110112974A (ko) | 패키지 기판 및 그의 제조방법 | |

| JP2009135147A (ja) | 配線基板及び電子素子の接続構造及び電子装置 | |

| JP4759981B2 (ja) | 電子部品内蔵モジュールの製造方法 | |

| JP2016219730A (ja) | 電子部品内蔵基板及びその製造方法と電子装置 | |

| KR102521788B1 (ko) | 딥 캐비티 구조의 다층 인쇄회로기판 제조 방법 | |

| JP5363377B2 (ja) | 配線基板及びその製造方法 | |

| JP2006049762A (ja) | 部品内蔵基板及び部品内蔵基板の製造方法 | |

| JP5825111B2 (ja) | シリコンインターポーザ及びそれを用いる半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170927 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180112 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180403 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180418 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6332680 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |