JP6151650B2 - 記憶装置 - Google Patents

記憶装置 Download PDFInfo

- Publication number

- JP6151650B2 JP6151650B2 JP2014007265A JP2014007265A JP6151650B2 JP 6151650 B2 JP6151650 B2 JP 6151650B2 JP 2014007265 A JP2014007265 A JP 2014007265A JP 2014007265 A JP2014007265 A JP 2014007265A JP 6151650 B2 JP6151650 B2 JP 6151650B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- memory

- storage device

- switch

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 claims description 143

- 230000008859 change Effects 0.000 claims description 66

- 239000000463 material Substances 0.000 claims description 18

- 229910052798 chalcogen Inorganic materials 0.000 claims description 13

- 150000001787 chalcogens Chemical class 0.000 claims description 13

- 239000011669 selenium Substances 0.000 claims description 12

- 229910052751 metal Inorganic materials 0.000 claims description 11

- 229910052760 oxygen Inorganic materials 0.000 claims description 11

- 239000001301 oxygen Substances 0.000 claims description 11

- 239000002184 metal Substances 0.000 claims description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 8

- 150000004767 nitrides Chemical class 0.000 claims description 8

- 229910052710 silicon Inorganic materials 0.000 claims description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 7

- 239000011777 magnesium Substances 0.000 claims description 7

- 239000010703 silicon Substances 0.000 claims description 7

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 claims description 6

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 claims description 6

- 229910052711 selenium Inorganic materials 0.000 claims description 6

- 229910052717 sulfur Inorganic materials 0.000 claims description 6

- 239000011593 sulfur Substances 0.000 claims description 6

- 229910052714 tellurium Inorganic materials 0.000 claims description 6

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 claims description 6

- 229910052782 aluminium Inorganic materials 0.000 claims description 5

- 230000003247 decreasing effect Effects 0.000 claims description 5

- 229910052755 nonmetal Inorganic materials 0.000 claims description 5

- 229910052761 rare earth metal Inorganic materials 0.000 claims description 5

- 229910052733 gallium Inorganic materials 0.000 claims description 4

- 229910052749 magnesium Inorganic materials 0.000 claims description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 claims description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 3

- 229910052787 antimony Inorganic materials 0.000 claims description 3

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 claims description 3

- 229910052785 arsenic Inorganic materials 0.000 claims description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 claims description 3

- 229910052732 germanium Inorganic materials 0.000 claims description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 3

- 229910052735 hafnium Inorganic materials 0.000 claims description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 3

- 229910000314 transition metal oxide Inorganic materials 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 228

- 150000002500 ions Chemical class 0.000 description 23

- 238000010586 diagram Methods 0.000 description 12

- 238000002474 experimental method Methods 0.000 description 10

- 150000004770 chalcogenides Chemical class 0.000 description 9

- 230000007423 decrease Effects 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- -1 GeTe Chemical class 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 230000005684 electric field Effects 0.000 description 6

- 238000000034 method Methods 0.000 description 6

- 239000010949 copper Substances 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 229910004298 SiO 2 Inorganic materials 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 229910052723 transition metal Inorganic materials 0.000 description 3

- 229910005900 GeTe Inorganic materials 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000002457 bidirectional effect Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000014759 maintenance of location Effects 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910000618 GeSbTe Inorganic materials 0.000 description 1

- 229910005866 GeSe Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000008034 disappearance Effects 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000001556 precipitation Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000006722 reduction reaction Methods 0.000 description 1

- 238000013341 scale-up Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000007847 structural defect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/20—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes

- H10B63/24—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having two electrodes, e.g. diodes of the Ovonic threshold switching type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

- H10N70/245—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies the species being metal cations, e.g. programmable metallization cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/841—Electrodes

- H10N70/8416—Electrodes adapted for supplying ionic species

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8822—Sulfides, e.g. CuS

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8825—Selenides, e.g. GeSe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8828—Tellurides, e.g. GeSbTe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8833—Binary metal oxides, e.g. TaOx

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

Landscapes

- Semiconductor Memories (AREA)

- Mram Or Spin Memory Techniques (AREA)

Description

1.実施の形態(スイッチ層をOTS層と高抵抗層との積層構造とした例)

1−1.スイッチ素子

1−2.記憶装置

2.実施例

(1−1.スイッチ素子)

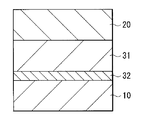

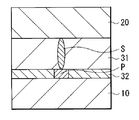

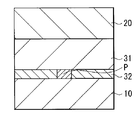

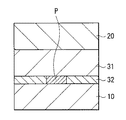

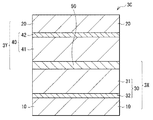

図1は、本開示の一実施の形態に係るスイッチ素子1Aの断面構成を表したものである。このスイッチ素子1Aは、例えば図8に示した、所謂クロスポイントアレイ構造を有するメモリセルアレイ2において複数配設されたうちの任意の記憶素子(記憶素子3Y;図8)を選択的に動作させるためのものである。スイッチ素子1A(スイッチ素子3X;図8)は、記憶素子3Y(具体的には記憶層40)に直列に接続されており、下部電極10(第1電極)、スイッチ層30および上部電極20(第2電極)をこの順に有するものである。

記憶装置(メモリ)は、後述する記憶素子3Yを多数、例えば列状やマトリクス状に配列することにより構成することができる。このとき、本開示のスイッチ素子1Aは、スイッチ素子3Xとして、記憶素子3Yと直列に接続されており、これによりメモリセル3を構成している。メモリセル3は、配線を介してセンスアンプ,アドレスデコーダおよび書き込み・消去・読み出し回路等に接続される。

非選択時のリーク電流が大きいと非選択のメモリセルで誤書き込みを生じる虞がある。よって、書き込み動作では、記憶素子3Yを書き込む際に必要な電流が得られる電圧に書き込み電圧Vwriteを設定したうえで、Vwrite/2にバイアスされた非選択のメモリセルが誤書き込みを生じない程度のリーク電流に抑える必要がある。Vwrite/2にバイアスさ

れた非選択時のリーク電流が小さければ小さいほど大規模なクロスポイントアレイを誤書き込みなく動作させることができる。従って、書き込み動作時もスイッチ素子3Xの選択比を大きくすることが、メモリセルアレイの大容量化につながる。

以下、本開示の具体的な実施例について説明する。

まず、TiNよりなる下部電極10を逆スパッタによってクリーニングしたのち、TiN上にSiO2膜を2nmの膜厚に形成して高抵抗層32とする。次に、OTS層31と

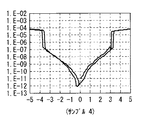

してGeTe膜を40nmの膜厚で形成したのち、Wを30nmの膜厚で形成して上部電極20とした。続いて、フォトリソグラフィやドライエッチングなどの公知の技術を用いて素子サイズが100nmφとなるように微細加工を行い、スイッチ素子1A(サンプル1)を作製した。また、比較例として、高抵抗層32を形成していないスイッチ素子100(サンプル2)を作製した。これらサンプル1およびサンプル2の印加電圧と各電極に流れる電流値との関係を測定し、そのIV特性を図12に示した。

次に、OTS層31として40nmの厚みのMgTeBO膜を、高抵抗層32として2nmの厚みのSiO2膜を形成し、スイッチ素子1A(サンプル3)を作製した。同様に、OTS層31として40nmの厚みのMgTeBO膜を、高抵抗層32として5nmの厚みのSiN膜を形成したスイッチ素子1A(サンプル4)を作製した。この他、比較のために電極間にMgTeBO膜からなるOTS層31のみを形成(高抵抗層32は未形成)したスイッチ素子100(サンプル5)を作製した。これらサンプル3〜5のIV特性を図13A(サンプル3),図13B(サンプル4),図13C(サンプル5)に示した。

たサンプル3よりもSiNを用いたサンプル4の方が、閾値電圧が高くリーク電流が小さかった。これは、SiO2およびSiNの膜厚や成膜条件によって適宜制御することがで

きる。

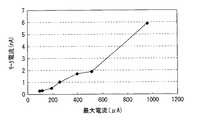

次に、サンプル3を用いて最大印加電圧を6V一定とし、スイッチ素子1Aに直列に接続されている抵抗値を変化(5kΩ,12.5kΩ,50kΩ)させることにより最大電流値を変化させた。図15は各抵抗値における正バイアスのIV曲線を示したものである。スイッチ素子1Aに流れる最大電流値が変化することにより、リーク電流と閾値電圧が変化することがわかった。次に、これらの測定から求めたサンプル3に流す最大電流とリーク電流との関係および最大電流と閾値電圧との関係を図16A,図16Bに示した。なお、リーク電流の定義は正バイアス0.5Vの電流とした。

(1)第1電極および前記第1電極に対向配置された第2電極と、前記第1電極と前記第2電極との間に設けられたスイッチ層とを有し、前記スイッチ層は、カルコゲン元素を含む第1層と、高抵抗材料を含む第2層とを備えたスイッチ素子。

(2)前記第2層は前記第1層の少なくとも一方の面に接して設けられている、前記(1)に記載のスイッチ素子。

(3)前記第1層は酸素(O),硫黄(S),セレン(Se)およびテルル(Te)のうちの少なくとも1種を含んでいる、前記(1)または(2)に記載のスイッチ素子。

(4)前記第1層はさらに、ゲルマニウム(Ge),アンチモン(Sb),ケイ素(Si),ヒ素(As)のうちの少なくとも1種を含んでいる、前記(3)に記載のスイッチ素子。

(5)前記第2層は金属元素または非金属元素の酸化物あるいは窒化物を含む、前記(1)乃至(4)のうちのいずれか1つに記載のスイッチ素子。

(6)前記金属元素はアルミニウム(Al),ガリウム(Ga),マグネシウム(Mg),ケイ素(Si),ハフニウム(Hf)および希土類元素のうちの少なくとも1種である、前記(5)に記載のスイッチ素子。

(7)前記第1層は、印加電圧を所定の閾値電圧以上とすることにより低抵抗状態に、該閾値電圧以下に減少させることにより高抵抗状態に変化する、前記(1)乃至(6)のうちのいずれか1つに記載のスイッチ素子。

(8)前記第2層は層内に伝導パスを有する、前記(1)乃至(7)のうちのいずれか1つに記載のスイッチ素子。

(9)前記第2層の抵抗値は前記第1層よりも高い、前記(8)に記載のスイッチ素子。

(10)記憶素子および該記憶素子に直接接続されたスイッチ素子を含むメモリセルを複数備え、前記スイッチ素子は、第1電極および前記第1電極に対向配置された第2電極と、前記第1電極と前記第2電極との間に設けられたスイッチ層とを有し、前記スイッチ層は、カルコゲン元素を含む第1層と、高抵抗材料を含む第2層とを備えた記憶装置。

(11)前記記憶素子は前記スイッチ素子の前記第1電極および前記第2電極間に記憶層を有する、前記(10)に記載の記憶装置。

(12)前記記憶層はテルル(Te),硫黄(S)およびセレン(Se)から選ばれる少なくとも1種のカルコゲン元素を含むイオン源層と、抵抗変化層とを含む、前記(11)に記載の記憶装置。

(13)前記記憶層および前記スイッチ層は前記第1電極と前記第2電極との間に第3電極を介して積層されている、前記(11)または(12)に記載の記憶装置。

(14)前記記憶層および前記スイッチ層は前記第2層を介して積層されている、前記(12)または(13)に記載の記憶装置。

(15)前記記憶層および前記スイッチ層は前記抵抗変化層を介して積層されている、前記(12)乃至(14)のいずれか1つに記載の記憶装置。

(16)前記スイッチ層の前記第2層は、前記記憶層の前記抵抗変化層を兼ねている、前記(12)乃至(15)のいずれか1つに記載の記憶装置。

(17)複数の行ラインおよび複数の列ラインを有し、前記複数の行ラインと複数の列ラインとの各交差領域付近に前記メモリセルが配置されている、前記(10)乃至(16)のいずれか1つに記載の記憶装置。

(18)前記記憶層は、遷移金属酸化物からなる抵抗変化層、相変化型メモリ層、磁気抵抗変化型メモリ層のいずれかである、前記(11)乃至(17)のいずれか1つに記載の記憶装置。

(19)前記スイッチ素子は、オボニック閾値スイッチ素子である、前記(10)乃至(18)のいずれか1つに記載の記憶装置。

(20)前記記憶素子は、書き込み閾値電圧が1.5V以上である、前記(10)乃至(19)のいずれか1つに記載の記憶装置。

Claims (15)

- 記憶素子および該記憶素子に接続されたスイッチ素子を含むメモリセルを複数備え、

前記スイッチ素子は、第1電極および前記第1電極に対向配置された第2電極と、前記第1電極と前記第2電極との間に設けられると共に、カルコゲン元素を含む第1層と高抵抗材料を含む第2層とを備えたスイッチ層とを有し、

前記記憶素子は、前記スイッチ素子の前記第1電極と前記第2電極との間に、テルル(Te),硫黄(S)およびセレン(Se)から選ばれる少なくとも1種のカルコゲン元素を含むイオン源層と、抵抗変化層とを含む記憶層を有し、

前記スイッチ層の前記第2層は、前記記憶層の前記抵抗変化層を兼ねている

記憶装置。 - 前記第2層は前記第1層の少なくとも一方の面に接して設けられている、請求項1に記載の記憶装置。

- 前記第1層は酸素(O),硫黄(S),セレン(Se)およびテルル(Te)のうちの少なくとも1種を含んでいる、請求項1に記載の記憶装置。

- 前記第1層はさらに、ゲルマニウム(Ge),アンチモン(Sb),ケイ素(Si),ヒ素(As)のうちの少なくとも1種を含んでいる、請求項3に記載の記憶装置。

- 前記第2層は金属元素または非金属元素の酸化物あるいは窒化物を含む、請求項1に記載の記憶装置。

- 前記金属元素はアルミニウム(Al),ガリウム(Ga),マグネシウム(Mg),ケイ素(Si),ハフニウム(Hf)および希土類元素のうちの少なくとも1種である、請求項5に記載の記憶装置。

- 前記第1層は、印加電圧を所定の閾値電圧以上とすることにより低抵抗状態に、該所定の閾値電圧未満に減少させることにより高抵抗状態に変化する、請求項1に記載の記憶装置。

- 前記第2層は層内に伝導パスを有する、請求項1に記載の記憶装置。

- 前記第2層の抵抗値は前記第1層よりも高い、請求項1に記載の記憶装置。

- 前記記憶層および前記スイッチ層は前記第2層を介して積層されている、請求項1に記載の記憶装置。

- 前記記憶層および前記スイッチ層は前記抵抗変化層を介して積層されている、請求項1に記載の記憶装置。

- 複数の行ラインおよび複数の列ラインを有し、前記複数の行ラインと複数の列ラインとの各交差領域付近に前記メモリセルが配置されている、請求項1に記載の記憶装置。

- 前記記憶層は、遷移金属酸化物からなる抵抗変化層、相変化型メモリ層、磁気抵抗変化型メモリ層のいずれかである、請求項1に記載の記憶装置。

- 前記スイッチ素子は、オボニック閾値スイッチ素子である、請求項1に記載の記憶装置。

- 前記記憶素子は、書き込み閾値電圧が1.5V以上である、請求項1に記載の記憶装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014007265A JP6151650B2 (ja) | 2014-01-17 | 2014-01-17 | 記憶装置 |

| TW103144866A TWI661535B (zh) | 2014-01-17 | 2014-12-22 | 切換裝置及儲存單元 |

| US14/590,014 US9543512B2 (en) | 2014-01-17 | 2015-01-06 | Switch device and storage unit |

| KR1020150003278A KR102356740B1 (ko) | 2014-01-17 | 2015-01-09 | 스위치 소자 및 기억 장치 |

| US15/379,209 US20170098683A1 (en) | 2014-01-17 | 2016-12-14 | Switch device and storage unit |

| US15/379,390 US20170098684A1 (en) | 2014-01-17 | 2016-12-14 | Switch device and storage unit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014007265A JP6151650B2 (ja) | 2014-01-17 | 2014-01-17 | 記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015135917A JP2015135917A (ja) | 2015-07-27 |

| JP2015135917A5 JP2015135917A5 (ja) | 2016-04-14 |

| JP6151650B2 true JP6151650B2 (ja) | 2017-06-21 |

Family

ID=53545587

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014007265A Expired - Fee Related JP6151650B2 (ja) | 2014-01-17 | 2014-01-17 | 記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US9543512B2 (ja) |

| JP (1) | JP6151650B2 (ja) |

| KR (1) | KR102356740B1 (ja) |

| TW (1) | TWI661535B (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10373653B2 (en) | 2017-06-13 | 2019-08-06 | Samsung Electronics Co., Ltd. | Semiconductor device having first memory section and second memory section stacked vertically on each other |

| US10861902B2 (en) | 2017-06-13 | 2020-12-08 | Samsung Electronics Co., Ltd. | Semiconductor device having magnetic tunnel junction pattern |

| US12102012B2 (en) | 2021-03-12 | 2024-09-24 | Kioxia Corporation | Magnetoresistance memory device and method of manufacturing magnetoresistance memory device |

Families Citing this family (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8884261B2 (en) | 2010-08-23 | 2014-11-11 | Crossbar, Inc. | Device switching using layered device structure |

| US9685608B2 (en) | 2012-04-13 | 2017-06-20 | Crossbar, Inc. | Reduced diffusion in metal electrode for two-terminal memory |

| US9741765B1 (en) | 2012-08-14 | 2017-08-22 | Crossbar, Inc. | Monolithically integrated resistive memory using integrated-circuit foundry compatible processes |

| JP6151650B2 (ja) * | 2014-01-17 | 2017-06-21 | ソニーセミコンダクタソリューションズ株式会社 | 記憶装置 |

| US10290801B2 (en) * | 2014-02-07 | 2019-05-14 | Crossbar, Inc. | Scalable silicon based resistive memory device |

| US9716225B2 (en) | 2014-09-03 | 2017-07-25 | Micron Technology, Inc. | Memory cells including dielectric materials, memory devices including the memory cells, and methods of forming same |

| CN107533862B (zh) * | 2015-08-07 | 2021-04-13 | 慧与发展有限责任合伙企业 | 交叉阵列、图像处理器及计算设备 |

| CN105514136A (zh) * | 2016-01-26 | 2016-04-20 | 上海新储集成电路有限公司 | 三维阻变存储器的制备方法 |

| JP6567441B2 (ja) * | 2016-02-09 | 2019-08-28 | 株式会社東芝 | 超格子メモリ及びクロスポイント型メモリ装置 |

| US9741764B1 (en) | 2016-02-22 | 2017-08-22 | Samsung Electronics Co., Ltd. | Memory device including ovonic threshold switch adjusting threshold voltage thereof |

| KR101854023B1 (ko) * | 2016-02-23 | 2018-05-02 | 연세대학교 산학협력단 | 비선형 스위치 소자, 이의 제조 방법 및 이를 포함하는 비휘발성 메모리 소자 |

| KR102453349B1 (ko) | 2016-02-25 | 2022-10-07 | 삼성전자주식회사 | 가변 저항 메모리 장치 및 이의 제조 방법 |

| KR102578481B1 (ko) * | 2016-03-15 | 2023-09-14 | 삼성전자주식회사 | 반도체 메모리 소자 및 이의 제조방법 |

| KR102495000B1 (ko) * | 2016-03-18 | 2023-02-02 | 삼성전자주식회사 | 반도체 소자 및 이의 제조방법 |

| KR102483704B1 (ko) * | 2016-03-30 | 2023-01-02 | 삼성전자주식회사 | 가변 저항 메모리 장치 및 그 제조 방법 |

| KR101889600B1 (ko) * | 2016-03-31 | 2018-08-17 | 연세대학교 산학협력단 | 비휘발성 메모리 소자 및 이의 제조 방법 |

| JP2017224688A (ja) | 2016-06-14 | 2017-12-21 | ソニー株式会社 | 回路素子、記憶装置、電子機器、回路素子への情報の書き込み方法、および回路素子からの情報の読み出し方法 |

| KR102530067B1 (ko) * | 2016-07-28 | 2023-05-08 | 삼성전자주식회사 | 가변 저항 메모리 소자 및 그 제조 방법 |

| KR102584288B1 (ko) | 2016-08-03 | 2023-09-27 | 삼성전자주식회사 | 비휘발성 메모리 장치 |

| WO2018057012A1 (en) * | 2016-09-23 | 2018-03-29 | Intel Corporation | Threshold switching selector based memory |

| JP7079201B2 (ja) * | 2016-10-04 | 2022-06-01 | ソニーセミコンダクタソリューションズ株式会社 | スイッチ素子および記憶装置ならびにメモリシステム |

| US10658588B2 (en) * | 2017-04-06 | 2020-05-19 | Sony Corporation | Memory cell switch device |

| US10672833B2 (en) | 2017-07-26 | 2020-06-02 | Micron Technology, Inc. | Semiconductor devices including a passive material between memory cells and conductive access lines, and related electronic devices |

| KR102465179B1 (ko) | 2018-01-18 | 2022-11-08 | 에스케이하이닉스 주식회사 | 선택 소자, 이의 제조 방법 및 이를 포함하는 비휘발성 메모리 소자 |

| US11024372B2 (en) * | 2018-08-13 | 2021-06-01 | Micron Technology, Inc. | Segregation-based memory |

| KR102630031B1 (ko) * | 2018-10-05 | 2024-01-30 | 삼성전자주식회사 | 가변 저항 메모리 장치 |

| KR20200041031A (ko) | 2018-10-11 | 2020-04-21 | 삼성전자주식회사 | 가변 저항 메모리 소자 |

| KR102130219B1 (ko) * | 2018-10-30 | 2020-07-03 | 연세대학교 산학협력단 | 비선형 스위치 소자, 이의 제조 방법 및 이를 포함하는 비휘발성 메모리 소자 |

| JP2021103749A (ja) | 2019-12-25 | 2021-07-15 | キオクシア株式会社 | 抵抗変化素子 |

| US11271155B2 (en) * | 2020-03-10 | 2022-03-08 | International Business Machines Corporation | Suppressing oxidation of silicon germanium selenium arsenide material |

| CN111584710B (zh) * | 2020-04-10 | 2023-09-26 | 中国科学院上海微系统与信息技术研究所 | 一种ots材料、选通器单元及其制备方法 |

| JP2022051104A (ja) | 2020-09-18 | 2022-03-31 | キオクシア株式会社 | スイッチング素子 |

| CN114242748A (zh) * | 2021-12-20 | 2022-03-25 | 厦门半导体工业技术研发有限公司 | 一种存储单元组及其制造方法 |

| JP2023137900A (ja) * | 2022-03-18 | 2023-09-29 | キオクシア株式会社 | スイッチング素子及び記憶装置 |

| WO2024219141A1 (ja) * | 2023-04-20 | 2024-10-24 | 国立大学法人東北大学 | 抵抗変化材料、スイッチ素子用材料、スイッチ層、スイッチ素子及び記憶装置 |

| WO2024219142A1 (ja) * | 2023-04-20 | 2024-10-24 | 国立大学法人東北大学 | 抵抗変化材料、スイッチ素子用材料、スイッチ層、スイッチ素子及び記憶装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6806526B2 (en) * | 2001-08-13 | 2004-10-19 | Advanced Micro Devices, Inc. | Memory device |

| US7687830B2 (en) * | 2004-09-17 | 2010-03-30 | Ovonyx, Inc. | Phase change memory with ovonic threshold switch |

| US7646630B2 (en) * | 2004-11-08 | 2010-01-12 | Ovonyx, Inc. | Programmable matrix array with chalcogenide material |

| US20080042119A1 (en) * | 2005-08-09 | 2008-02-21 | Ovonyx, Inc. | Multi-layered chalcogenide and related devices having enhanced operational characteristics |

| US7414883B2 (en) * | 2006-04-20 | 2008-08-19 | Intel Corporation | Programming a normally single phase chalcogenide material for use as a memory or FPLA |

| DE602006012825D1 (de) * | 2006-07-27 | 2010-04-22 | St Microelectronics Srl | Phasenwechsel-Speichervorrichtung |

| US20100165716A1 (en) | 2008-12-30 | 2010-07-01 | Stmicroelectronics S.R.L. | Nonvolatile memory with ovonic threshold switches |

| US7983065B2 (en) * | 2009-04-08 | 2011-07-19 | Sandisk 3D Llc | Three-dimensional array of re-programmable non-volatile memory elements having vertical bit lines |

| JP5420436B2 (ja) * | 2010-01-15 | 2014-02-19 | 株式会社日立製作所 | 不揮発性記憶装置およびその製造方法 |

| JP2012019042A (ja) * | 2010-07-07 | 2012-01-26 | Sony Corp | 記憶素子および記憶装置 |

| KR101699713B1 (ko) * | 2011-09-14 | 2017-01-26 | 인텔 코포레이션 | 저항 변화 메모리 소자용 전극 |

| JP6151650B2 (ja) * | 2014-01-17 | 2017-06-21 | ソニーセミコンダクタソリューションズ株式会社 | 記憶装置 |

| US9716225B2 (en) * | 2014-09-03 | 2017-07-25 | Micron Technology, Inc. | Memory cells including dielectric materials, memory devices including the memory cells, and methods of forming same |

-

2014

- 2014-01-17 JP JP2014007265A patent/JP6151650B2/ja not_active Expired - Fee Related

- 2014-12-22 TW TW103144866A patent/TWI661535B/zh not_active IP Right Cessation

-

2015

- 2015-01-06 US US14/590,014 patent/US9543512B2/en not_active Expired - Fee Related

- 2015-01-09 KR KR1020150003278A patent/KR102356740B1/ko active IP Right Grant

-

2016

- 2016-12-14 US US15/379,209 patent/US20170098683A1/en not_active Abandoned

- 2016-12-14 US US15/379,390 patent/US20170098684A1/en not_active Abandoned

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10373653B2 (en) | 2017-06-13 | 2019-08-06 | Samsung Electronics Co., Ltd. | Semiconductor device having first memory section and second memory section stacked vertically on each other |

| US10861902B2 (en) | 2017-06-13 | 2020-12-08 | Samsung Electronics Co., Ltd. | Semiconductor device having magnetic tunnel junction pattern |

| US11361798B2 (en) | 2017-06-13 | 2022-06-14 | Samsung Electronics Co., Ltd. | Semiconductor device |

| US11557631B2 (en) | 2017-06-13 | 2023-01-17 | Samsung Electronics Co., Ltd. | Semiconductor device having first memory section and second memory section |

| US12102012B2 (en) | 2021-03-12 | 2024-09-24 | Kioxia Corporation | Magnetoresistance memory device and method of manufacturing magnetoresistance memory device |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201535680A (zh) | 2015-09-16 |

| JP2015135917A (ja) | 2015-07-27 |

| TWI661535B (zh) | 2019-06-01 |

| US20170098683A1 (en) | 2017-04-06 |

| US20170098684A1 (en) | 2017-04-06 |

| KR102356740B1 (ko) | 2022-01-28 |

| US9543512B2 (en) | 2017-01-10 |

| US20150207066A1 (en) | 2015-07-23 |

| KR20150086182A (ko) | 2015-07-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6151650B2 (ja) | 記憶装置 | |

| KR102488896B1 (ko) | 스위치 소자 및 기억 장치 | |

| US9136468B2 (en) | Nonvolatile semiconductor memory device | |

| US9025369B2 (en) | Resistance change nonvolatile semiconductor memory device | |

| US8759806B2 (en) | Semiconductor memory device | |

| JP2015135917A5 (ja) | ||

| US9019777B2 (en) | Nonvolatile semiconductor memory device and operating method of the same | |

| KR102507303B1 (ko) | 메모리 소자 | |

| US8586978B2 (en) | Non-volatile memory device including diode-storage node and cross-point memory array including the non-volatile memory device | |

| JPWO2016158430A1 (ja) | スイッチ素子および記憶装置 | |

| JP6787785B2 (ja) | スイッチ素子および記憶装置 | |

| KR102465179B1 (ko) | 선택 소자, 이의 제조 방법 및 이를 포함하는 비휘발성 메모리 소자 | |

| US20210036221A1 (en) | Switching device and storage unit, and memory system | |

| US11522132B2 (en) | Storage device and storage unit with a chalcogen element | |

| JPWO2018190071A1 (ja) | 記憶装置 | |

| JP2010278275A (ja) | 半導体記憶装置 | |

| TWI733520B (zh) | 記憶胞、記憶體裝置以及使用記憶胞的選擇器元件來放大資料的方法 | |

| KR20200048751A (ko) | 비선형 스위치 소자, 이의 제조 방법 및 이를 포함하는 비휘발성 메모리 소자 | |

| KR20240115515A (ko) | 가변 저항 메모리 소자 및 그 제조 방법 | |

| Qureshi et al. | Next Generation Memory Technologies |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160224 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160224 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20160720 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20160721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170419 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170502 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170525 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6151650 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |