JP6110975B2 - 積層構造体、及びその作製方法 - Google Patents

積層構造体、及びその作製方法 Download PDFInfo

- Publication number

- JP6110975B2 JP6110975B2 JP2016053949A JP2016053949A JP6110975B2 JP 6110975 B2 JP6110975 B2 JP 6110975B2 JP 2016053949 A JP2016053949 A JP 2016053949A JP 2016053949 A JP2016053949 A JP 2016053949A JP 6110975 B2 JP6110975 B2 JP 6110975B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- oxide semiconductor

- gate insulating

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 17

- 239000004065 semiconductor Substances 0.000 claims description 224

- 239000001257 hydrogen Substances 0.000 claims description 91

- 229910052739 hydrogen Inorganic materials 0.000 claims description 91

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 81

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 48

- 238000010438 heat treatment Methods 0.000 claims description 42

- 238000000034 method Methods 0.000 claims description 41

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 39

- 239000001301 oxygen Substances 0.000 claims description 39

- 229910052760 oxygen Inorganic materials 0.000 claims description 39

- 229910052757 nitrogen Inorganic materials 0.000 claims description 24

- 229910052738 indium Inorganic materials 0.000 claims description 6

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 4

- 239000000758 substrate Substances 0.000 description 71

- 239000011229 interlayer Substances 0.000 description 36

- 230000015654 memory Effects 0.000 description 36

- 239000000463 material Substances 0.000 description 35

- 239000003990 capacitor Substances 0.000 description 21

- 239000002585 base Substances 0.000 description 20

- 229910007541 Zn O Inorganic materials 0.000 description 18

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 16

- 230000015572 biosynthetic process Effects 0.000 description 15

- 239000013078 crystal Substances 0.000 description 15

- 239000007789 gas Substances 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 14

- 239000004973 liquid crystal related substance Substances 0.000 description 13

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 229910052710 silicon Inorganic materials 0.000 description 12

- 239000010703 silicon Substances 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 238000004458 analytical method Methods 0.000 description 11

- 125000004430 oxygen atom Chemical group O* 0.000 description 11

- 238000004544 sputter deposition Methods 0.000 description 11

- 238000010586 diagram Methods 0.000 description 10

- 150000002431 hydrogen Chemical class 0.000 description 10

- 238000009826 distribution Methods 0.000 description 9

- 239000010410 layer Substances 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- NWAIGJYBQQYSPW-UHFFFAOYSA-N azanylidyneindigane Chemical compound [In]#N NWAIGJYBQQYSPW-UHFFFAOYSA-N 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 239000011701 zinc Substances 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- 125000004429 atom Chemical group 0.000 description 6

- 238000000151 deposition Methods 0.000 description 6

- 230000008021 deposition Effects 0.000 description 6

- 229910052733 gallium Inorganic materials 0.000 description 6

- 239000011521 glass Substances 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- 239000000969 carrier Substances 0.000 description 5

- 239000011734 sodium Substances 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 230000005669 field effect Effects 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 239000010453 quartz Substances 0.000 description 4

- 229910019092 Mg-O Inorganic materials 0.000 description 3

- 229910019395 Mg—O Inorganic materials 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 238000001678 elastic recoil detection analysis Methods 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- 229910052748 manganese Inorganic materials 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 238000004611 spectroscopical analysis Methods 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000003795 desorption Methods 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 229910001195 gallium oxide Inorganic materials 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 229910000476 molybdenum oxide Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- PQQKPALAQIIWST-UHFFFAOYSA-N oxomolybdenum Chemical compound [Mo]=O PQQKPALAQIIWST-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 238000011282 treatment Methods 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910018657 Mn—Al Inorganic materials 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- 241001591005 Siga Species 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 238000011276 addition treatment Methods 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000002294 plasma sputter deposition Methods 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H01L29/7869—

Landscapes

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Electrodes Of Semiconductors (AREA)

- Liquid Crystal (AREA)

Description

路に搭載されるパワーデバイス、メモリ、サイリスタ、コンバータ、イメージセンサなど

を含む半導体集積回路、液晶表示装置に代表される電気光学装置、発光素子を有する発光

表示装置などを部品として搭載した電子機器に関する。

般を指し、電気光学装置、発光表示装置、半導体回路および電子機器は全て半導体装置で

ある。

モルファスシリコン、多結晶シリコンなどによって構成されている。アモルファスシリコ

ンを用いたトランジスタは電界効果移動度が低いもののガラス基板の大面積化に対応する

ことができる。また、多結晶シリコンを用いたトランジスタの電界効果移動度は高いがガ

ラス基板の大面積化には適していないという欠点を有している。

製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導

体として、酸化亜鉛、In−Ga−Zn−O系酸化物を用いてトランジスタを作製し、表

示装置の画素のスイッチング素子などに用いる技術が特許文献1および特許文献2で開示

されている。

化物半導体のキャリア濃度が高まると、ゲートに電圧を印加しなくてもトランジスタにチ

ャネルが形成されてしまう。即ち、しきい値電圧が負方向にシフトする。酸化物半導体の

水素を完全に取り除くことは困難であるため、しきい値電圧の制御も困難となる。

ることが示されている。また、酸化物半導体膜に接する絶縁膜から酸化物半導体膜に、水

素が拡散していくことが示されている。

体装置を作製することを課題とする。

水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱

処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させること

を技術的思想とする。

透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素

捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸

化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることがで

きる。

の界面近傍の水素濃度を低減することができる。

導体装置を作製することができる。

以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれ

ば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈さ

れるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す

符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターン

を同じくし、特に符号を付さない場合がある。

ランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶ

とき他方をソースと呼ぶ。すなわち、電位の高低によって、それらを区別しない。従って

、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

場合が多い。なお、電位を電圧と言い換えることが可能である。

、物理的な接続部分がなく、配線が延在しているだけの場合もある。

を示すものではない。また、本明細書において発明を特定するための事項として固有の名

称を示すものではない。

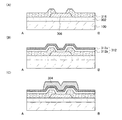

本実施の形態では、本発明の一態様のトランジスタの一例について図1を用いて説明する

。

点鎖線C−Dにおける断面は、それぞれ図1(B)に示すA−B断面および図1(C)に

示すC−D断面に対応する。

を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲ

ート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112を介してゲート

電極104上にある酸化物半導体膜106と、酸化物半導体膜106上にあり酸化物半導

体膜106と一部が接する一対の電極116と、を有する。なお、酸化物半導体膜106

上に層間絶縁膜118を有すると、酸化物半導体膜106が露出しないため好ましい。

素透過膜を用いる。なお、酸化物半導体膜と水素捕縛膜との間に水素透過膜を設けること

で、酸化物半導体膜の界面近傍の水素濃度を低減することができる。

を用いればよい。具体的には、少なくとも窒化インジウムを含み、加えて酸化インジウム

、酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリ

ブデン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む化合

物材料を用いればよい。なお、酸窒化物とは、酸化物を構成する酸素の一部が窒素で置き

換わった化合物をいう。

omic%未満とすればよい。窒素濃度が0.01atomic%以上7atomic%

未満である窒化インジウムを含む酸窒化物膜は、高い絶縁性を有する。または、第1のゲ

ート絶縁膜112aは、7atomic%以上20atomic%以下とすればよい。窒

素濃度が7atomic%以上20atomic%以下である窒化インジウムを含む酸窒

化物膜は、水素と結合すると高い導電性を有することがある。第1のゲート絶縁膜112

aの一部が高い導電性を有するとき、該一部がゲート電極の一部として機能することがあ

る。このとき、高い絶縁性を有する第2のゲート絶縁膜112bを有することで、第1の

ゲート絶縁膜112aを介した一対の電極116およびゲート電極104からの電荷のリ

ークを防ぐことができる。なお、第1のゲート絶縁膜112aの窒素濃度は、X線光電子

分光法(XPS:X−ray Photoelectron Spectroscopy

)分析によって定量化できる。

る。電子は負の電荷を有するため、ゲート電極側から負のバイアスが印加されているのと

同様に電界を生じ、トランジスタのしきい値電圧を正方向にシフトさせる。なお、酸化物

半導体膜を用いたトランジスタは、酸化物半導体膜内の酸素欠損および水素の一部がキャ

リアである電子を放出することで、しきい値電圧が負方向にシフトしやすい傾向がある。

そのため、窒化インジウムを含む酸窒化物膜が有する負の電荷により、トランジスタのし

きい値電圧を正方向にシフトさせると好ましい場合がある。なお、第1のゲート絶縁膜1

12aにおける水素濃度を制御することで、負の電荷量を調整することができる。第1の

ゲート絶縁膜112aにおける水素濃度は、第1のゲート絶縁膜112aの窒素濃度によ

り調整することができる。

−3以下、好ましくは1×1020cm−3以上3×1020cm−3以下とする。なお

、第1のゲート絶縁膜112aの水素濃度は、二次イオン質量分析法(SIMS:Sec

ondary Ion Mass Spectrometry)によって定量化できる。

リコン膜または酸化窒化シリコン膜を用いればよい。なお、第2のゲート絶縁膜112b

は、厚さが0.5nm以上15nm以下、好ましくは2nm以上5nm以下とする。第2

のゲート絶縁膜112bの厚さが薄いほど、より低温で水素を拡散することが可能となる

。

であって、好ましくは、酸素が50atomic%以上70atomic%以下、窒素が

0.5atomic%以上15atomic%以下、シリコンが25atomic%以上

35atomic%以下、水素が0atomic%以上10atomic%以下の範囲で

含まれるものをいう。ただし、上記範囲は、ラザフォード後方散乱法(RBS:Ruth

erford Backscattering Spectrometry)や、水素前

方散乱法(HFS:Hydrogen Forward scattering Spe

ctrometry)を用いて測定した場合のものである。また、構成元素の含有比率は

、その合計が100atomic%を超えない値をとる。

8cm−3以下とする。酸化物半導体膜106中の水素濃度は、SIMSによって定量化

できる。

カリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特

に、アルカリ金属のうちナトリウム(Na)は、酸化物半導体膜に接する絶縁膜中に拡散

してNa+となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する

金属と酸素の結合を分断する、または、その結合中に割り込む。その結果、例えば、しき

い値電圧が負方向にシフトすることによるノーマリオン化、電界効果移動度の低下などの

、トランジスタの電気的特性の劣化が起こり、加えて、トランジスタの電気的特性のばら

つきも生じる。この不純物によりもたらされるトランジスタの電気的特性の劣化と、トラ

ンジスタの電気的特性のばらつきは、酸化物半導体膜中の水素濃度が十分に低い場合にお

いて顕著に現れる。従って、酸化物半導体膜中の水素濃度が1×1018cm−3以下、

または1×1017cm−3以下である場合には、上記不純物の濃度を低減することが望

ましい。具体的に、Na濃度の測定値は、5×1016cm−3以下、好ましくは1×1

016cm−3以下、更に好ましくは1×1015cm−3以下とするとよい。同様に、

リチウム(Li)濃度の測定値は、5×1015cm−3以下、好ましくは1×1015

cm−3以下とするとよい。同様に、カリウム(K)濃度の測定値は、5×1015cm

−3以下、好ましくは1×1015cm−3以下とするとよい。

きる。例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電

流は、1×10−18A以下、または1×10−21A以下、または1×10−24A以

下となる。

含む材料を用いればよい。

.5eV以上、好ましくは3.0eV以上の材料を選択する。

−Zn−O系の材料、In−Sn−Zn−O系の材料、In−Al−Zn−O系の材料、

Sn−Ga−Zn−O系の材料、Al−Ga−Zn−O系の材料、Sn−Al−Zn−O

系の材料や、In−Zn−O系の材料、Sn−Zn−O系の材料、Al−Zn−O系の材

料、Zn−Mg−O系の材料、Sn−Mg−O系の材料、In−Mg−O系の材料、In

−Ga−O系の材料や、In−O系の材料、Sn−O系の材料、Zn−O系の材料などを

用いればよい。ここで、例えば、In−Ga−Zn−O系の材料は、インジウム(In)

、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、その組成比は特

に問わない。また、InとGaとZn以外の元素を含んでいてもよい。このとき、酸化物

半導体膜106の化学量論的組成比に対し、Oを過剰にすると好ましい。Oを過剰にする

ことで酸化物半導体膜106の酸素欠損に起因するキャリアの生成を抑制することができ

る。

比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さら

に好ましくはIn/Zn=1.5以上15以下とする。Znの原子数比を前述の範囲とす

ることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の

原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい。

料を用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複

数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたは

GaおよびCoなどを用いてもよい。

素を有する材料で形成すると好ましい。これは、スパッタリング法で成膜する場合、同一

ターゲットを用いて成膜ガスによって作り分けすることが可能となり、材料コストおよび

装置コストを低減できるためである。例えば、酸化物半導体膜106としてIn−Ga−

Zn−O膜を用いた場合、第1のゲート絶縁膜112aとしてIn−Ga−Zn−O−N

膜を用いればよい。

どの状態をとる。

Crystalline Oxide Semiconductor)膜とする。

は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜で

ある。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであること

が多い。また、透過型電子顕微鏡(TEM:Transmission Electro

n Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と

結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレ

インバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に

起因する電子移動度の低下が抑制される。

ルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角

形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または

金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸お

よびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、8

5°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5

°以上5°以下の範囲も含まれることとする。

C−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形

成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CA

AC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶

質化することもある。

ルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成

面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。な

お、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクト

ルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、また

は成膜後に加熱処理などの結晶化処理を行うことにより形成される。

動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

ン、酸化アルミニウム、ポリイミドおよびアクリルなどを、単層で、または積層して用い

ればよく、例えば、プラズマCVD法、スパッタリング法およびスピンコート法などで形

成する。また、層間絶縁膜118は、加熱処理により酸素を放出する膜を用いると好まし

い。加熱処理により酸素を放出する膜を用いることで、酸化物半導体膜106に生じる酸

素欠損を修復することができ、トランジスタの電気的特性の劣化を抑制できる。

であって、好ましくは、酸素が5atomic%以上30atomic%以下、窒素が2

0atomic%以上55atomic%以下、シリコンが25atomic%以上35

atomic%以下、水素が10atomic%以上25atomic%以下の範囲で含

まれるものをいう。但し、上記範囲は、RBSや、HFSを用いて測定した場合のもので

ある。また、構成元素の含有比率は、その合計が100atomic%を超えない値をと

る。

n Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての

酸素の放出量が1.0×1018cm−3以上、または1.0×1020cm−3以上で

あることをいう。

したイオン強度の積分値と、標準試料の基準値との比により、気体の放出量を計算するこ

とができる。標準試料の基準値とは、所定の密度の原子を含む試料において、当該原子に

相当するイオン強度の積分値に対する当該原子の密度の割合である。

び絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式1で求め

ることができる。ここで、TDS分析で得られる質量数32で検出されるガスの全てが酸

素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可

能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の

酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界における存在比

率が極微量であるため考慮しない。

料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、N

H2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値であ

る。αは、TDS分析におけるイオン強度に影響する係数である。数式1の詳細に関して

は、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子

科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として

1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分

子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量につ

いて見積もることができる。

の放出量の2倍となる。

iOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))

とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものをいう。単位

体積当たりのシリコン原子数および酸素原子数は、RBSにより測定した値である。

もいう。)で酸化物半導体膜106と層間絶縁膜118との界面準位密度を低減できる。

この結果、トランジスタの動作などに起因して、酸化物半導体膜106と層間絶縁膜11

8との界面にキャリアが捕獲されることを抑制することができ、電気的特性の劣化の少な

いトランジスタを得ることができる。

化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結

果、トランジスタのしきい値電圧が負方向へシフトしてしまう。層間絶縁膜118から酸

化物半導体膜106に酸素が十分に供給されることにより、しきい値電圧が負方向へシフ

トする要因である、酸化物半導体膜106の酸素欠損を低減することができる。

導体膜106と層間絶縁膜118との界面の界面準位密度、ならびに酸化物半導体膜10

6の酸素欠損を低減し、酸化物半導体膜106と層間絶縁膜118との界面におけるキャ

リア捕獲の影響を小さくすることができる。

上で、酸化物半導体膜106に含まれる水素濃度を低減させることが好ましい。

有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基

板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶

半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI

(Silicon On Insulator)基板などを適用することも可能であり、

これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。

ランジスタを作製すればよい。なお、可とう性基板上にトランジスタを設ける方法として

は、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性

基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジ

スタとの間に剥離層を設けるとよい。

aおよびW、それらの窒化物、酸化物ならびに合金から一以上選択し、単層でまたは積層

して用いればよい。

にすることで酸化物半導体膜106の光による劣化、電荷の発生を抑制しているが、これ

に限定されるものではない。例えば、酸化物半導体膜106がゲート電極104よりも、

上面図において縦、横ともに大きい形状にしても構わない。

たは合金膜などを単層でまたは積層して用いればよい。

でも配線遅延などの発生を低減することができる。一対の電極116にCuを用いる場合

、基板100の材質によっては密着性が悪くなるため、基板100と密着性のよい膜との

積層構造にすることが好ましい。基板100と密着性のよい膜として、Ti、Mo、Mn

、CuまたはAlなどを含む膜を用いればよい。例えば、Cu−Mn−Al合金を用いて

もよい。

ート電極104を形成する。次に、ゲート電極104を覆う、第1のゲート絶縁膜112

a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜112bからなるゲート

絶縁膜112を形成する(図7(A)参照。)。

se Laser Deposition)法、ALD(Atomic Layer D

eposition)法などを用いて成膜すればよい。例えば、スパッタリング法を用い

る場合、少なくとも酸化インジウムを含むターゲットを用いる。酸化インジウムに加えて

酸化ガリウム、酸化亜鉛、酸化スズ、酸化アルミニウム、酸化タングステン、酸化モリブ

デン、酸化チタン、酸化タンタルおよび酸化シリコンの少なくとも一種以上を含む材料を

ターゲットに用いても構わない。成膜ガスには少なくとも窒素を含ませればよい。また成

膜ガスとして、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノンなど)およ

び酸素のいずれか一種以上を用いても構わない。このような方法で成膜することにより、

窒素濃度が0.01atomic%以上7atomic%未満または7atomic%以

上20atomic%以下である、少なくとも窒化インジウムを含む第1のゲート絶縁膜

112aを成膜することができる。

D法などを用いて、酸化シリコン膜または酸化窒化シリコン膜を成膜すればよい。

る(図7(B)参照。)。酸化物半導体膜136は、前述の材料を用い、スパッタリング

法、PLD法、ALD法などを用いて成膜すればよい。

照。)。その後、450℃超過基板100の歪み点未満、好ましくは500℃以上650

℃以下で加熱処理を行い、酸化物半導体膜106から脱離した水素を、第2のゲート絶縁

膜112bを介して第1のゲート絶縁膜112aへ移動させる。移動した水素は、第1の

ゲート絶縁膜112aで捕縛される。このとき、酸化物半導体膜106の水素濃度は、1

×1019cm−3未満、好ましくは5×1018cm−3以下となる。また、第1のゲ

ート絶縁膜112aの水素濃度は、1×1019cm−3以上5×1020cm−3以下

、好ましくは1×1020cm−3以上3×1020cm−3以下となる。

06と少なくとも一部が接する一対の電極116を形成する。次に、酸化物半導体膜10

6および一対の電極116上に層間絶縁膜118を形成してもよい(図7(D)参照。)

。なお、酸化物半導体膜106を形成した後に行う加熱処理に代えて、層間絶縁膜118

の形成後に同様の加熱処理を行っても構わない。

ート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕

縛することにより、高純度化された酸化物半導体膜106を形成することができる。その

ため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高

い半導体装置を作製することができる。

より、トランジスタのしきい値電圧を正方向へシフトさせることができる。

説明する。

よび一点鎖線C−Dにおける断面は、それぞれ図2(B)に示すA−B断面および図2(

C)に示すC−D断面に対応する。

電極104を覆う、第1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上

の第2のゲート絶縁膜112bからなるゲート絶縁膜112と、ゲート絶縁膜112上の

一対の電極216と、ゲート絶縁膜112を介してゲート電極104上にあり、一対の電

極216と一部が接する酸化物半導体膜206と、を有する。なお、ゲート絶縁膜112

、一対の電極216および酸化物半導体膜206上に層間絶縁膜218を有すると、酸化

物半導体膜206が露出しないため好ましい。ここで、一対の電極216、酸化物半導体

膜206および層間絶縁膜218は、それぞれ一対の電極116、酸化物半導体膜106

および層間絶縁膜118と同様の方法および同様の材料により形成する。

にすることで酸化物半導体膜206の光による劣化、電荷の発生を抑制しているが、これ

に限定されるものではない。例えば、酸化物半導体膜206がゲート電極104よりも、

上面図において縦、横ともに大きい形状としても構わない。

1のゲート絶縁膜112a、および第1のゲート絶縁膜112a上の第2のゲート絶縁膜

112bからなるゲート絶縁膜112を形成する。次に、ゲート絶縁膜112上に一対の

電極216を形成する(図8(A)参照。)。

る(図8(B)参照。)。なお、酸化物半導体膜236は、酸化物半導体膜136と同様

の方法および同様の材料により形成する。

206を形成する(図8(C)参照。)。その後、450℃超過基板100の歪み点未満

、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜206から脱

離した水素を、第2のゲート絶縁膜112bを介して第1のゲート絶縁膜112aへ移動

させる。移動した水素は、第1のゲート絶縁膜112aで捕縛される。このとき、酸化物

半導体膜206の水素濃度は、1×1019cm−3未満、好ましくは5×1018cm

−3以下となる。また、第1のゲート絶縁膜112aの水素濃度は、1×1019cm−

3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020c

m−3以下となる。

(図8(D)参照。)。なお、酸化物半導体膜206を形成した後に行う加熱処理に代え

て、層間絶縁膜218の形成後に同様の加熱処理を行っても構わない。

ート絶縁膜112aへ水素を移動させ、移動した水素を第1のゲート絶縁膜112aで捕

縛することにより、高純度化された酸化物半導体膜206を形成することができる。その

ため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高

い半導体装置を作製することができる。

トランジスタのしきい値電圧を正方向へシフトさせることができる。そのため、トランジ

スタの電気的特性をノーマリーオフ、またはノーマリーオフに近づけることができる。

3を用いて説明する。

よび一点鎖線C−Dにおける断面は、それぞれ図3(B)に示すA−B断面および図3(

C)に示すC−D断面に対応する。

縁膜302上の酸化物半導体膜306と、酸化物半導体膜306上にあり酸化物半導体膜

306と一部が接する一対の電極316と、酸化物半導体膜306および一対の電極31

6上の、第2のゲート絶縁膜312b、および第2のゲート絶縁膜312b上の第1のゲ

ート絶縁膜312aからなるゲート絶縁膜312と、ゲート絶縁膜312を介して酸化物

半導体膜306上にあるゲート電極304と、を有する。なお、基板100の表面状態に

よっては、下地絶縁膜302を設けない構成としても構わない。ここで、一対の電極31

6、酸化物半導体膜306、ゲート電極304およびゲート絶縁膜312は、それぞれ一

対の電極116、酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と

同様の方法および同様の材料により形成する。

にすることで酸化物半導体膜306の光による劣化、電荷の発生を抑制しているが、これ

に限定されるものではない。例えば、酸化物半導体膜306がゲート電極304よりも、

上面図において縦、横ともに大きい形状としても構わない。

半導体膜306を形成する。次に、酸化物半導体膜306上に、酸化物半導体膜306と

少なくとも一部が接する一対の電極316を形成する(図9(A)参照。)。なお、基板

100の表面状態によっては、下地絶縁膜302を設けなくても構わない。

、および第2のゲート絶縁膜312b上の第1のゲート絶縁膜312aからなるゲート絶

縁膜312を形成する(図9(B)参照。)。その後、450℃超過基板100の歪み点

未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜306か

ら脱離した水素を、第2のゲート絶縁膜312bを介して第1のゲート絶縁膜312aへ

移動させる。移動した水素は、第1のゲート絶縁膜312aで捕縛される。このとき、酸

化物半導体膜306の水素濃度は、1×1019cm−3未満、好ましくは5×1018

cm−3以下となる。また、第1のゲート絶縁膜312aの水素濃度は、1×1019c

m−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×102

0cm−3以下となる。

形成する(図9(C)参照。)。なお、ゲート絶縁膜312を形成した後に行う加熱処理

に代えて、ゲート電極304の形成後に同様の加熱処理を行っても構わない。

ート絶縁膜312aへ水素を移動させ、移動した水素を第1のゲート絶縁膜312aで捕

縛することにより、高純度化された酸化物半導体膜306を形成することができる。その

ため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高

い半導体装置を作製することができる。

トランジスタのしきい値電圧を正方向へシフトさせることができる。

を用いて説明する。

よび一点鎖線C−Dにおける断面は、それぞれ図4(B)に示すA−B断面および図4(

C)に示すC−D断面に対応する。

縁膜302上の一対の電極416と、一対の電極416上にあり一対の電極416と一部

が接する酸化物半導体膜406と、酸化物半導体膜406および一対の電極416上の、

第2のゲート絶縁膜412b、および第2のゲート絶縁膜412b上の第1のゲート絶縁

膜412aからなるゲート絶縁膜412と、ゲート絶縁膜412を介して酸化物半導体膜

406上にあるゲート電極404と、を有する。なお、基板100の表面状態によっては

、下地絶縁膜302を設けなくても構わない。ここで、一対の電極416、酸化物半導体

膜406、ゲート電極404およびゲート絶縁膜412は、それぞれ一対の電極116、

酸化物半導体膜106、ゲート電極104およびゲート絶縁膜112と同様の方法および

同様の材料により形成する。

にすることで酸化物半導体膜406の光による劣化、電荷の発生を抑制しているが、これ

に限定されるものではない。例えば、酸化物半導体膜406がゲート電極404よりも、

上面図において縦、横ともに大きい形状としても構わない。

電極416を形成する(図10(A)参照。)。なお、基板100の表面状態によっては

、下地絶縁膜302を設けなくても構わない。

形成する(図10(B)参照。)。

よび第2のゲート絶縁膜412b上の第1のゲート絶縁膜412aからなるゲート絶縁膜

412を形成する(図10(C)参照。)。その後、450℃超過基板100の歪み点未

満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化物半導体膜406から

脱離した水素を、第2のゲート絶縁膜412bを介して第1のゲート絶縁膜412aへ移

動させる。移動した水素は、第1のゲート絶縁膜412aで捕縛される。このとき、酸化

物半導体膜406の水素濃度は、1×1019cm−3未満、好ましくは5×1018c

m−3以下となる。また、第1のゲート絶縁膜412aの水素濃度は、1×1019cm

−3以上5×1020cm−3以下、好ましくは1×1020cm−3以上3×1020

cm−3以下となる。

形成する(図10(D)参照。)。なお、ゲート絶縁膜412を形成した後に行う加熱処

理に代えて、ゲート電極404の形成後に同様の加熱処理を行っても構わない。

ート絶縁膜412aへ水素を移動させ、移動した水素を第1のゲート絶縁膜412aで捕

縛することにより、高純度化された酸化物半導体膜406を形成することができる。その

ため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高

い半導体装置を作製することができる。

トランジスタのしきい値電圧を正方向へシフトさせることができる。

を用いて説明する。

よび一点鎖線C−Dにおける断面は、それぞれ図5(B)に示すA−B断面および図5(

C)に示すC−D断面に対応する。

縁膜302上のチャネル領域505、ソース領域507aおよびドレイン領域507bを

有する酸化物半導体膜506と、酸化物半導体膜506上の、第2のゲート絶縁膜512

b、および第2のゲート絶縁膜512b上の第1のゲート絶縁膜512aからなるゲート

絶縁膜512と、ゲート絶縁膜512を介してチャネル領域505と重畳するゲート電極

504と、酸化物半導体膜506およびゲート電極504上の層間絶縁膜518と、ゲー

ト絶縁膜512および層間絶縁膜518に設けられた開口部を介して酸化物半導体膜50

6と接する一対の電極516と、を有する。なお、基板100の表面状態によっては、下

地絶縁膜302を設けなくても構わない。ここで、一対の電極516、酸化物半導体膜5

06、ゲート電極504、層間絶縁膜518およびゲート絶縁膜512は、それぞれ一対

の電極116、酸化物半導体膜106、ゲート電極104、層間絶縁膜118およびゲー

ト絶縁膜112と同様の方法および同様の材料により形成する。

状としてもよい。この形状は、ゲート電極504およびゲート絶縁膜512を同一のマス

クを用いて加工することで得られる。または、ゲート電極504をマスクに用いてゲート

絶縁膜512を加工することによって得られる。

状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507aお

よびドレイン領域507bを露出するものであれば、形状は問わない。

ース領域507aおよびドレイン領域507bは、窒素、リン、水素、または希ガスなど

を含む。

507bは低抵抗領域である。

半導体膜506を形成する。次に、下地絶縁膜302および酸化物半導体膜506上に、

第2のゲート絶縁膜512b、および第2のゲート絶縁膜512b上の第1のゲート絶縁

膜512aからなるゲート絶縁膜512を形成する(図11(A)参照。)。その後、4

50℃超過基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を

行い、酸化物半導体膜506から脱離した水素を、第2のゲート絶縁膜512bを介して

第1のゲート絶縁膜512aへ移動させる。移動した水素は、第1のゲート絶縁膜512

aで捕縛される。このとき、酸化物半導体膜506の水素濃度は、1×1019cm−3

未満、好ましくは5×1018cm−3以下となる。また、第1のゲート絶縁膜512a

の水素濃度は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1

020cm−3以上3×1020cm−3以下となる。なお、基板100の表面状態によ

っては、下地絶縁膜302を設けなくても構わない。

る。なお、ゲート電極504を形成後、プラズマ処理または薬液処理によってゲート電極

504の幅を細くしても構わない。

たは希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸化

物半導体膜506の、ゲート電極504と重畳しない領域を低抵抗化し、チャネル領域5

05、ソース領域507aおよびドレイン領域507bを形成する(図11(B)参照。

)。なお、ここで行う加熱処理を、ゲート絶縁膜512を形成した後に行う加熱処理に代

えることができる。

1(C)参照。)、ソース領域507aおよびドレイン領域507bをそれぞれ露出する

開口部をゲート絶縁膜512および層間絶縁膜518に形成する。次に、酸化物半導体膜

506と接する一対の電極516を形成する(図11(D)参照。)。なお、ゲート絶縁

膜512を形成した後に行う加熱処理、ソース領域507aおよびドレイン領域507b

を形成するための加熱処理に代えて、層間絶縁膜518または一対の電極516の形成後

に同様の加熱処理を行っても構わない。

ート絶縁膜512aへ水素を移動させ、移動した水素を第1のゲート絶縁膜512aで捕

縛することにより、高純度化された酸化物半導体膜506を形成することができる。その

ため、トランジスタのオフ電流が極めて小さく、安定した電気的特性を有する信頼性の高

い半導体装置を作製することができる。

トランジスタのしきい値電圧を正方向へシフトさせることができる。

形状は円形であるが、これに限定されるものではない。該開口部は、ソース領域507a

およびドレイン領域507bを露出するものであれば、形状は問わない。

を用いて説明する。

よび一点鎖線C−Dにおける断面は、それぞれ図6(B)に示すA−B断面および図6(

C)に示すC−D断面に対応する。

電極604を覆う、第1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上

の第2のゲート絶縁膜612bからなるゲート絶縁膜612と、ゲート絶縁膜612を介

してゲート電極604上にあり、チャネル領域605、ソース領域607aおよびドレイ

ン領域607bを有する酸化物半導体膜606と、ゲート絶縁膜612および酸化物半導

体膜606上の、ソース領域607aおよびドレイン領域607bをそれぞれ露出する開

口部を有する層間絶縁膜618と、層間絶縁膜618に設けられた開口部を介して酸化物

半導体膜606と接する一対の電極616と、を有する。ここで、一対の電極616、酸

化物半導体膜606、ゲート電極604、層間絶縁膜618およびゲート絶縁膜612は

、それぞれ示した一対の電極116、酸化物半導体膜106、ゲート電極104、層間絶

縁膜118およびゲート絶縁膜112と同様の方法および同様の材料により形成する。

いるが、これに限定されない。ゲート電極604とチャネル領域605の形状が異なって

いても構わない。

ガスなどを含む。

607b低抵抗領域である。

1のゲート絶縁膜612a、および第1のゲート絶縁膜612a上の第2のゲート絶縁膜

612bからなるゲート絶縁膜612を形成する(図12(A)参照。)。

基板100の歪み点未満、好ましくは500℃以上650℃以下で加熱処理を行い、酸化

物半導体膜606から脱離した水素を、第2のゲート絶縁膜612bを介して第1のゲー

ト絶縁膜612aへ移動させる。移動した水素は、第1のゲート絶縁膜612aで捕縛さ

れる。このとき、酸化物半導体膜606の水素濃度は、1×1019cm−3未満、好ま

しくは5×1018cm−3以下となる。また、第1のゲート絶縁膜612aの水素濃度

は、1×1019cm−3以上5×1020cm−3以下、好ましくは1×1020cm

−3以上3×1020cm−3以下となる。

または希ガスを添加する。該添加、または該添加に加えて加熱処理を行うことにより、酸

化物半導体膜606の、ゲート電極604と重畳しない領域を低抵抗化し、チャネル領域

605、ソース領域607aおよびドレイン領域607bを形成する(図12(C)参照

。)。なお、ここで行う加熱処理を、ゲート絶縁膜612を形成した後に行う加熱処理に

代えることができる。なお、レジストマスクなどは、ゲート電極604をマスクに裏面露

光技術によって形成しても構わない。その場合、ソース領域607aおよびドレイン領域

607bと、ゲート電極604との重畳する面積が小さくできるため寄生容量が低減され

、トランジスタの動作速度を高めることができる。また、レジストマスクを形成するため

のフォトマスク数が低減できるため、トランジスタの作製コストを低減することができる

ため好ましい。

ドレイン領域607bをそれぞれ露出する開口部を有する層間絶縁膜618を形成する。

次に、導電膜をスパッタリング法、蒸着法などで成膜し、加工して、酸化物半導体膜60

6と接する一対の電極616を形成する(図12(D)参照。)。

本実施の形態では、実施の形態1に示したトランジスタを用いて作製した液晶表示装置に

ついて説明する。なお、本実施の形態では液晶表示装置に本発明の一形態を適用した例に

ついて説明するが、これに限定されるものではない。例えば、発光装置の一つであるEL

(Electro Luminescence)表示装置に本発明の一形態を適用するこ

とも、当業者であれば容易に想到し得るものである。

、ソース線SL_1乃至SL_a、ゲート線GL_1乃至GL_bおよび複数の画素22

00を有する。画素2200は、トランジスタ2230と、キャパシタ2220と、液晶

素子2210と、を含む。こうした画素2200が複数集まって液晶表示装置の画素部を

構成する。なお、単にソース線またはゲート線を指す場合には、ソース線SLまたはゲー

ト線GLと記載することもある。

いる。実施の形態1で示したトランジスタは電気的特性が良好な酸化物半導体を用いたト

ランジスタであるため、表示品位が高く、消費電力が小さい表示装置を得ることができる

。

230のソースと接続し、トランジスタ2230のドレインは、キャパシタ2220の一

方の容量電極および液晶素子2210の一方の画素電極と接続する。キャパシタ2220

の他方の容量電極および液晶素子2210の他方の画素電極は、共通電極と接続する。な

お、共通電極はゲート線GLと同一層かつ同一材料で設けてもよい。

で示したトランジスタを含んでもよい。

で示したトランジスタを含んでもよい。

板上に形成し、COG(Chip On Glass)、ワイヤボンディング、またはT

AB(Tape Automated Bonding)などの方法を用いて接続しても

よい。

ましい。保護回路は、非線形素子を用いて構成することが好ましい。

、ソース線SLから供給された電荷がトランジスタ2230のドレイン電流となってキャ

パシタ2220に蓄積される。1行分の充電後、該行にあるトランジスタ2230はオフ

状態となり、ソース線SLから電圧が掛からなくなるが、キャパシタ2220に蓄積され

た電荷によって必要な電圧を維持することができる。その後、次の行のキャパシタ222

0の充電に移る。このようにして、1行からb行の充電を行う。ドレイン電流とは、トラ

ンジスタにおいてソースからチャネルを介してドレインに流れる電流のことである。ドレ

イン電流はゲート電圧がしきい値電圧よりも大きいときに流れる。

する期間を長くすることができる。この効果によって、動きの少ない画像(静止画を含む

。)では、表示の書き換え周波数を低減でき、さらなる消費電力の低減が可能となる。ま

た、キャパシタ2220の容量をさらに小さくすることが可能となるため、充電に必要な

消費電力を低減することができる。

置を提供することができる。

本実施の形態では、実施の形態1で示したトランジスタを用いて、半導体記憶装置を作製

する例について説明する。

てキャパシタに電荷を蓄積することで、情報を記憶するDRAM(Dynamic Ra

ndom Access Memory)、フリップフロップなどの回路を用いて記憶内

容を保持するSRAM(Static Random Access Memory)が

ある。

にノードを有し、当該ノードに電荷を保持することで記憶を行うフラッシュメモリがある

。

スタを適用することができる。

セルについて図14を用いて説明する。

タTrと、キャパシタCと、を有する(図14(A)参照。)。

4(B)に示すように徐々に低減していくことが知られている。当初V0からV1まで充

電された電圧は、時間が経過するとdata1を読み出す限界点であるVAまで低減する

。この期間を保持期間T_1とする。即ち、2値メモリセルの場合、保持期間T_1の間

にリフレッシュをする必要がある。

が小さいため、保持期間T_1を長くすることができる。即ち、リフレッシュの頻度を少

なくすることが可能となるため、消費電力を低減することができる。例えば、オフ電流が

1×10−21A以下、好ましくは1×10−24A以下となった酸化物半導体膜を用い

たトランジスタでメモリセルを構成すると、電力を供給せずに数日間から数十年間に渡っ

てデータを保持することが可能となる。

置を得ることができる。

ルについて図14と異なる例を図15を用いて説明する。

トランジスタTr_1のゲートと接続するゲート線GL_1と、トランジスタTr_1の

ソースと接続するソース線SL_1と、トランジスタTr_2と、トランジスタTr_2

のソースと接続するソース線SL_2と、トランジスタTr_2のドレインと接続するド

レイン線DL_2と、キャパシタCと、キャパシタCの一端と接続する容量線CLと、キ

ャパシタCの他端、トランジスタTr_1のドレインおよびトランジスタTr_2のゲー

トと接続するノードNと、を有する。

2のしきい値電圧が変動することを利用したものである。例えば、図15(B)は容量線

CLの電圧VCLと、トランジスタTr_2を流れるドレイン電流Ids_2との関係を

説明する図である。

ば、ソース線SL_1の電位をVDDとする。このとき、ゲート線GL_1の電位をトラ

ンジスタTr_1のしきい値電圧VthにVDDを加えた電位以上とすることで、ノード

Nの電位をHIGHにすることができる。また、ゲート線GL_1の電位をトランジスタ

Tr_1のしきい値電圧Vth以下とすることで、ノードNの電位をLOWにすることが

できる。

L−Ids_2カーブのいずれかを得ることができる。即ち、N=LOWでは、VCL=

0VにてIds_2が小さいため、データ0となる。また、N=HIGHでは、VCL=

0VにてIds_2が大きいため、データ1となる。このようにして、データを記憶する

ことができる。

ランジスタはオフ電流を極めて小さくすることができるため、ノードNに蓄積された電荷

がトランジスタTr_1のソースおよびドレイン間を意図せずにリークすることを抑制で

きる。そのため、長期間に渡ってデータを保持することができる。また、本発明の一態様

に係るトランジスタTr_1はしきい値電圧が調整されるため、書き込みに必要な電圧を

低減することが可能となり、フラッシュメモリなどと比較して消費電力を低減することが

できる。

い。

体記憶装置を得ることができる。

実施の形態1で示したトランジスタを少なくとも一部に用いてCPU(Central

Processing Unit)を構成することができる。

PUは、基板1190上に、演算回路(ALU:Arithmetic logic u

nit)1191、ALUコントローラ1192、インストラクションデコーダ1193

、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ11

96、レジスタコントローラ1197、バスインターフェース(Bus I/F)119

8、書き換え可能なROM1199、およびROMインターフェース(ROM I/F)

1189を有している。基板1190には、半導体基板、SOI基板、ガラス基板などを

用いる。ROM1199およびROMインターフェース1189は、別チップに設けても

よい。もちろん、図16(A)に示すCPUは、その構成を簡略化して示した一例にすぎ

ず、実際のCPUはその用途によって多種多様な構成を有している。

デコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタ

ラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ

1195に入力される。

ラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制

御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御する

ための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラ

ム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク

状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアド

レスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

2、インストラクションデコーダ1193、インタラプトコントローラ1194、および

レジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタ

イミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号

CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種

回路に供給する。

スタ1196の記憶素子には、実施の形態3に示す記憶素子を用いることができる。

からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジス

タ1196が有する記憶素子において、位相反転素子によるデータの保持を行うか、容量

素子によるデータの保持を行うかを、選択する。位相反転素子によるデータの保持が選択

されている場合、レジスタ1196内の記憶素子への、電源電圧の供給が行われる。容量

素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行わ

れ、レジスタ1196内の記憶素子への電源電圧の供給を停止することができる。

源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設

けることにより行うことができる。以下に図16(B)および図16(C)の回路の説明

を行う。

ング素子に、実施の形態1で示したトランジスタを含む記憶回路の構成の一例を示す。

有する記憶素子群1143とを有している。具体的に、それぞれの記憶素子1142に、

実施の形態3に示す記憶素子を用いることができる。記憶素子群1143が有する各記憶

素子1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが

供給されている。さらに、記憶素子群1143が有するそれぞれの記憶素子1142に、

信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

極めて小さいトランジスタを用いており、該トランジスタは、そのゲートに与えられる信

号SigAによりスイッチングが制御される。

成を示しているが、これに限定されず、トランジスタを複数有していてもよい。スイッチ

ング素子1141が、スイッチング素子として機能するトランジスタを複数有している場

合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていても

よいし、直列と並列が組み合わされて接続されていてもよい。

スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記

憶装置の一例を示す。スイッチング素子1141により、記憶素子群1143が有するそ

れぞれの記憶素子1142への、ローレベルの電源電位VSSの供給を制御することがで

きる。

ッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合に

おいてもデータを保持することが可能であり、消費電力の低減を行うことができる。例え

ば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を

停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減す

ることができる。

rocessor)、カスタムLSI、FPGA(Field Programmabl

e Gate Array)などのLSIにも応用可能である。

本実施の形態では、実施の形態1乃至実施の形態4を適用した電子機器の例について説明

する。

00と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9

304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。本発明の

一態様は、表示部9303およびカメラ9305に適用することができる。また、図示し

ないが、本体内部にある演算装置、無線回路または記憶回路に本発明の一態様を適用する

こともできる。

0と、表示部9311と、を具備する。本発明の一態様は、表示部9311に適用するこ

とができる。本発明の一態様を用いることで、表示部9311のサイズを大きくしたとき

にも表示品位が高く、消費電力が小さいディスプレイとすることができる。

ラは、筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323

と、を具備する。本発明の一態様は、表示部9323に適用することができる。また、図

示しないが、記憶回路またはイメージセンサに本発明の一態様を適用することもできる。

ことができる。

する具体的な例について、加熱処理を行った試料および加熱処理を行っていない試料のS

IMS結果を用いて説明する。

酸化物半導体膜上に酸化シリコン膜を5nmの厚さで成膜し、酸化シリコン膜上に酸窒化

物膜(In−Ga−Zn−O−N膜)を300nmの厚さで成膜した試料を用意した。

数比、In2O3:ZnO:Ga2O3=1:1:2)を用い、ターゲット−基板間に印

加する電力を500W(DC)、成膜圧力を0.4Pa、成膜ガス流量をアルゴン30s

ccmおよび酸素15sccmとし、基板表面温度が200℃になるよう加熱処理しなが

ら成膜した。

kW、成膜圧力を0.4Pa、成膜ガス流量をアルゴン25sccmおよび酸素25sc

cmとし、基板表面温度が100℃になるよう加熱処理しながら成膜した。

、In2O3:ZnO:Ga2O3=1:1:2)を用い、成膜電力を500W、成膜圧

力を0.4Pa、成膜ガス流量を窒素40sccmとし、基板表面温度が200℃になる

よう加熱処理しながら成膜した。

る窒素濃度の深さ方向分布を示す。ここで、範囲6001は酸窒化物膜を、範囲6002

は酸化シリコン膜を、範囲6003は酸化物半導体膜を、範囲6004は石英基板を示す

。ただし、範囲6002は定量化されていない。また、各層の界面近傍はマトリックス効

果により正確な定量値が得られていない。なお、SIMSは、CAMECA社製IMS

7fRを用いた。

20は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の水素濃度分布

を示す。前述の加熱処理を行うことで、酸化物半導体膜中の水素濃度が低減し、酸窒化物

膜中の水素濃度が増大していることがわかる。即ち、前述の加熱処理によって、酸化物半

導体膜から酸化シリコン膜を介して酸窒化物膜に水素が移動していることがわかる。

40は成膜後に窒素雰囲気にて550℃で1時間の加熱処理を行った試料の窒素濃度分布

を示す。前述の加熱処理前後で、試料中の窒素濃度分布はほとんど変動しないことがわか

る。

104 ゲート電極

106 酸化物半導体膜

112 ゲート絶縁膜

112a 第1のゲート絶縁膜

112b 第2のゲート絶縁膜

116 一対の電極

118 層間絶縁膜

136 酸化物半導体膜

206 酸化物半導体膜

216 一対の電極

218 層間絶縁膜

236 酸化物半導体膜

302 下地絶縁膜

304 ゲート電極

306 酸化物半導体膜

312 ゲート絶縁膜

312a 第1のゲート絶縁膜

312b 第2のゲート絶縁膜

316 一対の電極

404 ゲート電極

406 酸化物半導体膜

412 ゲート絶縁膜

412a 第1のゲート絶縁膜

412b 第2のゲート絶縁膜

416 一対の電極

504 ゲート電極

505 チャネル領域

506 酸化物半導体膜

507a ソース領域

507b ドレイン領域

512 ゲート絶縁膜

512a 第1のゲート絶縁膜

512b 第2のゲート絶縁膜

516 一対の電極

518 層間絶縁膜

604 ゲート電極

605 チャネル領域

606 酸化物半導体膜

607a ソース領域

607b ドレイン領域

612 ゲート絶縁膜

612a 第1のゲート絶縁膜

612b 第2のゲート絶縁膜

616 一対の電極

618 層間絶縁膜

1141 スイッチング素子

1142 記憶素子

1143 記憶素子群

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

2200 画素

2210 液晶素子

2220 キャパシタ

2230 トランジスタ

6001 範囲

6002 範囲

6003 範囲

6004 範囲

6010 細線

6020 太線

6030 細線

6040 太線

9300 筐体

9301 ボタン

9302 マイクロフォン

9303 表示部

9304 スピーカ

9305 カメラ

9310 筐体

9311 表示部

9320 筐体

9321 ボタン

9322 マイクロフォン

9323 表示部

Claims (2)

- 酸化物半導体膜と、第1の層と、第2の層とを有し、

前記第1の層は、水素を拡散又は水素を透過する機能を有し、

前記第2の層は、インジウムと、窒素と、酸素とを有し、

前記第1の層は、前記酸化物半導体膜と接する領域を有し、

前記第1の層は、前記第2の層と接する領域を有することを特徴とする積層構造体。 - 酸化物半導体膜と、第1の層と、第2の層とを有し、

前記第1の層は、水素を拡散又は水素を透過する機能を有し、

前記第2の層は、インジウムと、窒素と、酸素とを有し、

前記第1の層は、前記酸化物半導体膜と接する領域を有し、

前記第1の層は、前記第2の層と接する領域を有する積層構造体の作製方法であって、

前記酸化物半導体膜から脱離した水素を、前記第2の層へ移動させるための加熱処理を行うことを特徴とする積層構造体の作製方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011067206 | 2011-03-25 | ||

| JP2011067206 | 2011-03-25 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012062923A Division JP5912709B2 (ja) | 2011-03-25 | 2012-03-20 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016149562A JP2016149562A (ja) | 2016-08-18 |

| JP6110975B2 true JP6110975B2 (ja) | 2017-04-05 |

Family

ID=46876568

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012062923A Expired - Fee Related JP5912709B2 (ja) | 2011-03-25 | 2012-03-20 | 半導体装置 |

| JP2016053949A Active JP6110975B2 (ja) | 2011-03-25 | 2016-03-17 | 積層構造体、及びその作製方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012062923A Expired - Fee Related JP5912709B2 (ja) | 2011-03-25 | 2012-03-20 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9012904B2 (ja) |

| JP (2) | JP5912709B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8956944B2 (en) * | 2011-03-25 | 2015-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| TWI545652B (zh) * | 2011-03-25 | 2016-08-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| US9219159B2 (en) | 2011-03-25 | 2015-12-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming oxide semiconductor film and method for manufacturing semiconductor device |

| KR101951260B1 (ko) * | 2012-03-15 | 2019-02-25 | 삼성디스플레이 주식회사 | 박막트랜지스터, 상기 박막트랜지스터를 포함하는 표시 장치 및 상기 박막트랜지스터를 포함하는 유기 발광 표시 장치 |

| CN104380444A (zh) | 2012-06-29 | 2015-02-25 | 株式会社半导体能源研究所 | 半导体装置 |

| JP2014042004A (ja) | 2012-07-26 | 2014-03-06 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| US9287411B2 (en) | 2012-10-24 | 2016-03-15 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US20150303200A1 (en) * | 2012-11-28 | 2015-10-22 | Ps4 Luxco S.A.R.L. | Semiconductor device and method for manufacturing same |

| US9349593B2 (en) | 2012-12-03 | 2016-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US20160118244A1 (en) * | 2013-06-04 | 2016-04-28 | Joled Inc. | Thin film transistor element, production method for same, and display device |

| US9299855B2 (en) | 2013-08-09 | 2016-03-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having dual gate insulating layers |

| JP2015036797A (ja) * | 2013-08-15 | 2015-02-23 | ソニー株式会社 | 表示装置および電子機器 |

| CN103700626B (zh) * | 2013-12-25 | 2017-02-15 | 京东方科技集团股份有限公司 | 一种阵列基板的制作方法、阵列基板和显示装置 |

| JP6611521B2 (ja) | 2015-08-25 | 2019-11-27 | 三菱電機株式会社 | 薄膜トランジスタ及びアレイ基板 |

| CN106021169B (zh) * | 2016-05-16 | 2019-01-11 | 中国计量大学 | 一种航天计算机及其非易失存储装置的刷新和升级方法 |

| CN106756877B (zh) * | 2016-12-13 | 2019-02-19 | 武汉华星光电技术有限公司 | C轴结晶igzo薄膜及其制备方法 |

| US11211467B2 (en) | 2017-11-09 | 2021-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

Family Cites Families (150)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3298974B2 (ja) | 1993-03-23 | 2002-07-08 | 電子科学株式会社 | 昇温脱離ガス分析装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| WO1997006554A2 (en) | 1995-08-03 | 1997-02-20 | Philips Electronics N.V. | Semiconductor device provided with transparent switching element |

| JP3409542B2 (ja) * | 1995-11-21 | 2003-05-26 | ソニー株式会社 | 半導体装置の製造方法 |

| US6391690B2 (en) * | 1995-12-14 | 2002-05-21 | Seiko Epson Corporation | Thin film semiconductor device and method for producing the same |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP3220645B2 (ja) * | 1996-09-06 | 2001-10-22 | 富士通株式会社 | 半導体装置の製造方法 |

| EP0881668A3 (en) * | 1997-05-28 | 2000-11-15 | Dow Corning Toray Silicone Company, Ltd. | Deposition of an electrically insulating thin film with a low dielectric constant |

| JPH11111994A (ja) * | 1997-10-03 | 1999-04-23 | Sanyo Electric Co Ltd | 薄膜トランジスタ及び薄膜トランジスタの製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| TW449928B (en) * | 2000-01-25 | 2001-08-11 | Samsung Electronics Co Ltd | A low temperature polycrystalline silicon type thin film transistor and a method of the thin film transistor fabrication |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US6803265B1 (en) * | 2002-03-27 | 2004-10-12 | Fasl Llc | Liner for semiconductor memories and manufacturing method therefor |

| JP2003297956A (ja) * | 2002-04-04 | 2003-10-17 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| KR100571803B1 (ko) * | 2002-05-03 | 2006-04-17 | 삼성전자주식회사 | 수소로 기능화된 반도체 탄소나노튜브를 포함하는 전자 소자 및 그 제조방법 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| KR100623232B1 (ko) * | 2003-11-29 | 2006-09-18 | 삼성에스디아이 주식회사 | 평판표시장치 및 그의 제조방법 |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| EP1737044B1 (en) | 2004-03-12 | 2014-12-10 | Japan Science and Technology Agency | Amorphous oxide and thin film transistor |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| JP5118812B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 電界効果型トランジスタ |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| JP5118811B2 (ja) | 2004-11-10 | 2013-01-16 | キヤノン株式会社 | 発光装置及び表示装置 |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| JP5126729B2 (ja) | 2004-11-10 | 2013-01-23 | キヤノン株式会社 | 画像表示装置 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI412138B (zh) | 2005-01-28 | 2013-10-11 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| US7566971B2 (en) * | 2005-05-27 | 2009-07-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US20060292774A1 (en) * | 2005-06-27 | 2006-12-28 | Macronix International Co., Ltd. | Method for preventing metal line bridging in a semiconductor device |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| EP1998375A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| CN101577231B (zh) | 2005-11-15 | 2013-01-02 | 株式会社半导体能源研究所 | 半导体器件及其制造方法 |

| EP1950177A4 (en) * | 2005-11-18 | 2009-02-25 | Idemitsu Kosan Co | SEMICONDUCTOR THIN FILM, MANUFACTURING METHOD AND THIN FILM TRANSISTOR |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7374998B2 (en) * | 2006-02-03 | 2008-05-20 | International Business Machines Corporation | Selective incorporation of charge for transistor channels |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| JP2007250519A (ja) * | 2006-03-14 | 2007-09-27 | Samsung Sdi Co Ltd | 有機電界発光表示装置 |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| US7781768B2 (en) * | 2006-06-29 | 2010-08-24 | Semiconductor Energy Laboratory Co., Ltd. | Display device, method for manufacturing the same, and electronic device having the same |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) * | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| JP5105842B2 (ja) | 2006-12-05 | 2012-12-26 | キヤノン株式会社 | 酸化物半導体を用いた表示装置及びその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| JP5320746B2 (ja) * | 2007-03-28 | 2013-10-23 | 凸版印刷株式会社 | 薄膜トランジスタ |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| CN101663762B (zh) | 2007-04-25 | 2011-09-21 | 佳能株式会社 | 氧氮化物半导体 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5213422B2 (ja) * | 2007-12-04 | 2013-06-19 | キヤノン株式会社 | 絶縁層を有する酸化物半導体素子およびそれを用いた表示装置 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP5291928B2 (ja) * | 2007-12-26 | 2013-09-18 | 株式会社日立製作所 | 酸化物半導体装置およびその製造方法 |

| KR20090080751A (ko) * | 2008-01-22 | 2009-07-27 | 삼성전자주식회사 | 저항성 메모리 소자 및 그 제조방법 |

| KR20090081153A (ko) * | 2008-01-23 | 2009-07-28 | 삼성전자주식회사 | 저항성 메모리 소자 및 그 제조방법 |

| JP5252961B2 (ja) * | 2008-03-21 | 2013-07-31 | 三菱電機株式会社 | 半導体装置の製造方法 |

| KR101496148B1 (ko) * | 2008-05-15 | 2015-02-27 | 삼성전자주식회사 | 반도체소자 및 그 제조방법 |

| KR101322267B1 (ko) * | 2008-06-12 | 2013-10-25 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 그 제조방법 |

| EP2139054A3 (en) * | 2008-06-25 | 2011-08-31 | Samsung Electronics Co., Ltd. | Memory device and method of manufacturing the same |

| US8129718B2 (en) * | 2008-08-28 | 2012-03-06 | Canon Kabushiki Kaisha | Amorphous oxide semiconductor and thin film transistor using the same |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| KR101603303B1 (ko) * | 2008-10-31 | 2016-03-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 도전성 산질화물 및 도전성 산질화물막의 제작 방법 |

| JP5515281B2 (ja) * | 2008-12-03 | 2014-06-11 | ソニー株式会社 | 薄膜トランジスタ、表示装置、電子機器および薄膜トランジスタの製造方法 |

| CN102257621B (zh) * | 2008-12-19 | 2013-08-21 | 株式会社半导体能源研究所 | 晶体管的制造方法 |

| JP2010205987A (ja) * | 2009-03-04 | 2010-09-16 | Sony Corp | 薄膜トランジスタおよびその製造方法並びに表示装置 |

| WO2010103935A1 (en) | 2009-03-12 | 2010-09-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| WO2011001879A1 (en) * | 2009-06-30 | 2011-01-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101476817B1 (ko) * | 2009-07-03 | 2014-12-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터를 갖는 표시 장치 및 그 제작 방법 |

| TWI596741B (zh) * | 2009-08-07 | 2017-08-21 | 半導體能源研究所股份有限公司 | 半導體裝置和其製造方法 |

| JP2011049297A (ja) * | 2009-08-26 | 2011-03-10 | Toppan Printing Co Ltd | 薄膜トランジスタの製造方法 |

| WO2011040213A1 (en) | 2009-10-01 | 2011-04-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR101082254B1 (ko) * | 2009-11-04 | 2011-11-09 | 삼성모바일디스플레이주식회사 | 유기전계발광 표시 장치 및 그의 제조 방법 |

| KR101615636B1 (ko) * | 2009-12-08 | 2016-04-27 | 삼성전자주식회사 | 트랜지스터 및 상기 트랜지스터를 포함한 전자 장치 |

| JP5727204B2 (ja) | 2009-12-11 | 2015-06-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR101623956B1 (ko) * | 2010-01-15 | 2016-05-24 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| JP5482286B2 (ja) * | 2010-02-25 | 2014-05-07 | ソニー株式会社 | 放射線撮像装置およびその駆動方法 |

| US8956944B2 (en) | 2011-03-25 | 2015-02-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9219159B2 (en) | 2011-03-25 | 2015-12-22 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming oxide semiconductor film and method for manufacturing semiconductor device |

| TWI545652B (zh) | 2011-03-25 | 2016-08-11 | 半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| US8841665B2 (en) * | 2012-04-06 | 2014-09-23 | Electronics And Telecommunications Research Institute | Method for manufacturing oxide thin film transistor |

-

2012

- 2012-03-16 US US13/422,244 patent/US9012904B2/en active Active

- 2012-03-20 JP JP2012062923A patent/JP5912709B2/ja not_active Expired - Fee Related

-

2016

- 2016-03-17 JP JP2016053949A patent/JP6110975B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012216792A (ja) | 2012-11-08 |

| US20120241736A1 (en) | 2012-09-27 |

| JP5912709B2 (ja) | 2016-04-27 |

| US9012904B2 (en) | 2015-04-21 |

| JP2016149562A (ja) | 2016-08-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6110975B2 (ja) | 積層構造体、及びその作製方法 | |

| JP6149141B2 (ja) | 半導体装置 | |

| JP6378721B2 (ja) | 半導体装置 | |

| JP6310042B2 (ja) | 液晶表示装置 | |

| JP6127180B2 (ja) | 半導体装置 | |

| JP6110593B2 (ja) | 半導体装置 | |

| JP5964090B2 (ja) | 半導体装置 | |

| JP5986392B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170131 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170131 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170221 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170310 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6110975 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |