JP5663904B2 - 電気光学装置及びその製造方法、並びに電子機器 - Google Patents

電気光学装置及びその製造方法、並びに電子機器 Download PDFInfo

- Publication number

- JP5663904B2 JP5663904B2 JP2010050233A JP2010050233A JP5663904B2 JP 5663904 B2 JP5663904 B2 JP 5663904B2 JP 2010050233 A JP2010050233 A JP 2010050233A JP 2010050233 A JP2010050233 A JP 2010050233A JP 5663904 B2 JP5663904 B2 JP 5663904B2

- Authority

- JP

- Japan

- Prior art keywords

- light

- shielding film

- insulating film

- region

- contact hole

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 26

- 239000000758 substrate Substances 0.000 claims description 77

- 239000004065 semiconductor Substances 0.000 claims description 74

- 238000000034 method Methods 0.000 claims description 37

- 239000012535 impurity Substances 0.000 claims description 22

- 230000008569 process Effects 0.000 claims description 22

- 239000000463 material Substances 0.000 claims description 16

- 238000000137 annealing Methods 0.000 claims description 15

- 230000003213 activating effect Effects 0.000 claims description 5

- 230000003287 optical effect Effects 0.000 claims description 5

- 239000010408 film Substances 0.000 description 172

- 239000010410 layer Substances 0.000 description 99

- 239000004973 liquid crystal related substance Substances 0.000 description 42

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 8

- 239000004020 conductor Substances 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- WNUPENMBHHEARK-UHFFFAOYSA-N silicon tungsten Chemical compound [Si].[W] WNUPENMBHHEARK-UHFFFAOYSA-N 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 238000005530 etching Methods 0.000 description 5

- 239000011159 matrix material Substances 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 239000011521 glass Substances 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000003086 colorant Substances 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- 239000012780 transparent material Substances 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000002708 enhancing effect Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 239000003365 glass fiber Substances 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136209—Light shielding layers, e.g. black matrix, incorporated in the active matrix substrate, e.g. structurally associated with the switching element

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78633—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device with a light shield

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Nonlinear Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Liquid Crystal (AREA)

- Electromagnetism (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

Description

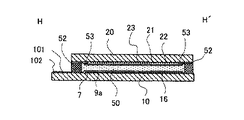

上記の本発明に係る電気光学装置は、基板と、データ線と、前記データ線に交差する走査線と、画素電極と、(i)前記データ線と電気的に接続された第1ソース・ドレイン領域、前記画素電極と電気的に接続された第2ソース・ドレイン領域、並びに前記第1ソース・ドレイン領域と前記第2ソース・ドレイン領域との間に配置されたチャネル領域を有する半導体層と、(ii)前記チャネル領域にゲート絶縁膜を介して対向するように配置されたゲート電極と、を有するトランジスターと、前記ゲート電極の上に配置される第1絶縁膜を介して前記ゲート電極と重なる部分を有するように配置され、前記第1絶縁膜を貫通するように配置された第1コンタクトホールを介して前記ゲート電極に電気的に接続された第1遮光膜と、前記半導体層と前記基板との間に配置される第2絶縁膜を介して前記半導体層に対向するように配置されており、前記第1絶縁膜、前記ゲート絶縁膜及び前記第2絶縁膜を貫通するように配置された第2コンタクトホールを介して前記第1遮光層と電気的に接続された第2遮光膜と、を備えることを特徴とする。

上記の本発明に係る電気光学装置は、基板上に、互いに交差するデータ線及び走査線と、前記データ線及び前記走査線の交差に対応する画素毎に設けられた画素電極と、(i)前記データ線と電気的に接続された第1ソース・ドレイン領域、前記画素電極と電気的に接続された第2ソース・ドレイン領域、並びに前記第1ソース・ドレイン領域及び前記第2ソース・ドレイン領域間に設けられたチャネル領域を有する半導体層と、(ii)前記チャネル領域にゲート絶縁膜を介して対向するように配置されたゲート電極を有するトランジスターと、前記ゲート電極より上側絶縁膜を介して上層側に前記ゲート電極と重なる部分を有して形成されると共に、前記上側絶縁膜に開孔された第1コンタクトホールを介して前記ゲート電極に電気的に接続された上側遮光膜と、前記半導体層より下側絶縁膜を介して下層側に形成されており、前記上側絶縁膜、前記ゲート絶縁膜及び前記下側絶縁膜を貫通するように開孔された第2コンタクトホールを介して前記上側遮光層と電気的に接続された下側遮光膜とを備える。

に所定電圧レベルのプリチャージ信号を画像信号に先行して各々供給するプリチャージ回路、製造途中や出荷時の当該液晶装置の品質、欠陥等を検査するための検査回路等を形成してもよい。

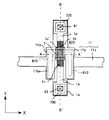

次に、図7及び図8を参照しながら、上述した本実施形態の液晶装置の製造方法を説明する。図7及び図8は、製造方法の各工程における図5及び図6に示す断面の構成を、順を追って示す工程断面図である。

次に、図9を参照しながら、上述した液晶装置を電子機器の一例であるプロジェクタに適用した場合を説明する。上述した液晶装置は、プロジェクタのライトバルブとして用いられている。図9は、プロジェクタの構成例を示す平面図である。

Claims (11)

- 基板と、

データ線と、

前記データ線に交差する走査線と、

画素電極と、

(i)前記データ線と電気的に接続された第1ソース・ドレイン領域、前記画素電極と電気的に接続された第2ソース・ドレイン領域、並びに前記第1ソース・ドレイン領域と前記第2ソース・ドレイン領域との間に配置されたチャネル領域を有する半導体層と、(ii)前記チャネル領域にゲート絶縁膜を介して対向するように配置されたゲート電極と、を有するトランジスターと、

前記ゲート電極の上に配置される第1絶縁膜を介して前記ゲート電極と重なる部分を有するように配置され、前記第1絶縁膜を貫通するように配置された第1コンタクトホールを介して前記ゲート電極に電気的に接続された第1遮光膜と、

前記半導体層と前記基板との間に配置される第2絶縁膜を介して前記半導体層に対向するように配置されており、前記第1絶縁膜、前記ゲート絶縁膜及び前記第2絶縁膜を貫通するように配置された第2コンタクトホールを介して前記第1遮光膜と電気的に接続された第2遮光膜と、

を備え、

前記第2遮光膜は前記走査線を兼ね、

前記第1遮光膜の側から前記第2遮光膜の側を見たとき、前記第1遮光膜が配置される領域は前記第2遮光膜が配置される領域に含まれることを特徴とする電気光学装置。 - 前記ゲート電極と前記第1遮光膜とは、同じ材料を含んでいることを特徴とする請求項1に記載の電気光学装置。

- 前記半導体層は、

前記第2ソース・ドレイン領域と前記チャネル領域との間に配置された接合領域を有し、

前記第1遮光膜は、前記接合領域を囲むように配置されていることを特徴とする請求項1または2に記載の電気光学装置。 - 前記第2コンタクトホールは、平面視して、前記第1遮光膜が前記チャネル領域に重な

る部分の脇から、前記半導体層に沿って形成されていることを特徴とする請求項1乃至3のいずれか一項に記載の電気光学装置。 - 前記第1遮光膜は、2以上のOD値を有することを特徴とする請求項1乃至4のいずれか一項に記載の電気光学装置。

- 前記第1コンタクトホールは、前記第2コンタクトホールと一体的に形成されていることを特徴とする請求項1乃至5のいずれか一項に記載の電気光学装置。

- 基板の上に第2遮光膜を形成する第1工程と、

前記第2遮光膜の上に第2絶縁膜を形成する第2工程と、

前記第2絶縁膜の上に、半導体層、ゲート絶縁膜及びゲート電極を形成する第3工程と、

前記ゲート電極をマスクとして前記半導体層に不純物を注入し、アニール処理を行うことにより、注入された前記不純物を活性化させる第4工程と、

前記第4工程の後に、前記ゲート電極の上に第1絶縁膜を形成し、該第1絶縁膜に第1コンタクトホールを形成する第5工程と、

前記第2絶縁膜、前記ゲート絶縁膜及び前記第1絶縁膜を貫通するように第2コンタクトホールを形成する第6工程と、

平面視して、前記第1コンタクトホール及び前記第2コンタクトホールを介して、第1遮光膜と前記ゲート電極が電気的に接続されるように前記第1遮光膜を形成する第6工程と、

を備え、

前記第1遮光膜の側から前記第2遮光膜の側を見たとき、前記第1遮光膜が配置される領域は前記第2遮光膜が配置される領域に含まれることを特徴とする電気光学装置の製造方法。 - 前記第1遮光膜は前記ゲート電極と同じ材料を含むことを特徴とする請求項7に記載の電気光学装置の製造方法。

- 前記第1コンタクトホールと前記第2コンタクトホールとは、同時に形成されることを特徴とする請求項7または8に記載の電気光学装置の製造方法。

- 前記第1コンタクトホール及び前記第2コンタクトホールは、一体的に形成されることを特徴とする請求項7乃至9のいずれか一項に記載の電気光学装置の製造方法。

- 請求項1乃至6のいずれか一項に記載の電気光学装置を具備することを特徴とする電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010050233A JP5663904B2 (ja) | 2010-03-08 | 2010-03-08 | 電気光学装置及びその製造方法、並びに電子機器 |

| US13/040,389 US8130333B2 (en) | 2010-03-08 | 2011-03-04 | Electric optical device and electronic device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010050233A JP5663904B2 (ja) | 2010-03-08 | 2010-03-08 | 電気光学装置及びその製造方法、並びに電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011186108A JP2011186108A (ja) | 2011-09-22 |

| JP2011186108A5 JP2011186108A5 (ja) | 2013-04-11 |

| JP5663904B2 true JP5663904B2 (ja) | 2015-02-04 |

Family

ID=44530530

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010050233A Active JP5663904B2 (ja) | 2010-03-08 | 2010-03-08 | 電気光学装置及びその製造方法、並びに電子機器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8130333B2 (ja) |

| JP (1) | JP5663904B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI447983B (zh) * | 2011-05-24 | 2014-08-01 | Au Optronics Corp | 半導體結構以及有機電致發光元件 |

| JP2013080040A (ja) | 2011-10-03 | 2013-05-02 | Seiko Epson Corp | 電気光学装置、電気光学装置の製造方法、及び電子機器 |

| KR102067669B1 (ko) | 2012-11-06 | 2020-01-20 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| KR102050460B1 (ko) * | 2012-11-30 | 2019-11-29 | 엘지디스플레이 주식회사 | 박막 트랜지스터 기판 및 그를 이용한 디스플레이 장치 |

| JP6044358B2 (ja) | 2013-01-18 | 2016-12-14 | セイコーエプソン株式会社 | 電気光学装置用基板、電気光学装置、および電子機器 |

| JP2016134388A (ja) * | 2015-01-15 | 2016-07-25 | 株式会社ジャパンディスプレイ | 表示装置 |

| TWI578509B (zh) * | 2015-07-23 | 2017-04-11 | 友達光電股份有限公司 | 畫素結構 |

| JP6977561B2 (ja) * | 2015-11-18 | 2021-12-08 | ソニーグループ株式会社 | 半導体装置および投射型表示装置 |

| TWI559511B (zh) * | 2016-03-03 | 2016-11-21 | 友達光電股份有限公司 | 導電元件基板、導電元件基板的製造方法以及顯示面板 |

| CN107154346B (zh) * | 2017-05-19 | 2021-03-16 | 京东方科技集团股份有限公司 | 一种膜层的掺杂方法、薄膜晶体管及其制作方法 |

| CN108459445B (zh) * | 2018-03-30 | 2021-05-18 | 上海天马微电子有限公司 | 一种液晶显示面板、显示装置及液晶显示面板的制备方法 |

| KR102621005B1 (ko) * | 2018-12-26 | 2024-01-05 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| JP7491144B2 (ja) | 2020-08-27 | 2024-05-28 | セイコーエプソン株式会社 | 電気光学装置、および電子機器 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3307181B2 (ja) * | 1995-07-31 | 2002-07-24 | ソニー株式会社 | 透過型表示装置 |

| JP3356429B2 (ja) * | 2000-04-11 | 2002-12-16 | 日本電気株式会社 | 液晶表示装置および液晶プロジェクタ装置 |

| JP4233307B2 (ja) * | 2002-11-05 | 2009-03-04 | シャープ株式会社 | アクティブマトリクス基板および表示装置 |

| JP4100351B2 (ja) * | 2004-02-09 | 2008-06-11 | セイコーエプソン株式会社 | 薄膜トランジスタの製造方法 |

| JP4876548B2 (ja) | 2005-11-22 | 2012-02-15 | セイコーエプソン株式会社 | 電気光学装置の製造方法 |

| JP4241777B2 (ja) * | 2006-07-25 | 2009-03-18 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP4349406B2 (ja) | 2006-08-24 | 2009-10-21 | セイコーエプソン株式会社 | 電気光学装置用基板及び電気光学装置、並びに電子機器 |

| JP5104140B2 (ja) * | 2007-09-10 | 2012-12-19 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP2009139417A (ja) * | 2007-12-03 | 2009-06-25 | Seiko Epson Corp | 電気光学装置及びその製造方法並びに電子機器 |

-

2010

- 2010-03-08 JP JP2010050233A patent/JP5663904B2/ja active Active

-

2011

- 2011-03-04 US US13/040,389 patent/US8130333B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20110215337A1 (en) | 2011-09-08 |

| JP2011186108A (ja) | 2011-09-22 |

| US8130333B2 (en) | 2012-03-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5663904B2 (ja) | 電気光学装置及びその製造方法、並びに電子機器 | |

| JP5245333B2 (ja) | 電気光学装置及び電子機器 | |

| JP5532568B2 (ja) | 電気光学装置及び電子機器 | |

| WO2001081994A1 (fr) | Dispositif electro-optique, affichage par projection et procede de fabrication dudit dispositif electro-optique | |

| JP5381031B2 (ja) | 電気光学装置及び電子機器 | |

| JP2009122253A (ja) | 電気光学装置及び電子機器 | |

| JP4211644B2 (ja) | 電気光学装置の製造方法 | |

| JP2009047967A (ja) | 電気光学装置及び電子機器 | |

| JP2009122256A (ja) | 電気光学装置及び電子機器 | |

| JP2008040399A (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP2010096966A (ja) | 電気光学装置及びその製造方法、並びに電子機器 | |

| JP2000081636A (ja) | 電気光学装置及びその製造方法並びに電子機器 | |

| JP5104140B2 (ja) | 電気光学装置及び電子機器 | |

| JP5298480B2 (ja) | 電気光学装置及び電子機器 | |

| JP2011186285A (ja) | 電気光学装置及びその製造方法、並びに電子機器 | |

| JP2011203288A (ja) | 電気光学装置及び電子機器 | |

| JP5292738B2 (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP2006253173A (ja) | 電気光学装置、その製造方法、及び電子機器 | |

| JP2009300477A (ja) | 電気光学装置及び電子機器 | |

| JP3991567B2 (ja) | 電気光学装置及び電子機器 | |

| JP2010008635A (ja) | 電気光学装置用基板の製造方法、電気光学装置用基板、電気光学装置及び電子機器 | |

| JP2011221119A (ja) | 電気光学装置及び電子機器、並びに電気光学装置の製造方法 | |

| JP5343476B2 (ja) | 電気光学装置及び電子機器 | |

| JP2010072219A (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP4984911B2 (ja) | 電気光学装置及び電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130222 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130919 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131008 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140812 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141009 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141111 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141124 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5663904 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |