JP5618963B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5618963B2 JP5618963B2 JP2011234814A JP2011234814A JP5618963B2 JP 5618963 B2 JP5618963 B2 JP 5618963B2 JP 2011234814 A JP2011234814 A JP 2011234814A JP 2011234814 A JP2011234814 A JP 2011234814A JP 5618963 B2 JP5618963 B2 JP 5618963B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- semiconductor

- semiconductor substrate

- semiconductor device

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 371

- 239000000758 substrate Substances 0.000 claims description 115

- 230000003071 parasitic effect Effects 0.000 description 33

- 238000010586 diagram Methods 0.000 description 16

- 230000007257 malfunction Effects 0.000 description 10

- 239000003990 capacitor Substances 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 208000032368 Device malfunction Diseases 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0617—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type

- H01L27/0629—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type in combination with diodes, or resistors, or capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/07—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common

- H01L27/0705—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type

- H01L27/0711—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type in combination with bipolar transistors and diodes, or capacitors, or resistors

- H01L27/0716—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration the components having an active region in common comprising components of the field effect type in combination with bipolar transistors and diodes, or capacitors, or resistors in combination with vertical bipolar transistors and diodes, or capacitors, or resistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Bipolar Integrated Circuits (AREA)

Description

(実施の形態1)

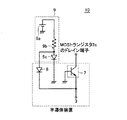

図1は、本発明の実施の形態1に係る半導体装置の構成を示す概略図である。図1に示す半導体装置10は、電力用であり、接続する負荷に電力を供給する電力素子1と、電力素子1を制御する回路素子2とを同一の半導体基板3に形成してある。さらに、半導体基板3には、電力素子1を形成した一面に、電力素子1および回路素子2に対し独立して配置したp型の半導体層4が形成してある。

実施の形態1に係る半導体装置10では、負電流が流れた場合、半導体層4に構成されるダイオード8の順方向に電流が導通し、ダイオード8を流れる電流が増加する。ダイオード8を流れる電流が増加すると、抵抗素子9bによる電圧降下によってダイオード9cのアノード電極の電位(半導体層4の電位)が下がる。

外部回路9の一部構成を半導体基板3内に形成する場合について説明する。図5は、本発明の実施の形態3に係る半導体装置の回路構成を示す回路図である。図5(a)に示す半導体装置10aは、図2に示す半導体装置10の外部回路9の一部構成を半導体基板3内に形成してある。具体的に、半導体装置10aは、抵抗素子9bおよびダイオード9cを半導体基板3に形成してある。抵抗素子9bは、半導体基板3にポリシリコン膜を形成することで構成し、ダイオード9cは、半導体基板3に注入する不純物の濃度を拡散することで構成してある。

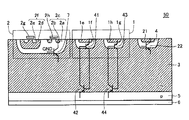

図6は、本発明の実施の形態4に係る半導体装置の構成を示す概略図である。図6に示す半導体装置40は、電力用であり、接続する負荷に電力を供給する電力素子1と、電力素子1を制御する回路素子2とを同一の半導体基板3に形成してある。

図8は、本発明の実施の形態5に係る半導体装置の構成を示す概略図である。図8に示す半導体装置50は、電力用であり、接続する負荷に電力を供給する電力素子1と、電力素子1を制御する回路素子2とを同一の半導体基板3に形成してある。さらに、半導体基板3には、電力素子1を形成した一面に、電力素子1および回路素子2に対し独立して配置したp型の半導体層4が形成してある。また、半導体装置50は、半導体層4内に、n型の半導体層21を形成してある。

図10は、本発明の実施の形態6に係る半導体装置60の回路構成を示す回路図である。図10に示す半導体装置60は、外部回路9以外の構成が実施の形態5に係る半導体装置50と同じであるため、半導体装置50と同じ構成要素について同じ符号を付して、詳細な説明を省略する。

Claims (8)

- 第1導電型の半導体基板と、

前記半導体基板の一面に形成し、接続する負荷に電力を供給する電力素子と、

前記電力素子を形成した前記半導体基板の前記一面に形成し、第1導電型のソース・ドレイン領域を有するMOSトランジスタを少なくとも1つ含む回路素子と、

前記電力素子を形成した前記半導体基板の前記一面に形成し、前記電力素子および前記回路素子に対し独立して配置した第2導電型の第1半導体層と、

前記半導体基板および前記第1半導体層と電気的に接続する外部回路と

を備え、

前記外部回路は、第1電源と、前記第1電源に一端を接続する第1抵抗素子と、前記第1抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地する第1ダイオードとを有し、

前記第1抵抗素子の他端に前記第1半導体層を接続する、半導体装置。 - 前記外部回路の前記第1抵抗素子および前記第1ダイオードのうち少なくとも一方を、前記半導体基板内に形成してある、請求項1に記載の半導体装置。

- 前記第1半導体層内に形成した第1導電型の第2半導体層をさらに備え、

前記第2半導体層と、前記第1半導体層と、前記半導体基板とで第1トランジスタを構成し、

前記第1抵抗素子の一端に前記第2半導体層を接続し、前記第1抵抗素子の他端に前記第1半導体層を接続する、請求項1または請求項2に記載の半導体装置。 - 前記電力素子を形成した前記半導体基板の前記一面に形成し、少なくとも前記回路素子および前記第1半導体層に対し独立して配置した第2導電型の第3半導体層と、

前記第3半導体層内に形成した第1導電型の第4半導体層と、

前記電力素子を形成した前記半導体基板の前記一面に形成し、少なくとも前記回路素子、前記第1半導体層および前記第3半導体層に対し独立して配置した第2導電型の第5半導体層と、

前記第5半導体層内に形成した第1導電型の第6半導体層とをさらに備え、

前記第4半導体層と、前記第3半導体層と、前記半導体基板とで第2トランジスタを、前記第6半導体層と、前記第5半導体層と、前記半導体基板とで第3トランジスタをそれぞれ構成し、

前記第2トランジスタおよび前記第3トランジスタのコレクタ電極は、前記半導体基板を介して接続し、

前記第1抵抗素子の他端に、前記第2トランジスタのベース電極を接続し、前記第2トランジスタのエミッタ電極に第2電源または第2抵抗素子を接続する、請求項3に記載の半導体装置。 - 前記第3トランジスタのエミッタ電極に、一端を接続する第3抵抗素子と、

前記第3抵抗素子の他端にアノード電極を接続し、前記第1抵抗素子の一端にカソード電極を接続した第2ダイオードと、

前記第1電源に対して並列に接続した容量素子と、

前記容量素子に対して並列に接続した第3ダイオードと、

前記第3ダイオードと前記第1電源との間に接続した第4抵抗素子と

をさらに備える、請求項4に記載の半導体装置。 - 前記第2抵抗素子、前記第3抵抗素子、前記第2ダイオード、前記第3ダイオードおよび前記容量素子のうち少なくとも1つは、前記半導体基板内に形成してある、請求項5に記載の半導体装置。

- 前記第1トランジスタ、前記第2トランジスタおよび前記第3トランジスタは、前記電力素子に形成する、請求項4〜請求項6のいずれか1項に記載の半導体装置。

- 前記第1半導体層内に形成した第1導電型の第2半導体層と、

前記電力素子を形成した前記半導体基板の前記一面に形成し、少なくとも前記回路素子および前記第1半導体層に対し独立して配置した第2導電型の第3半導体層と、

前記第3半導体層内に形成した第1導電型の第4半導体層とをさらに備え、

前記第2半導体層と、前記第1半導体層と、前記半導体基板とで第1トランジスタを、前記第4半導体層と、前記第3半導体層と、前記半導体基板とで第2トランジスタをそれぞれ構成し、

前記第1トランジスタおよび前記第2トランジスタのコレクタ電極は、前記半導体基板を介して接続し、

前記第1抵抗素子の他端に、前記第1トランジスタのベース電極を接続し、前記第1トランジスタのエミッタ電極に第2電源または第2抵抗素子を接続する、請求項1に記載の半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011234814A JP5618963B2 (ja) | 2011-10-26 | 2011-10-26 | 半導体装置 |

| US13/534,695 US8536655B2 (en) | 2011-10-26 | 2012-06-27 | Semiconductor device with power element and circuit element formed within the same semiconductor substrate |

| DE102012218765.0A DE102012218765B4 (de) | 2011-10-26 | 2012-10-15 | Halbleitervorrichtung mit innerhalb desselben Halbleitersubstrats ausgebildetem Leistungselement und Schaltungselement |

| CN201210416161.XA CN103077946B (zh) | 2011-10-26 | 2012-10-26 | 在同一半导体衬底内形成电力和电路元件的半导体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011234814A JP5618963B2 (ja) | 2011-10-26 | 2011-10-26 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013093448A JP2013093448A (ja) | 2013-05-16 |

| JP2013093448A5 JP2013093448A5 (ja) | 2014-01-30 |

| JP5618963B2 true JP5618963B2 (ja) | 2014-11-05 |

Family

ID=48084554

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011234814A Active JP5618963B2 (ja) | 2011-10-26 | 2011-10-26 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8536655B2 (ja) |

| JP (1) | JP5618963B2 (ja) |

| CN (1) | CN103077946B (ja) |

| DE (1) | DE102012218765B4 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9391448B2 (en) * | 2013-09-17 | 2016-07-12 | The Boeing Company | High current event mitigation circuit |

| JP5989265B2 (ja) * | 2014-05-30 | 2016-09-07 | 三菱電機株式会社 | 電力用半導体素子の駆動回路 |

| EP3382750B1 (en) * | 2015-12-28 | 2020-10-14 | Rohm Co., Ltd. | Semiconductor device |

| JP7227117B2 (ja) * | 2019-11-08 | 2023-02-21 | 株式会社東芝 | 半導体装置 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4933573A (en) * | 1987-09-18 | 1990-06-12 | Fuji Electric Co., Ltd. | Semiconductor integrated circuit |

| JPH06350032A (ja) | 1993-06-08 | 1994-12-22 | Toshiba Corp | 半導体装置の配線構体 |

| US5467050A (en) * | 1994-01-04 | 1995-11-14 | Texas Instruments Incorporated | Dynamic biasing circuit for semiconductor device |

| JP3400853B2 (ja) * | 1994-04-27 | 2003-04-28 | 三菱電機株式会社 | 半導体装置 |

| JP3532276B2 (ja) * | 1995-01-06 | 2004-05-31 | 株式会社ルネサステクノロジ | 基板バイアス回路 |

| JP4128700B2 (ja) * | 1999-09-08 | 2008-07-30 | ローム株式会社 | 誘導性負荷駆動回路 |

| JP4607291B2 (ja) | 2000-06-29 | 2011-01-05 | 三菱電機株式会社 | 半導体装置 |

| JP2005252044A (ja) * | 2004-03-05 | 2005-09-15 | Fujitsu Ten Ltd | 半導体集積回路の寄生トランジスタ発生防止装置、及び半導体集積回路の寄生トランジスタ発生防止方法 |

| JP2006156959A (ja) | 2004-10-26 | 2006-06-15 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| US7173315B2 (en) | 2004-10-26 | 2007-02-06 | Matsushita Electric Industrial Co., Ltd. | Semiconductor device |

| JP2006332539A (ja) * | 2005-05-30 | 2006-12-07 | Sanken Electric Co Ltd | 半導体集積回路装置 |

| JP5011748B2 (ja) * | 2006-02-24 | 2012-08-29 | 株式会社デンソー | 半導体装置 |

| JP2008140824A (ja) * | 2006-11-30 | 2008-06-19 | Toshiba Corp | 半導体装置 |

| JP2008311300A (ja) * | 2007-06-12 | 2008-12-25 | Toyota Motor Corp | パワー半導体装置、パワー半導体装置の製造方法、およびモータ駆動装置 |

| JP2010118548A (ja) * | 2008-11-13 | 2010-05-27 | Mitsubishi Electric Corp | 半導体装置 |

| JP5423377B2 (ja) | 2009-12-15 | 2014-02-19 | 三菱電機株式会社 | イグナイタ用電力半導体装置 |

-

2011

- 2011-10-26 JP JP2011234814A patent/JP5618963B2/ja active Active

-

2012

- 2012-06-27 US US13/534,695 patent/US8536655B2/en active Active

- 2012-10-15 DE DE102012218765.0A patent/DE102012218765B4/de active Active

- 2012-10-26 CN CN201210416161.XA patent/CN103077946B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20130106499A1 (en) | 2013-05-02 |

| JP2013093448A (ja) | 2013-05-16 |

| DE102012218765A1 (de) | 2013-05-02 |

| DE102012218765B4 (de) | 2019-02-07 |

| CN103077946B (zh) | 2015-09-16 |

| US8536655B2 (en) | 2013-09-17 |

| CN103077946A (zh) | 2013-05-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4942007B2 (ja) | 半導体集積回路 | |

| JP5438469B2 (ja) | 負荷駆動装置 | |

| JP6213136B2 (ja) | 半導体装置 | |

| US7456441B2 (en) | Single well excess current dissipation circuit | |

| JP4383159B2 (ja) | チャージポンプ回路 | |

| JP7031983B2 (ja) | ボルテージレギュレータ | |

| JP5618963B2 (ja) | 半導体装置 | |

| TWI765956B (zh) | 半導體裝置 | |

| JP2006080160A (ja) | 静電保護回路 | |

| JP4775684B2 (ja) | 半導体集積回路装置 | |

| JP6397926B2 (ja) | センサ装置 | |

| JP2006269902A (ja) | 半導体集積回路 | |

| JP4723443B2 (ja) | 半導体集積回路 | |

| JP2019103015A (ja) | 電源逆接続保護機能を備えた負荷駆動回路 | |

| JP3739365B2 (ja) | 半導体装置 | |

| WO2022134606A1 (zh) | 静电保护结构、静电保护电路、芯片 | |

| JP3680036B2 (ja) | 半導体回路、及び、フォトカップラー | |

| JP4775682B2 (ja) | 半導体集積回路装置 | |

| KR20120068142A (ko) | 방전소자 | |

| KR101349998B1 (ko) | 정전기 방전 보호 장치 | |

| JP2007189048A (ja) | 半導体装置 | |

| JP2010177561A (ja) | 半導体装置 | |

| JP2014053497A (ja) | Esd保護回路 | |

| JP5252830B2 (ja) | 半導体集積回路 | |

| JP2005109051A (ja) | 半導体集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131206 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140417 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140422 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140530 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140819 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140916 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5618963 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |