JP5282419B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP5282419B2 JP5282419B2 JP2008060164A JP2008060164A JP5282419B2 JP 5282419 B2 JP5282419 B2 JP 5282419B2 JP 2008060164 A JP2008060164 A JP 2008060164A JP 2008060164 A JP2008060164 A JP 2008060164A JP 5282419 B2 JP5282419 B2 JP 5282419B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- insulating film

- film

- offset spacer

- silicon nitride

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/021—Manufacture or treatment using multiple gate spacer layers, e.g. bilayered sidewall spacers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/017—Manufacture or treatment using dummy gates in processes wherein at least parts of the final gates are self-aligned to the dummy gates, i.e. replacement gate processes

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Description

ダマシンプロセスにおいては、例えば、基板の絶縁膜にゲート電極用溝を形成し、ゲート電極用溝の内部を埋めこんで導電性材料を堆積させ、CMP(化学機械研磨)処理などを行い、ゲート電極用溝内に導電性材料を残して外部の導電性材料を除去することにより、配線とする。

ゲート絶縁膜として用いられるSiON系絶縁膜は、32nmルール以降の世代ではリークが大きくなってしまうのでゲート絶縁膜として用いることは難しい。

一般に、High−k膜は耐熱性が弱いため、高温処理が必要なソース・ドレイン領域の拡散熱処理の後でゲート絶縁膜を形成する必要がある。

上記の手順を可能にする方法として、上記のダマシンプロセスを用いて、MOSトランジスタのゲート電極を形成するダマシンゲートプロセスが知られている。

以上のようにして、エクステンション領域が設けられたソース・ドレイン領域を形成することができる。

以上のようにして、ダマシンゲートプロセスを用いてMOSトランジスタを形成することができる。

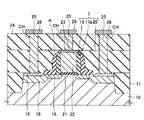

図1は、本実施形態に係る半導体装置の模式断面図である。

例えば、チャネル形成領域を有するシリコンの半導体基板10に、活性領域を区切るSTI(shallow trench isolation)法による素子分離絶縁膜11が形成されており、半導体基板10上に、オフセットスペーサ15、窒化シリコン膜(サイドウォールスペーサ)17a及び層間絶縁膜20などを含む絶縁膜Iが形成されている。

例えば、上記の絶縁膜Iにはゲート電極用溝Aが形成されており、ゲート電極用溝Aの底部には、酸化ハフニウムあるいは酸化アルミニウムなどの酸化シリコンより誘電率が高い、いわゆるHigh−k膜あるいは酸化シリコンなどからなるゲート絶縁膜21が形成されている。また、ゲート絶縁膜21の上層においてゲート電極用溝Aに埋め込まれて、ポリシリコンあるいは金属材料などからなるゲート電極22が形成されている。また、ゲート電極22がポリシリコンなどからなる場合、図示のようにゲート電極22の上部表面にNiSiなどの高融点金属シリサイド層23が形成されている。ゲート電極22が金属材料などからなる場合、例えば、タングステン、ハフニウム、タンタル、チタン、モリブデン、ルテニウム、ニッケル、白金からなる群から選択された金属、該金属を含む合金、または、該金属の化合物からなる。

また、窒化シリコン膜(サイドウォールスペーサ)17aは、絶縁膜Iの一部として半導体基板10に接して形成され、ゲート電極22から遠い側のオフセットスペーサ15の両側部に形成されている。

層間絶縁膜20は、例えば酸化シリコンから形成されている。

上記のようにして、電界効果トランジスタが構成されている。

まず、図2(a)に示すように、例えば、チャネル形成領域を有するシリコンの半導体基板10において、STI(shallow trench isolation)法により、活性領域を区切る素子分離絶縁膜11を形成する。

次に、例えば熱酸化法により全面に膜厚4nm程度の酸化シリコンを形成し、さらにCVD(化学気相成長)法により膜厚が150〜200nmのポリシリコンを堆積し、さらに膜厚が50〜100nmの窒化シリコンを堆積させる。つづいて、フォトリソグラフィによりゲート形成領域を残してエッチング加工することにより、半導体基板10の活性領域におけるゲート電極形成領域上において、酸化シリコンのダミーゲート絶縁膜12、ポリシリコンからなるダミーゲート電極13、及び窒化シリコンからなるハードマスク層14を積層する。

例えば、ホウ素を1.5〜3.5×1015/cm2のドーズ量、2〜4keVのエネルギーで注入する。

以上のようにして、少なくともオフセットスペーサ15及びサイドウォールスペーサ17の下部における半導体基板10において、エクステンション領域16を有するソース・ドレイン領域18が形成される。

この後、不純物の活性化のためにRTA処理(1050℃)の熱処理を施す。

ここで、上記のDHF処理において、サイドウォールスペーサを構成する酸化シリコン膜17bが除去されてしまう。以降は、窒化シリコン膜17aのみでもサイドウォールスペーサと称することがある。

上記のようにして得られた層間絶縁膜20と、オフセットスペーサ15及び窒化シリコン膜(サイドウォールスペーサ)17aを合わせて絶縁膜Iと称する。

上記のエッチングが、酸化シリコンのダミーゲート絶縁膜に対して十分に選択比を有するようなエッチング条件とする。

上記のダミーゲート絶縁膜12の除去のためのエッチング処理は、まず、第1処理として、露出したダミーゲート絶縁膜12の表面をアンモニア及びフッ化水素を含むエッチングガスで処理する。次に、第2処理として、第1処理で形成された生成物を分解及び蒸発させる。

ダミーゲート絶縁膜12の表面を、NH3,HF,Arからなる混合ガス雰囲気でケミカルエッチングする。

具体的には、エッチング装置のケミカルエッチング室にウェーハ(半導体基板10)を搬送し、ウェーハ用ステージにウェーハを載置した後に、以下のガス雰囲気をつくり、ダミーゲート絶縁膜12の表面にSiを含む錯体を形成させる。

NH3/HF/Ar=50/50/80sccm,圧力=6.7Pa,ステージ温度=30℃

ケミカルエッチング室に、気相でHF/NH3/Arが供給されると、ダミーゲート絶縁膜12の表面に露出している酸化シリコンの表面に、ガスがラングミュア吸着される。同時に次のような化学反応が進行する。

SiO2+4HF→SiF4+2H2O (1)

SiF4+2NH3+2HF→(NH4)2SiF6 (2)

この反応は、ラングミュア吸着による分子数層レベルのガス吸着に支配されており、吸着ガス分子の被覆率が飽和すると自己停止する。したがって、(NH4)2SiF6錯体の生成量も飽和する。

ステージ温度=200℃,圧力=26.7Pa

この反応は以下の式で説明される。酸化シリコンのダミーゲート絶縁膜12の表面に被覆した(NH4)2SiF6の錯体は、基板温度が200℃に加熱されると、SiF4、NH3、HFなどに分解して蒸発し、ガスとしてドライポンプにより排気される。

(NH4)2SiF6→SiF4+2NH3+HF

例えば、ガスの供給時間を設定することで、酸化シリコンのダミーゲート絶縁膜12のエッチング量を所望の値にできる。

以上のようにして、絶縁膜Iにゲート電極用溝Aを形成する。

例えば、オフセットスペーサ15の厚みを8nm、ダミーゲート絶縁膜12の厚みを4nmとし、上記のエッチング条件でエッチングすると、ダミーゲート絶縁膜12を完全にエッチングするまでに45秒を要し、この間にオフセットスペーサ15は3.9nm除去される。従って、4.1nm程度の厚みでオフセットスペーサを残すことが可能となる。

次に、例えば、スパッタリング法あるいはCVD法などにより、ゲート絶縁膜21の上層において、ゲート電極用溝Aの内壁面を被覆して、ルテニウム、窒化チタン、ハフニウムシリサイド(HfSix)やタングステンなどの金属材料またはポリシリコンなどの導電体材料を堆積させ、研磨などによりゲート電極用溝Aの外部に堆積された導電体材料を除去し、ゲート電極22を形成する。

さらに、ゲート電極22をポリシリコンなどで形成した場合には、ゲート電極22の上部表面にNiSiなどの高融点金属シリサイド層23を形成してもよい。

次に、上層絶縁膜24及び層間絶縁膜20を貫通して、ソース・ドレイン領域18の高融点金属シリサイド層19及びゲート電極22の高融点金属シリサイド層23に達する開口部CHを形成する。

得られた開口部CH内に、金属などの導電性材料からなるプラグ25を埋め込んで形成し、さらに、これに接続して上層絶縁膜24上に導電性材料からなる上層配線26を形成する。

以上で、図1に示す構造の半導体装置と同様の半導体装置を製造することができる。

本実施形態に係る半導体装置は、実質的に第1実施形態と同様である。

本実施形態に係る半導体装置の製造方法について図面を参照して説明する。

まず、図7(a)に示すように、まず、チャネル形成領域を有するシリコンの半導体基板10において、STI法により活性領域を区切る素子分離絶縁膜11を形成する。次に、熱酸化法により全面に膜厚4nm程度の酸化シリコンを堆積し、さらにCVD法によりポリシリコン及び窒化シリコンを堆積させ、フォトリソグラフィによりゲート形成領域を残してエッチング加工することで、ダミーゲート絶縁膜12、ポリシリコンからなるダミーゲート電極13、及び窒化シリコンからなるハードマスク層14を積層する。

次に、例えば、プラズマCVD法あるいはALD(原子層堆積)法などにより、全面に0.28nmの厚みで窒化シリコンを堆積し、さらにCVD法などによって8〜14nmの厚みの酸化シリコンを堆積し、全面にエッチバックすることで、ダミーゲート電極13の両側部に半導体基板10に接して、窒化シリコン膜15a及び酸化シリコン膜15bからなるオフセットスペーサ15を形成する。

上記のエッチングが、酸化シリコンのダミーゲート絶縁膜に対して十分に選択比を有するようなエッチング条件とする。

以上のようにして、絶縁膜Iにゲート電極用溝Aを形成する。

ダミーゲート絶縁膜を除去する処理時間が変更になった場合には、窒化シリコン膜15aの厚みを適宜変更することができる。

以上で、本実施形態に係る半導体装置と同様の半導体装置を製造することができる。

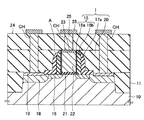

図9は、本実施形態に係る半導体装置の断面図である。

実質的に第1実施形態と同様であるが、オフセットスペーサ15が、窒化シリコン膜15aと酸化シリコン膜15bの積層体として残されていることが異なる。上記以外は第1実施形態と同様である。

まず、図10(a)に示すように、例えば第2実施形態と同様にして、ダミーゲート電極13(及びハードマスク層14)を除去工程までを行う。

以上のようにして、絶縁膜Iにゲート電極用溝Aを形成する。

ダミーゲート絶縁膜を除去する処理時間が変更になった場合には、窒化シリコン膜15aの厚みを適宜変更することができる。

以上で、本実施形態に係る半導体装置と同様の半導体装置を製造することができる。

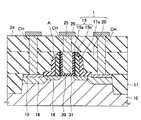

図11は、本実施形態に係る半導体装置の断面図である。

実質的に第1実施形態と同様であるが、オフセットスペーサ15、窒化シリコン膜(サイドウォールスペーサ)17a、層間絶縁膜20を含む絶縁膜Iの厚みがより薄くなっており、即ち、ゲート電極22の高さもより低く形成されている。上記以外は第1実施形態と同様である。

まず、図12(a)に示すように、例えば、第1実施形態と同様にして、ソース・ドレイン領域の表面に高融点金属シリサイド層19を形成する工程までを行う。

上記のようにして得られた層間絶縁膜20と、オフセットスペーサ15及び窒化シリコン膜(サイドウォールスペーサ)17aを合わせて絶縁膜Iと称する。

例えば、ハードマスク層14を有していた場合には、ハードマスク層14が完全に研磨除去されて、ダミーゲート電極13の表面が露出する程度とすることができる。あるいは、さらにダミーゲート電極13の途中の高さまで研磨してもよい。

また、ハードマスク層14が有していない場合には、ダミーゲート電極13の途中の高さまで研磨除去する。

以上で、本実施形態に係る半導体装置と同様の半導体装置を製造することができる。

図13は、本実施形態に係る半導体装置の断面図である。

実質的に第3実施形態と同様であるが、上記の第4実施形態と同様にオフセットスペーサ15、窒化シリコン膜(サイドウォールスペーサ)17a、層間絶縁膜20を含む絶縁膜Iの厚みがより薄くなっており、即ち、ゲート電極22の高さもより低く形成されている。上記以外は第3実施形態と同様である。

図14〜図17は、本実施形態に係る半導体装置の断面図である。

実質的に上記の第1〜第5実施形態と同様であるが、ゲート絶縁膜として、ALD法によりゲート電極用溝Aの内壁を被覆して、酸化ハフニウムや酸化アルミニウムなどのいわゆるHigh−k材料からなるゲート絶縁膜30が形成されており、ゲート絶縁膜30の上層においてゲート電極用溝Aを埋め込んでルテニウムやタングステンなどの金属材料が埋め込まれてゲート電極31が構成されている。

図14が第1及び第2実施形態、図15が第3実施形態、図16が第4実施形態、図17が第5実施形態にそれぞれ対応している。

第1実施形態において記載された、ダミーゲート絶縁膜を除去するためのエッチング法について、熱酸化法による酸化シリコン膜(a)、TEOSを原料とするプラズマCVD法による酸化シリコン膜(b)、プラズマCVD法による窒化シリコン膜(c)について、エッチング処理時間とエッチング量の関係を調べた。

結果を図18に示す。

また、窒化シリコン膜(c)の場合には、常に熱酸化法による酸化シリコン膜(a)のエッチング量より小さく、それぞれの材料をダミーゲート絶縁膜とオフセットスペーサとして用いることで、オフセットスペーサを残しながら、ダミーゲート電極を除去することができる。

例えば、ゲート絶縁膜及びゲート電極を構成する材料は、上記の実施形態に限定されない。

高融点金属シリサイド層は形成されていなくてもよい。

オフセットスペーサの材料は、例えば第1実施形態においては酸化シリコン膜の代わりにホウ素含有窒化シリコン(SiBN)膜を用いてもよく、第2実施形態においては窒化シリコン膜と酸化シリコン膜の積層体の代わりに窒化シリコン膜とホウ素含有窒化シリコン膜の積層体を用いてもよく、また、第3実施形態においては窒化シリコン膜と酸化シリコン膜の積層体の代わりにホウ素含有窒化シリコン膜と酸化シリコン膜の積層体を用いてもよい。ホウ素含有窒化シリコン膜は、窒化シリコン膜と比較し比誘電率が低く、B/N比が2のときに比誘電率は5程度になる。また、SiBNは酸化シリコン膜と比較し耐酸性が高く、エッチング処理の際にエッチング量が比較的少ないため、酸化シリコン膜をオフセットスペーサとして用いる場合よりも薄く形成することができる。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

また、本発明の半導体装置の製造方法は、MOSFETを有する半導体装置を製造する方法に適用できる。

Claims (5)

- チャネル形成領域を有する半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜に形成されたゲート電極用溝と、

前記ゲート電極用溝の底部に形成されたゲート絶縁膜と、

前記ゲート絶縁膜の上層において前記ゲート電極用溝に埋め込まれて形成されたゲート電極と、

前記絶縁膜の一部として前記ゲート電極用溝の側壁を構成し、前記ゲート電極側からホウ素含有窒化シリコン膜と酸化シリコン膜とが積層した構成のオフセットスペーサと、

前記絶縁膜の一部として前記ゲート電極から遠い側の前記オフセットスペーサの両側部に形成されたサイドウォールスペーサと、

少なくとも前記オフセットスペーサ及び前記サイドウォールスペーサの下部における前記半導体基板において形成されたエクステンション領域を有するソース・ドレイン領域と

を有し、電界効果トランジスタが構成されており、

前記オフセットスペーサの前記ゲート電極側端面の位置が、実質的に前記エクステンション領域のチャネル側の先端の位置決めになっており、

前記オフセットスペーサにおいて、前記ホウ素含有窒化シリコン膜が前記酸化シリコン膜より薄い

半導体装置。 - 前記ゲート電極は、タングステン、ハフニウム、タンタル、チタン、モリブデン、ルテニウム、ニッケル、白金からなる群から選択された金属、該金属を含む合金、または、該金属の化合物からなる

請求項1に記載の半導体装置。 - チャネル形成領域を有する半導体基板にダミーゲート絶縁膜及びダミーゲート電極を形成する工程と、

前記ダミーゲート電極の両側部にホウ素含有窒化シリコン膜と酸化シリコン膜とを順に、前記ホウ素含有窒化シリコン膜を前記酸化シリコン膜より薄くなるように積層させてオフセットスペーサを形成する工程と、

前記オフセットスペーサ及び前記ゲート電極をマスクとして前記半導体基板にエクステンション領域を形成する工程と、

前記オフセットスペーサの両側部にサイドウォールスペーサを形成する工程と、

前記サイドウォールスペーサ、前記オフセットスペーサ及び前記ゲート電極をマスクとして前記半導体基板にソース・ドレイン領域を形成する工程と、

前記ダミーゲート電極を被覆する絶縁膜を形成する工程と、

前記絶縁膜の上面から前記ダミーゲート電極が露出するまで前記絶縁膜を除去する工程と、

前記オフセットスペーサを構成する前記ホウ素含有窒化シリコン膜の少なくとも一部を残しながら、前記ダミーゲート電極及びダミーゲート絶縁膜を除去してゲート電極用溝を形成する工程と、

前記ゲート電極用溝の底部にゲート絶縁膜を形成する工程と、

前記ゲート電極用溝を埋め込んで前記ゲート絶縁膜の上層に導電層を形成する工程と、

前記ゲート電極用溝の外部の前記導電層を除去する工程と

を有して、電界効果トランジスタを形成することを特徴とする

半導体装置の製造方法。 - 少なくとも前記ダミーゲート絶縁膜を除去する工程において、露出した前記絶縁層の表面をアンモニア及びフッ化水素を含むエッチングガスで処理する第1処理と、前記第1処理で形成された生成物を分解及び蒸発させる第2処理とを含むエッチング処理を行う

ことを特徴とする

請求項3に記載の半導体装置の製造方法。 - 前記エッチング処理において前記第1処理で形成され、前記第2処理で分解及び蒸発される前記生成物が、(NH4)2SiF6錯体である

請求項4に記載の半導体装置の製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008060164A JP5282419B2 (ja) | 2007-04-18 | 2008-03-10 | 半導体装置及びその製造方法 |

| TW097112894A TWI446522B (zh) | 2007-04-18 | 2008-04-09 | 半導體裝置及其製造方法 |

| US12/101,568 US8350335B2 (en) | 2007-04-18 | 2008-04-11 | Semiconductor device including off-set spacers formed as a portion of the sidewall |

| KR1020080035540A KR101457006B1 (ko) | 2007-04-18 | 2008-04-17 | 반도체 디바이스 및 그 제조 방법 |

| CN2008102103134A CN101335300B (zh) | 2007-04-18 | 2008-04-18 | 半导体装置及其制造方法 |

| US12/817,949 US20100255650A1 (en) | 2007-04-18 | 2010-06-17 | Semiconductor device and method for manufacturing the same |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007108953 | 2007-04-18 | ||

| JP2007108953 | 2007-04-18 | ||

| JP2008060164A JP5282419B2 (ja) | 2007-04-18 | 2008-03-10 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008288560A JP2008288560A (ja) | 2008-11-27 |

| JP2008288560A5 JP2008288560A5 (ja) | 2010-04-15 |

| JP5282419B2 true JP5282419B2 (ja) | 2013-09-04 |

Family

ID=40147954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008060164A Expired - Fee Related JP5282419B2 (ja) | 2007-04-18 | 2008-03-10 | 半導体装置及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| JP (1) | JP5282419B2 (ja) |

| KR (1) | KR101457006B1 (ja) |

| CN (1) | CN101335300B (ja) |

| TW (1) | TWI446522B (ja) |

Families Citing this family (106)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8048733B2 (en) * | 2009-10-09 | 2011-11-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for fabricating a gate structure |

| CN105655351B (zh) * | 2009-11-13 | 2019-11-01 | 株式会社半导体能源研究所 | 显示器件 |

| CN102479722B (zh) * | 2010-11-30 | 2014-03-12 | 中芯国际集成电路制造(北京)有限公司 | 晶体管的制作方法 |

| CN102479694B (zh) * | 2010-11-30 | 2013-09-04 | 中芯国际集成电路制造(北京)有限公司 | 一种金属栅极及mos晶体管的形成方法 |

| CN102487085B (zh) * | 2010-12-01 | 2014-04-23 | 中国科学院微电子研究所 | 半导体器件及其制造方法 |

| US10283321B2 (en) | 2011-01-18 | 2019-05-07 | Applied Materials, Inc. | Semiconductor processing system and methods using capacitively coupled plasma |

| US9064815B2 (en) | 2011-03-14 | 2015-06-23 | Applied Materials, Inc. | Methods for etch of metal and metal-oxide films |

| US8999856B2 (en) | 2011-03-14 | 2015-04-07 | Applied Materials, Inc. | Methods for etch of sin films |

| CN102738225A (zh) * | 2011-04-06 | 2012-10-17 | 联华电子股份有限公司 | 半导体元件及其制作方法 |

| US8334198B2 (en) * | 2011-04-12 | 2012-12-18 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of fabricating a plurality of gate structures |

| CN102779751B (zh) * | 2011-05-11 | 2015-09-09 | 中国科学院微电子研究所 | 一种半导体器件的制造方法 |

| CN102956544B (zh) * | 2011-08-25 | 2015-06-17 | 中芯国际集成电路制造(上海)有限公司 | 金属互连线的制造方法 |

| US20130260564A1 (en) * | 2011-09-26 | 2013-10-03 | Applied Materials, Inc. | Insensitive dry removal process for semiconductor integration |

| US9059263B2 (en) | 2011-11-09 | 2015-06-16 | QUALCOMM Incorpated | Low-K dielectric protection spacer for patterning through substrate vias through a low-K wiring layer |

| CN103545209A (zh) * | 2012-07-13 | 2014-01-29 | 中芯国际集成电路制造(上海)有限公司 | 形成高k金属栅极器件的方法 |

| US9267739B2 (en) | 2012-07-18 | 2016-02-23 | Applied Materials, Inc. | Pedestal with multi-zone temperature control and multiple purge capabilities |

| US9373517B2 (en) | 2012-08-02 | 2016-06-21 | Applied Materials, Inc. | Semiconductor processing with DC assisted RF power for improved control |

| US9132436B2 (en) | 2012-09-21 | 2015-09-15 | Applied Materials, Inc. | Chemical control features in wafer process equipment |

| US10256079B2 (en) | 2013-02-08 | 2019-04-09 | Applied Materials, Inc. | Semiconductor processing systems having multiple plasma configurations |

| US9362130B2 (en) | 2013-03-01 | 2016-06-07 | Applied Materials, Inc. | Enhanced etching processes using remote plasma sources |

| KR102106885B1 (ko) * | 2013-03-15 | 2020-05-06 | 삼성전자 주식회사 | 실리콘 산화막 증착용 전구체 조성물 및 상기 전구체 조성물을 이용한 반도체 소자 제조 방법 |

| US9299537B2 (en) | 2014-03-20 | 2016-03-29 | Applied Materials, Inc. | Radial waveguide systems and methods for post-match control of microwaves |

| US9903020B2 (en) | 2014-03-31 | 2018-02-27 | Applied Materials, Inc. | Generation of compact alumina passivation layers on aluminum plasma equipment components |

| US9309598B2 (en) | 2014-05-28 | 2016-04-12 | Applied Materials, Inc. | Oxide and metal removal |

| US9461144B2 (en) * | 2014-06-13 | 2016-10-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for semiconductor device fabrication |

| US9613822B2 (en) | 2014-09-25 | 2017-04-04 | Applied Materials, Inc. | Oxide etch selectivity enhancement |

| US9966240B2 (en) | 2014-10-14 | 2018-05-08 | Applied Materials, Inc. | Systems and methods for internal surface conditioning assessment in plasma processing equipment |

| US9355922B2 (en) | 2014-10-14 | 2016-05-31 | Applied Materials, Inc. | Systems and methods for internal surface conditioning in plasma processing equipment |

| US11637002B2 (en) | 2014-11-26 | 2023-04-25 | Applied Materials, Inc. | Methods and systems to enhance process uniformity |

| US10573496B2 (en) | 2014-12-09 | 2020-02-25 | Applied Materials, Inc. | Direct outlet toroidal plasma source |

| US10224210B2 (en) | 2014-12-09 | 2019-03-05 | Applied Materials, Inc. | Plasma processing system with direct outlet toroidal plasma source |

| US11257693B2 (en) | 2015-01-09 | 2022-02-22 | Applied Materials, Inc. | Methods and systems to improve pedestal temperature control |

| US9728437B2 (en) | 2015-02-03 | 2017-08-08 | Applied Materials, Inc. | High temperature chuck for plasma processing systems |

| US20160225652A1 (en) | 2015-02-03 | 2016-08-04 | Applied Materials, Inc. | Low temperature chuck for plasma processing systems |

| US9881805B2 (en) | 2015-03-02 | 2018-01-30 | Applied Materials, Inc. | Silicon selective removal |

| US9691645B2 (en) | 2015-08-06 | 2017-06-27 | Applied Materials, Inc. | Bolted wafer chuck thermal management systems and methods for wafer processing systems |

| US9741593B2 (en) | 2015-08-06 | 2017-08-22 | Applied Materials, Inc. | Thermal management systems and methods for wafer processing systems |

| US9349605B1 (en) | 2015-08-07 | 2016-05-24 | Applied Materials, Inc. | Oxide etch selectivity systems and methods |

| US10504700B2 (en) | 2015-08-27 | 2019-12-10 | Applied Materials, Inc. | Plasma etching systems and methods with secondary plasma injection |

| US10504754B2 (en) | 2016-05-19 | 2019-12-10 | Applied Materials, Inc. | Systems and methods for improved semiconductor etching and component protection |

| US10522371B2 (en) | 2016-05-19 | 2019-12-31 | Applied Materials, Inc. | Systems and methods for improved semiconductor etching and component protection |

| JP6594261B2 (ja) * | 2016-05-24 | 2019-10-23 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US9865484B1 (en) | 2016-06-29 | 2018-01-09 | Applied Materials, Inc. | Selective etch using material modification and RF pulsing |

| US10062575B2 (en) | 2016-09-09 | 2018-08-28 | Applied Materials, Inc. | Poly directional etch by oxidation |

| US10629473B2 (en) | 2016-09-09 | 2020-04-21 | Applied Materials, Inc. | Footing removal for nitride spacer |

| US10546729B2 (en) | 2016-10-04 | 2020-01-28 | Applied Materials, Inc. | Dual-channel showerhead with improved profile |

| US10062585B2 (en) | 2016-10-04 | 2018-08-28 | Applied Materials, Inc. | Oxygen compatible plasma source |

| US9934942B1 (en) | 2016-10-04 | 2018-04-03 | Applied Materials, Inc. | Chamber with flow-through source |

| US10062579B2 (en) | 2016-10-07 | 2018-08-28 | Applied Materials, Inc. | Selective SiN lateral recess |

| US9947549B1 (en) | 2016-10-10 | 2018-04-17 | Applied Materials, Inc. | Cobalt-containing material removal |

| US10163696B2 (en) | 2016-11-11 | 2018-12-25 | Applied Materials, Inc. | Selective cobalt removal for bottom up gapfill |

| US9768034B1 (en) | 2016-11-11 | 2017-09-19 | Applied Materials, Inc. | Removal methods for high aspect ratio structures |

| US10026621B2 (en) | 2016-11-14 | 2018-07-17 | Applied Materials, Inc. | SiN spacer profile patterning |

| US10242908B2 (en) | 2016-11-14 | 2019-03-26 | Applied Materials, Inc. | Airgap formation with damage-free copper |

| US10566206B2 (en) | 2016-12-27 | 2020-02-18 | Applied Materials, Inc. | Systems and methods for anisotropic material breakthrough |

| US10431429B2 (en) | 2017-02-03 | 2019-10-01 | Applied Materials, Inc. | Systems and methods for radial and azimuthal control of plasma uniformity |

| US10403507B2 (en) | 2017-02-03 | 2019-09-03 | Applied Materials, Inc. | Shaped etch profile with oxidation |

| US10043684B1 (en) | 2017-02-06 | 2018-08-07 | Applied Materials, Inc. | Self-limiting atomic thermal etching systems and methods |

| US10319739B2 (en) | 2017-02-08 | 2019-06-11 | Applied Materials, Inc. | Accommodating imperfectly aligned memory holes |

| US10943834B2 (en) | 2017-03-13 | 2021-03-09 | Applied Materials, Inc. | Replacement contact process |

| US10319649B2 (en) | 2017-04-11 | 2019-06-11 | Applied Materials, Inc. | Optical emission spectroscopy (OES) for remote plasma monitoring |

| JP7176860B6 (ja) | 2017-05-17 | 2022-12-16 | アプライド マテリアルズ インコーポレイテッド | 前駆体の流れを改善する半導体処理チャンバ |

| US11276590B2 (en) | 2017-05-17 | 2022-03-15 | Applied Materials, Inc. | Multi-zone semiconductor substrate supports |

| US11276559B2 (en) | 2017-05-17 | 2022-03-15 | Applied Materials, Inc. | Semiconductor processing chamber for multiple precursor flow |

| US10049891B1 (en) | 2017-05-31 | 2018-08-14 | Applied Materials, Inc. | Selective in situ cobalt residue removal |

| US10497579B2 (en) | 2017-05-31 | 2019-12-03 | Applied Materials, Inc. | Water-free etching methods |

| US10920320B2 (en) | 2017-06-16 | 2021-02-16 | Applied Materials, Inc. | Plasma health determination in semiconductor substrate processing reactors |

| US10541246B2 (en) | 2017-06-26 | 2020-01-21 | Applied Materials, Inc. | 3D flash memory cells which discourage cross-cell electrical tunneling |

| US10727080B2 (en) | 2017-07-07 | 2020-07-28 | Applied Materials, Inc. | Tantalum-containing material removal |

| US10541184B2 (en) | 2017-07-11 | 2020-01-21 | Applied Materials, Inc. | Optical emission spectroscopic techniques for monitoring etching |

| US10354889B2 (en) | 2017-07-17 | 2019-07-16 | Applied Materials, Inc. | Non-halogen etching of silicon-containing materials |

| US10043674B1 (en) | 2017-08-04 | 2018-08-07 | Applied Materials, Inc. | Germanium etching systems and methods |

| US10170336B1 (en) | 2017-08-04 | 2019-01-01 | Applied Materials, Inc. | Methods for anisotropic control of selective silicon removal |

| US10297458B2 (en) | 2017-08-07 | 2019-05-21 | Applied Materials, Inc. | Process window widening using coated parts in plasma etch processes |

| US10128086B1 (en) | 2017-10-24 | 2018-11-13 | Applied Materials, Inc. | Silicon pretreatment for nitride removal |

| US10283324B1 (en) | 2017-10-24 | 2019-05-07 | Applied Materials, Inc. | Oxygen treatment for nitride etching |

| US10256112B1 (en) | 2017-12-08 | 2019-04-09 | Applied Materials, Inc. | Selective tungsten removal |

| US10903054B2 (en) | 2017-12-19 | 2021-01-26 | Applied Materials, Inc. | Multi-zone gas distribution systems and methods |

| US11328909B2 (en) | 2017-12-22 | 2022-05-10 | Applied Materials, Inc. | Chamber conditioning and removal processes |

| US10854426B2 (en) | 2018-01-08 | 2020-12-01 | Applied Materials, Inc. | Metal recess for semiconductor structures |

| US10679870B2 (en) | 2018-02-15 | 2020-06-09 | Applied Materials, Inc. | Semiconductor processing chamber multistage mixing apparatus |

| US10964512B2 (en) | 2018-02-15 | 2021-03-30 | Applied Materials, Inc. | Semiconductor processing chamber multistage mixing apparatus and methods |

| TWI716818B (zh) | 2018-02-28 | 2021-01-21 | 美商應用材料股份有限公司 | 形成氣隙的系統及方法 |

| US10593560B2 (en) | 2018-03-01 | 2020-03-17 | Applied Materials, Inc. | Magnetic induction plasma source for semiconductor processes and equipment |

| US10319600B1 (en) | 2018-03-12 | 2019-06-11 | Applied Materials, Inc. | Thermal silicon etch |

| US10497573B2 (en) | 2018-03-13 | 2019-12-03 | Applied Materials, Inc. | Selective atomic layer etching of semiconductor materials |

| US10573527B2 (en) | 2018-04-06 | 2020-02-25 | Applied Materials, Inc. | Gas-phase selective etching systems and methods |

| US10490406B2 (en) | 2018-04-10 | 2019-11-26 | Appled Materials, Inc. | Systems and methods for material breakthrough |

| US10699879B2 (en) | 2018-04-17 | 2020-06-30 | Applied Materials, Inc. | Two piece electrode assembly with gap for plasma control |

| US10886137B2 (en) | 2018-04-30 | 2021-01-05 | Applied Materials, Inc. | Selective nitride removal |

| US10755941B2 (en) | 2018-07-06 | 2020-08-25 | Applied Materials, Inc. | Self-limiting selective etching systems and methods |

| US10872778B2 (en) | 2018-07-06 | 2020-12-22 | Applied Materials, Inc. | Systems and methods utilizing solid-phase etchants |

| US10672642B2 (en) | 2018-07-24 | 2020-06-02 | Applied Materials, Inc. | Systems and methods for pedestal configuration |

| US10892198B2 (en) | 2018-09-14 | 2021-01-12 | Applied Materials, Inc. | Systems and methods for improved performance in semiconductor processing |

| US11049755B2 (en) | 2018-09-14 | 2021-06-29 | Applied Materials, Inc. | Semiconductor substrate supports with embedded RF shield |

| US11062887B2 (en) | 2018-09-17 | 2021-07-13 | Applied Materials, Inc. | High temperature RF heater pedestals |

| US11417534B2 (en) | 2018-09-21 | 2022-08-16 | Applied Materials, Inc. | Selective material removal |

| US11682560B2 (en) | 2018-10-11 | 2023-06-20 | Applied Materials, Inc. | Systems and methods for hafnium-containing film removal |

| US11121002B2 (en) | 2018-10-24 | 2021-09-14 | Applied Materials, Inc. | Systems and methods for etching metals and metal derivatives |

| US11437242B2 (en) | 2018-11-27 | 2022-09-06 | Applied Materials, Inc. | Selective removal of silicon-containing materials |

| US11721527B2 (en) | 2019-01-07 | 2023-08-08 | Applied Materials, Inc. | Processing chamber mixing systems |

| US10920319B2 (en) | 2019-01-11 | 2021-02-16 | Applied Materials, Inc. | Ceramic showerheads with conductive electrodes |

| CN110491876B (zh) * | 2019-08-23 | 2024-04-05 | 福建省晋华集成电路有限公司 | 半导体存储元件的制造方法及该元件 |

| CN114093766B (zh) * | 2020-08-24 | 2024-09-13 | 联华电子股份有限公司 | 半导体装置及其制造方法 |

| KR20220151819A (ko) * | 2021-05-07 | 2022-11-15 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조 방법 |

| CN116779611B (zh) * | 2023-08-17 | 2023-11-28 | 合肥晶合集成电路股份有限公司 | 一种半导体结构及其制备方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3530026B2 (ja) * | 1997-06-30 | 2004-05-24 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP2000091562A (ja) * | 1998-09-16 | 2000-03-31 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| TW569319B (en) * | 2002-06-06 | 2004-01-01 | Winbond Electronics Corp | Gate structure and method of manufacture |

| JP2004014875A (ja) * | 2002-06-07 | 2004-01-15 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| US7029536B2 (en) * | 2003-03-17 | 2006-04-18 | Tokyo Electron Limited | Processing system and method for treating a substrate |

| US7176041B2 (en) * | 2003-07-01 | 2007-02-13 | Samsung Electronics Co., Ltd. | PAA-based etchant, methods of using same, and resultant structures |

| JP4546201B2 (ja) * | 2004-03-17 | 2010-09-15 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP4118255B2 (ja) * | 2004-06-18 | 2008-07-16 | 株式会社ルネサステクノロジ | Mosトランジスタの製造方法 |

| JP2006295071A (ja) * | 2005-04-14 | 2006-10-26 | Toshiba Corp | 半導体装置の製造方法 |

-

2008

- 2008-03-10 JP JP2008060164A patent/JP5282419B2/ja not_active Expired - Fee Related

- 2008-04-09 TW TW097112894A patent/TWI446522B/zh active

- 2008-04-17 KR KR1020080035540A patent/KR101457006B1/ko not_active Expired - Fee Related

- 2008-04-18 CN CN2008102103134A patent/CN101335300B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008288560A (ja) | 2008-11-27 |

| TWI446522B (zh) | 2014-07-21 |

| KR101457006B1 (ko) | 2014-10-31 |

| CN101335300B (zh) | 2010-07-21 |

| TW200849557A (en) | 2008-12-16 |

| CN101335300A (zh) | 2008-12-31 |

| KR20080093911A (ko) | 2008-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5282419B2 (ja) | 半導体装置及びその製造方法 | |

| US8350335B2 (en) | Semiconductor device including off-set spacers formed as a portion of the sidewall | |

| US11508583B2 (en) | Selective high-k formation in gate-last process | |

| JP5154222B2 (ja) | 置換金属ゲート形成のための半導体構造の平坦化 | |

| US7615840B2 (en) | Device performance improvement using flowfill as material for isolation structures | |

| JP5070969B2 (ja) | 半導体装置の製造方法 | |

| KR101521948B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| TW201113936A (en) | Method for fabricating a gate structure | |

| US8629508B2 (en) | Semiconductor device and method of manufacture | |

| JP2008515190A (ja) | 金属ゲート電極半導体デバイス | |

| CN102024743A (zh) | 半导体结构与在鳍状装置之鳍状结构之间形成隔离的方法 | |

| JP2006041337A (ja) | 窒化珪素膜の製造方法及び半導体装置の製造方法 | |

| JP2009033032A (ja) | 半導体装置及び半導体装置の製造方法 | |

| CN103545186B (zh) | 一种制造金属栅半导体器件的方法 | |

| TWI389203B (zh) | 製造半導體元件之方法 | |

| JP2005064032A (ja) | 半導体装置及びその製造方法 | |

| JP5374947B2 (ja) | 半導体装置およびその製造方法 | |

| JP2007157744A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP5130652B2 (ja) | 金属膜のエッチング方法及び半導体装置の製造方法 | |

| CN109786254B (zh) | 后栅极工艺中的选择性高k形成 | |

| CN1905138B (zh) | 半导体器件及其制造方法 | |

| KR100715272B1 (ko) | 게이트 구조물의 형성 방법 및 이를 이용한 반도체 장치의제조 방법 | |

| CN121604486A (zh) | 半导体元件制造方法以及半导体元件制造装置 | |

| JP2010219289A (ja) | 半導体装置及びその製造方法 | |

| CN107785312A (zh) | 半导体器件及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100225 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100225 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120622 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120703 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120827 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121120 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130430 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130513 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5282419 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |