JP5111196B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5111196B2 JP5111196B2 JP2008087530A JP2008087530A JP5111196B2 JP 5111196 B2 JP5111196 B2 JP 5111196B2 JP 2008087530 A JP2008087530 A JP 2008087530A JP 2008087530 A JP2008087530 A JP 2008087530A JP 5111196 B2 JP5111196 B2 JP 5111196B2

- Authority

- JP

- Japan

- Prior art keywords

- tft

- channel

- film

- oled

- power supply

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 67

- 230000015572 biosynthetic process Effects 0.000 claims description 26

- 239000010408 film Substances 0.000 description 167

- 239000010410 layer Substances 0.000 description 118

- 238000000034 method Methods 0.000 description 66

- 238000005530 etching Methods 0.000 description 32

- 239000012535 impurity Substances 0.000 description 30

- 239000003990 capacitor Substances 0.000 description 27

- 239000000463 material Substances 0.000 description 25

- 239000000758 substrate Substances 0.000 description 25

- 150000002894 organic compounds Chemical class 0.000 description 20

- 238000003860 storage Methods 0.000 description 18

- 238000010438 heat treatment Methods 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 239000007789 gas Substances 0.000 description 15

- 229910052710 silicon Inorganic materials 0.000 description 15

- 239000010703 silicon Substances 0.000 description 15

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 14

- 230000008569 process Effects 0.000 description 14

- 239000013078 crystal Substances 0.000 description 13

- 239000011229 interlayer Substances 0.000 description 13

- 238000000059 patterning Methods 0.000 description 13

- 230000001681 protective effect Effects 0.000 description 13

- 239000011347 resin Substances 0.000 description 13

- 229920005989 resin Polymers 0.000 description 13

- 229910052760 oxygen Inorganic materials 0.000 description 12

- 238000002425 crystallisation Methods 0.000 description 11

- 230000008025 crystallization Effects 0.000 description 11

- 230000006870 function Effects 0.000 description 11

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 10

- 239000011159 matrix material Substances 0.000 description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 9

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 230000004888 barrier function Effects 0.000 description 8

- 229910052739 hydrogen Inorganic materials 0.000 description 8

- 238000002347 injection Methods 0.000 description 8

- 239000007924 injection Substances 0.000 description 8

- 229920005591 polysilicon Polymers 0.000 description 8

- 239000002585 base Substances 0.000 description 7

- 238000005247 gettering Methods 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 229910052759 nickel Inorganic materials 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- 230000007423 decrease Effects 0.000 description 6

- 230000006866 deterioration Effects 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 229910052721 tungsten Inorganic materials 0.000 description 6

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 5

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 5

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 239000001257 hydrogen Substances 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 239000010409 thin film Substances 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 5

- 230000001133 acceleration Effects 0.000 description 4

- 239000012298 atmosphere Substances 0.000 description 4

- 239000000969 carrier Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000005284 excitation Effects 0.000 description 4

- 229910010272 inorganic material Inorganic materials 0.000 description 4

- 239000011147 inorganic material Substances 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 230000004913 activation Effects 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 230000001678 irradiating effect Effects 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- 229910000676 Si alloy Inorganic materials 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- 238000005984 hydrogenation reaction Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 238000004020 luminiscence type Methods 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 230000001737 promoting effect Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910018575 Al—Ti Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- 229910001069 Ti alloy Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 238000009125 cardiac resynchronization therapy Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000006356 dehydrogenation reaction Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000002274 desiccant Substances 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- AIYYMMQIMJOTBM-UHFFFAOYSA-L nickel(ii) acetate Chemical compound [Ni+2].CC([O-])=O.CC([O-])=O AIYYMMQIMJOTBM-UHFFFAOYSA-L 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- -1 tungsten nitride Chemical class 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- Y02B20/36—

Landscapes

- Electroluminescent Light Sources (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

- Recrystallisation Techniques (AREA)

- Electrodes Of Semiconductors (AREA)

Description

そのため、ポリシリコン膜を用いたTFTからなる駆動回路を画素と同一の基板上に設け、各画素の制御を行うための開発が盛んに行われている。同一基板上に画素と駆動回路とを組み込んだアクティブマトリクス型表示装置は、製造コストの低減、表示装置の小型化、歩留まりの上昇、スループットの低減など、様々な利点が得られると予想される。

また、データ線側駆動回路のTFTも、高い駆動能力(オン電流、Ion)及びホットキャリア効果による劣化を防ぎ信頼性を向上させることが求められている。

本発明は、画素部における開口率を向上させる画素構成を提供することも課題としている。

に対するバラツキ(本明細書中ではこのバラツキを規格化したバラツキとも呼ぶ)とがある。

しかし、図11に示すように、チャネル長を長くするだけでは電流値が減少するだけで、ある個数のTFTの集合における電流値の中央値に対するバラツキ(規格化したバラツキ)は変化しない。

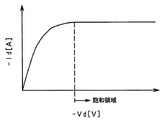

また、OLEDが劣化すると、OLEDの負荷曲線は左側にシフトする。gdが大きい場合、劣化によりOLEDの負荷曲線が左側にシフトして点線で示した曲線となると、OLEDの負荷曲線との交点が変化して劣化前後で電流値が異なってしまう。一方、gdが小さい場合、劣化によりOLEDの負荷曲線が左側にシフトしても、電流値はほとんど変化しないため、輝度のバラツキが低減され、均一な輝度が得られる。

、L×W=500μm×4μm(Bタイフ゜)の場合において631.3(fF)である。また、酸化膜容量COXを求める際の他の値としては、ゲート絶縁膜(酸化膜)の膜厚Tox=115nm、ε0=8.8542×10-12(F/m2)、εOX=4.1とした。

代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

なお、図5では、簡略化のため、EL層は図示しておらず、OLEDの一方の電極(画素電極107)しか図示していない。

また、OLEDに電流を供給するTFTのソース領域(またはドレイン領域)と電源供給線106とが接続され、OLEDに電流を供給するTFTのドレイン領域(またはソース領域)と接続電極108とが接続され、該接続電極108と接して画素電極107が形成されている。また、ゲート電極100の上方には、電源供給線106と、隣合う画素のソース配線とが一部重なるように配置されている。なお、半導体層102のうち、ゲート電極100とゲート絶縁膜を介して重なるチャネル形成領域の上方には、電源供給線106と、隣合う画素のソース配線とが一部重なるように配置されている。このゲート電極100と電源供給線106との間で形成される容量は、全てEL素子の保持容量として利用することができる。従って、このゲート電極100と電源供給線106との間で形成される容量で必要とされる保持容量をある程度確保することができる。

さらに1つの画素に複数(2個、または3個以上)のTFTや様々な回路(カレントミラー回路など)を組み込んだ構造としてもよい。

この加熱処理は、電気炉の熱処理または強光の照射を用いればよい。電気炉の熱処理で行う場合は、500℃〜650℃で4〜24時間で行えばよい。ここでは脱水素化のための熱処理(500℃、1時間)の後、結晶化のための熱処理(550℃、4時間)を行って結晶構造を有するシリコン膜を得た。なお、ここでは炉を用いた熱処理を用いて結晶化を行ったが、短時間での結晶化が可能なランプアニール装置で結晶化を行ってもよい。なお、ここではシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いたが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

電気炉に代えてランプアニール装置を用いてもよい。

ここでは、第3のエッチング条件としてエッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30/30(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを60秒行った。基板側(試料ステージ)にも20WのRF(13.56MHz)

電力を投入し、実質的に負の自己バイアス電圧を印加する。この後、レジストからなるマスクを除去せずに第4のエッチング条件に変え、エッチング用ガスにCF4とCl2とO2とを用い、それぞれのガス流量比を20/20/20(sccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約20秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、ここでは、第3のエッチング条件及び第4のエッチング条件を第2のエッチング処理と呼ぶこととする。この段階で第1の導電層304aを下層とし、第2の導電層304bを上層とするゲート電極304および各電極305〜307が形成される。この段階で、画素の上面構造を、例えば、図6に示したものとすればよい。

第3のドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。

n型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用いる。ここでは、イオンドープ法を用い、フォスフィン(PH3)を水素で5%に希釈したガスを流量40sccmとし、ドーズ量を2×1015atoms/cm2とし、加速電圧を80keVとして行う。この場合、レジストからなるマスクと第1の導電層及び第2の導電層がn型を付与する不純物元素に対するマスクとなり、第3の不純物領域313、314、326〜328が形成される。第3の不純物領域には1×1020〜1×1021/cm3の濃度範囲でn型を付与する不純物元素を添加される。ここでは、第3の不純物領域と同じ濃度範囲の領域をn+領域とも呼ぶ。

が添加された領域(n--領域)であるが、p型を付与する不純物元素の濃度がその1.5〜3倍添加されていて導電型はp型となっている。ここでは、第4の不純物領域と同じ濃度範囲の領域をp+領域とも呼ぶ。

図15にその一例を示す。なお、上面図は同一であるので省略する。

また、カバー材620には凹部を設け、乾燥剤621を設置してもよい。

Claims (10)

- 画素電極に電気的に接続されるTFTと、

ソース配線と、前記ソース配線に直交するゲート配線と、前記ソース配線と平行で、前記TFTと電気的に接続される電源供給線とを有する半導体装置であって、

前記TFTは、チャネル形成領域を有する半導体層を有し、

前記ソース配線と隣合うソース配線との間には、前記画素電極と前記電源供給線とを有し、

前記チャネル形成領域は、前記電源供給線と、前記隣合うソース配線とに重なり、かつ前記電源供給線と、前記隣合うソース配線とは重ならないように配置され、

前記TFTのチャネル長Lに対するチャネル幅Wの比が0.1〜0.01であることを特徴とする半導体装置。 - 画素電極に電気的に接続されるTFTと、

ソース配線と、前記ソース配線に直交するゲート配線と、前記ソース配線と平行で、前記TFTと電気的に接続される電源供給線とを有する半導体装置であって、

前記TFTは、チャネル形成領域を有する半導体層を有し、

前記ソース配線と隣合うソース配線との間には、前記画素電極と前記電源供給線とを有し、

前記チャネル形成領域は、前記電源供給線と、前記隣合うソース配線とに重なり、かつ前記電源供給線と、前記隣合うソース配線とは重ならないように配置され、

前記TFTのチャネル長Lが100μm以上であることを特徴とする半導体装置。 - 画素電極に電気的に接続されるTFTと、

ソース配線と、前記ソース配線に直交するゲート配線と、前記ソース配線と平行で、前記TFTと電気的に接続される電源供給線とを有する半導体装置であって、

前記TFTは、チャネル形成領域を有する半導体層を有し、

前記ソース配線と隣合うソース配線との間には、前記画素電極と前記電源供給線とを有し、

前記チャネル形成領域は、前記電源供給線と、前記隣合うソース配線とに重なり、かつ前記電源供給線と、前記隣合うソース配線とは重ならないように配置され、

前記TFTは飽和領域で動作することができることを特徴とする半導体装置。 - 請求項1乃至3のいずれか一において、前記TFTは、ソースドレイン間電圧Vdとしきい値電圧Vthとの和がゲート電圧Vgより大きい範囲でチャネルコンダクタンスgdが0〜1×10−8Sであることを特徴とする半導体装置。

- 請求項1乃至3のいずれか一において、前記TFTは、ソースドレイン間電圧Vdとしきい値電圧Vthとの和がゲート電圧Vgより大きい範囲でチャネルコンダクタンスgdが0〜5×10−9Sであることを特徴とする半導体装置。

- 請求項1乃至3のいずれか一において、前記TFTは、ソースドレイン間電圧Vdとしきい値電圧Vthとの和がゲート電圧Vgより大きい範囲でチャネルコンダクタンスgdが0〜2×10−9Sであることを特徴とする半導体装置。

- 請求項1乃至6のいずれか一において、前記TFTは、pチャネル型TFTまたはnチャネル型TFTであることを特徴とする半導体装置。

- 請求項1乃至7のいずれか一において、前記TFTのチャネル形成領域は、前記ゲート配線方向に蛇行させた形状であることを特徴とする半導体装置。

- 請求項1乃至7のいずれか一において、前記TFTのチャネル形成領域は、前記ソース配線方向に蛇行させた形状であることを特徴とする半導体装置。

- 請求項1乃至7のいずれか一において、前記TFTのチャネル形成領域は、矩形形状であることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008087530A JP5111196B2 (ja) | 2001-11-09 | 2008-03-28 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001344671 | 2001-11-09 | ||

| JP2001344671 | 2001-11-09 | ||

| JP2008087530A JP5111196B2 (ja) | 2001-11-09 | 2008-03-28 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002010766A Division JP4149168B2 (ja) | 2001-11-09 | 2002-01-18 | 発光装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012105184A Division JP2012195596A (ja) | 2001-11-09 | 2012-05-02 | 発光装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008235912A JP2008235912A (ja) | 2008-10-02 |

| JP5111196B2 true JP5111196B2 (ja) | 2012-12-26 |

Family

ID=38697587

Family Applications (19)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008087530A Expired - Fee Related JP5111196B2 (ja) | 2001-11-09 | 2008-03-28 | 半導体装置 |

| JP2012105184A Withdrawn JP2012195596A (ja) | 2001-11-09 | 2012-05-02 | 発光装置 |

| JP2012233881A Expired - Lifetime JP5459918B2 (ja) | 2001-11-09 | 2012-10-23 | 半導体装置 |

| JP2013239680A Expired - Lifetime JP5568678B2 (ja) | 2001-11-09 | 2013-11-20 | 発光装置 |

| JP2013239679A Expired - Fee Related JP5679535B2 (ja) | 2001-11-09 | 2013-11-20 | 発光装置 |

| JP2014001793A Withdrawn JP2014099635A (ja) | 2001-11-09 | 2014-01-08 | 発光装置 |

| JP2014132514A Expired - Lifetime JP5917612B2 (ja) | 2001-11-09 | 2014-06-27 | 発光装置 |

| JP2014231325A Expired - Lifetime JP5784209B2 (ja) | 2001-11-09 | 2014-11-14 | 発光装置及び電子機器 |

| JP2015094506A Expired - Lifetime JP6053067B2 (ja) | 2001-11-09 | 2015-05-05 | 発光装置、及び電子機器 |

| JP2015106208A Expired - Lifetime JP6096832B2 (ja) | 2001-11-09 | 2015-05-26 | 発光装置 |

| JP2016054981A Withdrawn JP2016136641A (ja) | 2001-11-09 | 2016-03-18 | 発光装置 |

| JP2017168422A Expired - Lifetime JP6514286B2 (ja) | 2001-11-09 | 2017-09-01 | 発光装置 |

| JP2018017185A Expired - Lifetime JP6306808B1 (ja) | 2001-11-09 | 2018-02-02 | 発光装置 |

| JP2018018864A Expired - Lifetime JP6383507B2 (ja) | 2001-11-09 | 2018-02-06 | 発光装置 |

| JP2018134240A Expired - Lifetime JP6608008B2 (ja) | 2001-11-09 | 2018-07-17 | 発光装置 |

| JP2018229341A Withdrawn JP2019071431A (ja) | 2001-11-09 | 2018-12-06 | 発光装置 |

| JP2018241382A Expired - Lifetime JP6622893B2 (ja) | 2001-11-09 | 2018-12-25 | 発光装置 |

| JP2020135660A Expired - Lifetime JP7032625B2 (ja) | 2001-11-09 | 2020-08-11 | 発光装置 |

| JP2020151903A Withdrawn JP2021013023A (ja) | 2001-11-09 | 2020-09-10 | 発光装置 |

Family Applications After (18)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012105184A Withdrawn JP2012195596A (ja) | 2001-11-09 | 2012-05-02 | 発光装置 |

| JP2012233881A Expired - Lifetime JP5459918B2 (ja) | 2001-11-09 | 2012-10-23 | 半導体装置 |

| JP2013239680A Expired - Lifetime JP5568678B2 (ja) | 2001-11-09 | 2013-11-20 | 発光装置 |

| JP2013239679A Expired - Fee Related JP5679535B2 (ja) | 2001-11-09 | 2013-11-20 | 発光装置 |

| JP2014001793A Withdrawn JP2014099635A (ja) | 2001-11-09 | 2014-01-08 | 発光装置 |

| JP2014132514A Expired - Lifetime JP5917612B2 (ja) | 2001-11-09 | 2014-06-27 | 発光装置 |

| JP2014231325A Expired - Lifetime JP5784209B2 (ja) | 2001-11-09 | 2014-11-14 | 発光装置及び電子機器 |

| JP2015094506A Expired - Lifetime JP6053067B2 (ja) | 2001-11-09 | 2015-05-05 | 発光装置、及び電子機器 |

| JP2015106208A Expired - Lifetime JP6096832B2 (ja) | 2001-11-09 | 2015-05-26 | 発光装置 |

| JP2016054981A Withdrawn JP2016136641A (ja) | 2001-11-09 | 2016-03-18 | 発光装置 |

| JP2017168422A Expired - Lifetime JP6514286B2 (ja) | 2001-11-09 | 2017-09-01 | 発光装置 |

| JP2018017185A Expired - Lifetime JP6306808B1 (ja) | 2001-11-09 | 2018-02-02 | 発光装置 |

| JP2018018864A Expired - Lifetime JP6383507B2 (ja) | 2001-11-09 | 2018-02-06 | 発光装置 |

| JP2018134240A Expired - Lifetime JP6608008B2 (ja) | 2001-11-09 | 2018-07-17 | 発光装置 |

| JP2018229341A Withdrawn JP2019071431A (ja) | 2001-11-09 | 2018-12-06 | 発光装置 |

| JP2018241382A Expired - Lifetime JP6622893B2 (ja) | 2001-11-09 | 2018-12-25 | 発光装置 |

| JP2020135660A Expired - Lifetime JP7032625B2 (ja) | 2001-11-09 | 2020-08-11 | 発光装置 |

| JP2020151903A Withdrawn JP2021013023A (ja) | 2001-11-09 | 2020-09-10 | 発光装置 |

Country Status (2)

| Country | Link |

|---|---|

| JP (19) | JP5111196B2 (ja) |

| CN (1) | CN101009322B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011064819A1 (ja) | 2009-11-27 | 2011-06-03 | パナソニック株式会社 | 発光表示装置 |

| JP5508301B2 (ja) * | 2011-01-18 | 2014-05-28 | パナソニック株式会社 | 発光表示装置 |

| TWI713943B (zh) | 2013-09-12 | 2020-12-21 | 日商新力股份有限公司 | 顯示裝置及電子機器 |

| KR102238641B1 (ko) * | 2014-12-26 | 2021-04-09 | 엘지디스플레이 주식회사 | 박막트랜지스터 어레이 기판 |

| CN113490998A (zh) * | 2018-08-09 | 2021-10-08 | 阵列光子学公司 | 用于混合式半导体生长的氢扩散屏障 |

| CN113381286B (zh) * | 2021-06-02 | 2023-03-03 | 山东大学 | 离子束增强腐蚀制备晶体薄膜的方法 |

Family Cites Families (62)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS548986A (en) * | 1977-06-22 | 1979-01-23 | Nec Corp | Semiconductor device |

| JPS5626468A (en) * | 1979-08-09 | 1981-03-14 | Sharp Corp | Structure of membrane transistor |

| JPS58171860A (ja) * | 1982-04-01 | 1983-10-08 | Seiko Epson Corp | 薄膜トランジスタ |

| JPH0680828B2 (ja) * | 1985-10-18 | 1994-10-12 | 株式会社日立製作所 | 薄膜トランジスタ |

| JPS63151083A (ja) * | 1986-12-16 | 1988-06-23 | Hitachi Ltd | 薄膜半導体装置 |

| JPH0258030A (ja) * | 1988-08-24 | 1990-02-27 | Hitachi Ltd | 液晶表示装置 |

| JP2645663B2 (ja) * | 1989-01-24 | 1997-08-25 | 日本電信電話株式会社 | 薄膜半導体装置とその製造方法 |

| JP2622183B2 (ja) * | 1990-04-05 | 1997-06-18 | シャープ株式会社 | アクティブマトリクス表示装置 |

| JP3357699B2 (ja) * | 1992-02-21 | 2002-12-16 | 株式会社東芝 | 液晶表示装置 |

| JPH0653441A (ja) * | 1992-07-28 | 1994-02-25 | Sony Corp | 薄膜トランジスタを備えたセル構造、薄膜トランジスタを備えたsramメモリーセル構造、及び薄膜トランジスタを備えたセル構造の形成方法 |

| US5556706A (en) * | 1993-10-06 | 1996-09-17 | Matsushita Electric Industrial Co., Ltd. | Conductive layered product and method of manufacturing the same |

| JP3504993B2 (ja) * | 1995-01-20 | 2004-03-08 | 株式会社半導体エネルギー研究所 | アクティブマトリクス回路 |

| JP3246189B2 (ja) * | 1994-06-28 | 2002-01-15 | 株式会社日立製作所 | 半導体表示装置 |

| US5608557A (en) * | 1995-01-03 | 1997-03-04 | Xerox Corporation | Circuitry with gate line crossing semiconductor line at two or more channels |

| GB9520888D0 (en) * | 1995-10-12 | 1995-12-13 | Philips Electronics Nv | Electronic devices comprising thin-film circuitry |

| JP3522442B2 (ja) * | 1996-03-11 | 2004-04-26 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置 |

| JP3522433B2 (ja) * | 1995-12-04 | 2004-04-26 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置 |

| JP3522440B2 (ja) * | 1996-03-08 | 2004-04-26 | 株式会社半導体エネルギー研究所 | 薄膜半導体装置 |

| JP3188167B2 (ja) * | 1995-12-15 | 2001-07-16 | 三洋電機株式会社 | 薄膜トランジスタ |

| JP3520401B2 (ja) * | 1996-09-17 | 2004-04-19 | セイコーエプソン株式会社 | 液晶パネル用基板およびそれを用いた液晶パネル並びに投射型表示装置 |

| CN1170321C (zh) * | 1996-11-12 | 2004-10-06 | 国际商业机器公司 | 导电聚合物图形及其作为电极或电接触的应用 |

| JPH11133463A (ja) * | 1997-10-31 | 1999-05-21 | Semiconductor Energy Lab Co Ltd | アクティブマトリクス型液晶表示装置及び電子機器 |

| DE69841721D1 (de) * | 1997-02-17 | 2010-07-29 | Seiko Epson Corp | Anzeigevorrichtung |

| JPH10254410A (ja) * | 1997-03-12 | 1998-09-25 | Pioneer Electron Corp | 有機エレクトロルミネッセンス表示装置及びその駆動方法 |

| US5981970A (en) * | 1997-03-25 | 1999-11-09 | International Business Machines Corporation | Thin-film field-effect transistor with organic semiconductor requiring low operating voltages |

| JP3520396B2 (ja) * | 1997-07-02 | 2004-04-19 | セイコーエプソン株式会社 | アクティブマトリクス基板と表示装置 |

| DE69829458T2 (de) * | 1997-08-21 | 2005-09-29 | Seiko Epson Corp. | Anzeigevorrichtung mit aktiver matrix |

| JPH11194363A (ja) * | 1997-12-26 | 1999-07-21 | Seiko Epson Corp | パターン形成方法、アクティブマトリックス基板及びその製造方法、電子機器 |

| GB9808061D0 (en) * | 1998-04-16 | 1998-06-17 | Cambridge Display Tech Ltd | Polymer devices |

| JP3276930B2 (ja) * | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP2968269B2 (ja) * | 1998-11-26 | 1999-10-25 | 株式会社日立製作所 | 液晶表示装置の製造方法 |

| JP2000214800A (ja) * | 1999-01-20 | 2000-08-04 | Sanyo Electric Co Ltd | エレクトロルミネッセンス表示装置 |

| JP2000223279A (ja) * | 1999-01-29 | 2000-08-11 | Sanyo Electric Co Ltd | エレクトロルミネッセンス表示装置 |

| JP2000243963A (ja) * | 1999-02-17 | 2000-09-08 | Sanyo Electric Co Ltd | 薄膜トランジスタ及び表示装置 |

| JP4229513B2 (ja) * | 1999-03-10 | 2009-02-25 | 三洋電機株式会社 | アクティブ型el表示装置 |

| JP2000347624A (ja) * | 1999-03-31 | 2000-12-15 | Seiko Epson Corp | エレクトロルミネセンス表示装置 |

| JP4246845B2 (ja) * | 1999-04-22 | 2009-04-02 | Tdk株式会社 | 有機el素子の駆動装置および有機el表示装置 |

| JP4337171B2 (ja) * | 1999-06-14 | 2009-09-30 | ソニー株式会社 | 表示装置 |

| JP4877675B2 (ja) * | 1999-06-28 | 2012-02-15 | 株式会社半導体エネルギー研究所 | 電気光学装置の作製方法 |

| EP1208603A1 (en) * | 1999-08-31 | 2002-05-29 | E Ink Corporation | Transistor for an electronically driven display |

| JP2001109405A (ja) * | 1999-10-01 | 2001-04-20 | Sanyo Electric Co Ltd | El表示装置 |

| JP2001111053A (ja) | 1999-10-04 | 2001-04-20 | Sanyo Electric Co Ltd | 薄膜トランジスタ及び表示装置 |

| JP3548063B2 (ja) * | 1999-10-20 | 2004-07-28 | 三洋電機株式会社 | アクティブマトリクス型表示装置 |

| JP2001195016A (ja) * | 1999-10-29 | 2001-07-19 | Semiconductor Energy Lab Co Ltd | 電子装置 |

| US6384427B1 (en) * | 1999-10-29 | 2002-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device |

| JP2001147659A (ja) * | 1999-11-18 | 2001-05-29 | Sony Corp | 表示装置 |

| JP4727029B2 (ja) * | 1999-11-29 | 2011-07-20 | 株式会社半導体エネルギー研究所 | El表示装置、電気器具及びel表示装置用の半導体素子基板 |

| JP4748847B2 (ja) * | 1999-12-15 | 2011-08-17 | 株式会社半導体エネルギー研究所 | El表示装置および電気器具 |

| JP2001244213A (ja) * | 1999-12-24 | 2001-09-07 | Semiconductor Energy Lab Co Ltd | レーザ照射装置並びに半導体装置の作製方法 |

| US6307322B1 (en) * | 1999-12-28 | 2001-10-23 | Sarnoff Corporation | Thin-film transistor circuitry with reduced sensitivity to variance in transistor threshold voltage |

| JP4485078B2 (ja) * | 2000-01-26 | 2010-06-16 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP5008223B2 (ja) * | 2000-01-31 | 2012-08-22 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型表示装置 |

| JP3967081B2 (ja) * | 2000-02-03 | 2007-08-29 | 株式会社半導体エネルギー研究所 | 発光装置及びその作製方法 |

| JP2001318627A (ja) * | 2000-02-29 | 2001-11-16 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| JP2001272930A (ja) * | 2000-03-28 | 2001-10-05 | Sanyo Electric Co Ltd | エレクトロルミネッセンス表示装置 |

| JP2001284592A (ja) * | 2000-03-29 | 2001-10-12 | Sony Corp | 薄膜半導体装置及びその駆動方法 |

| JP4150998B2 (ja) * | 2000-03-30 | 2008-09-17 | セイコーエプソン株式会社 | 表示装置 |

| JP2001296818A (ja) * | 2000-04-12 | 2001-10-26 | Sharp Corp | 有機エレクトロルミネッセンス表示装置 |

| JP5030345B2 (ja) * | 2000-09-29 | 2012-09-19 | 三洋電機株式会社 | 半導体装置 |

| JP4925528B2 (ja) * | 2000-09-29 | 2012-04-25 | 三洋電機株式会社 | 表示装置 |

| JP3612494B2 (ja) * | 2001-03-28 | 2005-01-19 | 株式会社日立製作所 | 表示装置 |

| JP4149168B2 (ja) * | 2001-11-09 | 2008-09-10 | 株式会社半導体エネルギー研究所 | 発光装置 |

-

2002

- 2002-11-09 CN CN200710085012.9A patent/CN101009322B/zh not_active Expired - Lifetime

-

2008

- 2008-03-28 JP JP2008087530A patent/JP5111196B2/ja not_active Expired - Fee Related

-

2012

- 2012-05-02 JP JP2012105184A patent/JP2012195596A/ja not_active Withdrawn

- 2012-10-23 JP JP2012233881A patent/JP5459918B2/ja not_active Expired - Lifetime

-

2013

- 2013-11-20 JP JP2013239680A patent/JP5568678B2/ja not_active Expired - Lifetime

- 2013-11-20 JP JP2013239679A patent/JP5679535B2/ja not_active Expired - Fee Related

-

2014

- 2014-01-08 JP JP2014001793A patent/JP2014099635A/ja not_active Withdrawn

- 2014-06-27 JP JP2014132514A patent/JP5917612B2/ja not_active Expired - Lifetime

- 2014-11-14 JP JP2014231325A patent/JP5784209B2/ja not_active Expired - Lifetime

-

2015

- 2015-05-05 JP JP2015094506A patent/JP6053067B2/ja not_active Expired - Lifetime

- 2015-05-26 JP JP2015106208A patent/JP6096832B2/ja not_active Expired - Lifetime

-

2016

- 2016-03-18 JP JP2016054981A patent/JP2016136641A/ja not_active Withdrawn

-

2017

- 2017-09-01 JP JP2017168422A patent/JP6514286B2/ja not_active Expired - Lifetime

-

2018

- 2018-02-02 JP JP2018017185A patent/JP6306808B1/ja not_active Expired - Lifetime

- 2018-02-06 JP JP2018018864A patent/JP6383507B2/ja not_active Expired - Lifetime

- 2018-07-17 JP JP2018134240A patent/JP6608008B2/ja not_active Expired - Lifetime

- 2018-12-06 JP JP2018229341A patent/JP2019071431A/ja not_active Withdrawn

- 2018-12-25 JP JP2018241382A patent/JP6622893B2/ja not_active Expired - Lifetime

-

2020

- 2020-08-11 JP JP2020135660A patent/JP7032625B2/ja not_active Expired - Lifetime

- 2020-09-10 JP JP2020151903A patent/JP2021013023A/ja not_active Withdrawn

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10680049B2 (en) | Light emitting device | |

| JP6622893B2 (ja) | 発光装置 | |

| JP4149443B2 (ja) | 発光装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110915 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120502 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121002 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121009 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5111196 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |