JP4651359B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4651359B2 JP4651359B2 JP2004315998A JP2004315998A JP4651359B2 JP 4651359 B2 JP4651359 B2 JP 4651359B2 JP 2004315998 A JP2004315998 A JP 2004315998A JP 2004315998 A JP2004315998 A JP 2004315998A JP 4651359 B2 JP4651359 B2 JP 4651359B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- semiconductor device

- solder resist

- wiring board

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/3201—Structure

- H01L2224/32012—Structure relative to the bonding area, e.g. bond pad

- H01L2224/32014—Structure relative to the bonding area, e.g. bond pad the layer connector being smaller than the bonding area, e.g. bond pad

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48145—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

- H01L2224/48228—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item the bond pad being disposed in a recess of the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48471—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area being a ball bond, i.e. wedge-to-ball, reverse stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

- H01L2224/48476—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area

- H01L2224/48477—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding)

- H01L2224/48478—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball

- H01L2224/48479—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48475—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball

- H01L2224/48476—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area

- H01L2224/48477—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding)

- H01L2224/48478—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball

- H01L2224/4848—Connecting portions connected to auxiliary connecting means on the bonding areas, e.g. pre-ball, wedge-on-ball, ball-on-ball between the wire connector and the bonding area being a pre-ball (i.e. a ball formed by capillary bonding) the connecting portion being a wedge bond, i.e. wedge on pre-ball outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/78—Apparatus for connecting with wire connectors

- H01L2224/7825—Means for applying energy, e.g. heating means

- H01L2224/783—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/78301—Capillary

- H01L2224/78302—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85009—Pre-treatment of the connector or the bonding area

- H01L2224/85051—Forming additional members, e.g. for "wedge-on-ball", "ball-on-wedge", "ball-on-ball" connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8512—Aligning

- H01L2224/85148—Aligning involving movement of a part of the bonding apparatus

- H01L2224/85169—Aligning involving movement of a part of the bonding apparatus being the upper part of the bonding apparatus, i.e. bonding head, e.g. capillary or wedge

- H01L2224/8518—Translational movements

- H01L2224/85186—Translational movements connecting first outside the semiconductor or solid-state body, i.e. off-chip, reverse stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85986—Specific sequence of steps, e.g. repetition of manufacturing steps, time sequence

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06506—Wire or wire-like electrical connections between devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0651—Wire or wire-like electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06582—Housing for the assembly, e.g. chip scale package [CSP]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01028—Nickel [Ni]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01046—Palladium [Pd]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/1015—Shape

- H01L2924/1016—Shape being a cuboid

- H01L2924/10162—Shape being a cuboid with a square active surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15182—Fan-in arrangement of the internal vias

- H01L2924/15183—Fan-in arrangement of the internal vias in a single layer of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Description

複数の電極が形成された主面と、前記主面と対向する裏面とを有する半導体チップを準備する工程、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材を介して、前記半導体チップの裏面が前記配線基板の主面と対向するように、前記半導体チップを前記配線基板の主面上に搭載する工程、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とを複数のボンディングワイヤを介してそれぞれ電気的に接続する工程、

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を樹脂で封止する工程、

を含み、

前記半導体チップは、前記半導体チップの端部が前記絶縁膜の前記開口部と平面的に重なるように、前記配線基板の主面上に搭載され、

前記半導体チップ主面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を前記樹脂で覆うように封止するものである。

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材と、

複数の電極が形成された主面と、前記主面と対向する裏面とを有し、前記裏面が前記配線基板の主面と対向するように、前記接着材を介して前記配線基板の主面上に搭載された半導体チップと、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とをそれぞれ電気的に接続する複数のボンディングワイヤと、

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を封止する封止樹脂と、

を含み、

前記開口部は、前記絶縁膜において前記半導体チップの端部と平面的に重なる領域に形成されており、

前記封止樹脂は、前記半導体チップ主面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を覆うように形成されているものである。

本実施の形態の半導体装置およびその製造工程を図面を参照して説明する。

図30は、本発明の他の実施の形態である半導体装置1bの製造工程中の要部断面図であり、上記実施の形態1の図4にほぼ対応する領域が示されている。図31および図32は、本実施の形態のワイヤボンディング工程の説明図(要部断面図)である。

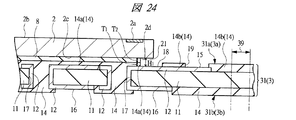

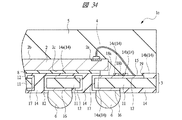

図34は、本発明の他の実施の形態である半導体装置1cの要部断面図であり、図35は、その平面透視図(上面図)である。図34は、上記実施の形態1の図4に対応する。また、図35は、上記実施の形態1の図7に対応し、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1cの平面透視図(上面図)、すなわち半導体装置1cに用いられている配線基板3の上面図が示されている。なお、図35では、半導体チップ2の外形を点線で示してある。また、図35は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、第3ソルダレジスト部14c、および第2ソルダレジスト部14bの開口部19から露出する接続端子15にハッチングを付してある。

図36は、本発明の他の実施の形態である半導体装置1dの要部断面図であり、上記実施の形態1の図4に対応する。

図37は、本発明の他の実施の形態である半導体装置の平面透視図(上面図)であり、図38は、本発明の更に他の実施の形態である半導体装置の平面透視図(上面図)であり、それぞれ上記実施の形態1の図7に対応する。従って図37および図38には、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置の平面透視図(上面図)、すなわち、本実施の形態の半導体装置に用いられている配線基板3の上面図が示されている。また、図37および図38では、半導体チップ2の外形を点線で示してある。また、図37および図38は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、および第2ソルダレジスト部14bの開口部19から露出する接続端子15にハッチングを付してある。

図39は、本発明の他の実施の形態である半導体装置1eの端部近傍領域の要部断面図(部分拡大断面図)であり、上記実施の形態1の図4に対応する。図40は、封止樹脂5を透視したときの半導体装置1eの平面透視図(上面図)であり、上記実施の形態1の図6に対応する。図41は、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1eの平面透視図(上面図)、すなわち半導体装置1eに用いられている配線基板3の上面図であり、上記実施の形態1の図7に対応する。図42〜図44は、本実施の形態の半導体装置1eの製造に用いられる配線基板31の製造工程の一例を模式的に示す平面図(上面図)であり、上記実施の形態1の図21〜図23に対応する。なお、図41では、半導体チップ2の外形を点線で示してある。また、図41は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、および第2ソルダレジスト部14bから露出する接続端子15にハッチングを付してある。

図45は、本発明の他の実施の形態である半導体装置1fの要部断面図であり、上記実施の形態6の図39に対応する。

図46は、本発明の他の実施の形態である半導体装置1gの平面透視図(上面図)であり、図47は、その断面図である。図46は、上記実施の形態1の図6に対応し、封止樹脂5を透視したときの半導体装置1gの平面透視図(上面図)が示されている。図47は、上記実施の形態1の図3に対応し、図46のB−B線の断面が図47にほぼ対応する。

図48は、本発明の他の実施の形態である半導体装置1hの平面透視図(上面図)であり、図49および図50は、その断面図である。図48は、上記実施の形態1の図6に対応し、封止樹脂5を透視したときの半導体装置1hの平面透視図(上面図)が示されている。また、図49と図50とは異なる断面である。

1a 半導体装置

1b 半導体装置

1c 半導体装置

1d 半導体装置

1e 半導体装置

1f 半導体装置

1g 半導体装置

1h 半導体装置

2 半導体チップ

2a 電極

2b 表面

2c 裏面

2d 外周部

2e 側面

2f 端部

3 配線基板

3a 上面

3b 下面

4 ボンディングワイヤ

5 封止樹脂

5a 封止樹脂

6 半田ボール

8 接着材

11 基材層

11a 上面

11b 下面

12 導体層

14 ソルダレジスト層

14a 第1ソルダレジスト部

14b 第2ソルダレジスト部

14c 第3ソルダレジスト部

15 接続端子

16 ランド

17 開口部

18 領域

18a 領域

18b 領域

19 開口部

19a 開口部

20a 開口部

20b 後退部

21 空間

31 配線基板

32 半導体装置領域

33 導体パターン

34 めっき配線

35 スタッドバンプ

36 レーザ

41 キャピラリ

61 第1の部分

62 第2の部分

70 半導体チップ

70a 電極

71 接着材

101 半導体装置

103 配線基板

103a 上面

114 ソルダレジスト層

201 半導体装置

203 配線基板

203a 上面

214 ソルダレジスト層

214a 第1ソルダレジスト部

214b 第2ソルダレジスト部

218 領域

221 空間

301 半導体装置

Claims (11)

- 平面形状が四角形から成る基材層と、前記基材層の主面に設けられた複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するように前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板を準備する工程、

複数の電極が形成された主面と、前記主面と対向する裏面とを有する半導体チップを準備する工程、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材を介して、前記半導体チップの裏面が前記配線基板の主面と対向するように、前記半導体チップを前記配線基板の主面上に搭載する工程、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とを複数のボンディングワイヤを介してそれぞれ電気的に接続する工程、

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を樹脂で封止する工程、

を含み、

前記半導体チップは、前記半導体チップの端部が前記絶縁膜の前記開口部と平面的に重なるように、前記配線基板の主面上に搭載され、

前記半導体チップ主面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を前記樹脂で覆うように封止することを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記複数のボンディングワイヤの接続は、キャピラリを用いて行われることを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記開口部は、前記半導体チップの端部に沿って形成されていることを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記開口部の平面形状は、リング状に形成されていることを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法において、

前記半導体チップの平面形状は四角形から成り、

前記半導体チップは、前記半導体チップの各辺が前記配線基板の各辺と並ぶように前記配線基板の主面上に搭載され、

前記開口部は、前記半導体チップの各辺に沿って形成され、

前記開口部の角部は、前記配線基板の角部に向かって後退していることを特徴とする半導体装置の製造方法。 - 請求項5記載の半導体装置の製造方法において、

前記開口部の各辺のそれぞれの一部は、前記配線基板の各辺に向かって後退していることを特徴とする半導体装置の製造方法。 - 平面形状が四角形から成る基材層と、前記基材層の主面に設けられた複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するように前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板と、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材と、

複数の電極が形成された主面と、前記主面と対向する裏面とを有し、前記裏面が前記配線基板の主面と対向するように、前記接着材を介して前記配線基板の主面上に搭載された半導体チップと、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とをそれぞれ電気的に接続する複数のボンディングワイヤと、

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を封止する封止樹脂と、

を含み、

前記開口部は、前記絶縁膜において前記半導体チップの端部と平面的に重なる領域に形成されており、

前記封止樹脂は、前記半導体チップ主面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を覆うように形成されていることを特徴とする半導体装置。 - 請求項7記載の半導体装置において、

前記開口部は、前記半導体チップの端部に沿って形成されていることを特徴とする半導体装置。 - 請求項7記載の半導体装置において、

前記開口部の平面形状は、リング状に形成されていることを特徴とする半導体装置。 - 請求項7記載の半導体装置において、

前記半導体チップの平面形状は四角形から成り、

前記半導体チップは、前記半導体チップの各辺が前記配線基板の各辺と並ぶように前記配線基板の主面上に搭載され、

前記開口部は、前記半導体チップの各辺に沿って形成され、

前記開口部の角部は、前記配線基板の角部に向かって後退していることを特徴とする半導体装置。 - 請求項10記載の半導体装置において、

前記開口部の各辺のそれぞれの一部は、前記配線基板の各辺に向かって後退していることを特徴とする半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004315998A JP4651359B2 (ja) | 2004-10-29 | 2004-10-29 | 半導体装置およびその製造方法 |

| TW094135613A TWI374527B (en) | 2004-10-29 | 2005-10-13 | A semiconductor device and a method for manufacturing of the same |

| KR1020050102451A KR101117848B1 (ko) | 2004-10-29 | 2005-10-28 | 반도체 장치 및 그 제조 방법 |

| CNB200510117027XA CN100479135C (zh) | 2004-10-29 | 2005-10-28 | 半导体器件及其制造方法 |

| US11/260,084 US7518250B2 (en) | 2004-10-29 | 2005-10-28 | Semiconductor device and a method for manufacturing of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004315998A JP4651359B2 (ja) | 2004-10-29 | 2004-10-29 | 半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006128455A JP2006128455A (ja) | 2006-05-18 |

| JP2006128455A5 JP2006128455A5 (ja) | 2007-12-13 |

| JP4651359B2 true JP4651359B2 (ja) | 2011-03-16 |

Family

ID=36260867

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004315998A Expired - Fee Related JP4651359B2 (ja) | 2004-10-29 | 2004-10-29 | 半導体装置およびその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7518250B2 (ja) |

| JP (1) | JP4651359B2 (ja) |

| KR (1) | KR101117848B1 (ja) |

| CN (1) | CN100479135C (ja) |

| TW (1) | TWI374527B (ja) |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SG111935A1 (en) | 2002-03-04 | 2005-06-29 | Micron Technology Inc | Interposer configured to reduce the profiles of semiconductor device assemblies and packages including the same and methods |

| SG121707A1 (en) | 2002-03-04 | 2006-05-26 | Micron Technology Inc | Method and apparatus for flip-chip packaging providing testing capability |

| JP2007335581A (ja) * | 2006-06-14 | 2007-12-27 | Renesas Technology Corp | 半導体装置の製造方法 |

| EP2272794A1 (en) * | 2006-07-14 | 2011-01-12 | STMicroelectronics S.r.l. | Semiconductor package substrate, in particular for MEMS devices |

| KR100766503B1 (ko) * | 2006-09-20 | 2007-10-15 | 삼성전자주식회사 | 반도체 소자 패키지 |

| JP2008078367A (ja) * | 2006-09-21 | 2008-04-03 | Renesas Technology Corp | 半導体装置 |

| JP5511125B2 (ja) * | 2006-12-27 | 2014-06-04 | キヤノン株式会社 | 半導体モジュール及びその製造方法 |

| KR20090041756A (ko) * | 2007-10-24 | 2009-04-29 | 삼성전자주식회사 | 접착층을 갖는 프린트 배선 기판 및 이를 이용한 반도체패키지 |

| JP2009194079A (ja) * | 2008-02-13 | 2009-08-27 | Panasonic Corp | 半導体装置用配線基板とその製造方法及びそれを用いた半導体装置 |

| KR101351188B1 (ko) * | 2008-02-29 | 2014-01-14 | 삼성테크윈 주식회사 | 볼 그리드 어레이 패키지용 인쇄회로기판 및 그 제조 방법 |

| JP2010165923A (ja) * | 2009-01-16 | 2010-07-29 | Renesas Electronics Corp | 半導体装置、及びその製造方法 |

| JP2010238693A (ja) * | 2009-03-30 | 2010-10-21 | Toppan Printing Co Ltd | 半導体素子用基板の製造方法および半導体装置 |

| WO2010112983A1 (en) * | 2009-03-31 | 2010-10-07 | Stmicroelectronics (Grenoble 2) Sas | Wire-bonded semiconductor package with a coated wire |

| JP2011077108A (ja) * | 2009-09-29 | 2011-04-14 | Elpida Memory Inc | 半導体装置 |

| US8536718B2 (en) * | 2010-06-24 | 2013-09-17 | Stats Chippac Ltd. | Integrated circuit packaging system with trenches and method of manufacture thereof |

| JP2012084840A (ja) | 2010-09-13 | 2012-04-26 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

| WO2013065420A1 (ja) | 2011-10-31 | 2013-05-10 | 株式会社村田製作所 | 電子部品、集合基板及び電子部品の製造方法 |

| JP2015220235A (ja) * | 2014-05-14 | 2015-12-07 | マイクロン テクノロジー, インク. | 半導体装置 |

| US11171126B2 (en) * | 2015-09-04 | 2021-11-09 | Octavo Systems Llc | Configurable substrate and systems |

| KR101815754B1 (ko) * | 2016-03-10 | 2018-01-08 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스 |

| JP6776280B2 (ja) * | 2018-01-10 | 2020-10-28 | 株式会社東芝 | 無線通信モジュール、プリント基板、および製造方法 |

| CN110112117A (zh) * | 2018-02-01 | 2019-08-09 | 爱思开海力士有限公司 | 半导体封装 |

| US10879160B2 (en) * | 2018-02-01 | 2020-12-29 | SK Hynix Inc. | Semiconductor package with packaging substrate |

| JP2020047664A (ja) | 2018-09-14 | 2020-03-26 | キオクシア株式会社 | 半導体装置および半導体装置の作製方法 |

| CN109650323B (zh) * | 2018-12-24 | 2020-11-03 | 烟台艾睿光电科技有限公司 | 一种焊料隔离结构以及电子器件 |

| KR20220009622A (ko) | 2020-07-16 | 2022-01-25 | 삼성전자주식회사 | 반도체 패키지 |

| US20230046645A1 (en) * | 2021-08-11 | 2023-02-16 | Stmicroelectronics (Malta) Ltd. | Integrated circuit package with warpage control using cavity formed in laminated substrate below the integrated circuit die |

| US11729915B1 (en) * | 2022-03-22 | 2023-08-15 | Tactotek Oy | Method for manufacturing a number of electrical nodes, electrical node module, electrical node, and multilayer structure |

Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06506319A (ja) * | 1990-12-21 | 1994-07-14 | モトローラ・インコーポレイテッド | リードレス・パッド・アレイ・チップ・キャリア |

| JPH08316360A (ja) * | 1995-05-18 | 1996-11-29 | Citizen Watch Co Ltd | Ic実装構造 |

| JPH09307043A (ja) * | 1996-05-10 | 1997-11-28 | Dainippon Printing Co Ltd | リードフレーム部材とその製造方法、および該リードフレーム部材を用いた半導体装置 |

| JPH09330943A (ja) * | 1996-06-13 | 1997-12-22 | Shinko Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2000058699A (ja) * | 1998-08-04 | 2000-02-25 | Sony Corp | 半導体装置およびその製造方法 |

| JP2000133742A (ja) * | 1998-10-23 | 2000-05-12 | Hitachi Ltd | パッケージ基板およびそれを用いた半導体装置ならびにその製造方法 |

| JP2000174168A (ja) * | 1998-12-03 | 2000-06-23 | Sanyo Electric Co Ltd | 半導体装置 |

| JP2002314003A (ja) * | 2001-04-12 | 2002-10-25 | Mitsubishi Electric Corp | ベース配線基板およびその製造方法ならびに半導体装置およびその製造方法 |

| JP2002329807A (ja) * | 1994-08-15 | 2002-11-15 | Citizen Watch Co Ltd | 半導体装置 |

| JP2003051511A (ja) * | 2001-08-03 | 2003-02-21 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2003092374A (ja) * | 2001-09-18 | 2003-03-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2003273287A (ja) * | 2002-03-15 | 2003-09-26 | Mitsubishi Electric Corp | 半導体装置 |

| JP2004282098A (ja) * | 1994-03-18 | 2004-10-07 | Hitachi Chem Co Ltd | 半導体パッケージの製造方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4401775A (en) * | 1982-06-24 | 1983-08-30 | Rca Corporation | Epoxy encapsulating formulation |

| JP2931741B2 (ja) * | 1993-09-24 | 1999-08-09 | 株式会社東芝 | 半導体装置 |

| US6867493B2 (en) * | 2000-11-15 | 2005-03-15 | Skyworks Solutions, Inc. | Structure and method for fabrication of a leadless multi-die carrier |

| JP4075306B2 (ja) * | 2000-12-19 | 2008-04-16 | 日立電線株式会社 | 配線基板、lga型半導体装置、及び配線基板の製造方法 |

| JP2002280414A (ja) * | 2001-03-22 | 2002-09-27 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| US6894398B2 (en) * | 2001-03-30 | 2005-05-17 | Intel Corporation | Insulated bond wire assembly for integrated circuits |

| JP2003007921A (ja) * | 2001-06-19 | 2003-01-10 | Sanyo Electric Co Ltd | 回路装置およびその製造方法 |

| SG104291A1 (en) * | 2001-12-08 | 2004-06-21 | Micron Technology Inc | Die package |

| US6740193B2 (en) * | 2001-12-21 | 2004-05-25 | Henkel Corporation | Gem-diesters and epoxidized derivatives thereof |

| US20050194698A1 (en) * | 2004-03-03 | 2005-09-08 | St Assembly Test Service Ltd. | Integrated circuit package with keep-out zone overlapping undercut zone |

| US7459795B2 (en) * | 2004-08-19 | 2008-12-02 | Formfactor, Inc. | Method to build a wirebond probe card in a many at a time fashion |

-

2004

- 2004-10-29 JP JP2004315998A patent/JP4651359B2/ja not_active Expired - Fee Related

-

2005

- 2005-10-13 TW TW094135613A patent/TWI374527B/zh not_active IP Right Cessation

- 2005-10-28 CN CNB200510117027XA patent/CN100479135C/zh not_active Expired - Fee Related

- 2005-10-28 KR KR1020050102451A patent/KR101117848B1/ko not_active IP Right Cessation

- 2005-10-28 US US11/260,084 patent/US7518250B2/en not_active Expired - Fee Related

Patent Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06506319A (ja) * | 1990-12-21 | 1994-07-14 | モトローラ・インコーポレイテッド | リードレス・パッド・アレイ・チップ・キャリア |

| JP2004282098A (ja) * | 1994-03-18 | 2004-10-07 | Hitachi Chem Co Ltd | 半導体パッケージの製造方法 |

| JP2002329807A (ja) * | 1994-08-15 | 2002-11-15 | Citizen Watch Co Ltd | 半導体装置 |

| JPH08316360A (ja) * | 1995-05-18 | 1996-11-29 | Citizen Watch Co Ltd | Ic実装構造 |

| JPH09307043A (ja) * | 1996-05-10 | 1997-11-28 | Dainippon Printing Co Ltd | リードフレーム部材とその製造方法、および該リードフレーム部材を用いた半導体装置 |

| JPH09330943A (ja) * | 1996-06-13 | 1997-12-22 | Shinko Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2000058699A (ja) * | 1998-08-04 | 2000-02-25 | Sony Corp | 半導体装置およびその製造方法 |

| JP2000133742A (ja) * | 1998-10-23 | 2000-05-12 | Hitachi Ltd | パッケージ基板およびそれを用いた半導体装置ならびにその製造方法 |

| JP2000174168A (ja) * | 1998-12-03 | 2000-06-23 | Sanyo Electric Co Ltd | 半導体装置 |

| JP2002314003A (ja) * | 2001-04-12 | 2002-10-25 | Mitsubishi Electric Corp | ベース配線基板およびその製造方法ならびに半導体装置およびその製造方法 |

| JP2003051511A (ja) * | 2001-08-03 | 2003-02-21 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2003092374A (ja) * | 2001-09-18 | 2003-03-28 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP2003273287A (ja) * | 2002-03-15 | 2003-09-26 | Mitsubishi Electric Corp | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101117848B1 (ko) | 2012-03-15 |

| US7518250B2 (en) | 2009-04-14 |

| TW200629509A (en) | 2006-08-16 |

| CN1779951A (zh) | 2006-05-31 |

| CN100479135C (zh) | 2009-04-15 |

| JP2006128455A (ja) | 2006-05-18 |

| US20060091523A1 (en) | 2006-05-04 |

| TWI374527B (en) | 2012-10-11 |

| KR20060052333A (ko) | 2006-05-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4651359B2 (ja) | 半導体装置およびその製造方法 | |

| JP5271949B2 (ja) | 半導体装置 | |

| US7662672B2 (en) | Manufacturing process of leadframe-based BGA packages | |

| JP5280014B2 (ja) | 半導体装置及びその製造方法 | |

| US20140035161A1 (en) | Semiconductor device and method of manufacturing the same | |

| US8133759B2 (en) | Leadframe | |

| US20110037170A1 (en) | Electronic device and manufacturing method therefor | |

| KR20060101385A (ko) | 반도체 장치 및 그 제조 방법 | |

| US9972560B2 (en) | Lead frame and semiconductor device | |

| JP5946511B2 (ja) | 半導体装置の製造方法 | |

| JP2012084840A (ja) | 半導体装置及びその製造方法 | |

| JP2005244035A (ja) | 半導体装置の実装方法、並びに半導体装置 | |

| US20110291244A1 (en) | Semiconductor device and method of manufacturing the same | |

| US8179686B2 (en) | Mounted structural body and method of manufacturing the same | |

| US20180090429A1 (en) | Semiconductor device | |

| JP2008198916A (ja) | 半導体装置及びその製造方法 | |

| JP2007012716A (ja) | 半導体装置 | |

| TWI501371B (zh) | A wiring member for a semiconductor device, a composite wiring member for a semiconductor device, and a resin-sealed type semiconductor device | |

| JP2008235492A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2013254984A (ja) | 半導体装置 | |

| JP2005158999A (ja) | 半導体装置 | |

| JP2012138394A (ja) | 半導体装置の製造方法 | |

| JP7269756B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2008071847A (ja) | 半導体装置の製造方法 | |

| KR20240040041A (ko) | 전자 장치 및 전자 장치 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071025 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071025 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080303 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100916 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101130 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101214 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4651359 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131224 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |