JP4593159B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4593159B2 JP4593159B2 JP2004129233A JP2004129233A JP4593159B2 JP 4593159 B2 JP4593159 B2 JP 4593159B2 JP 2004129233 A JP2004129233 A JP 2004129233A JP 2004129233 A JP2004129233 A JP 2004129233A JP 4593159 B2 JP4593159 B2 JP 4593159B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- semiconductor device

- gate electrode

- writing

- charge storage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 48

- 238000000034 method Methods 0.000 claims description 44

- 230000008569 process Effects 0.000 claims description 33

- 239000000758 substrate Substances 0.000 claims description 21

- 238000002347 injection Methods 0.000 claims description 14

- 239000007924 injection Substances 0.000 claims description 14

- 239000002784 hot electron Substances 0.000 claims description 11

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 claims description 3

- 238000009792 diffusion process Methods 0.000 claims 8

- 239000012535 impurity Substances 0.000 claims 4

- 238000009413 insulation Methods 0.000 claims 3

- 230000014759 maintenance of location Effects 0.000 description 13

- 230000007423 decrease Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 238000000605 extraction Methods 0.000 description 4

- 238000013500 data storage Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- 238000012795 verification Methods 0.000 description 3

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- 238000005215 recombination Methods 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000012790 confirmation Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000006386 memory function Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/107—Programming all cells in an array, sector or block to the same state prior to flash erasing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3468—Prevention of overerasure or overprogramming, e.g. by verifying whilst erasing or writing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

Landscapes

- Read Only Memory (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

Description

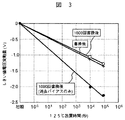

図6のような消去ブロック内で一括消去を行う半導体不揮発性記憶装置を想定し、本発明の実施形態である書換え手順を図7に示す。書換え開始後、消去ブロック内の全てのメモリセルを書込む。その処理が完了したら、消去ブロック内の全てのメモリセルに消去バイアスを印加する。全てのセルで、必要な読出電流が取れるまでしきい値を下げた事が確認できた段階で、消去処理は終了となる。本発明の、消去ブロック内の全てのメモリセルを書込む処理は、消去バイアスの印加と一体のものであり、消去コマンド実行時に必ず行うものとする。続いて、必要な情報を格納するために、所望のメモリセルに書込みを行う。書込みの方式は、ホットエレクトロンあるいはトンネル注入とする。書込みが完了した段階で、書換え処理の全てが完了する。この一連の動作により、過消去状態になるメモリセルを無くす事ができ、半導体不揮発性記憶装置の信頼度を高めることが出来る。

さらに、図6、図7について以下に詳細に説明をする。

まず、書換対象となる全ビットに書き込む処理を行う。書換対象のワード線群から最初の1本を選び、書き込みワード電圧を印加する。次に、共通ソース線に書き込み電圧を印加する。続いて、最初に書き込むセルに接続されたビット線に、書き込み選択信号である0Vを印加して書き込む。ビット線の書き込み選択信号は、セルのドレインに印加されるパルス電圧である。この書き込み処理の後、次のビット線を選択して0Vパルスを印加し、そのビット線に接続されたセルを書き込む。このようにして、同一のワード線に接続された全てのビット線に選択信号を印加して、そのワード線に接続された全てのセルに書き込む処理を終えたら、次のワード線を選択して、再び最初のビット線から書き込み電圧を印加する。こうして、全てのワード線に対して書き込み処理を終えたら、一旦、全ワード線、全ビット線、共通ソース線の電位を0Vに落とす。この後、セルのしきい値を下げる処理を行う。

消去が終了したので、次は必要な情報を書き込む。最初の書き込みワード線を選択し、次に共通ソース線に書き込み電圧を印加し、次に書き込みビット線を選択する。書き込みビット線選択は、セルのドレインに0Vを印加することに相当し、これによって、そのセルのソース・ドレイン間に書き込みに必要なチャネル電流が流れる。次にワード線と共通ソース線を0Vにしてチャネル電流を切る。続いて、このセルに正しく情報を書き込めたかどうかの検証を行う。共通ソース線には書き込み時より低い読出し電圧を印加する。書き込み時に選択したワード線に読み出し電圧を印加する。そして、そのセルが接続されているビット線に0Vを印加して選択し、セル電流を検出する。この電流が規定値以上の電流が検出されたときは、しきい値が十分に高くないので、再び書き込みの処理を行う。規定値以下であれば、しきい値が十分に高くなった、即ち、正常に書き込めたと判断して、次の書き込み対象となるセルが接続されたビット線を選択し、次のセルの書き込みを行う。この手順を繰り返し、同一ワード線内での書き込みが終了したら、次のワード線を選択し、書き込み対象となるビット線を次々に選択して書き込み処理を行う。全てのワード線内で、対象となるセルへの書込みが終了したら、全ワード線、全ビット線、共通ソース線の電位を0Vに戻し、書換処理は終了である。

図6のようなメモリアレイを同一基板上に搭載した半導体論理集積回路の実施形態である、マイクロコントローラを図8に示す。中央演算処理装置CPU、不揮発性メモリアレイを含み、情報の不揮発格納機能を有するフラッシュメモリモジュール、それを制御するフラッシュメモリモジュール制御回路、揮発性メモリモジュールRAM、バスステート制御回路部、入出力回路部I/O、その他の機能を有する周辺回路部から構成される。これらの回路ブロックは、内部バスに接続される。この内部バスは、アドレス信号、データ信号、制御信号を伝達する信号線を有する。CPUは命令解読、それにしたがった演算処理を実行する。フラッシュメモリモジュールは、CPUの動作プログラムあるいはデータの格納に供される。フラッシュメモリモジュールの動作は、CPUがフラッシュメモリモジュール制御回路に設定した制御データに基づいて行われる。RAMは、CPUのワーク領域あるいはデータの一時記憶に供される。バスステート制御回路は、内部バスを介するアクセス、外部バスに対するアクセスサイクル数、バス幅などの制御を行う。フラッシュメモリモジュールの情報書換え時に本発明の書換え法を用いれば、電化保持特性の劣化を抑制できる。即ち、信頼性の高い、不揮発メモリを搭載したマイクロコントローラを提供することが可能となる。

Claims (11)

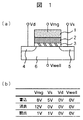

- 半導体基板の一主面側に所定の間隔を置いて形成されたソース拡散層およびドレイン拡散層と、前記ソース拡散層および前記ドレイン拡散層に挟まれた前記半導体基板の領域上に絶縁膜を介して電荷蓄積膜およびゲート電極が積層されてなるゲート部とからなるメモリセルを有し、

消去動作において、ホールが前記ゲート電極から前記電荷蓄積膜へ供給され、前記電荷蓄積膜に保存された電子と、前記ゲート電極から供給されるホールとが結合して消滅し、

前記電荷蓄積膜に保存された電子と結合できなかった前記ゲート電極から供給さるホールが、前記絶縁膜をトンネルして前記半導体基板に抜ける半導体装置であって、

前記メモリセルの書換えを行う前に、前記書換えの対象となるメモリセルの書込みを行い、その後に前記メモリセルの消去を行うことを特徴とする半導体装置。 - 半導体基板の一主面側に所定の間隔を置いて形成されたソース拡散層およびドレイン拡散層と、前記ソース拡散層および前記ドレイン拡散層に挟まれた前記半導体基板の領域上に絶縁膜を介して電荷蓄積膜およびゲート電極が積層されてなるゲート部とからなるメモリセルが配置されたサブブロックを有する半導体装置において、

前記メモリセルの書換えを行う前に、書換えの対象となる前記サブブロック内の全てのメモリセルに電子を注入することにより書込みを行い、

その後に前記ゲート電極から電極蓄積膜にホールを供給して消去を行い、

前記電荷蓄積膜に保存された電子と、前記ゲート電極から供給されるホールとが結合して消滅し、前記電荷蓄積膜に保存された電子と結合できなかった前記ゲート電極から供給されるホールが、前記絶縁膜をトンネルして前記半導体基板に抜けることを特徴とする半導体装置。 - 前記メモリセルの各々は、MONOS型あるいはMNOS型構造を有する電荷トラップ型メモリセルであり、前記半導体基板側から前記絶縁膜を通り、前記電荷トラップ型メモリセルへ電子を注入することにより書込みを行うことを特徴とする請求項1に記載の半導体装置。

- 前記メモリセルの各々は、MONOS型あるいはMNOS型構造を有する電荷トラップ型メモリセルであり、前記半導体基板側から前記絶縁膜を通り、前記電荷トラップ型メモリセルへ電子を注入することにより書込みを行うことを特徴とする請求項2に記載の半導体装置。

- 前記メモリセルの各々への書込みは、ホットエレクトロンを用いた電子注入によることを特徴とする請求項1に記載の半導体装置。

- 前記メモリセルの各々への書込みは、ホットエレクトロンを用いた電子注入によることを特徴とする請求項2に記載の半導体装置。

- メモリセルの消去において、前記メモリセルのメモリセル読み出し電流が検出され、前記メモリセル読み出し電流が所定値に達した時点で、前記消去が停止することを特徴とする請求項1に記載の半導体装置。

- メモリセルの消去において、前記メモリセルのメモリセル読み出し電流が検出され、前記メモリセル読み出し電流が所定値に達した時点で、前記消去が停止することを特徴とする請求項2に記載の半導体装置。

- 前記メモリセルの各々の消去は、前記メモリセルのしきい値を下げることにより行われることを特徴とする請求項1に記載の半導体装置。

- 前記メモリセルの各々の消去は、前記メモリセルのしきい値を下げることにより行われることを特徴とする請求項2に記載の半導体装置。

- 半導体基板の一主面側に所定の間隔を置いて形成された第1不純物導入領域および第2不純物導入領域と、前記第1不純物導入領域および前記第2不純物導入領域に挟まれた前記半導体基板の領域上に絶縁膜を介して電荷蓄積膜および電極が積層されてなるゲート部とからなるメモリセルを有し、

消去動作において、ホールが前記ゲート電極から前記電荷蓄積膜へ供給され、前記電荷蓄積膜に保存された電子と、前記ゲート電極から供給されるホールとが結合して消滅し、

前記電荷蓄積膜に保存された電子と結合できなかった前記ゲート電極から供給さるホールが、前記絶縁膜をトンネルして前記半導体基板に抜ける半導体装置であって、

前記メモリセルの消去コマンドの実行は、前記消去の対象となるメモリセルに書込み処理を行った後に行うことを特徴とする半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004129233A JP4593159B2 (ja) | 2003-05-28 | 2004-04-26 | 半導体装置 |

| TW093114807A TW200506952A (en) | 2003-05-28 | 2004-05-25 | Semiconductor device |

| US10/852,150 US8054680B2 (en) | 2003-05-28 | 2004-05-25 | Semiconductor device |

| KR1020040038120A KR20040103781A (ko) | 2003-05-28 | 2004-05-28 | 반도체 장치 |

| CNA2004100455022A CN1574062A (zh) | 2003-05-28 | 2004-05-28 | 半导体器件 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003150226 | 2003-05-28 | ||

| JP2004129233A JP4593159B2 (ja) | 2003-05-28 | 2004-04-26 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005011490A JP2005011490A (ja) | 2005-01-13 |

| JP2005011490A5 JP2005011490A5 (ja) | 2007-05-17 |

| JP4593159B2 true JP4593159B2 (ja) | 2010-12-08 |

Family

ID=33566714

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004129233A Expired - Fee Related JP4593159B2 (ja) | 2003-05-28 | 2004-04-26 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8054680B2 (ja) |

| JP (1) | JP4593159B2 (ja) |

| KR (1) | KR20040103781A (ja) |

| CN (1) | CN1574062A (ja) |

| TW (1) | TW200506952A (ja) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007193862A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP4965948B2 (ja) | 2006-09-21 | 2012-07-04 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5068053B2 (ja) * | 2006-10-02 | 2012-11-07 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置およびその動作方法 |

| JP2008270343A (ja) * | 2007-04-17 | 2008-11-06 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

| JP5238208B2 (ja) | 2007-09-27 | 2013-07-17 | 株式会社東芝 | 不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置 |

| US7643349B2 (en) * | 2007-10-18 | 2010-01-05 | Macronix International Co., Ltd. | Efficient erase algorithm for SONOS-type NAND flash |

| JP5166095B2 (ja) | 2008-03-31 | 2013-03-21 | 株式会社東芝 | 不揮発性半導体記憶装置の駆動方法及び不揮発性半導体記憶装置 |

| US8514630B2 (en) | 2010-07-09 | 2013-08-20 | Sandisk Technologies Inc. | Detection of word-line leakage in memory arrays: current based approach |

| US8432732B2 (en) | 2010-07-09 | 2013-04-30 | Sandisk Technologies Inc. | Detection of word-line leakage in memory arrays |

| US8379454B2 (en) * | 2011-05-05 | 2013-02-19 | Sandisk Technologies Inc. | Detection of broken word-lines in memory arrays |

| US8775901B2 (en) | 2011-07-28 | 2014-07-08 | SanDisk Technologies, Inc. | Data recovery for defective word lines during programming of non-volatile memory arrays |

| US8750042B2 (en) | 2011-07-28 | 2014-06-10 | Sandisk Technologies Inc. | Combined simultaneous sensing of multiple wordlines in a post-write read (PWR) and detection of NAND failures |

| US8730722B2 (en) | 2012-03-02 | 2014-05-20 | Sandisk Technologies Inc. | Saving of data in cases of word-line to word-line short in memory arrays |

| US9165683B2 (en) | 2013-09-23 | 2015-10-20 | Sandisk Technologies Inc. | Multi-word line erratic programming detection |

| KR102170975B1 (ko) * | 2013-10-31 | 2020-10-28 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 불량 워드라인 탐지 방법 |

| US9443612B2 (en) | 2014-07-10 | 2016-09-13 | Sandisk Technologies Llc | Determination of bit line to low voltage signal shorts |

| US9514835B2 (en) | 2014-07-10 | 2016-12-06 | Sandisk Technologies Llc | Determination of word line to word line shorts between adjacent blocks |

| US9460809B2 (en) | 2014-07-10 | 2016-10-04 | Sandisk Technologies Llc | AC stress mode to screen out word line to word line shorts |

| US9484086B2 (en) | 2014-07-10 | 2016-11-01 | Sandisk Technologies Llc | Determination of word line to local source line shorts |

| US9240249B1 (en) | 2014-09-02 | 2016-01-19 | Sandisk Technologies Inc. | AC stress methods to screen out bit line defects |

| US9202593B1 (en) | 2014-09-02 | 2015-12-01 | Sandisk Technologies Inc. | Techniques for detecting broken word lines in non-volatile memories |

| US9449694B2 (en) | 2014-09-04 | 2016-09-20 | Sandisk Technologies Llc | Non-volatile memory with multi-word line select for defect detection operations |

| US9659666B2 (en) | 2015-08-31 | 2017-05-23 | Sandisk Technologies Llc | Dynamic memory recovery at the sub-block level |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02137196A (ja) * | 1988-11-17 | 1990-05-25 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH0936264A (ja) * | 1995-05-18 | 1997-02-07 | Sanyo Electric Co Ltd | 半導体装置および不揮発性半導体メモリ |

| JPH11134881A (ja) * | 1997-10-31 | 1999-05-21 | Sanyo Electric Co Ltd | 不揮発性多値メモリ装置及びそのデータの消去方法 |

| JP2000021181A (ja) * | 1998-06-30 | 2000-01-21 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置 |

| WO2003012878A1 (en) * | 2001-07-27 | 2003-02-13 | Renesas Technology Corp. | Semiconductor device |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3882469A (en) * | 1971-11-30 | 1975-05-06 | Texas Instruments Inc | Non-volatile variable threshold memory cell |

| US5408115A (en) * | 1994-04-04 | 1995-04-18 | Motorola Inc. | Self-aligned, split-gate EEPROM device |

| US6469343B1 (en) * | 1998-04-02 | 2002-10-22 | Nippon Steel Corporation | Multi-level type nonvolatile semiconductor memory device |

| TW451427B (en) * | 1999-02-19 | 2001-08-21 | Mitsubishi Electric Corp | Non-volatile semiconductor memory device and the driving method, operation method and manufacturing method of the same |

| JP3980874B2 (ja) * | 2001-11-30 | 2007-09-26 | スパンション エルエルシー | 半導体記憶装置及びその駆動方法 |

| JP2003257192A (ja) * | 2002-03-06 | 2003-09-12 | Mitsubishi Electric Corp | 半導体記憶装置および不揮発性半導体記憶装置 |

| KR100456596B1 (ko) * | 2002-05-08 | 2004-11-09 | 삼성전자주식회사 | 부유트랩형 비휘발성 기억소자의 소거 방법 |

| US6894931B2 (en) * | 2002-06-20 | 2005-05-17 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| JP2004303918A (ja) * | 2003-03-31 | 2004-10-28 | Renesas Technology Corp | 半導体装置の製造方法および半導体装置 |

-

2004

- 2004-04-26 JP JP2004129233A patent/JP4593159B2/ja not_active Expired - Fee Related

- 2004-05-25 US US10/852,150 patent/US8054680B2/en not_active Expired - Lifetime

- 2004-05-25 TW TW093114807A patent/TW200506952A/zh unknown

- 2004-05-28 KR KR1020040038120A patent/KR20040103781A/ko not_active Application Discontinuation

- 2004-05-28 CN CNA2004100455022A patent/CN1574062A/zh active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02137196A (ja) * | 1988-11-17 | 1990-05-25 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH0936264A (ja) * | 1995-05-18 | 1997-02-07 | Sanyo Electric Co Ltd | 半導体装置および不揮発性半導体メモリ |

| JPH11134881A (ja) * | 1997-10-31 | 1999-05-21 | Sanyo Electric Co Ltd | 不揮発性多値メモリ装置及びそのデータの消去方法 |

| JP2000021181A (ja) * | 1998-06-30 | 2000-01-21 | Matsushita Electric Ind Co Ltd | 不揮発性半導体記憶装置 |

| WO2003012878A1 (en) * | 2001-07-27 | 2003-02-13 | Renesas Technology Corp. | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200506952A (en) | 2005-02-16 |

| US8054680B2 (en) | 2011-11-08 |

| US20050006698A1 (en) | 2005-01-13 |

| CN1574062A (zh) | 2005-02-02 |

| JP2005011490A (ja) | 2005-01-13 |

| KR20040103781A (ko) | 2004-12-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4593159B2 (ja) | 半導体装置 | |

| KR101463967B1 (ko) | 불휘발성 반도체 메모리, 소거 방법 및 프로그램 방법 | |

| JP5072723B2 (ja) | 不揮発性半導体記憶装置 | |

| KR102098266B1 (ko) | 반도체 메모리 장치 | |

| KR100381804B1 (ko) | 비휘발성 반도체 기억 장치 및 비휘발성 반도체 기억장치의 데이터 소거 방법 | |

| US6788580B2 (en) | Nonvolatile semiconductor storage device and data erasing method | |

| JP3709126B2 (ja) | 不揮発性半導体メモリ装置の消去方法 | |

| US6515908B2 (en) | Nonvolatile semiconductor memory device having reduced erase time and method of erasing data of the same | |

| KR100960352B1 (ko) | 선 소거 단계를 이용하여 플래시 메모리를 소거하는 방법 | |

| JP5058461B2 (ja) | フラッシュメモリのための選択的消去方法 | |

| JP3980874B2 (ja) | 半導体記憶装置及びその駆動方法 | |

| JP5565948B2 (ja) | 半導体メモリ | |

| JP2009266356A (ja) | Nand型フラッシュメモリ | |

| US7075832B2 (en) | Method for erasing an NROM cell | |

| TWI549134B (zh) | Nand型快閃記憶體及其程式化方法 | |

| JP3974778B2 (ja) | 不揮発性半導体メモリ装置およびそのデータ消去方法 | |

| KR20120006936A (ko) | 비휘발성 메모리 블록의 소프트 프로그램 | |

| JP2012198966A (ja) | 不揮発性半導体記憶装置及びそのデータ消去方法 | |

| CN111724852A (zh) | 非易失性存储器件及其擦除方法 | |

| JPWO2006059375A1 (ja) | 半導体装置および半導体装置の制御方法 | |

| JP4672673B2 (ja) | 半導体装置および半導体装置の制御方法 | |

| JP2007102923A (ja) | 不揮発性半導体記憶装置およびそのデータ消去方法 | |

| JP4613353B2 (ja) | 半導体装置およびプログラム方法 | |

| US20110069556A1 (en) | Nand flash memory | |

| KR101161393B1 (ko) | 플래쉬 메모리 장치의 소거 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070323 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070323 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070323 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090713 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090721 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090918 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100414 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100510 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100915 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4593159 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |