JP4369009B2 - 電圧クランプされたゲートを備えるパワーmosfet - Google Patents

電圧クランプされたゲートを備えるパワーmosfet Download PDFInfo

- Publication number

- JP4369009B2 JP4369009B2 JP2000107465A JP2000107465A JP4369009B2 JP 4369009 B2 JP4369009 B2 JP 4369009B2 JP 2000107465 A JP2000107465 A JP 2000107465A JP 2000107465 A JP2000107465 A JP 2000107465A JP 4369009 B2 JP4369009 B2 JP 4369009B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- voltage

- diode

- mosfet

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000006378 damage Effects 0.000 claims description 7

- 239000012535 impurity Substances 0.000 claims 2

- 230000015556 catabolic process Effects 0.000 description 24

- 238000010586 diagram Methods 0.000 description 13

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 5

- 239000008186 active pharmaceutical agent Substances 0.000 description 5

- 229910001416 lithium ion Inorganic materials 0.000 description 5

- 239000000463 material Substances 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000005641 tunneling Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 230000001502 supplementing effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/32—Means for protecting converters other than automatic disconnection

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/18—Digital stores in which the information is moved stepwise, e.g. shift registers using capacitors as main elements of the stages

- G11C19/182—Digital stores in which the information is moved stepwise, e.g. shift registers using capacitors as main elements of the stages in combination with semiconductor elements, e.g. bipolar transistors, diodes

- G11C19/184—Digital stores in which the information is moved stepwise, e.g. shift registers using capacitors as main elements of the stages in combination with semiconductor elements, e.g. bipolar transistors, diodes with field-effect transistors, e.g. MOS-FET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0611—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region

- H01L27/0617—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type

- H01L27/0629—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration integrated circuits having a two-dimensional layout of components without a common active region comprising components of the field-effect type in combination with diodes, or resistors, or capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/435—Resistive materials for field effect devices, e.g. resistive gate for MOSFET or MESFET

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/04—Modifications for accelerating switching

- H03K17/041—Modifications for accelerating switching without feedback from the output circuit to the control circuit

- H03K17/0412—Modifications for accelerating switching without feedback from the output circuit to the control circuit by measures taken in the control circuit

- H03K17/04123—Modifications for accelerating switching without feedback from the output circuit to the control circuit by measures taken in the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/081—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit

- H03K17/0812—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit by measures taken in the control circuit

- H03K17/08122—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit by measures taken in the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/161—Modifications for eliminating interference voltages or currents in field-effect transistor switches

- H03K17/162—Modifications for eliminating interference voltages or currents in field-effect transistor switches without feedback from the output circuit to the control circuit

- H03K17/163—Soft switching

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Logic Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electronic Switches (AREA)

Description

【発明の属する技術分野】

本発明はパワーMOSFETに関し、より詳細にはゲート酸化層を保護するために過電圧をクランプする回路を備えたMOSFETに関する。

【0002】

【従来の技術】

パワーMOSFETは、可搬型のコンピュータのような機器に対して電力を制御するためのスイッチとして幅広く用いられている。図1Aは、ゲートG´、ソースS´及びドレインD´を有するパワーMOSFET10の模式図であり、ゲートG´にバッファ増幅器12が接続された典型的な構成である。またMOSFET10はボディBを有しており、ボディBがゲートG´に短絡され、MOSFET10内の寄生バイポーラトランジスタがターンオンするのを防いでいる。また図1Aには寄生ダイオード11も示されており、MOSFET10のソース/ボディに接続されるアノードとドレインD´に接続されるカソードとを有している。そのMOSFETはNチャネルMOSFETであるため、バッファ増幅器12は正のゲート駆動電圧Vccを供給してMOSFET10をターンオンし、或いはゲートG´を接地してMOSFET10をターンオフする。またMOSFET10はPチャネルMOSFETであってもよいが、その場合にはMOSFET10をターンオンするのに必要な電圧Vccは負の電圧であろう。

【0003】

ソースS´、ボディB及びドレインD´はシリコンのような半導体材料で形成される。ゲートG´は多結晶シリコンのような導電性材料からなり、典型的には二酸化シリコンのような絶縁層により、その半導体材料から分離される。通常動作時には、ゲート酸化層を保護するために、Vccは最大ゲート−ソース間電圧VGS(max)の超えることのないように設定される。VccがVGS(max)より大きくなると、ゲート酸化層が破壊されるか、そこまでに至らなくても損傷してしまい、MOSFET10が復旧不可能に破壊されてしまう。

【0004】

VGS(max)は一般にゲート酸化層の厚さ(XOX)により決定される。一般に、VGSが約10〜12(MV)×XOX(cm)より大きくなる場合、ゲート酸化膜が破壊されることになる。ゲート酸化膜が厚い(例えば300オングストローム厚)である場合、ゲートと半導体材料との間の通り抜け(トンネル作用)の結果である漏れ電流が小さいため、この係数は実際には小さくなる(例えば8MV/cm)。トンネル作用はゲート酸化膜を損傷することはない。従って50%の安全率を見込むと、VGSは通常、5或いは6MV/cm×XOX未満に、又はゲート酸化層が厚くても4MV/cm×XOX未満に保持されなければならない。例えば175オングストローム厚の酸化層は16〜18Vで破壊され、VGS(max)は約8〜9Vであるのに対して、300オングストローム厚酸化層は約24Vで破壊され、VGS(max)は約12Vであろう。

【0005】

ゲート電圧VGSがよい高い破壊電圧より高くなる場合には、デバイスは瞬時に破壊されるであろう。VGSが破壊電圧とVGS(max)との間の範囲にある場合、そのデバイスは瞬時に破壊されることないが、部分的に損傷を受ける場合がある。ゲート電圧がVGS(max)未満の安全なレベルに戻った場合でも、この潜在する損傷により、結局はゲート酸化層が徐々に破壊され、後にはデバイスが動作しなくなる。このため、VGS(max)と破壊電圧との間のゲート電圧をかけられたMOSFETは、多くの場合「(動作可能だが)損傷を受けている」ものと考えられる。

【0006】

静電放電(ESD)から生じる電圧が種々の状況で存在する。ESD電圧は非常に高電圧であるが、非常に短期間しか持続しないため、図1Bに示されるように、直列に抵抗Resdが接続された数千V(例えば図1Bに示されるように2kV以上)に帯電したコンデンサDesdとして図式化される場合が多い。Desdの相対的な大きさ、MOSFET10のゲート容量及びResdの大きさにより、Cesdが小さく(すなわちESDパルスが短く)、Resd及びゲート容量が大きい場合には、MOSFET10は損傷を受けずにESDパルスに耐えることができる。この場合にはゲートを流れる電流はResdにより制限され、ESDパルスに関連するエネルギーが散逸してしまう前に、VGSの立ち上がりが危険なレベルに達するのを防ぐ。本質的には、Cesd、Resd及びゲート容量は分圧回路を形成する。

【0007】

ドレイン上に発生するESDパルス或いは他の高電圧は一般には問題ではないが、それは半導体材料の空乏領域の広がりがドレイン−ゲート間の大部分の電圧を吸収し、それによりゲート酸化膜に全ドレイン電圧がかからないためである。

【0008】

図2はいくつかの状況においてMOSFETにかけられるVGSのグラフである。デバイスは5Vの標準ゲート駆動電圧用に設計されており、破壊電圧8Vが許容される。VGSが正負いずれかの方向に8Vを超える場合に、12Vの過電圧状態が生じる。これらの状態はバッテリ充電器の電圧のリンギングにより生じるか、或いは不良のバッテリ充電器に差し込まれる際に生じる。これらの電圧は比較的長時間に渡るため、ゲート電圧をクランプするために用いられるダイオードを燃やしてしまうこともできる。最終的に、そのデバイスには、正負いずれかの2000VのESDパルスがかけられる。しかしながらESDパルスは極く短時間であるため、ダイオードクランプがその電圧に耐えることができる。

【0009】

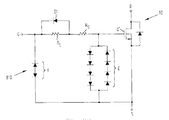

図3A及び図3Bは、それぞれMOSFET32及び34のゲートを保護するために電圧クランプ31及び33を備えるリチウムイオンバッテリバック30の回路図である。MOSFET32及び34はリチウムイオンバッテリからの電流を切替え、ドレイン−ドレイン接続構成で直列に接続される。MOSFET32及び34のゲート電圧は制御IC36により制御される。電圧クランプ31及び33は、一対の逆向き接続のダイオードからなるものとして示される。図3Aは、バッテリパック30の端子に12,000VのESDパルスがかけられる場合を示す。ESDパルスが発生する際にそのデバイスがオン状態である場合には、12,000Vのパルスがバッテリパック30のデバイス間に分散され、そのうちのある量がMOSFET32及び34のゲート−ソース端子間に現れるようになる。

【0010】

しかしながら図3Bに示されるように、12VのDC過電圧がかけられる場合には、制御IC36が全12Vに耐え、MOSFET32及び34のゲート上に全12Vをかける。例えば電圧クランプ31及び33が8V、すなわちMOSFET32及び34の定格動作電圧でブレークダウンするように設計されているものと仮定すると、電圧クランプ内のダイオードは、おそらく過大な電流が流れ、焼けてしまうであろう。

【0011】

本発明が一部継続出願となっており、参照して本明細書の一部としている1997年12月31日出願の特許出願第09/001,768号は、ゲート酸化膜を保護するために電圧クランプとして用いることができるいくつかのダイオード構成を記載している。

【0012】

【発明が解決しようとする課題】

MOSFETのゲート酸化膜が損傷するのを防ぐために、MOSFETのゲート−ソース間に過大な電圧がかかる場合でも電圧を制限することができるクランプを有するMOSFETを提供する。

【0013】

【課題を解決するための手段】

本発明に従えば、MOSFETのソース−ゲート間に1つ以上のダイオードが接続される。標準の動作状態では、ダイオードは導通せず、開回路状態となっている。しかしながらゲート−ソース間電圧が所定のレベルを超える場合には、ダイオードがブレークダウンし(或いは電流が順方向に流れ)、それにより所定の最大レベルにゲート電圧をクランプする。

【0014】

本発明により種々の実施例を実現可能である。例えば複数対の逆向きダイオード(すなわちアノードとアノード或いはカソードとカソードを接続されたダイオード)がゲート−ソース間に直列に接続され、正負両方の電圧スパイクからゲート酸化膜を保護する。MOSFETセルのゲートと、パワーMOSFETのゲート端子或いはパッドとの間に抵抗が接続され、ブレークダウン状態でもダイオード対を流れる電流を制限する。さらに逆向きのダイオード対が、第2の電圧クランプとしてゲート−ソースパッド間に接続され、第1のグループのダイオード対を保護することができる。

【0015】

別法では、ゲート−ソース間に接続される逆向きダイオード対の代わりに、並列のダイオード回路網がを用いることができる。並列ダイオード回路網の各ブランチは、同じ向きの数個のダイオード(すなわちカソード−アノード接続)を備えており、各ブランチのダイオードは他のブランチのダイオードとは逆向きになっている。この実施例は特に薄いゲート酸化膜の場合に有用であるが、それはVGSが、ダイオード間の順方向電圧降下の和に等しい電圧でクランプされるためである。各順方向電圧降下は典型的には0.6V〜0.8Vの範囲にある。この回路網を、上記のような抵抗及びソース−ゲートパッド間に接続される複数の逆向きダイオード対とともに用いることができる。ゲート電圧が標準時にソース電圧に対して一方向のみ(正或いは負)向いているなら、並列回路網の一ブランチはその中に1つのダイオードのみを備えるだけでよく、ゲート電圧は非動作方向に一段の順方向ダイオード降下でクランプされる。

【0016】

別の一群の実施例では、並列に接続された抵抗及びダイオードが、ゲートパッド或いは端子とMOSFETのゲートとの間の経路において上記の電流制限抵抗と直列に接続される。NチャネルMOSFETの場合、このダイオードは、アノードがMOSFETのゲートに面して、カソードがゲートパッド或いは端子に面して接続される。この配列により、MOSFETはターンオンより速くターンオフすることができるが、それはゲートがMOSFETをターンオフするために低電圧で駆動される際に、ダイオードが順方向にバイアスされ、並列に接続された抵抗を実際にはバイパスして電流を流すためである。PチャネルMOSFETの場合、このダイオードは、アノードがゲートパッド或いは端子に面して、カソードがMOSFETのゲートに面して接続される。MOSFETのターンオフ時間に比べてターンオン時間が相対的に遅くなるため、ターンオン時間が遅いことにより、回路内にインダクタンスが存在する場合に生じるようになるリンギング及びオーバーシュートが避けられる点で有利である。

【0017】

本発明の原理は以下に記載する図面を参照すれば理解が進むであろう。同様の構成要素には同じ参照番号を付与している。

【0018】

【発明の実施の形態】

図4は、電圧クランプ402により保護されたゲートG´を有するMOSFET10の回路図である。MOSFET10のソース、ドレイン及びゲート端子或いはパッドは、デバイスの内部領域と区別するためにそれぞれS、D及びGと表記される。電圧クランプ402は、n対の逆向きダイオードの直列のスタック、すなわちアノード−アノード接続ダイオード対を備えているが、カソード−カソード接続ダイオードであってもよい。逆向きダイオード対はMOSFET10のゲートG´−ソースS´間に接続される。各ダイオードの逆方向ブレークダウン電圧は典型的には4.5〜7.7Vの範囲内にあり、PNダイオードの順方向電圧降下は0.6〜0.7Vの範囲内にあるため、各逆向きダイオード対は約5〜8V、典型的には6.5或いは7.0Vの電圧でブレークダウンするであろう。例えば電圧クランプ402が、それぞれ6.5Vのブレークダウン電圧を有する2つのダイオード対を備えるものと仮定すると、ゲートG´は約13Vでクランプされることになる。クランプ電圧は、個々のダイオードのブレークダウン特性及び直列接続ダイオード対の数を調整することにより変更される。

【0019】

電圧クランプ402の動作が図9に示されており、横軸はMV/cm(ゲート酸化膜厚)で表したゲートG−ソースS間の電界EGSを、また縦軸は電圧クランプを流れる電流IGを表す。縦方向の破線は、上記のような安全動作領域、潜在的な損傷領域及び瞬時破壊領域の間の境界線である。括弧内の数字は、175オングストローム厚ゲート酸化層の場合の電圧の代表値を示す。この実施例では、電圧クランプ402のダイオード対は±8Vでブレークダウンするように設計されており、その電圧は潜在的な損傷が生じ始める電圧である。MOSFETは、EGSが約±17Vに達すると破壊されてしまう。

【0020】

一旦電圧クランプがブレークダウンすると、逆向きダイオード対内を電流が流れる。電流が十分に大きく、長時間に渡る場合には、ダイオードが焼けてしまうであろう。さらにブレークダウン電圧は、可能な限り所望のレベル(この場合には8V)に近くなるように設定されるべきである。ブレークダウン電圧がそのレベルより非常に小さい場合には、電圧クランプは良好に保護動作するが、ゲート電圧の動作範囲は制限されることになる。ブレークダウン電圧がその所望のレベルより非常に高い場合には、ゲート酸化層は潜在的な損傷を受ける危険性がある。これらの問題は、図5に示される電圧クランプ404を用いる場合に緩和される。電圧クランプ404は内側ブランチ406を備えており、ブランチ406は、1つのダイオード対として表される、ゲートG´−ソースS´間に直列に接続されたm個の逆向きダイオード対を備えており、また電圧クランプ404は、ゲートパッドG‐ソースパッドS間に接続されたn個の逆向きダイオード対を含む外側ブランチも備えている。電流制限抵抗RがゲートパッドG−ゲートG´間に接続される。

【0021】

電圧クランプ404の動作が図10に示される。電圧クランプ402の場合と同様に、ブランチ406のダイオード対は4〜5MV/cmでブレークダウンし、この場合にはそれは約7Vである。しかしながらここより高い電圧では、抵抗Rがダイオード対を流れる電流を制限し、ダイオード対が焼けるのを防ぐ。電流は約1/Rの割合で増加するが、その間ゲート電圧はまだ7Vにクランプされている。抵抗R及びダイオード対は、ゲートパッドG−ソースパッドS間で概ね分圧回路として動作する。この状況は、通常瞬時破壊が生じると思われる領域まで続く。ゲートパッド−ソースパッド間電圧が、外側ブランチ408のダイオード対のブレークダウン電圧を超えた場合にのみ、電流が急激に増加し始める。その場合でも、外側ブランチ408のダイオードは焼けてしまう場合があるが、ゲート酸化膜は保護される。

【0022】

図13及び図14は、図10を補足する測定データを示す。電流制限抵抗は1.8kΩに設定された。図のように、内側ダイオードは約7Vでブレークダウンし、その後外側ダイオードが約14Vでブレークダウンするまで電流が線形に増加すいる。その時点で、ゲートパッド−ソースパッド間の合成電流が急激に増加し始める。

【0023】

逆向きダイオード対を用いると、約5Vより非常に低いブレークダウン電圧を得ることが難しく、この電圧では非常に薄いゲート酸化層には高いすぎる場合がある。図6に示される電圧クランプ410は並列のダイオード回路網を含んでおり、2つの各ブランチ412A及び412B内のダイオードは同じ方向を向いているが、ブランチ412Aのダイオードはブランチ412Bのダイオードとは反対向きである。従ってクランプ電圧は、各ブランチのダイオード間の順方向電圧降下の和である。図11に示されるように、各ブランチにz個のダイオードがあり、各ダイオードが順方向ブレークダウン電圧Vfを有するものと仮定すると、ゲートはz・Vfでクランプされる。各ダイオード間の順方向電圧降下が1.2Vの場合には、例えば4個のダイオードが約5Vの全クランプ電圧を与え、それは薄いゲート酸化層の場合に4MV/cmと同等である。並列に配置されているため、ゲート−ソース間の電圧が正か負かの違いはあるが、クランプは同様に動作する(第1象限或いは第3象限の動作)。

【0024】

図7に示される電圧クランプ416は、図6に示される種類の並列ダイオード回路網を、図5に示されるように外側ブランチ408と組み合わせたものである。図12に示されるように、並列ダイオード回路網がz・Vfでブレークダウンした後、電圧が外側ブランチ416の逆向きダイオード対がブレークダウンする電圧に達するまで、電流は1/Rの割合で増加する。外側ブランチ416の逆向きダイオードが一対であるものと仮定すると、外側ブランチのブレークダウン電圧は5.5Vであるが、さらにダイオード対を増やせばブレークダウン電圧は高くすることができる。

【0025】

ある場合には、動作中のゲート電圧は常にソース電圧に対して正か負である。その場合図8に示される種類の電圧クランプを用いることができる。電圧クランプ420は一方に向いた4個のダイオードと他方を向いた1個のダイオードとを並列に組み合わせたものを含む。ブランチ424の1個のダイオードは、ゲート電圧がソース電圧より1個分の順方向降下電圧だけ低くなる場合に、クランプすることになる。従って電圧クランプ420は、ゲート電圧が通常ソース電圧より低くならない場合に特に有効である。

【0026】

従って広範な態様においては、本発明による電圧クランプはMOSFETのゲート−ソース端子間に接続された1つ以上の並列ブランチを含む。各ブランチは少なくとも1個のダイオードを含み、多くの場合には所望のクランプ電圧に応じて、ゲート−ソース間電圧が所定のレベルに達する際に、ダイオードがブレークダウンするか、或いは順方向に導通するように接続された一連のダイオードを含む。

【0027】

より低いクランプ電圧を実現するためには、ダイオードは典型的には順方向に導通するように接続され、より高いクランプ電圧を実現するためには、ダイオードはアバランシェブレークダウンを生じるように接続される。多数の例では、所与のブランチは、所望のクランプ電圧を得るために、種々の方向に接続された(例えばアノード−アノード接続のダイオード対)ダイオードを含む。2つ以上のブランチを用いる場合には、一方のブランチのダイオードは他方のブランチのダイオードより低いクランプ電圧を与える。ダイオードを流れる電流の量を制限し、それによりダイオードが急激な電流により焼けてしまうのを防ぐために、低いクランプ電圧を与えるダイオードと直列に抵抗を接続することができる。あるブランチのダイオードは一方にゲート電圧が振れることからゲート酸化層を保護し、他方のダイオードは別の方向に電圧が振れることからゲート酸化層を保護することができる。

【0028】

一般に、上記の電圧クランプに用いられるダイオードはできるだけ高レベルにドープされ、ダイオードがブレークダウンする際に可能な限り低い抵抗を与えるべきである。しかしながらダイオードのドーピングが高すぎる場合、ダイオードが多数の欠陥を有するようになるため、ダイオードに逆方向バイアスがかかる際に漏れが非常の大きくなる傾向がある。漏れ電流は、ダイオードが高温になる際に特に大きくなる。

【0029】

図15及び図16はこれらの変数間の関係を示すグラフである。図15では、横軸はP領域のドーピング濃度を表す。BVを付された曲線はダイオードのブレークダウン電圧を表しており、その目盛りは左側になっている。I漏れを付された曲線は漏れ電流を表しており、Pポリシートρを付された曲線はシート抵抗を表しており、その両変数の目盛りは右側である。予想されるように、ブレークダウン電圧及びシート抵抗はドーピング濃度の増加ととも減少するが、一方漏れ電流は増加する。図16のグラフは、ブレークダウン電圧の関数として、漏れ電流(左軸)及びシート抵抗(右軸)を示す。

【0030】

図17に示される電圧クランプ800は電圧クランプ404(図5)と同様であるが、高抵抗RL及び低抵抗RSがゲートパッドGとゲートG´との間に直列に接続され、ダイオードD1がRLと並列に接続されている点が異なる。ゲート電圧が高位側に引っ張られ、MOSFET10がターンオンする際に、ダイオードD1には逆方向バイアスがかかり、ゲートG´に流れ込む全電流は抵抗RL及び抵抗RSの両方を通って流れなければならない。しかしながらゲート電圧が再び低位側に引っ張られ、MOSFET10がターンオフする際には、ダイオードD1には順方向バイアスがかかり、電流は高抵抗RLを迂回して分流される。RLの抵抗は50kΩ〜2MΩの範囲内にし、RSの抵抗は25Ω〜1kΩの範囲内にすることができる。

【0031】

この動作は図21A、図21B及び図21Cに示されており、それは時間の関数として、ゲートパッドGの電圧(VGS)、ゲートG´の電圧(VGS´)、ソース−ドレイン間電圧(VDS)及びドレイン電流IDを示している。時間t1では、階段関数VGSが加わる際に、VGS´が、概ね高抵抗RLにより確定される割合で上昇する。従ってVDSはVCCから降下し、IDは、リンギング或いはオーバーシュート(破線で示される)を避ける割合で0から上昇する。安定状態にあるという条件で、VDSはI・RDSに等しい。対照的に時間t2では、VGSが低位側に引っ張られMOSFET10がターンオフする際に、VGSは低抵抗RSにより確定される割合で降下し、VDS及びIDも同様に急激に変動する。

【0032】

図17の電圧クランプ800は、内側ブランチにm個の逆向きダイオード対を、外側ブランチにn個の逆向きダイオード対を含んでおり、それは図5の電圧クランプ404と同様である。種々のターンオン、ターンオフ条件を与える別の実施例が図18−図20に示される。図18の電圧クランプ810は、内側ブランチに並列ダイオード回路網を、外側ブランチにn個の逆向きダイオード対を備え、その点で図7に示される電圧クランプ416と同様である。図19の電圧クランプ820は、n個の逆向きダイオード対を含む外側ブランチとともに、図8の電圧クランプ420と同様の内側ブランチを備える。

【0033】

図20の電圧クランプ830では、低抵抗RSはなくなり、その結果ターンオフ時間が最小になる。一方、ブレークダウン状態では、より多くの電流がクランプダイオードを流れるようになる。

【0034】

上記実施例は例示にすぎず、本発明の幅広い範囲を制限するものと見なされるべきではない。本発明による多数のさらに別の実施例は当業者には明らかであろう。

【0035】

【発明の効果】

上記のように本発明により、MOSFETのゲート−ソース間に過大な電圧がかかる場合でも、並列のダイオード回路網並びに又抵抗を用いた回路をMOSFETのゲート−ソース間に使用することにより、所望のレベルに電圧をクランプしてMOSFETのゲート酸化膜が損傷するのを防ぐことができる。

【図面の簡単な説明】

【図1】A及びBよりなり、Aは従来のパワーMOSFETの模式図であり、BはMOSFETのゲートに静電放電パルスを印加する場合を示す等価回路図である。

【図2】正常な動作状態時、過電圧印加状態時及び静電放電印加状態時のMOSFETのゲート電圧を示すグラフである。

【図3】A及びBよりなり、Aはリチウムイオンバッテリ内のバッテリパックと、バッテリパックが静電放電パルスを印加されている場合に、MOSFETのゲートを保護するために一対のMOSFET及び電圧クランプを備えるスイッチとの回路図であり、Bは不適当なバッテリ充電器がリチウムイオンバッテリに用いられた場合の図3Aと同様の回路図である。

【図4】電圧クランプが、MOSFETのゲート−ソースパッド或いは端子間に直列に接続された複数の逆向きダイオード対を備える本発明による実施例の回路図である。

【図5】MOSFETのゲートとゲートパッド或いは端子間に接続された電流制限抵抗と、MOSFETのゲート−ソースパッド或いは端子間に直列に接続された第2の複数の逆向きダイオード対とを備える実施例の回路図である。

【図6】電圧クランプがMOSFETのゲート−ソースパッド或いは端子間に接続された並列ダイオード回路網を備え、各ブランチのダイオードが同じ方向を向くが、他のブランチではダイオードの向きが反対である実施例の回路図である。

【図7】MOSFETのゲートとゲートパッド或いは端子間に接続された電流制限抵抗と、MOSFETのゲート−ソースパッド或いは端子間に接続された複数の逆向きダイオード対とを組み合わせた図6のクランプの回路図である。

【図8】電圧クランプが、1つのダイオードと並列に接続された複数のダイオードを備える実施例の回路図である。

【図9】図4の実施例の動作を示す電流−電圧グラフである。

【図10】図5の実施例の動作を示す電流−電圧グラフである。

【図11】図6の実施例の動作を示す電流−電圧グラフである。

【図12】図7の実施例の動作を示す電流−電圧グラフである。

【図13】図5の実施例の動作を示す実験的に導かれた電流−電圧グラフである。

【図14】図13と同じデータであるが、電流レベルが高い場合のグラフである。

【図15】P領域のドーパント濃度の関数としてPNダイオードのブレークダウン電圧、漏れ電流及び抵抗を示すグラフである。

【図16】ブレークダウン電圧の関数としてPNダイオードの漏れ電流及び抵抗を示すグラフである。

【図17】電圧クランプがMOSFETのゲートパッド或いは端子とゲートとの間に並列に接続されたダイオード及び抵抗を備える場合の図5、図6及び図8に示されるものと同様の実施例の回路図である。

【図18】電圧クランプがMOSFETのゲートパッド或いは端子とゲートとの間に並列に接続されたダイオード及び抵抗を備える場合の図5、図6及び図8に示されるものと同様の実施例の回路図である。

【図19】電圧クランプがMOSFETのゲートパッド或いは端子とゲートとの間に並列に接続されたダイオード及び抵抗を備える場合の図5、図6及び図8に示されるものと同様の実施例の回路図である。

【図20】電圧クランプがMOSFETのゲートパッド或いは端子とゲートとの間に並列に接続されたダイオード及び抵抗を備える場合の図5、図6及び図8に示されるものと同様の実施例の回路図である。

【図21】A乃至Cよりなり、図17−図20に示される実施例とは異なるターンオン特性、ターンオフ特性を示すタイミング図である。

【符号の説明】

10 パワーMOSFET

11 寄生ダイオード

12 バッファ増幅器

30 リチウムイオンバッテリバック

31 電圧クランプ

32 MOSFET

33 電圧クランプ

34 MOSFET

35 バッテリ

36 制御IC

402 電圧クランプ

404 電圧クランプ

406 ブランチ

408 ブランチ

410 電圧クランプ

412A、B ブランチ

416 電圧クランプ

420 電圧クランプ

422 ブランチ

424 ブランチ

800 電圧クランプ

810 電圧クランプ

820 電圧クランプ

830 電圧クランプ

Claims (11)

- ソース、ドレイン及びゲートを備えるMOSFETであって、

前記ソースが絶縁層により前記ゲートから分離されており、ゲート端子が前記ゲートに接続され、かつソース端子が前記ソースに接続されており、

前記MOSFETがさらに、

前記ゲートと前記ゲート端子との間に接続される抵抗と、

前記ゲートと前記抵抗との間のゲートライン第1部分と、前記ソースとの間に接続される第1の電圧クランプと、

前記ゲート端子と前記抵抗との間のゲートライン第2部分と、前記ソース端子との間に接続される第2の電圧クランプとを備え、

前記第1の電圧クランプが、少なくとも1つの第1のダイオードを備え、前記第2の電圧クランプが、少なくとも1つの第2のダイオードを備え、

前記第1及び第2の電圧クランプが、前記ソースにおける第1の電圧と前記ゲートにおける第2の電圧との間の差を、前記絶縁層に損傷が生じるのを防ぐように所定のクランプ電圧に制限し、前記第1の電圧クランプが、前記第2の電圧クランプよりも低いクランプ電圧を有することを特徴とするMOSFET。 - 前記ソース、前記ドレイン、前記ゲート、前記抵抗及び前記第1及び第2の電圧クランプが1つの集積回路ダイに形成されることを特徴とする請求項1に記載のMOSFET。

- 前記ダイオードが、P型不純物をドープされた領域とN型不純物をドープされた領域との間の接合部を有することを特徴とする請求項1に記載のMOSFET。

- 前記ゲートと前記ゲート端子との間に前記抵抗に直列に接続される第2の抵抗をさらに備えることを特徴とする請求項1に記載のMOSFET。

- 前記第1の電圧クランプが、直列にアノード−アノード接続された前記第1のダイオードを備え、前記第2の電圧クランプが、直列にアノード−アノード接続された前記第2のダイオードを備えることを特徴とする請求項1に記載のMOSFET。

- 前記第1の電圧クランプが、直列にアノード−カソード接続された前記第1のダイオードを備え、前記第2の電圧クランプが、直列にアノード−カソード接続された前記第2のダイオードを備えることを特徴とする請求項1に記載のMOSFET。

- 前記第1の電圧クランプが、直列に複数のダイオードが接続された前記第1のダイオードを備え、前記第2の電圧クランプが、直列に複数のダイオードが接続された前記第2のダイオードを備えることを特徴とする請求項1乃至6の何れかに記載のMOSFET。

- 前記第1の電圧クランプが、第1及び第2のブランチを有する並列回路網を備え、前記第1のブランチが第1の複数のダイオードを備え、前記第1の複数のダイオードがそれぞれ、前記ソースと前記ゲートとの間で同じ方向を向いていることを特徴とする請求項1に記載のMOSFET。

- 前記第2のブランチが第2の複数のダイオードを備え、前記第2の複数のダイオードがそれぞれ、前記ソースと前記ゲートとの間で、前記第1の複数のダイオードの向きとは反対の方向を向いていることを特徴とする請求項8に記載のMOSFET。

- 前記第2のブランチが1個のダイオードのみを含み、前記1個のダイオードが、前記ソースと前記ゲートとの間で、前記第1の複数のダイオードの向きとは反対の方向を向いていることを特徴とする請求項8に記載のMOSFET。

- 前記第1のブランチが、前記ソースと前記ゲートとの間で、前記第1の複数のダイオードとは反対の方向を向いた少なくとも1つの追加のダイオードを含むことを特徴とする請求項8若しくは9に記載のMOSFET。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/306003 | 1999-05-05 | ||

| US09/306,003 US6172383B1 (en) | 1997-12-31 | 1999-05-05 | Power MOSFET having voltage-clamped gate |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009158635A Division JP5178649B2 (ja) | 1999-05-05 | 2009-07-03 | 電圧クランプされたゲートを備えるパワーmosfet |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000349235A JP2000349235A (ja) | 2000-12-15 |

| JP2000349235A5 JP2000349235A5 (ja) | 2007-05-31 |

| JP4369009B2 true JP4369009B2 (ja) | 2009-11-18 |

Family

ID=23183305

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000107465A Expired - Fee Related JP4369009B2 (ja) | 1999-05-05 | 2000-04-10 | 電圧クランプされたゲートを備えるパワーmosfet |

| JP2009158635A Expired - Lifetime JP5178649B2 (ja) | 1999-05-05 | 2009-07-03 | 電圧クランプされたゲートを備えるパワーmosfet |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009158635A Expired - Lifetime JP5178649B2 (ja) | 1999-05-05 | 2009-07-03 | 電圧クランプされたゲートを備えるパワーmosfet |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6172383B1 (ja) |

| EP (1) | EP1063757B1 (ja) |

| JP (2) | JP4369009B2 (ja) |

| KR (1) | KR100625916B1 (ja) |

| DE (1) | DE60009214T2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10636728B2 (en) | 2017-03-24 | 2020-04-28 | Kabushiki Kaisha Toshiba | Semiconductor device |

Families Citing this family (68)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3564958B2 (ja) | 1997-08-07 | 2004-09-15 | 株式会社日立製作所 | 電子ビームを用いた検査方法及び検査装置 |

| JP2000022456A (ja) * | 1998-06-26 | 2000-01-21 | Nec Ic Microcomput Syst Ltd | 半導体集積回路 |

| US6249410B1 (en) * | 1999-08-23 | 2001-06-19 | Taiwan Semiconductor Manufacturing Company | ESD protection circuit without overstress gate-driven effect |

| KR100794151B1 (ko) * | 2000-05-22 | 2008-01-14 | 소니 가부시끼 가이샤 | 전계 효과 트랜지스터의 보호 회로 및 반도체 장치 |

| JP4846106B2 (ja) * | 2001-02-16 | 2011-12-28 | 三菱電機株式会社 | 電界効果型半導体装置及びその製造方法 |

| JP4641660B2 (ja) * | 2001-05-18 | 2011-03-02 | 三菱電機株式会社 | レベルシフト回路 |

| US6798629B1 (en) * | 2001-06-15 | 2004-09-28 | Integrated Device Technology, Inc. | Overvoltage protection circuits that utilize capacitively bootstrapped variable voltages |

| JP2003243512A (ja) * | 2002-02-14 | 2003-08-29 | Hitachi Ltd | 静電破壊保護回路 |

| US20030189215A1 (en) | 2002-04-09 | 2003-10-09 | Jong-Lam Lee | Method of fabricating vertical structure leds |

| US7075763B2 (en) * | 2002-10-31 | 2006-07-11 | Micron Technology, Inc. | Methods, circuits, and applications using a resistor and a Schottky diode |

| AU2003285650A1 (en) * | 2002-12-20 | 2004-07-14 | Koninklijke Philips Electronics N.V. | Power factor controller utilizing duel-switch configuration |

| US6906386B2 (en) | 2002-12-20 | 2005-06-14 | Advanced Analogic Technologies, Inc. | Testable electrostatic discharge protection circuits |

| CN1745477A (zh) * | 2002-12-20 | 2006-03-08 | 先进模拟科技公司 | 可测试静电放电保护电路 |

| US6897707B2 (en) * | 2003-06-11 | 2005-05-24 | Northrop Grumman Corporation | Isolated FET drive utilizing Zener diode based systems, methods and apparatus |

| US7675726B2 (en) * | 2003-07-28 | 2010-03-09 | Siemens Aktiengesellschaft | Device for protecting electronic modules in a multi-voltage on-board electrical system against short circuits |

| JP2005142363A (ja) * | 2003-11-06 | 2005-06-02 | Toshiba Corp | 半導体集積回路 |

| JP2005175054A (ja) * | 2003-12-09 | 2005-06-30 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| EP1624570A1 (en) * | 2004-08-03 | 2006-02-08 | Freescale Semiconductor Inc. (A Delaware Corp) | A semiconductor switch arrangement |

| JP2007049012A (ja) * | 2005-08-11 | 2007-02-22 | Nec Electronics Corp | 半導体装置 |

| US7545614B2 (en) * | 2005-09-30 | 2009-06-09 | Renesas Technology America, Inc. | Electrostatic discharge device with variable on time |

| KR20080085226A (ko) * | 2006-02-17 | 2008-09-23 | 엔엑스피 비 브이 | 집적 반도체 디바이스를 보호하기 위한 회로 장치, 집적 회로 소자 및 그 제조 방법 |

| JP2008042950A (ja) * | 2006-08-01 | 2008-02-21 | Mitsubishi Electric Corp | 電力変換装置 |

| US8476709B2 (en) * | 2006-08-24 | 2013-07-02 | Infineon Technologies Ag | ESD protection device and method |

| US8144441B2 (en) | 2006-08-30 | 2012-03-27 | Triquint Semiconductor, Inc. | Electrostatic discharge protection circuit for compound semiconductor devices and circuits |

| TWI496272B (zh) | 2006-09-29 | 2015-08-11 | Fairchild Semiconductor | 用於功率金氧半導體場效電晶體之雙電壓多晶矽二極體靜電放電電路 |

| JP4427561B2 (ja) * | 2007-05-29 | 2010-03-10 | 株式会社東芝 | 半導体装置 |

| KR101014152B1 (ko) | 2008-10-15 | 2011-02-14 | 기아자동차주식회사 | 차량 인버터 회로 및 그를 이용한 차량 |

| US9142592B2 (en) | 2009-04-09 | 2015-09-22 | Infineon Technologies Ag | Integrated circuit including ESD device |

| WO2011093472A1 (ja) | 2010-01-29 | 2011-08-04 | 富士電機システムズ株式会社 | 半導体装置 |

| US8614480B2 (en) * | 2011-07-05 | 2013-12-24 | Texas Instruments Incorporated | Power MOSFET with integrated gate resistor and diode-connected MOSFET |

| KR101818537B1 (ko) * | 2011-07-14 | 2018-01-15 | 현대모비스 주식회사 | Mosfet 보호 회로 및 방법 |

| KR101799017B1 (ko) | 2011-08-18 | 2017-11-20 | 에스케이하이닉스 주식회사 | 전압 안정화 회로를 구비한 반도체 집적 회로 |

| DE102012014860A1 (de) | 2012-07-26 | 2014-05-15 | Infineon Technologies Ag | ESD-Schutz |

| JP2014045004A (ja) * | 2012-08-24 | 2014-03-13 | Samsung Electro-Mechanics Co Ltd | Esd保護回路及び電子機器 |

| EP2736171A1 (en) * | 2012-11-23 | 2014-05-28 | Nxp B.V. | Cascoded semiconductor devices |

| JP5729371B2 (ja) * | 2012-12-27 | 2015-06-03 | 富士電機株式会社 | 半導体装置 |

| US9966584B2 (en) | 2013-03-11 | 2018-05-08 | Atieva, Inc. | Bus bar for battery packs |

| US10901019B2 (en) | 2013-03-15 | 2021-01-26 | Atieva, Inc. | Method of connecting cell voltage sensors |

| US10063071B2 (en) | 2013-03-15 | 2018-08-28 | Atieva, Inc. | Balance resistor and low pass filter |

| US10084214B2 (en) | 2013-03-15 | 2018-09-25 | Atieva, Inc. | Automatic switchover from cell voltage to interconnect voltage monitoring |

| US9041454B2 (en) | 2013-03-15 | 2015-05-26 | Atieva, Inc. | Bias circuit for a switched capacitor level shifter |

| CN103347330B (zh) * | 2013-06-22 | 2015-04-08 | 潍坊晶兰电源技术有限公司 | 一种led驱动控制电路 |

| CN103347329B (zh) * | 2013-06-22 | 2015-04-08 | 潍坊晶兰电源技术有限公司 | 一种led驱动电路 |

| CN103347331A (zh) * | 2013-06-22 | 2013-10-09 | 潍坊晶兰电源技术有限公司 | 一种驱动芯片保护电路 |

| JP2015015643A (ja) * | 2013-07-05 | 2015-01-22 | ローム株式会社 | 信号伝達回路 |

| TWI502836B (zh) * | 2013-08-05 | 2015-10-01 | Ind Tech Res Inst | 電壓保護傳輸裝置及包括該裝置的電壓保護裝置 |

| JP5741666B2 (ja) * | 2013-10-30 | 2015-07-01 | 富士電機株式会社 | 半導体装置 |

| JP6364758B2 (ja) * | 2013-12-04 | 2018-08-01 | オムロン株式会社 | 全波整流回路 |

| US9640972B2 (en) * | 2014-03-26 | 2017-05-02 | Infineon Technologies Ag | Controlled switch-off of a power switch |

| JP6256320B2 (ja) * | 2014-11-28 | 2018-01-10 | 三菱電機株式会社 | Esd保護回路及びrfスイッチ |

| CN104538395B (zh) * | 2015-01-08 | 2019-01-25 | 电子科技大学 | 一种功率vdmos器件二极管并联式esd防护机构 |

| CN104505390B (zh) * | 2015-01-08 | 2019-03-15 | 电子科技大学 | 集成式二极管链功率mos防静电保护结构 |

| JP2016201069A (ja) * | 2015-04-14 | 2016-12-01 | 富士通セミコンダクター株式会社 | 整流回路、電源回路及びrfidタグ |

| DE102015212152B4 (de) | 2015-06-30 | 2018-03-15 | TRUMPF Hüttinger GmbH + Co. KG | Nicht lineare Hochfrequenzverstärkeranordnung |

| DE102015212247A1 (de) | 2015-06-30 | 2017-01-05 | TRUMPF Hüttinger GmbH + Co. KG | Hochfrequenzverstärkeranordnung |

| TWI627822B (zh) * | 2016-11-09 | 2018-06-21 | 致茂電子股份有限公司 | 鉗位控制電路 |

| CN110178298B (zh) * | 2016-12-29 | 2021-03-09 | 斯堪的诺维亚系统公司 | 电脉冲发生模块与储存电容器、续流二极管和在充电期间复位的变压器 |

| KR101916795B1 (ko) | 2017-06-22 | 2018-11-08 | 현대오트론 주식회사 | 스위치드 릴럭턴스 모터를 갖는 모터 시스템 및 그것의 동작 방법 |

| US10897246B2 (en) * | 2017-11-10 | 2021-01-19 | Qorvo Us, Inc. | Radio frequency switching circuitry with reduced switching time |

| CN107834824B (zh) * | 2017-12-12 | 2024-02-27 | 深圳市禾望电气股份有限公司 | 一种功率开关管驱动电路 |

| JP7155534B2 (ja) * | 2018-02-16 | 2022-10-19 | 富士電機株式会社 | 半導体装置 |

| FR3079348B1 (fr) * | 2018-03-22 | 2023-08-11 | St Microelectronics Tours Sas | Circuit de protection contre les décharges électrostatiques |

| TWI729538B (zh) | 2018-11-21 | 2021-06-01 | 大陸商上海瀚薪科技有限公司 | 一種整合箝制電壓箝位電路的碳化矽半導體元件 |

| US11387648B2 (en) | 2019-01-10 | 2022-07-12 | Analog Devices International Unlimited Company | Electrical overstress protection with low leakage current for high voltage tolerant high speed interfaces |

| US11579645B2 (en) | 2019-06-21 | 2023-02-14 | Wolfspeed, Inc. | Device design for short-circuitry protection circuitry within transistors |

| US11410990B1 (en) | 2020-08-25 | 2022-08-09 | Semiq Incorporated | Silicon carbide MOSFET with optional asymmetric gate clamp |

| JP2023032984A (ja) * | 2021-08-27 | 2023-03-09 | 富士電機株式会社 | 半導体モジュール |

| CN115831956A (zh) * | 2021-09-17 | 2023-03-21 | 中兴光电子技术有限公司 | 一种静电释放保护电路、保护单元以及芯片和装置 |

Family Cites Families (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3967295A (en) | 1975-04-03 | 1976-06-29 | Rca Corporation | Input transient protection for integrated circuit element |

| JPS5825264A (ja) | 1981-08-07 | 1983-02-15 | Hitachi Ltd | 絶縁ゲート型半導体装置 |

| US4757363A (en) | 1984-09-14 | 1988-07-12 | Harris Corporation | ESD protection network for IGFET circuits with SCR prevention guard rings |

| FR2587157B1 (fr) | 1985-09-06 | 1987-11-20 | Thomson Csf | Dispositif de commutation de tension |

| JPH0693485B2 (ja) | 1985-11-29 | 1994-11-16 | 日本電装株式会社 | 半導体装置 |

| JP2724146B2 (ja) | 1987-05-29 | 1998-03-09 | 日産自動車株式会社 | 縦形mosfet |

| JPH02185069A (ja) | 1988-12-02 | 1990-07-19 | Motorola Inc | 高エネルギー阻止能力及び温度補償された阻止電圧を具備する半導体デバイス |

| US5119162A (en) | 1989-02-10 | 1992-06-02 | Texas Instruments Incorporated | Integrated power DMOS circuit with protection diode |

| US5274274A (en) | 1992-03-23 | 1993-12-28 | Power Integrations, Inc. | Dual threshold differential discriminator |

| US5504449A (en) | 1992-04-09 | 1996-04-02 | Harris Corporation | Power driver circuit |

| US5397914A (en) | 1992-04-30 | 1995-03-14 | Hitachi Ltd. | Power transistor device including power transistors in darlington connection and zener diode which is coupled between collector and base of power transistors and which is formed in polysilicon film |

| US5439842A (en) | 1992-09-21 | 1995-08-08 | Siliconix Incorporated | Low temperature oxide layer over field implant mask |

| US5525925A (en) | 1992-09-25 | 1996-06-11 | Texas Instruments Incorporated | Simple power MOSFET low side driver switch-off circuit with limited di/dt and fast response |

| EP0601823B1 (en) | 1992-12-09 | 2000-10-11 | Compaq Computer Corporation | Method of forming a field effect transistor with integrated schottky diode clamp |

| EP0631390B1 (en) * | 1993-06-22 | 1999-09-01 | Philips Electronics Uk Limited | A power semiconductor circuit |

| GB9313651D0 (en) * | 1993-07-01 | 1993-08-18 | Philips Electronics Uk Ltd | A semiconductor device |

| EP0646964B1 (en) | 1993-09-30 | 1999-12-15 | Consorzio per la Ricerca sulla Microelettronica nel Mezzogiorno | Integrated structure active clamp for the protection of power devices against overvoltages, and manufacturing process thereof |

| US5510747A (en) | 1993-11-30 | 1996-04-23 | Siliconix Incorporated | Gate drive technique for a bidirectional blocking lateral MOSFET |

| JP2792417B2 (ja) * | 1993-12-17 | 1998-09-03 | 日本電気株式会社 | 半導体回路の入力保護回路 |

| US5946588A (en) | 1994-12-07 | 1999-08-31 | Micron Technology, Inc. | Low temperature sub-atmospheric ozone oxidation process for making thin gate oxides |

| JP3485655B2 (ja) | 1994-12-14 | 2004-01-13 | 株式会社ルネサステクノロジ | 複合型mosfet |

| JPH08172188A (ja) * | 1994-12-19 | 1996-07-02 | Kawasaki Steel Corp | 半導体装置 |

| US5805123A (en) | 1995-03-16 | 1998-09-08 | Texas Instruments Incorporated | Display panel driving circuit having an integrated circuit portion and a high power portion attached to the integrated circuit |

| US5661322A (en) | 1995-06-02 | 1997-08-26 | Siliconix Incorporated | Bidirectional blocking accumulation-mode trench power MOSFET |

| DE69617098T2 (de) | 1995-06-02 | 2002-04-18 | Siliconix Inc | Grabengate-Leistungs-MOSFET mit Schutzdioden in periodischer Anordnung |

| US5602046A (en) | 1996-04-12 | 1997-02-11 | National Semiconductor Corporation | Integrated zener diode protection structures and fabrication methods for DMOS power devices |

| US5818084A (en) | 1996-05-15 | 1998-10-06 | Siliconix Incorporated | Pseudo-Schottky diode |

| US5804846A (en) | 1996-05-28 | 1998-09-08 | Harris Corporation | Process for forming a self-aligned raised source/drain MOS device and device therefrom |

| US5811857A (en) | 1996-10-22 | 1998-09-22 | International Business Machines Corporation | Silicon-on-insulator body-coupled gated diode for electrostatic discharge (ESD) and analog applications |

| US5923210A (en) | 1997-05-07 | 1999-07-13 | Caterpillar Inc. | High side driver circuit with diagnostic output |

| JPH11251594A (ja) * | 1997-12-31 | 1999-09-17 | Siliconix Inc | 電圧クランプされたゲ―トを有するパワ―mosfet |

-

1999

- 1999-05-05 US US09/306,003 patent/US6172383B1/en not_active Expired - Lifetime

-

2000

- 2000-04-10 JP JP2000107465A patent/JP4369009B2/ja not_active Expired - Fee Related

- 2000-04-11 DE DE60009214T patent/DE60009214T2/de not_active Expired - Lifetime

- 2000-04-11 EP EP00107746A patent/EP1063757B1/en not_active Expired - Lifetime

- 2000-05-03 KR KR1020000023687A patent/KR100625916B1/ko active IP Right Grant

-

2009

- 2009-07-03 JP JP2009158635A patent/JP5178649B2/ja not_active Expired - Lifetime

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10636728B2 (en) | 2017-03-24 | 2020-04-28 | Kabushiki Kaisha Toshiba | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009224803A (ja) | 2009-10-01 |

| KR100625916B1 (ko) | 2006-09-20 |

| DE60009214T2 (de) | 2005-01-27 |

| EP1063757B1 (en) | 2004-03-24 |

| DE60009214D1 (de) | 2004-04-29 |

| EP1063757A3 (en) | 2001-12-05 |

| JP2000349235A (ja) | 2000-12-15 |

| JP5178649B2 (ja) | 2013-04-10 |

| EP1063757A2 (en) | 2000-12-27 |

| KR20000077143A (ko) | 2000-12-26 |

| US6172383B1 (en) | 2001-01-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4369009B2 (ja) | 電圧クランプされたゲートを備えるパワーmosfet | |

| JP3658065B2 (ja) | バッテリ切離しスイッチ及びバッテリ切離しスイッチシステム | |

| JP4401500B2 (ja) | 静電放電における寄生バイポーラ効果を低減する半導体装置および方法 | |

| US5825600A (en) | Fast turn-on silicon controlled rectifier (SCR) for electrostatic discharge (ESD) protection | |

| US5654574A (en) | Electrostatic discharge protection device for integrated circuit | |

| US11315919B2 (en) | Circuit for controlling a stacked snapback clamp | |

| US4994904A (en) | MOSFET having drain voltage detection function | |

| US8351172B2 (en) | Power supply control apparatus | |

| US5747834A (en) | Adjustable Bipolar SCR holding voltage for ESD protection circuits in high speed Bipolar/BiCMOS circuits | |

| US9705318B2 (en) | Over-limit electrical condition protection circuits for integrated circuits | |

| US9029910B2 (en) | Programmable SCR for ESD protection | |

| US8848328B2 (en) | Load driving device | |

| US20070047162A1 (en) | Electrostatic protection circuit | |

| WO2006013211A1 (en) | A semiconductor switch arrangement and an electronic device | |

| JP2792417B2 (ja) | 半導体回路の入力保護回路 | |

| JP2655572B2 (ja) | 電圧衝撃保護回路 | |

| JP7038531B2 (ja) | 電源逆接続保護機能を備えた負荷駆動回路 | |

| TWI221662B (en) | Semiconductor device having a protective circuit | |

| US20030043517A1 (en) | Electro-static discharge protecting circuit | |

| US6108181A (en) | Electrostatic discharge (ESD) circuit | |

| JPH0758331A (ja) | 半導体装置 | |

| JP3739376B2 (ja) | 半導体装置 | |

| JP4248658B2 (ja) | フューズトリミング回路 | |

| JP4457620B2 (ja) | 静電破壊保護回路 | |

| JPH10108359A (ja) | 入力保護回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070409 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080616 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080624 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080912 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080918 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081121 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081127 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081223 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090317 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090611 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20090717 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090804 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090827 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4369009 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120904 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130904 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |