JP4148717B2 - 半導体素子の製造方法 - Google Patents

半導体素子の製造方法 Download PDFInfo

- Publication number

- JP4148717B2 JP4148717B2 JP2002227883A JP2002227883A JP4148717B2 JP 4148717 B2 JP4148717 B2 JP 4148717B2 JP 2002227883 A JP2002227883 A JP 2002227883A JP 2002227883 A JP2002227883 A JP 2002227883A JP 4148717 B2 JP4148717 B2 JP 4148717B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- semiconductor substrate

- forming

- ion implantation

- oxide film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 135

- 238000004519 manufacturing process Methods 0.000 title claims description 33

- 238000005468 ion implantation Methods 0.000 claims description 128

- 239000012535 impurity Substances 0.000 claims description 116

- 239000000758 substrate Substances 0.000 claims description 90

- 125000001475 halogen functional group Chemical group 0.000 claims description 66

- 125000006850 spacer group Chemical group 0.000 claims description 63

- 238000000034 method Methods 0.000 claims description 44

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 37

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 37

- 238000005530 etching Methods 0.000 claims description 16

- 150000002500 ions Chemical class 0.000 claims description 11

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 10

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims description 10

- 230000015572 biosynthetic process Effects 0.000 claims description 10

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 10

- 238000005498 polishing Methods 0.000 claims description 7

- 238000002955 isolation Methods 0.000 claims description 3

- 238000002513 implantation Methods 0.000 claims description 2

- 239000007943 implant Substances 0.000 claims 1

- 230000000694 effects Effects 0.000 description 19

- 239000000463 material Substances 0.000 description 13

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 8

- 229910052785 arsenic Inorganic materials 0.000 description 8

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 8

- 229910052698 phosphorus Inorganic materials 0.000 description 8

- 239000011574 phosphorus Substances 0.000 description 8

- 229910021332 silicide Inorganic materials 0.000 description 8

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 8

- 238000001312 dry etching Methods 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 5

- 230000010354 integration Effects 0.000 description 5

- 229910015900 BF3 Inorganic materials 0.000 description 4

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 4

- 230000003247 decreasing effect Effects 0.000 description 4

- 230000008021 deposition Effects 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000007517 polishing process Methods 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 1

- 238000010297 mechanical methods and process Methods 0.000 description 1

- 230000005226 mechanical processes and functions Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66492—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a pocket or a lightly doped drain selectively formed at the side of the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28035—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28114—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor characterised by the sectional shape, e.g. T, inverted-T

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823412—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823418—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

- H01L21/823425—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures manufacturing common source or drain regions between a plurality of conductor-insulator-semiconductor structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823468—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate sidewall spacers, e.g. double spacers, particular spacer material or shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/6656—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using multiple spacer layers, e.g. multiple sidewall spacers

Description

【発明の属する技術分野】

本発明は半導体素子及びその製造方法に係り、より詳細には低いゲート抵抗と小さな寄生キャパシタンスを有する第1ゲート電極と第2ゲート電極とよりなるT字状構造のゲート電極と、短チャンネル効果を効果的に抑制できるハロ(halo)イオン注入領域を含む半導体素子の構造と、ゲート電極間の間隔を広げなくても高角ハロイオン注入が可能な半導体素子の製造方法に関する。

【0002】

【従来の技術】

MOSトランジスタを採用した半導体素子において、ゲート電極の臨界寸法(critical demension、CD)はMOSトランジスタの特性に多くの影響を及ぼす。半導体素子の集積度が高まるにつれてゲート電極の臨界寸法は小さくなりつつあり、これにより短チャンネル効果が深刻な問題となっている。このようなトランジスタのスケールダウンによる短チャンネル効果を改善するために狭幅接合を形成させる方法が用いられているが、この方法はソース/ドレイン延長領域の抵抗を増加させる限界を有している。これに対する解決方法としてハロイオン注入法が提案された。しかし、ゲートの臨界寸法の縮小による短チャンネル効果を抑制するためにハロイオン注入の濃度を高め続けており、これは接合キャパシタンス及び接合漏れ電流の増加、オン電流の減少などの問題を引き起こした。この問題を解決する方法として提示されたものが高角ハロイオン注入法である。

【0003】

前記高角ハロイオン注入法は、イオン注入時に高角を使用してソース/ドレイン延長領域の側部に選択的に不純物を注入してハロイオン注入領域を形成させる方法であって、低濃度の不純物を使用しても短チャンネル効果を効果的に抑制できる。そして、このようにハロイオン注入領域の不純物濃度を低めれば、胴体効果(body effect、基板効果ともいう)を減らしてオン電流は増加させ、オフ電流は減少させる効果がある。また、前記高角ハロイオン注入法を使用すれば、接合キャパシタンスの減少、ゲート大きさ変化の減少効果がある。

【0004】

【発明が解決しようとする課題】

しかし、半導体素子の集積度の上昇によるゲート電極間間隔の限界のために一定角度以上のハロイオン注入が不可能で高角ハロイオン注入法の長所を利用できない。すなわち、前述したように高性能トランジスタを作るためには高角ハロイオン注入法の適用が必須であるが、隣接したゲート電極によりイオン注入遮断効果が発生して高角のハロイオン注入を実施できない。これを解決するためにはゲート電極間の間隔を広げるか、あるいはゲート電極の高さを十分に低める必要がある。しかし、ゲート電極間の間隔を広げるほどチップサイズが大きくなって高集積化に逆行する結果をもたらす。また、ゲート電極の高さを低めることによって抵抗減少のために必須なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的工程に対する十分なゲート電極の高さを確保できなくなる。

【0005】

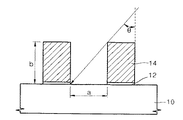

図1は、ゲート電極の高さとゲート電極の間隔がハロイオン注入角度に及ぼす影響を説明するために示した断面図である。

図1を参照すれば、ゲート電極14間の間隔をa、ゲート電極14の高さをb、半導体基板10に垂直の方向と不純物イオンの入射方向とがなす角をθとする時、θが大きい高角ハロイオン注入法を適用するためには十分なa/b比を有する必要がある。このためにはゲート電極14間の間隔aを十分に広げるか、あるいはゲート電極14の高さbを十分に低める必要がある。しかし、ゲート電極14の高さbを十分に低めれば、抵抗減少のために必須なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜12や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的研磨工程に対する十分なゲート電極の高さを確保できなくなる。一方、ゲート電極14間の間隔aを十分に大きくする場合は、デザインルール上の損失をもたらしてチップサイズが大きくなる。これは半導体工程において高集積化という目標に逆行する結果となる。

【0006】

本発明は、低いゲート抵抗と、小さい寄生キャパシタンスを有するT字状構造のゲート電極と、短チャンネル効果を効果的に抑制できるハロイオン注入領域を含む半導体素子の構造を提供することを目的とする。

本発明は、ゲート電極間の間隔を広げなくても高角ハロイオン注入が可能な半導体素子の製造方法を提供することを他の目的とする。

【0007】

【課題を解決するための手段】

本発明は、半導体基板内に形成された第1イオン注入領域と、この第1イオン注入領域の両側に形成された第2イオン注入領域と、この第2イオン注入領域に接して前記第1イオン注入領域と反対側に形成されたハロイオン注入領域と、前記半導体基板上に形成されたゲート酸化膜と、このゲート酸化膜上に形成された第1ゲート電極と、前記半導体基板の表面、前記ゲート酸化膜の側縁及び前記第1ゲート電極の側壁に沿って形成されたシリコン窒化膜と、このシリコン窒化膜に接して前記第1ゲート電極と反対側に形成された酸化膜と、前記第1ゲート電極、前記シリコン窒化膜及び前記酸化膜上に形成された第2ゲート電極と、この第2ゲート電極及び前記酸化膜の側壁に形成されたスペーサとを含むことを特徴とする半導体素子とする。

【0008】

前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極は前記第2ゲート電極の幅が前記第1ゲート電極の幅より大きいT字状構造を有する。

前記第1ゲート電極の両側部分に形成された前記シリコン窒化膜はL字状または逆L字状である。

前記ゲート酸化膜は前記第2イオン注入領域間の前記半導体基板の表面に形成されている。

前記第2イオン注入領域は前記スペーサ間の間隔より広い領域にわたって前記半導体基板内に形成されている。

前記ハロイオン注入領域の不純物は前記第1及び前記第2イオン注入領域の不純物とは反対タイプの不純物である。

前記第1イオン注入領域の不純物濃度は前記第2イオン注入領域の不純物濃度より高い。

前記第1イオン注入領域の不純物濃度は約3E15〜7E15cm−2であり、前記第2イオン注入領域の不純物濃度は約1E14〜2E15cm−2であることが望ましい。

前記ハロイオン注入領域の不純物濃度は約1E13〜5E14cm−2であることが望ましい。

前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成されることが望ましい。

前記第1ゲート電極の高さは約500Å〜1000Åであることが望ましい。

前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成されることが望ましい。

前記第2ゲート電極の高さは約300Å〜1500Åであることが望ましい。

前記シリコン窒化膜は約30Å〜200Åの厚さを有することが望ましい。

前記スペーサ間の前記半導体基板内に形成された第3イオン注入領域と、前記スペーサの側部に形成された第2スペーサとをさらに含む。

【0009】

本発明は、以下のような半導体素子の製造方法とする。まず、半導体基板上にゲート酸化膜及び第1ゲート電極を形成する。次に、前記半導体基板に不純物をイオン注入してソース/ドレイン延長領域を形成する。次に、高角ハロイオン注入法を利用して前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が所定角度をなすように不純物をイオン注入して前記ソース/ドレイン延長領域の両側部にハロイオン注入領域を形成する。次に、前記ハロイオン注入領域が形成されている前記半導体基板上にシリコン窒化膜を形成する。次に、前記シリコン窒化膜が形成されている前記半導体基板上に酸化膜を形成する。次に、前記酸化膜が形成されている前記半導体基板を化学機械的研磨して前記第1ゲート電極が露出されるように平坦化する。次に、前記第1ゲート電極上部に選択的にエピタキシャル成長法を利用して第2ゲート電極を形成する。次に、前記第2ゲート電極をエッチングマスクとして使用して前記シリコン窒化膜が露出されるように前記酸化膜をエッチバックする。次に、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングしてスペーサを形成する。次に、前記半導体基板に不純物をイオン注入して深いソース/ドレイン領域を形成する。

【0010】

前記スペーサを形成する段階は前記酸化膜をエッチバックする段階後、前記深いソース/ドレイン領域を形成する段階前に行う。さらに、前記深いソース/ドレイン領域を形成する段階後に、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングして第2スペーサを形成する段階と、前記半導体基板に不純物をイオン注入して第2の深いソース/ドレイン領域を形成する段階とをさらに含む。前記スペーサを形成する段階と前記不純物をイオン注入する段階とを2回以上反復実施する。

【0011】

また、前記深いソース/ドレイン領域を形成する段階は前記酸化膜をエッチバックする段階後、前記スペーサを形成する段階前に行う。さらに、前記スペーサを形成する段階後に、前記半導体基板に不純物をイオン注入して第2の深いソース/ドレイン領域を形成する段階と、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングして第2スペーサを形成する段階とをさらに含む。前記不純物をイオン注入する段階と前記スペーサをイオン注入する段階とを2回以上反復実施する。

【0012】

前記ゲート酸化膜及び前記第1ゲート電極を形成する段階前に、前記半導体基板に素子分離領域を形成する段階と、前記半導体基板にスレッショルド電圧調節のために不純物をイオン注入する段階とをさらに含む。

【0013】

前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角は約30゜〜80゜であることが望ましい。

前記半導体基板に垂直な方向と前記不純物イオンの入射方向とがなす最大角が約30゜〜80゜になるように前記第1ゲート電極の高さを調節する。

前記第1ゲート電極は約500Å〜1500Åの高さに形成することが望ましい。

前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することが望ましい。

前記ハロイオン注入領域形成のための不純物は前記ソース/ドレイン延長領域形成のための不純物とは反対タイプの不純物である。

前記深いソース/ドレイン領域形成のための不純物のイオン注入濃度は前記ソース/ドレイン延長領域形成のための不純物のイオン注入濃度より高い。

前記ソース/ドレイン延長領域形成のためのイオン注入は約1E14〜2E15cm−2の濃度で実施することが望ましい。

前記ハロイオン注入領域形成のためのイオン注入は約1E13〜5E14cm−2の濃度で実施することが望ましい。

前記深いソース/ドレイン領域形成のためのイオン注入は約3E15〜7E15cm−2の濃度で実施することが望ましい。

前記第2ゲート電極は約300Å〜1500Åの高さに形成することが望ましい。

前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することが望ましい。

前記シリコン窒化膜は約30Å〜200Åの厚さに形成することが望ましい。

前記酸化膜は前記シリコン窒化膜とのエッチング選択比が大きい高温酸化膜(High Temperature Oxide;HTO)、中温酸化膜(Middle Temperature Oxide;MTO)または低温酸化膜(Low Temperature Oxide;LTO)で形成することが望ましい。

前記第2ゲート電極の幅を前記第1ゲート電極の幅より大きく形成して前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極はT字状構造を有する。

【0014】

【発明の実施の形態】

以下、添付した図面を参照して本発明による望ましい実施形態を詳細に説明する。しかし、以下の実施形態は当業者が本発明を十分に理解できるように提供されるものであって、色々な他の形態に変形でき、本発明の範囲が以下の実施形態に限定されるものではない。以下の説明である層が他の層上に存在すると記述される時、これは他の層の真上に存在することもあり、その間に第3の層が介在されることもある。また図面で各層の厚さや大きさは説明の便宜及び明確性のために誇張された。図面上で同一符号は同じ要素を示す。

【0015】

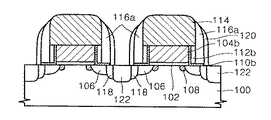

図12及び図16は、本発明の望ましい実施形態による半導体素子の構造を示した断面図である。

図12及び図16を参照すれば、半導体基板100内に第1イオン注入領域118、すなわち、深いソース/ドレイン領域118が形成されている。この第1イオン注入領域118は後述するスペーサ116a間の間隔より広い領域にわたって半導体基板100内に形成されている。第1イオン注入領域118の両側部には第2イオン注入領域106、すなわち、ソース/ドレイン延長領域106が形成されている。この第2イオン注入領域106の不純物濃度は第1イオン注入領域118の不純物濃度よりは低いことが望ましい。望ましくは、第1イオン注入領域118の不純物濃度は約3E15〜7E15cm−2であり、第2イオン注入領域106の不純物濃度は約1E14〜2E15cm−2であることが望ましい。また、ハロイオン注入領域108が第2イオン注入領域106に接して第1イオン注入領域118と反対側に形成されている。このハロイオン注入領域108に注入された不純物は第1及び第2イオン注入領域118,106に注入された不純物とは反対タイプである。例えば、第1及び第2イオン注入領域118,106に注入された不純物がホウ素及び/またはインジウムのようなP型不純物である場合、ハロイオン注入領域108に注入された不純物は砒素及び/または燐のようなN型不純物である。反対に、第1及び第2イオン注入領域118,106に注入された不純物が砒素及び/または燐のようなN型不純物である場合、ハロイオン注入領域108に注入された不純物はホウ素及び/またはインジウムのようなP型不純物である。ハロイオン注入領域108は低濃度の不純物を有することが望ましい。望ましくは、ハロイオン注入領域108の不純物濃度は約1E13〜5E14cm−2であることが望ましい。このようにハロイオン注入領域108をソース/ドレイン延長領域106の側部に形成させれば、低い不純物濃度でも短チャンネル効果を効果的に抑制でき、また胴体効果(body effect)を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。

【0016】

一方、半導体基板100上にはゲート酸化膜102が形成されている。すなわち、ソース/ドレイン延長領域106間の半導体基板100の表面にゲート酸化膜102が形成されている。このゲート酸化膜102上には第1ゲート電極104bが形成されている。この第1ゲート電極104bは多結晶シリコン膜またはシリコンゲルマニウム膜よりなることが望ましい。また、第1ゲート電極104bは約500Å〜1000Åの厚さを有することが望ましい。半導体基板100の表面、ゲート酸化膜102の側縁及び第1ゲート電極104bの側壁に沿ってシリコン窒化膜110bが形成されている。第1ゲート電極104bの両側部分に形成されたシリコン窒化膜110bはL字状または逆L字状である。このシリコン窒化膜110bは30Å〜200Å程度の厚さを有することが望ましい。また、このシリコン窒化膜110bに接して第1ゲート電極104bと反対側に酸化膜112bが形成されている。この酸化膜112bはHTO、MTOまたはLTOで形成できる。第1ゲート電極104b、シリコン窒化膜110b及び酸化膜112b上には第2ゲート電極114が形成されている。この第2ゲート電極114は多結晶シリコン膜またはシリコンゲルマニウム膜よりなることが望ましい。また、第2ゲート電極114は300Å〜1500Å程度の厚さを有することが望ましい。このような第2ゲート電極114及び酸化膜112bの側壁にはスペーサ116aが形成されている。すなわち、スペーサ116aは第2ゲート電極114及び酸化膜112bと接して、半導体基板表面に沿って位置するシリコン窒化膜110bの上に位置する。スペーサ116aはシリコン窒化膜、HTO、MTOまたはLTOで形成できる。

【0017】

本実施形態による半導体素子によれば、ゲート電極114,104bは第1ゲート電極104b及び第2ゲート電極114よりなるT字状構造を有する。このようなT字状ゲート構造の場合、ゲート下部(第1ゲート電極104b)の幅は小さくしてもゲート上部(第2ゲート電極114)の幅は大きくしてシリサイドを広く形成することによって抵抗を低められる。また、ゲートキャパシタンスを小さくすることができ、ゲートとソース/ドレイン延長領域間のオーバラップキャパシタンスも減らしうる。

【0018】

図13及び図17は、図12及び図16に示した半導体素子の構造に第3イオン注入領域122及び第2スペーサ120をさらに形成した構造を示した断面図である。

図13及び図17を参照すれば、半導体基板100内に第3イオン注入領域122、すなわち、第2の深いソース/ドレイン領域122が形成されている。この第3イオン注入領域122は後述する第2スペーサ120間の間隔より広い領域にわたって半導体基板100内に形成される。この第3イオン注入領域122の両側部には第1イオン注入領域118が形成されている。この第1イオン注入領域118の不純物濃度は第3イオン注入領域122の不純物濃度より低いことが望ましい。また、第2イオン注入領域106が第1イオン注入領域118に接して第3イオン注入領域122と反対側に形成されている。この第2イオン注入領域106の不純物濃度は第1イオン注入領域118の不純物濃度より低いことが望ましい。また、ハロイオン注入領域108が第2イオン注入領域106に接して第1イオン注入領域118と反対側に形成されている。このハロイオン注入領域108に注入された不純物は第1、第2及び第3イオン注入領域118,106,122に注入された不純物とは反対タイプである。例えば、第1、第2及び第3イオン注入領域118,106,122に注入された不純物がホウ素及び/またはインジウムのようなP型不純物である場合、ハロイオン注入領域108に注入された不純物は砒素及び/または燐のようなN型不純物である。反対に、第1、第2及び第3イオン注入領域118,106,122に注入された不純物が砒素及び/または燐のようなN型不純物である場合、ハロイオン注入領域108に注入された不純物はホウ素及び/またはインジウムのようなP型不純物である。このようにハロイオン注入領域108をソース/ドレイン延長領域106の側部に形成させれば、低い不純物濃度でも短チャンネル効果を効果的に抑制でき、また胴体効果を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。一方、半導体基板100の上部のゲート構造はゲート側壁に第2スペーサ120をさらに形成したことを除いては図13及び図16に示したT字状ゲート構造と同一である。

【0019】

以下、本発明の望ましい実施形態による半導体素子の製造方法を説明する。

図2ないし図13は、本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

図2を参照すれば、半導体基板100に活性領域を定義し、その活性領域を電気的に分離させるフィールド酸化膜(図示せず)を形成する。このフィールド酸化膜は通常のLOCOS工程または浅いトレンチ素子分離工程で形成できる。次いで、半導体基板100にスレッショルド電圧を調節するためにイオン注入を実施する。

【0020】

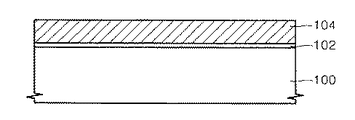

次に、半導体基板100上にゲート酸化膜102を形成する。次いで、ゲート酸化膜102上に第1ゲート物質104を蒸着する。この第1ゲート物質104は多結晶シリコンまたはシリコンゲルマニウムであることが望ましい。一方、この第1ゲート物質104の蒸着を厚くした場合は、後続のハロイオン注入工程で高角のイオン注入を実施できない。また、第1ゲート物質104の蒸着を薄くした場合は、抵抗減少のために必要なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜102や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的研磨工程に対する十分な厚さを確保できなくなる。したがって、第1ゲート物質104はこのような事項を考慮して適切にその蒸着の厚さを決定する必要がある。望ましくは、約500Å〜1500Åの厚さに第1ゲート物質104を蒸着する。

【0021】

図3を参照すれば、第1ゲート物質104及びゲート酸化膜102をパターニングする。このパターニングは通常の写真工程及びエッチング工程を利用し、このパターニングにより第1ゲート電極104aが形成される。

【0022】

図4を参照すれば、第1ゲート電極104aが形成されている半導体基板100に不純物をイオン注入してソース/ドレイン延長領域106を形成する。このソース/ドレイン延長領域106は半導体基板100のドーピングタイプと反対タイプの不純物をイオン注入する。例えば、半導体基板100がN型不純物でドーピングされている場合、ソース/ドレイン延長領域106はホウ素、フルオロ化ホウ素(BF2)のようなP型不純物でイオン注入する。反対に、半導体基板100がP型不純物でドーピングされている場合、ソース/ドレイン延長領域106は砒素、燐のようなN型不純物でイオン注入する。ソース/ドレイン延長領域106の不純物濃度は約1E14〜2E15cm−2であることが望ましい。

【0023】

図5を参照すれば、ソース/ドレイン延長領域106が形成されている半導体基板100に高角ハロイオン注入法を利用してハロイオン注入領域108を形成する。このハロイオン注入領域108はソース/ドレイン延長領域106の側部に形成される。このようにソース/ドレイン延長領域106の側部にハロイオン注入領域108を形成すれば、短チャンネル効果を効果的に抑制でき、胴体効果を減少させてオン電流は増加させ、オフ電流は減少させる効果を得られる。また、接合キャパシタンスの減少及びゲート長さ変化の減少効果を得られる。前記高角ハロイオン注入は半導体基板100に垂直の方向と不純物イオンの入射方向とがなす角θが約30゜〜80゜になるように実施することが望ましい。半導体基板100に垂直の方向と不純物イオンの入射方向とがなす角θが大きい高角を使用してソース/ドレイン延長領域106の側部にハロイオン注入領域108を形成すれば、低い不純物濃度を使用しても短チャンネル効果を効果的に抑制できる。一方、ハロイオン注入領域108はソース/ドレイン延長領域106のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、ソース/ドレイン延長領域106がN型不純物でドーピングされている場合、ハロイオン注入領域108はホウ素、インジウムのようなP型不純物でイオン注入する。反対に、ソース/ドレイン延長領域106がP型不純物でドーピングされている場合、ハロイオン注入領域108は砒素、燐のようなN型不純物でイオン注入する。ハロイオン注入領域108は低濃度の不純物でイオン注入されることが望ましい。ハロイオン注入領域108の不純物濃度が高すぎる場合、接合キャパシタンス及び接合漏れ電流の増加、オン電流の減少などの問題を引き起こすことがある。望ましくは、ハロイオン注入領域108の不純物濃度は約1E13〜5E14cm−2であることが望ましい。

【0024】

図6を参照すれば、ハロイオン注入領域108が形成されている半導体基板100上に段差に沿ってシリコン窒化膜110を形成する。このシリコン窒化膜110は約30Å〜200Åの厚さに形成することが望ましい。

次いで、シリコン窒化膜110上にシリコン窒化膜110とエッチング選択比が大きい酸化膜112を形成する。この酸化膜112はシリコン窒化膜100とのエッチング選択比が大きいHTO、MTOまたはLTOで形成できる。この酸化膜112は約500Å〜2500Åの厚さに形成することが望ましい。

【0025】

図7を参照すれば、酸化膜112が形成されている半導体基板100を第1ゲート電極104aの上部が露出されるように化学機械的研磨して平坦化する。この化学機械的研磨により第1ゲート電極104aを所定厚さだけリセスさせる。リセスされた後の第1ゲート電極104bの高さは約500Å〜1000Åにすることが望ましい。なお、化学機械的研磨後の残存酸化膜112は符号112aで、残存シリコン窒化膜110は符号110aでそれぞれ示す。

【0026】

図8を参照すれば、第1ゲート電極104bの上部に選択的にエピタキシャル成長法を利用して第2ゲート物質を成長させて第2ゲート電極114を形成する。このときの前記第2ゲート物質は多結晶シリコンまたはシリコンゲルマニウムであることが望ましい。また、前記第2ゲート物質は約300Å〜1500Åの厚さに成長させることが望ましい。このようにして第1ゲート電極104bの上部に第2ゲート電極114を形成することによって本発明のゲート電極は第2ゲート電極114と第1ゲート電極104bとよりなるT字状ゲート電極構造を有する。

【0027】

図9を参照すれば、酸化膜112aを第2ゲート電極114をエッチングマスクとして使用してエッチバックする。すなわち、第2ゲート電極114が形成された半導体基板100をフォトマスク層を形成せずに全面乾式エッチングする。このエッチバックにより酸化膜112aは第2ゲート電極114の下部にのみシリコン窒化膜110aと接しつつ酸化膜112bとして残ることになる。この時、酸化膜112aに対してエッチング選択比を有するシリコン窒化膜110aは前記エッチングに対するエッチング停止層の役割をする。

【0028】

図10を参照すれば、半導体基板100上にスペーサ形成用絶縁膜116を形成する。このスペーサ形成用絶縁膜116はHTO、MTO、LTOのような酸化膜またはシリコン窒化膜で形成できる。また、このスペーサ形成用絶縁膜116は約300Å〜2500Åの厚さに形成することが望ましい。

【0029】

図11を参照すれば、スペーサ形成用絶縁膜116を異方性乾式エッチングしてスペーサ116aを形成する。この時、スペーサ形成用絶縁膜116の下部に形成されたシリコン窒化膜110aもエッチングして所定領域の半導体基板100を露出させる。このエッチング後もゲート部に残ったシリコン窒化膜110aを符号110bで示す。

【0030】

図12を参照すれば、スペーサ116aが形成されている半導体基板100に不純物をイオン注入して深いソース/ドレイン領域118を形成する。この深いソース/ドレイン領域118は半導体基板100のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、半導体基板100がN型不純物でドーピングされている場合、深いソース/ドレイン領域118はホウ素、フルオロ化ホウ素のようなP型不純物でイオン注入する。反対に、半導体基板100がP型不純物でドーピングされている場合、深いソース/ドレイン領域118は砒素、燐のようなN型不純物でイオン注入する。深いソース/ドレイン領域118の不純物濃度はソース/ドレイン延長領域106の不純物濃度より高くすることが望ましい。望ましくは、深いソース/ドレイン領域118が約3E15〜7E15cm−2の不純物濃度を有するようにする。

【0031】

一方、図12ではスペーサ116aと深いソース/ドレイン領域118とを一つずつのみ形成したことを示したが、図13に示したように第2スペーサ120と第2の深いソース/ドレイン領域122とをさらに形成できる。すなわち、半導体基板100上にスペーサ形成用絶縁膜を形成した後、異方性乾式エッチングして第2スペーサ120を形成し、イオン注入を実施して第2の深いソース/ドレイン領域122を形成できる。このとき、第2の深いソース/ドレイン領域122の不純物濃度は深いソース/ドレイン領域118の不純物濃度より高いことが望ましい。また、前記スペーサ形成工程と深いソース/ドレイン領域形成工程を2回以上反復実施して、多重形態のスペーサ(図示せず)と多重の深いソース/ドレイン領域(図示せず)とを形成することもある。

【0032】

図14ないし図17は、本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

図2ないし図9に示した前記第1実施形態の各段階は本第2実施形態の各段階と同一である。したがって、前記第1実施形態で図2ないし図9を参照して詳細に説明した各工程段階は本第2実施形態では簡単に記述する。まず、半導体基板100に活性領域を定義し、その活性領域を電気的に分離させるフィールド酸化膜(図示せず)を形成する。次に、半導体基板100上にゲート酸化膜102及び第1ゲート物質104を形成した後、パターニングして第1ゲート電極104aを形成する。次いで、半導体基板100に不純物をイオン注入してソース/ドレイン延長領域106を形成する。次に、半導体基板100に高角ハロイオン注入法を利用してハロイオン注入領域108を形成する。次いで、半導体基板100上にシリコン窒化膜110及び酸化膜112を形成した後、第1ゲート電極104aの上部が露出されるように化学機械的研磨して平坦化する。次に、第1ゲート電極104bの上部に選択的にエピタキシャル成長法を利用して第2ゲート物質を成長させて第2ゲート電極114を形成する。次いで、酸化膜112aを第2ゲート電極114をエッチングマスクとして使用してエッチバックする。

【0033】

図14を参照すれば、酸化膜112bがエッチバックされている半導体基板100に不純物をイオン注入して深いソース/ドレイン領域118を形成する。この深いソース/ドレイン領域118は半導体基板100のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、半導体基板100がN型不純物でドーピングされている場合、深いソース/ドレイン領域118はホウ素及び/またはフルオロ化ホウ素のようなP型不純物でイオン注入する。反対に、半導体基板100がP型不純物でドーピングされている場合、深いソース/ドレイン領域118は砒素及び/または燐のようなN型不純物でイオン注入する。深いソース/ドレイン領域118の不純物濃度はソース/ドレイン延長領域106の不純物濃度よりは高くすることが望ましい。望ましくは、深いソース/ドレイン領域118が約3E15〜7E15cm−2のドーピング濃度を有するようにする。

【0034】

図15を参照すれば、深いソース/ドレイン領域118が形成されている半導体基板100上にスペーサ形成用絶縁膜116を形成する。このスペーサ形成用絶縁膜116はHTO、MTO、LTOのような酸化膜またはシリコン窒化膜で形成できる。また、このスペーサ形成用絶縁膜116は約300Å〜2500Åの厚さに形成することが望ましい。

【0035】

図16を参照すれば、スペーサ形成用絶縁膜116を異方性乾式エッチングしてスペーサ116aを形成する。この時、スペーサ形成用絶縁膜116の下部に形成されたシリコン窒化膜110aもエッチングして所定領域の半導体基板100を露出させる。このエッチング後もゲート部に残ったシリコン窒化膜110aを符号110bで示す。

【0036】

図16にはスペーサ116a及び深いソース/ドレイン領域118を一つずつのみ形成したことを示したが、図17に示したように第2スペーサ120と第2の深いソース/ドレイン領域122をさらに形成できる。すなわち、半導体基板100にイオン注入を実施して第2の深いソース/ドレイン領域122を形成した後、半導体基板100上にスペーサ形成用絶縁膜を形成し、異方性乾式エッチングして第2スペーサ120を形成できる。ここで、第2の深いソース/ドレイン領域122の不純物濃度は深いソース/ドレイン領域118の不純物濃度より高いことが望ましい。また、前記深いソース/ドレイン領域形成工程と前記スペーサ形成工程を2回以上反復実施して、多重の深いソース/ドレイン領域(図示せず)と多重形態のスペーサ(図示せず)とを形成できる。

【0037】

【発明の効果】

以上のように、本発明による半導体素子の構造によれば、ゲート電極は第1ゲート電極及び第2ゲート電極よりなるT字状構造を有する。したがって、ゲート下部(第1ゲート電極)の幅は小さくしてもゲート上部(第2ゲート電極)の幅は大きくしてシリサイドを広く形成することによって抵抗を低められる。また、ゲートキャパシタンスを小さくすることができ、ゲートとソース/ドレイン延長領域間のオーバラップキャパシタンスも減らしうる。

【0038】

一方、半導体素子の集積度が高まるにつれて、従来はゲート電極間の間隔の限界によって一定角度以上のハロイオン注入が不可能で高角イオン注入法の長所を利用できなかったが、本発明のように従来より低い第1ゲート電極を形成した後、高角ハロイオン注入を実施して第2ゲート電極を形成することによってゲート電極間の間隔を広げずに高角ハロイオン注入を実施できる。

【0039】

また、本発明の半導体素子の製造方法によれば、ソース/ドレイン延長領域の側部に選択的に不純物を注入してハロイオン注入領域を形成することによって、短チャンネル効果を効果的に抑制できる。低い不純物濃度でハロイオン注入領域を形成することによって、胴体効果を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。

【図面の簡単な説明】

【図1】ゲート電極の高さとゲート電極の間隔がハロイオン注入角度に及ぼす影響を説明するために示した断面図である。

【図2】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図3】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図4】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図5】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図6】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図7】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図8】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図9】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図10】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図11】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図12】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図13】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図14】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図15】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図16】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図17】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【符号の説明】

100 半導体基板

102 ゲート酸化膜

104b 第1ゲート電極

106 ソース/ドレイン延長領域

108 ハロイオン注入領域

110b シリコン窒化膜

112b 酸化膜

114 第2ゲート電極

116a スペーサ

118 深いソース/ドレイン領域

120 第2スペーサ

122 第2の深いソース/ドレイン領域

Claims (17)

- 半導体基板上にゲート酸化膜及び第1ゲート電極を形成する第1工程と、

前記第1工程後、前記半導体基板に不純物をイオン注入して、前記第1ゲート電極両側の前記半導体基板内にソース/ドレイン延長領域を形成する第2工程と、

前記第2工程後、前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が約30゜〜80゜である高角ハロイオン注入法を利用して、前記ソース/ドレイン延長領域のチャネル領域側の側部に隣接するように、前記半導体基板部分にハロイオン注入領域を形成する第3工程と、

前記第3工程後、前記半導体基板上の全面に、表面の段差に沿ってシリコン窒化膜を形成し、さらにその上に平坦化用の酸化膜を形成する第4工程と、

前記第4工程後、前記半導体基板上の全面を化学機械的研磨することにより、前記第1ゲート電極の上面が露出される状態にして、全面を平坦化する第5工程と、

前記第5工程後、幅が前記第1ゲート電極の幅より大きい第2ゲート電極を前記第1ゲート電極上部に形成する第6工程と、

前記第6工程後、前記第2ゲート電極をエッチングマスクとして使用して前記平坦化用の酸化膜をエッチングすることにより、前記第1ゲート電極の側面部分に相当する前記第2ゲート電極の側端部下のみに前記平坦化用の酸化膜を残す第7工程と、

前記第7工程後、残存した前記平坦化用の酸化膜の側面と前記第2ゲート電極の側面に絶縁膜の第1スペーサを形成する第8工程と、

前記第8工程後、前記第2ゲート電極および前記第1スペーサをマスクとして前記半導体基板に不純物をイオン注入することにより、前記第1スペーサ側方の前記半導体基板部分に深いソース/ドレイン領域を形成する第9工程と、

を具備することを特徴とする半導体素子の製造方法。 - 前記第9工程後、前記第1スペーサの側壁に絶縁膜の第2スペーサを形成する第10工程と、

前記第10工程後、前記第1スペーサ、前記第2スペーサおよび前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第2スペーサ側方の前記半導体基板部分に第2の深いソース/ドレイン領域を形成する第11工程と、

が追加されることを特徴とする請求項1に記載の半導体素子の製造方法。 - 半導体基板上にゲート酸化膜及び第1ゲート電極を形成する第1工程と、

前記第1工程後、前記半導体基板に不純物をイオン注入して、前記第1ゲート電極両側の前記半導体基板内にソース/ドレイン延長領域を形成する第2工程と、

前記第2工程後、前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が約30゜〜80゜である高角ハロイオン注入法を利用して、前記ソース/ドレイン延長領域のチャネル領域側の側部に隣接するように、前記半導体基板部分にハロイオン注入領域を形成する第3工程と、

前記第3工程後、前記半導体基板上の全面に、表面の段差に沿ってシリコン窒化膜を形成し、さらにその上に平坦化用の酸化膜を形成する第4工程と、

前記第4工程後、前記半導体基板上の全面を化学機械的研磨することにより、前記第1ゲート電極の上面が露出される状態にして、全面を平坦化する第5工程と、

前記第5工程後、幅が前記第1ゲート電極の幅より大きい第2ゲート電極を前記第1ゲート電極上部に形成する第6工程と、

前記第6工程後、前記第2ゲート電極をエッチングマスクとして使用して前記平坦化用の酸化膜をエッチングすることにより、前記第1ゲート電極の側面部分に相当する前記第2ゲート電極の側端部下のみに前記平坦化用の酸化膜を残す第7工程と、

前記第7工程後、前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第2ゲート電極側方の前記半導体基板部分に深いソース/ドレイン領域を形成する第8工程と、

前記第8工程後、前記第2ゲート電極の側面と、該第2ゲート電極の側端部下に残存した前記平坦化用の酸化膜の側面とに絶縁膜の第1スペーサを形成する第9工程と、

を具備することを特徴とする半導体素子の製造方法。 - 前記第9工程後、前記第1スペーサおよび前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第1スペーサ側方の前記半導体基板部分に第2の深いソース/ドレイン領域を形成する第10工程と、

前記第10工程後に、前記第1スペーサの側壁に絶縁膜の第2スペーサを形成する第11工程と、

が追加されることを特徴とする請求項3に記載の半導体素子の製造方法。 - 前記ゲート酸化膜及び前記第1ゲート電極を形成する工程の前に、

前記半導体基板に素子分離領域を形成する工程と、

前記半導体基板にスレッショルド電圧調節のために不純物をイオン注入する工程とが実施されることを特徴とする請求項1または3に記載の半導体素子の製造方法。 - 前記第1ゲート電極は約500Å〜1500Åの高さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記ハロイオン注入領域形成のための不純物は前記ソース/ドレイン延長領域形成のための不純物とは反対タイプの不純物であることを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記深いソース/ドレイン領域形成のための不純物のイオン注入ドーズ量は前記ソース/ドレイン延長領域形成のための不純物のイオン注入ドーズ量より高いことを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記ソース/ドレイン延長領域形成のためのイオン注入は約1E14〜2E15cm−2のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記ハロイオン注入領域形成のためのイオン注入は約1E13〜5E14cm−2のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記深いソース/ドレイン領域形成のためのイオン注入は約3E15〜7E15cm−2のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記第2ゲート電極は約300Å〜1500Åの高さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記シリコン窒化膜は約30Å〜200Åの厚さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記平坦化用の酸化膜は前記シリコン窒化膜とのエッチング選択比が大きい高温酸化膜、中温酸化膜または低温酸化膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

- 前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極はT字状構造を有することを特徴とする請求項1または3に記載の半導体素子の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2001-047148 | 2001-08-04 | ||

| KR1020010047148A KR100374649B1 (en) | 2001-08-04 | 2001-08-04 | Structure of semiconductor device and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003110104A JP2003110104A (ja) | 2003-04-11 |

| JP4148717B2 true JP4148717B2 (ja) | 2008-09-10 |

Family

ID=19712880

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002227883A Expired - Fee Related JP4148717B2 (ja) | 2001-08-04 | 2002-08-05 | 半導体素子の製造方法 |

| JP2003392420A Expired - Fee Related JP4903361B2 (ja) | 2000-07-27 | 2003-11-21 | 情報アクセス装置および方法ならびに情報提供装置および方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003392420A Expired - Fee Related JP4903361B2 (ja) | 2000-07-27 | 2003-11-21 | 情報アクセス装置および方法ならびに情報提供装置および方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6548862B2 (ja) |

| JP (2) | JP4148717B2 (ja) |

| KR (1) | KR100374649B1 (ja) |

| CN (1) | CN1290203C (ja) |

| DE (1) | DE10234392B4 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100398874B1 (ko) * | 2001-11-21 | 2003-09-19 | 삼성전자주식회사 | 티자형의 게이트 전극을 갖는 모스 트랜지스터 및 그 제조방법 |

| US6770932B2 (en) * | 2002-07-10 | 2004-08-03 | Kabushiki Kaisha Toshiba | Semiconductor memory device having a memory region and a peripheral region, and a manufacturing method thereof |

| US6806126B1 (en) * | 2002-09-06 | 2004-10-19 | Advanced Micro Devices, Inc. | Method of manufacturing a semiconductor component |

| JP3574644B2 (ja) * | 2002-11-20 | 2004-10-06 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| US6905976B2 (en) * | 2003-05-06 | 2005-06-14 | International Business Machines Corporation | Structure and method of forming a notched gate field effect transistor |

| US7135373B2 (en) * | 2003-09-23 | 2006-11-14 | Texas Instruments Incorporated | Reduction of channel hot carrier effects in transistor devices |

| DE102004005992B3 (de) * | 2004-02-06 | 2005-11-17 | Infineon Technologies Ag | Herstellungsverfahren für eine Halbleiterstruktur |

| WO2006043328A1 (ja) * | 2004-10-22 | 2006-04-27 | Mitsubishi Denki Kabushiki Kaisha | 情報格納システム及びデジタル放送受信端末及び情報格納装置 |

| JP4646672B2 (ja) * | 2005-03-31 | 2011-03-09 | セイコーインスツル株式会社 | コンテンツデータ配信システム、および受信装置 |

| US20070001199A1 (en) * | 2005-06-30 | 2007-01-04 | Thunderbird Technologies, Inc. | Circuits and Integrated Circuits Including Field Effect Transistors Having Differing Body Effects |

| JP4810932B2 (ja) * | 2005-08-29 | 2011-11-09 | カシオ計算機株式会社 | 携帯端末装置およびテレビ受信装置および番組表示制御方法 |

| JP2007165541A (ja) * | 2005-12-13 | 2007-06-28 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| KR100846393B1 (ko) * | 2007-03-30 | 2008-07-15 | 주식회사 하이닉스반도체 | 반도체 소자의 트랜지스터 및 그 제조 방법 |

| US20090218638A1 (en) * | 2008-02-29 | 2009-09-03 | Smith Michael A | Nand flash peripheral circuitry field plate |

| CN101867665B (zh) * | 2009-04-15 | 2015-04-01 | 中兴通讯股份有限公司 | 媒体资源播放系统、方法、以及业务服务器 |

| US9048254B2 (en) * | 2009-12-02 | 2015-06-02 | United Microelectronics Corp. | Semiconductor structure having a metal gate with side wall spacers |

| CN101794712A (zh) * | 2010-01-28 | 2010-08-04 | 中国科学院上海微系统与信息技术研究所 | 大角度离子注入抑制soi mos器件浮体效应的方法 |

| CN102386085A (zh) * | 2010-09-06 | 2012-03-21 | 中国科学院微电子研究所 | 一种用于后栅工艺的平坦化方法及其器件结构 |

| CN104217933B (zh) * | 2013-06-05 | 2016-12-28 | 中芯国际集成电路制造(上海)有限公司 | 半导体结构及其形成方法 |

| US9349817B2 (en) | 2014-02-03 | 2016-05-24 | Taiwan Semiconductor Manufacturing Co., Ltd | Semiconductor device including spacers having different dimensions |

| US10096523B2 (en) * | 2015-11-30 | 2018-10-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Spacer structure and manufacturing method thereof |

| JP2018148123A (ja) * | 2017-03-08 | 2018-09-20 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及び半導体装置の製造方法 |

| US10790148B2 (en) * | 2018-05-23 | 2020-09-29 | Globalfoundries Inc. | Method to increase effective gate height |

| US20230282716A1 (en) * | 2022-03-04 | 2023-09-07 | Qualcomm Incorporated | High performance device with double side contacts |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63141467A (ja) * | 1986-12-03 | 1988-06-13 | Matsushita Graphic Commun Syst Inc | 番組自動受信起動装置 |

| JPH03220729A (ja) * | 1990-01-25 | 1991-09-27 | Nec Corp | 電界効果型トランジスタの製造方法 |

| US5744372A (en) * | 1995-04-12 | 1998-04-28 | National Semiconductor Corporation | Fabrication of complementary field-effect transistors each having multi-part channel |

| JP3714995B2 (ja) * | 1995-07-05 | 2005-11-09 | シャープ株式会社 | 半導体装置 |

| JPH09160852A (ja) * | 1995-12-05 | 1997-06-20 | Nippon Telegr & Teleph Corp <Ntt> | 情報提供装置 |

| JPH09289498A (ja) * | 1996-04-24 | 1997-11-04 | Toshiba Corp | 番組放送システム |

| JPH1056632A (ja) * | 1996-08-07 | 1998-02-24 | Toshiba Corp | 放送システムおよび放送受信装置 |

| JP3167109B2 (ja) * | 1996-12-16 | 2001-05-21 | 株式会社アクセス | テレビ番組と連携してインターネットホームページを自動的にテレビ画面上に表示させる方法および装置 |

| US5843815A (en) * | 1997-01-15 | 1998-12-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method for fabricating a MOSFET device, for an SRAM cell, using a self-aligned ion implanted halo region |

| JPH10261285A (ja) * | 1997-03-19 | 1998-09-29 | Matsushita Electric Ind Co Ltd | 記録再生装置 |

| KR100260044B1 (ko) * | 1997-11-25 | 2000-07-01 | 윤종용 | 고속/고성능 모스 트랜지스터 및 그 제조방법 |

| JP4249814B2 (ja) * | 1998-01-14 | 2009-04-08 | 株式会社インフォシティ | 情報アクセス方法および装置 |

| US6049114A (en) * | 1998-07-20 | 2000-04-11 | Motorola, Inc. | Semiconductor device having a metal containing layer overlying a gate dielectric |

| JP2000156502A (ja) * | 1998-09-21 | 2000-06-06 | Texas Instr Inc <Ti> | 集積回路及び方法 |

| JP3237626B2 (ja) * | 1998-10-02 | 2001-12-10 | 日本電気株式会社 | 半導体装置の製造方法 |

| JP4280946B2 (ja) * | 1998-12-28 | 2009-06-17 | ソニー株式会社 | 情報処理システムおよび方法、携帯端末、情報処理装置、並びに、記録媒体 |

| US6168995B1 (en) * | 1999-01-12 | 2001-01-02 | Lucent Technologies Inc. | Method of fabricating a split gate memory cell |

-

2001

- 2001-08-04 KR KR1020010047148A patent/KR100374649B1/ko not_active IP Right Cessation

-

2002

- 2002-05-14 US US10/144,962 patent/US6548862B2/en not_active Expired - Fee Related

- 2002-07-19 CN CNB021264384A patent/CN1290203C/zh not_active Expired - Lifetime

- 2002-07-23 DE DE10234392A patent/DE10234392B4/de not_active Expired - Lifetime

- 2002-08-05 JP JP2002227883A patent/JP4148717B2/ja not_active Expired - Fee Related

-

2003

- 2003-02-21 US US10/371,093 patent/US6764910B2/en not_active Expired - Lifetime

- 2003-11-21 JP JP2003392420A patent/JP4903361B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20030030103A1 (en) | 2003-02-13 |

| US20030151097A1 (en) | 2003-08-14 |

| JP2004147336A (ja) | 2004-05-20 |

| DE10234392B4 (de) | 2008-08-14 |

| CN1290203C (zh) | 2006-12-13 |

| US6764910B2 (en) | 2004-07-20 |

| JP4903361B2 (ja) | 2012-03-28 |

| US6548862B2 (en) | 2003-04-15 |

| JP2003110104A (ja) | 2003-04-11 |

| DE10234392A1 (de) | 2003-02-27 |

| CN1405894A (zh) | 2003-03-26 |

| KR100374649B1 (en) | 2003-03-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4148717B2 (ja) | 半導体素子の製造方法 | |

| US6372559B1 (en) | Method for self-aligned vertical double-gate MOSFET | |

| US8106456B2 (en) | SOI transistors having an embedded extension region to improve extension resistance and channel strain characteristics | |

| US8227316B2 (en) | Method for manufacturing double gate finFET with asymmetric halo | |

| KR20030058633A (ko) | 수직형 트랜지스터 및 그 제조 방법 | |

| KR100639971B1 (ko) | 리세스된 소스/드레인 구조를 갖는 초박막의 에스오아이모스 트랜지스터 및 그 제조방법 | |

| JP3821707B2 (ja) | 半導体装置の製造方法 | |

| JP4489467B2 (ja) | 半導体装置の形成方法 | |

| KR100506823B1 (ko) | 반도체 장치의 제조 방법 | |

| JPH077773B2 (ja) | 半導体装置の製造方法 | |

| JP2000138375A (ja) | 半導体装置およびその製造方法 | |

| KR100525960B1 (ko) | 반도체 소자 형성방법 | |

| US20060068542A1 (en) | Isolation trench perimeter implant for threshold voltage control | |

| KR100282453B1 (ko) | 반도체 소자 및 그 제조방법 | |

| KR100728953B1 (ko) | 반도체 소자의 제조방법 | |

| KR100606288B1 (ko) | 자기정렬 공정을 이용한 고집적 vdmos 트랜지스터제조 방법 | |

| KR100506455B1 (ko) | 반도체소자의 형성방법 | |

| KR100579849B1 (ko) | 반도체 소자 및 그의 제조 방법 | |

| KR100485004B1 (ko) | 에스오아이 반도체 소자 및 그 제조 방법 | |

| KR100348314B1 (ko) | 반도체소자 및 그의 제조방법 | |

| KR100821467B1 (ko) | 반도체소자 및 그의 제조방법 | |

| KR100591124B1 (ko) | 반도체 소자 및 그의 제조 방법 | |

| KR100359164B1 (ko) | 트랜지스터의 제조 방법 | |

| KR950000152B1 (ko) | 게이트중첩 엘디디(ldd) 구조 씨모스(cmos) 장치의 제조방법 | |

| KR20030082820A (ko) | 단채널 현상을 방지할 수 있는 반도체 소자 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070330 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070424 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070723 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071016 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080523 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080617 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080624 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110704 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4148717 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120704 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130704 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |