JP4097635B2 - 電流検出回路及びそれを用いたスイッチング電源 - Google Patents

電流検出回路及びそれを用いたスイッチング電源 Download PDFInfo

- Publication number

- JP4097635B2 JP4097635B2 JP2004226094A JP2004226094A JP4097635B2 JP 4097635 B2 JP4097635 B2 JP 4097635B2 JP 2004226094 A JP2004226094 A JP 2004226094A JP 2004226094 A JP2004226094 A JP 2004226094A JP 4097635 B2 JP4097635 B2 JP 4097635B2

- Authority

- JP

- Japan

- Prior art keywords

- switch element

- output

- current

- voltage

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of DC power input into DC power output

- H02M3/02—Conversion of DC power input into DC power output without intermediate conversion into AC

- H02M3/04—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters

- H02M3/10—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of DC power input into DC power output without intermediate conversion into AC by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0009—Devices or circuits for detecting current in a converter

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

Description

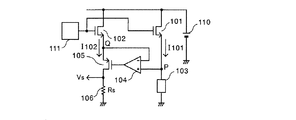

まず、差動アンプ104と補償トランジスタ105とにより、接続点Qに対する接続点Pの電位が正方向に増大すると接続点Qの電位が増大し、逆に負方向に増大すると接続点Qの電位が下降する。こうして、出力トランジスタ101のソース電位(接続点Pの電位)と補助トランジスタ102のソース電位(接続点Qの電位)とが実質的に等しくなる。また、出力トランジスタ101と補助トランジスタ102におけるそれぞれのドレイン電位及びゲート電位は回路構成から明らかなように等しい。従って、出力トランジスタ101と補助トランジスタ102の両トランジスタのドレイン、ゲート及びソースの各電位は等しく、出力トランジスタ101のソース電流I101と補助トランジスタ102のソース電流I102との比I101/I102は、一定値nに保たれる。即ち、補助トランジスタ102のソース電流I102は、 I102=I101/n となり、電流検出用抵抗106には出力トランジスタ101のソース電流I101に比例した検出電圧Vsが発生する。電流検出用抵抗106の抵抗値をRsとすると、検出電圧Vsは、 Vs=Rs・I101/n となる。

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位が等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、

を具備し、

前記オフセット電圧源は、オフセット用抵抗素子と、前記オフセット用抵抗素子に電流を流す電流源回路と、を有し、

前記オフセット用抵抗素子は、前記スイッチ素子と同チャネルのFETである。このように構成された本発明に係る電流検出回路は、スイッチ素子に流れる逆流電流を精度高く検出することができる。

前記電流検出回路は、

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位とが等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、を有し、

前記オフセット電圧源は、オフセット用抵抗素子と、前記オフセット用抵抗素子に電流を流す電流源回路と、を有し、

前記オフセット用抵抗素子は、前記スイッチ素子と同チャネルのFETである。このように構成された本発明に係るスイッチング電源は、スイッチ素子に流れる逆流電流を検出できる電流検出回路を用いることにより優れた過渡応答特性を有する。

また、本発明の第5の観点のスイッチング電源は、前記第4の観点の構成において、前記スイッチ素子と前記補助スイッチ素子とを同チャネルのFETで構成してもよい。

また、本発明の第6の観点のスイッチング電源は、前記第4の観点または第5の観点における前記補償回路を、前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と、前記補助スイッチ素子の出力電位が入力される差動アンプと、前記補助スイッチ素子の出力端子に接続され、前記差動アンプの出力によってインピーダンスが変化する可変インピーダンス素子と、を有するよう構成してもよい。

本発明の第8の観点のスイッチング電源は、前記第7の観点における前記整流回路が、整流スイッチ素子を有し、前記制御回路を前記スイッチ素子と前記整流スイッチ素子を交互にオンオフするよう構成してもよい。

本発明の第9の観点のスイッチング電源は、前記第7の観点における前記制御回路を、前記出力電圧が目標値を含む所定の範囲内にある時に、前記制御信号の変化幅を制限するよう構成してもよい。

また、本発明の第11の観点のスイッチング電源は、スイッチ素子と、前記スイッチ素子に接続されるインダクタと、前記インダクタの出力を整流する整流回路と、前記整流回路を流れる電流を平滑する平滑手段と、前記スイッチ素子の電流を検出する電流検出回路と、前記電流検出回路からの電流検出信号と前記平滑手段から出力される出力電圧が入力されて、前記出力電圧を制御するために前記スイッチ素子をオンオフする制御回路と、を具備するスイッチング電源であって、

前記電流検出回路は、

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位とが等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、を有し、

前記制御回路は、出力電圧を制御するための制御信号を生成し、前記電流検出回路からの電流検出信号が前記制御信号に追従するように、前記スイッチ素子をオンオフするよう構成され、

前記制御回路は、前記出力電圧が所定値以上の時に前記オフセット電圧を正の所定の電圧に増加し、前記出力電圧が所定値以下の時に前記オフセット電圧を負の所定の電圧へ減少するよう構成されている。このように構成された本発明に係るスイッチング電源は、スイッチ素子に流れる逆流電流を検出できる電流検出回路を用いることにより優れた過渡応答特性を有する。

また、本発明に係る電流検出回路を電流モード制御方式のスイッチング電源のスイッチ素子に流れる電流の検出に適用することにより、出力から入力へ電力が回生するように流れるスイッチ素子の逆流電流を検出・制御することが可能となる。このことにより、出力電流の急減などによって出力電圧に発生したオーバーシュートを速やかに抑制することができる。

また、本発明に係る電流検出回路を用いた電流モード制御方式のスイッチング電源において、電流検出回路のオフセットレベルを可変とし、出力条件の急変などの過渡時にはオフセットレベルを大きくすることによって検出レベルをシフトし、応答性を高速化するとともに通常動作への復帰もスムーズにできるという優れた効果を奏する。

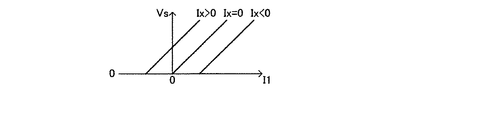

図1は、本発明に係る第1の実施の形態の電流検出回路の構成を示した回路図である。第1の実施の形態の電流検出回路において、出力トランジスタ1はスイッチ素子であり、NチャネルMISFET(Metal Insulator Semiconductor Field Effect:絶縁ゲート型電界効果トランジスタ)で構成されている。出力トランジスタに並設された補助トランジスタ2はNチャネルMISFETで構成されている。また、補償トランジスタ5はPチャネルMISFETで構成されている。図1において、3は負荷、4は差動アンプ、6は電流検出用抵抗、7はオフセット用抵抗、8は電流源回路、9は駆動回路、及び10は直流電源である。

第1の実施の形態の電流検出回路において、差動アンプ4と補償トランジスタ5とにより、接続点Qに対する接続点Pの電位が正方向に増大すると、接続点Qの電位が増大する。逆に、接続点Qに対する接続点Pの電位が負方向に増大すると、接続点Qの電位が下降する。こうして、オフセット用抵抗7と電流源回路8との接続点Pの電位と補助トランジスタ2のソース電位(接続点Qの電位)とが実質的に等しくなる。

電流源回路8の電流値Ixがゼロより小さい場合(Ix<0)、即ち、電流源回路8の電流がオフセット用抵抗7を逆方向に流れる場合には、Vs=0となる(−Ix・Rx/Ron)の値も正値を示す。この場合には、より大きな出力トランジスタ1のソース電流I1が検出可能となる。

尚、第1の実施の形態の電流検出回路において、オフセット用抵抗7及び電流源回路8によりオフセット電圧源が構成されている。また、差動アンプ4及び補償トランジスタ5により補償回路が構成されている。

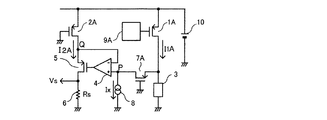

以下、本発明に係る第2の実施の形態の電流検出回路を添付の図3を用いて説明する。図3は第2の実施の形態の電流検出回路の構成を示した回路図である。

図3において、1Aはスイッチ素子であり、PチャネルMISFETである出力トランジスタ、2AはPチャネルMISFETである補助トランジスタ、3は負荷、4は差動アンプ、5はPチャネルMISFETである補償トランジスタ、6は電流検出用抵抗、7AはPチャネルMISFETであるオフセット用抵抗素子、8は電流源回路、9Aは駆動回路、10は直流電源である。第2の実施の形態の電流検出回路において、前述の図1に示した第1の実施の形態の電流検出回路の構成と異なるところは、出力トランジスタ1Aと補助トランジスタ2Aとオフセット用抵抗素子7AがPチャネルMISFETで構成されている点と、補助トランジスタ2Aのゲートとオフセット用抵抗素子7Aのゲートが接地されている点である。他の構成は図1に示した第1の実施の形態と同様であるので、その詳細な説明は省略する。

第2の実施の形態の電流検出回路において、差動アンプ4と補償トランジスタ5とにより、前述の第1の実施の形態と同様に、接続点Qに対する接続点Pの電位が正方向に増大すると、接続点Qの電位が増大する。逆に、接続点Qに対する接続点Pの電位が負方向に増大すると、接続点Qの電位が下降する。こうして、オフセット用抵抗素子7Aと電流源回路8との接続点Pの電位と補助トランジスタ2Aのドレイン電位(接続点Qの電位)とが実質的に等しくなる。

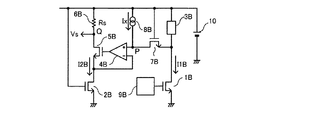

以下、本発明に係る第3の実施の形態の電流検出回路を添付の図4を用いて説明する。図4は第3の実施の形態の電流検出回路の構成を示した回路図である。

図4に示すように、第3の実施の形態の電流検出回路においては、負荷3Bが電源電位側に接続され、スイッチ素子である出力トランジスタ1Bがソースを接地したNチャネルMISFETで構成されている。図4において、補助トランジスタ2B、補償トランジスタ5B、及びオフセット用抵抗素子7Bは、全てNチャネルMISFETで構成されている。補助トランジスタ2Bとオフセット用抵抗素子7Bの各ゲートは電源電位Viとなっており、補助トランジスタ2Bのソースは接地されている。電流源回路8Bはオフセット用抵抗素子7Bへ電流を流し込むよう構成されており、電流検出用抵抗6Bは電源電位側に接続されている。

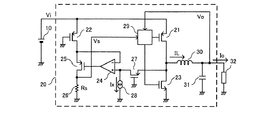

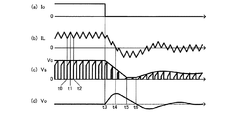

本発明に係る第4の実施の形態のスイッチング電源を添付の図5及び図6用いて説明する。図5は第4の実施の形態のスイッチング電源の構成を示した回路図であり、図6は第4の実施の形態のスイッチング電源における要部動作波形図である。第4の実施の形態のスイッチング電源は、前述の第2の実施の形態の電流検出回路の構成を有するスイッチング電源である。

制御回路29は、電流検出用抵抗26から検出電圧Vsが入力され、出力コンデンサ31から負荷32に供給される出力電圧Voを検出する。そして、制御回路29は、出力電圧Voを安定化させるように、検出電圧Vsの上限値を設定し、スイッチ素子21と同期整流トランジスタ23を交互にオンオフする。

まず、図6の波形図における左側部分(時刻t3まで状態)の通常動作について説明する。

時刻t0において、制御回路29からの駆動信号によって、同期整流トランジスタ23がオフ状態になり、スイッチ素子21がオン状態になると、直流電源10からスイッチ素子21を介してインダクタ30に電流が流れる。このインダクタ電流ILは、インダクタ30への印加電圧である降圧コンバータ20の入出力電圧差(Vi−Vo)に比例して時間と共に増加していく。補助トランジスタ22と差動アンプ24と補償トランジスタ25と電流検出用抵抗26とオフセット用抵抗素子27と電流源回路28は第2の実施の形態で示した電流検出回路と同様の構成であり、電流検出用抵抗26には次式(5)で表される検出電圧Vsが発生する。

出力電流Ioが急減した後、降圧コンバータ20は負荷32への電力供給が過剰となり、出力電圧Voは上昇する。制御回路29は上昇した出力電圧Voを元に戻すために、検出電圧Vsの上限設定値Vcを下げる。上限設定値Vcの低下に従い、スイッチ素子21のオン時間は短くなり、インダクタ電流ILは減少する。時刻t4において、インダクタ電流ILはゼロになるが、検出電圧Vsは Rs・Ix/k である。出力電圧Voの上昇はこの時点で停止する。時刻t4以降のインダクタ電流ILはゼロを下回り、やがて時刻t5において、インダクタ電流ILのピーク値が Vc=0 に相当する −(n/k)・Ix まで減少して出力電圧Voが下がり続ける。時刻t6において、出力電圧Voが目標値に近づくと、制御回路29は上限設定値Vcを上昇させ、出力電圧Voの低下を制動する。この後、出力電圧Voは減衰振動しながら目標値に達する。

尚、第4の実施の形態のスイッチング電源において、オフセット用抵抗素子27及び電流源回路28によりオフセット電圧源が構成されている。また、差動アンプ24及び補償トランジスタ25により補償回路が構成されている。

以下、本発明に係る第5の実施の形態のスイッチング電源を添付の図7及び図8用いて説明する。図7は第5の実施の形態のスイッチング電源の構成を示した回路図である。図8は第5の実施の形態のスイッチング電源におけるインダクタ電流ILと検出電圧Vsの関係を示す特性図である。図7において、図5に示した第4の実施の形態のスイッチング電源と同じ機能、構成を有する要素には同じ番号を付与し、その説明は省略する。第5の実施の形態のスイッチング電源において、第4の実施の形態の構成と異なるところは制御回路の構成であり、第4の実施の形態における制御回路29に出力電圧の急変に対応できる機能が追加されている。従って、第5の実施の形態においては、図5に示した第4の実施の形態の制御回路29と区別するため、制御回路29Aとし、その内部構成を以下具体的に説明する。

まず、通常時の動作を説明する。出力電圧Voは出力電圧検出回路291によって分圧され、誤差アンプ292において基準電圧Vrと比較される。このとき、基準電圧Vrは第1の電圧Vr1に設定されている。誤差アンプ292の出力である検出電圧の上限設定値Vcは、出力電圧Voが目標値よりも高いと低下し、出力電圧Voが目標値よりも低いと上昇する。クロック回路297からのクロック信号によりセットされたRSラッチ299はHレベルを出力し、駆動回路300によって同期整流トランジスタ23がオフ状態とされ、スイッチ素子21がオン状態とされる。この結果、直流電源10よりスイッチ素子21を介してインダクタ30に電流が流れる。このインダクタ電流ILの増加とともに検出電圧Vsも上昇する。

基準電圧Vrが第1の電圧Vr1から第2の電圧Vr2へと変化したため、誤差アンプ292は出力電圧Voを上昇させるために、上限設定値Vcを上昇させる。同時に、第1の比較器293は負入力端子への印加電圧が第2の電圧Vr2に上昇したので、出力がLレベルとなり、上限設定値Vcに対する第1の設定電圧Vc1以下とするクランプを解除する。このため、上限設定値Vcは第1の設定電圧Vc1より高くなり、インダクタ電流ILも通常動作での最大値より大きくなって、出力コンデンサ31への充電が急速に進む。そして、出力電圧Voが基準電圧源290の第2の電圧Vr2で設定される目標値に近づくと、第1の比較器293は出力がHレベルとなり、上限設定値Vcに対する第1の設定電圧Vc1以下になるようクランプがかかる。このため、上限設定値Vcは第1の設定電圧Vc1まで低下し、インダクタ電流ILは通常動作時の最大値に制限され、出力コンデンサ31への充電動作に制動が加わる。やがて上限設定値Vcは第1の設定電圧Vc1より下降し、出力電圧Voは基準電圧源290の第2の電圧Vr2により設定された目標値に安定化される。

基準電圧Vrが第2の電圧Vr2から第1の電圧Vr1へと変化したため、誤差アンプ292は出力電圧Voを低下させるために、上限設定値Vcを低下させる。同時に、第2の比較器294は正入力端子への印加電圧が第1の電圧Vr1に低下したので、出力がLレベルとなり、上限設定値Vcに対する第2の設定電圧Vc2以上とするクランプを解除する。このため、上限設定値Vcは第2の設定電圧Vc2より低くなり、インダクタ電流ILも通常動作での最小値より小さくなって逆流し、出力コンデンサ31からの放電が急速に進む。そして、出力電圧Voが第1の電圧Vr1で設定される目標値に近づくと、第2の比較器294は出力がHレベルとなり、上限設定値Vcに対する第2の設定電圧Vc2以上となるクランプがかかる。このため、上限設定値Vcは第2の設定電圧Vc2まで上昇し、インダクタ電流ILは通常動作時の最小値に制限され、出力コンデンサ31からの放電動作に制動が加わる。やがて上限設定値Vcは第2の設定電圧Vc2より上昇し、出力電圧Voは第1の電圧Vr1で設定される目標値に安定化される。

図8に示すように、第5の実施の形態のスイッチング電源において、インダクタ電流ILはその変化幅が通常動作時では第1の設定電圧Vc1と第2の設定電圧Vc2とで設定された範囲内に制限されており必要最小限に抑制されている。そして、必要な期間においては、インダクタ電流ILの制限範囲を外して、電力の供給と回生を急速に行っている。従って、第5の実施の形態のスイッチング電源は、出力電圧の急変などに高速に対応し、且つ通常動作への復帰もスムーズに行うことができる。

以下、本発明に係る第6の実施の形態のスイッチング電源を添付の図9及び図10用いて説明する。図9は第6の実施の形態のスイッチング電源の構成を示した回路図である。図10は第6の実施の形態のスイッチング電源におけるインダクタ電流ILと検出電圧Vsの関係を示す特性図である。

図9において、図5に示した第4の実施の形態のスイッチング電源と同じ機能、構成を有する要素には同じ番号を付与し、その説明は省略する。第6の実施の形態のスイッチング電源において、第4の実施の形態の構成と異なるところは電流源回路と制御回路の構成である。従って、第6の実施の形態においては、図5に示した第4の実施の形態の電流源回路28及び制御回路29と区別するため、電流源回路28B及び制御回路29Bとし、その内部構成を以下具体的に説明する。

図9において、電流源回路28Bは、オフセット用抵抗素子27のドレインからの電流を接地へ流す出す第1の電流源回路281と、オフセット用抵抗素子27のドレインに電流を流し込む第2の電流源回路282とを有している。第1の電流源回路281と第2の電流源回路282はそれぞれ制御端子を有しており、それらの制御端子にHレベルの信号が入力されると、第1の電流源回路281と第2の電流源回路282が活性化される構成である。

まず、通常時の動作を説明する。出力電圧Voは出力電圧検出回路291によって分圧され、誤差アンプ292によって基準電圧源290の基準電圧Vrと比較される。誤差アンプ292の出力である検出電圧の上限設定値Vcは、出力電圧Voが目標値よりも高いと低下し、出力電圧Voが目標値よりも低いと上昇する。クロック回路297からのクロック信号でセットされたRSラッチ299はHレベルを出力し、駆動回路300によって同期整流トランジスタ23がオフ状態とされ、スイッチ素子21がオン状態とされる。この状態において、直流電源10よりスイッチ素子21を介してインダクタ30に電流が流れる。このインダクタ電流ILの増加とともに検出電圧Vsも上昇する。検出電圧Vsが上限設定値Vcを上回ると電流比較器298の出力がHレベルとなり、リセットされたRSラッチ299はLレベルの信号を出力する。このLレベルの信号により、駆動回路300はスイッチ素子21をオフ状態とし、同期整流トランジスタ23をオン状態とする。この状態はクロック回路297からのクロック信号が発生するまでである。

基準電圧Vrが第1の電圧Vr1から第2の電圧Vr2へと変化したため、誤差アンプ292は出力電圧Voを上昇させるために、上限設定値Vcが上昇する。同時に、第1の比較器293Bは正入力端子への印加電圧が第2の電圧Vr2に上昇したので、出力V3がHレベルとなり、電流源回路28Bの第1の電流源回路281を活性化する。このため、第1の電流源回路281の電流によってオフセット用抵抗素子27には電圧が発生し、電流検出用抵抗26に発生する検出電圧Vsは、スイッチ素子21に流れる電流に比例する電圧から所定値だけ低下した電圧となる。即ち、上限設定値Vcは元のままであるが、検出電圧Vsが低くなるために、検出電圧Vsが上限設定値Vcに追従するように、スイッチ素子21のオン時間は長くなる。結果的にインダクタ電流ILは通常動作での最大値より大きくなり、出力コンデンサ31への充電が急速に進む。そして、出力電圧Voが基準電圧源290の第2の電圧Vr2で設定された目標値に近づくと、第1の比較器293Bは出力V3がLレベルとなり、第1の電流源回路281は不活性化されて電流を流さなくなる。このため、オフセット用抵抗素子27にはオフセット電圧は発生せず、電流検出用抵抗26に発生する検出電圧Vsは、スイッチ素子21に流れる電流に比例する電圧に戻り、検出電圧Vsが高くなる。結果的にインダクタ電流ILは通常動作時の最大値に制限され、出力コンデンサ31への充電に制動が加わった状態となる。やがて上限設定値Vcは下降し、出力電圧Voは基準電圧源290の第2の電圧Vr2で設定された目標値に安定化される。

基準電圧Vrが第2の電圧Vr2から第1の電圧Vr1へと変化したため、誤差アンプ292は出力電圧Voを低下させるために、上限設定値Vcが低下する。同時に、第2の比較器294Bは負入力端子への印加電圧が第1の電圧Vr1に低下したため、出力V4がHレベルとなり、電流源回路28Bの第2の電流源回路282を活性化する。このため、第2の電流源回路282の電流によってオフセット用抵抗素子27には電圧が発生し、電流検出用抵抗26に発生する検出電圧Vsは、スイッチ素子21に流れる電流に比例する電圧から所定値だけ上昇した電圧となる。即ち、上限設定値Vcは元のままであるが、検出電圧Vsが高くなるために、検出電圧Vsが上限設定値Vcに追従するように、スイッチ素子21のオン時間は短くなる。結果的にインダクタ電流ILも通常動作での最小値より小さくなって逆流し、出力コンデンサ31からの放電が急速に進む。そして、出力電圧Voが基準電圧源290の第1の電圧Vr1で設定された目標値に近づくと、第2の比較器294Bは出力V4がLレベルとなり、第2の電流源回路282は不活性化されて電流を流さなくなる。このため、オフセット用抵抗素子27にはオフセット電圧は発生せず、電流検出用抵抗26に発生する検出電圧Vsは、スイッチ素子21に流れる電流に比例する電圧に戻り、検出電圧Vsが低くなる。結果的にインダクタ電流ILは通常動作時の最小値に制限され、出力コンデンサ31からの放電に制動が加わった状態となる。やがて上限設定値Vcは上昇し、出力電圧Voは基準電圧源290の第1の電圧Vr1で設定された目標値に安定化される。

図10に示すように、第6の実施の形態のスイッチング電源においては、インダクタ電流ILに対する検出電圧Vsの関係をインダクタ電流ILの零値を挟んで前後にシフトさせることにより、電力の供給と回生を急速に行うことができる。この結果、第6の実施の形態のスイッチング電源は、出力電圧の急変などに高速に対応することができ、且つ通常動作への復帰もスムーズに行うことができる。

尚、上記の各実施の形態において、スイッチ素子としてMISFETで構成した例で説明したが、このMISFETはMOSFETを含む電界効果トランジスタであり、MISFETとしてMOSFETを使用しても同様の効果を奏する。

2 補助トランジスタ

3 負荷

4 差動アンプ

5 補償トランジスタ

6 電流検出用抵抗

7 オフセット用抵抗

8 電流源回路

9 駆動回路

10 直流電源

21 スイッチ素子

22 補助トランジスタ

23 同期整流トランジスタ

24 差動アンプ

25 補償トランジスタ

26 電流検出用抵抗

27 オフセット用抵抗素子

28 電流源回路

29 制御回路

30 インダクタ

31 出力コンデンサ

32 負荷

Claims (11)

- スイッチ素子の電流を検出する電流検出回路であって、

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位が等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、

を具備し、

前記オフセット電圧源は、オフセット用抵抗素子と、前記オフセット用抵抗素子に電流を流す電流源回路と、を有し、

前記オフセット用抵抗素子は、前記スイッチ素子と同チャネルのFETである電流検出回路。 - 前記スイッチ素子と前記補助スイッチ素子は同チャネルのFETである請求項1に記載の電流検出回路。

- 前記補償回路は、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と、前記補助スイッチ素子の出力電位が入力される差動アンプと、

前記補助スイッチ素子の出力端子に接続され、前記差動アンプの出力によってインピーダンスが変化する可変インピーダンス素子と、を有する請求項1または2に記載の電流検出回路。 - スイッチ素子と、前記スイッチ素子に接続されるインダクタと、前記インダクタの出力を整流する整流回路と、前記整流回路を流れる電流を平滑する平滑手段と、前記スイッチ素子の電流を検出する電流検出回路と、前記電流検出回路からの電流検出信号と前記平滑手段から出力される出力電圧が入力されて、前記出力電圧を制御するために前記スイッチ素子をオンオフする制御回路と、を具備するスイッチング電源であって、

前記電流検出回路は、

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位とが等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、を有し、

前記オフセット電圧源は、オフセット用抵抗素子と、前記オフセット用抵抗素子に電流を流す電流源回路と、を有し、

前記オフセット用抵抗素子は、前記スイッチ素子と同チャネルのFETであるスイッチング電源。 - 前記スイッチ素子と前記補助スイッチ素子は同チャネルのFETである請求項4に記載のスイッチング電源。

- 前記補償回路は、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と、前記補助スイッチ素子の出力電位が入力される差動アンプと、

前記補助スイッチ素子の出力端子に接続され、前記差動アンプの出力によってインピーダンスが変化する可変インピーダンス素子と、を有する請求項4または5に記載のスイッチング電源。 - 前記制御回路は、出力電圧を制御するための制御信号を生成し、前記電流検出回路からの電流検出信号が前記制御信号に追従するように、前記スイッチ素子をオンオフするよう構成された請求項6に記載のスイッチング電源。

- 前記整流回路は整流スイッチ素子を有し、前記制御回路は前記スイッチ素子と前記整流スイッチ素子を交互にオンオフするよう構成された請求項7に記載のスイッチング電源。

- 前記制御回路は、前記出力電圧が目標値を含む所定の範囲内にある時に、前記制御信号の変化幅を制限するよう構成された請求項7に記載のスイッチング電源。

- 前記制御回路は、前記出力電圧が所定値以上の時に前記オフセット電圧を正の所定の電圧に増加し、前記出力電圧が所定値以下の時に前記オフセット電圧を負の所定の電圧へ減少するよう構成された請求項7に記載のスイッチング電源。

- スイッチ素子と、前記スイッチ素子に接続されるインダクタと、前記インダクタの出力を整流する整流回路と、前記整流回路を流れる電流を平滑する平滑手段と、前記スイッチ素子の電流を検出する電流検出回路と、前記電流検出回路からの電流検出信号と前記平滑手段から出力される出力電圧が入力されて、前記出力電圧を制御するために前記スイッチ素子をオンオフする制御回路と、を具備するスイッチング電源であって、

前記電流検出回路は、

前記スイッチ素子と並設されて、少なくとも前記スイッチ素子がオン状態の時にはオン状態である補助スイッチ素子と、

オフセット電圧を発生するオフセット電圧源と、

前記スイッチ素子の出力電位に前記オフセット電圧を加えた電位と前記補助スイッチ素子の出力電位とが等しくなるように前記補助スイッチ素子の出力電流を調整する補償回路と、を有し、

前記制御回路は、出力電圧を制御するための制御信号を生成し、前記電流検出回路からの電流検出信号が前記制御信号に追従するように、前記スイッチ素子をオンオフするよう構成され、

前記制御回路は、前記出力電圧が所定値以上の時に前記オフセット電圧を正の所定の電圧に増加し、前記出力電圧が所定値以下の時に前記オフセット電圧を負の所定の電圧へ減少するよう構成されたスイッチング電源。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004226094A JP4097635B2 (ja) | 2004-08-02 | 2004-08-02 | 電流検出回路及びそれを用いたスイッチング電源 |

| US11/195,835 US7323850B2 (en) | 2004-08-02 | 2005-08-02 | Current detection circuit and switching power supply using the same |

| US11/843,896 US7479771B2 (en) | 2004-08-02 | 2007-08-23 | Current detection circuit and switching power supply |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004226094A JP4097635B2 (ja) | 2004-08-02 | 2004-08-02 | 電流検出回路及びそれを用いたスイッチング電源 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006050724A JP2006050724A (ja) | 2006-02-16 |

| JP4097635B2 true JP4097635B2 (ja) | 2008-06-11 |

Family

ID=35756775

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004226094A Expired - Lifetime JP4097635B2 (ja) | 2004-08-02 | 2004-08-02 | 電流検出回路及びそれを用いたスイッチング電源 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7323850B2 (ja) |

| JP (1) | JP4097635B2 (ja) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI249090B (en) * | 2003-01-16 | 2006-02-11 | Shindengen Electric Mfg | Switching circuit |

| JP3916163B2 (ja) * | 2004-02-19 | 2007-05-16 | ローム株式会社 | 電流方向検出回路及びそれを備えたスイッチングレギュレータ |

| JP4980588B2 (ja) * | 2005-06-21 | 2012-07-18 | ローム株式会社 | 降圧型スイッチングレギュレータ、その制御回路、ならびにそれを用いた電子機器 |

| JP4842614B2 (ja) * | 2005-10-27 | 2011-12-21 | ルネサスエレクトロニクス株式会社 | 電流検出回路 |

| JP5055517B2 (ja) * | 2006-02-17 | 2012-10-24 | 日本電産サンキョー株式会社 | ポンプシステム |

| US7336085B2 (en) * | 2006-02-17 | 2008-02-26 | Infineon Technologies Ag | Current sensing circuit |

| US20080266911A1 (en) * | 2007-04-30 | 2008-10-30 | O2Micro Inc | Current sensing circuits and methods for a converter |

| JP2008295158A (ja) * | 2007-05-23 | 2008-12-04 | Panasonic Corp | 電源装置 |

| JP5217319B2 (ja) * | 2007-09-12 | 2013-06-19 | 株式会社リコー | 定電流出力制御型スイッチングレギュレータ |

| US8004866B2 (en) * | 2008-01-03 | 2011-08-23 | Teknic, Inc. | Method and apparatus to remove energy from DC loads |

| JP4702403B2 (ja) * | 2008-06-06 | 2011-06-15 | ミツミ電機株式会社 | 充電制御用半導体集積回路 |

| KR100925394B1 (ko) * | 2008-09-25 | 2009-11-09 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| CN102246402B (zh) * | 2008-12-09 | 2015-01-28 | 惠普开发有限公司 | 电源电路 |

| JP5135199B2 (ja) * | 2008-12-22 | 2013-01-30 | パナソニック株式会社 | 電流検出回路およびそれを用いた電圧コンバータ |

| US8232781B2 (en) * | 2008-12-23 | 2012-07-31 | Stmicroelectronics S.R.L. | Device for measuring the current flowing through a power transistor of a voltage regulator |

| US7911260B2 (en) * | 2009-02-02 | 2011-03-22 | Infineon Technologies Ag | Current control circuits |

| DE102009001899B4 (de) | 2009-03-26 | 2024-01-18 | Robert Bosch Gmbh | Messen eines Laststroms eines Unterbrechers |

| EP2239591B1 (en) * | 2009-04-08 | 2012-05-30 | Alcatel Lucent | Use of a current monitor in a control device for controlling a switching stage of an envelope tracking modulator |

| JP5586211B2 (ja) * | 2009-11-17 | 2014-09-10 | 株式会社東芝 | Dc−dcコンバータおよび半導体集積回路 |

| JP2011220767A (ja) * | 2010-04-07 | 2011-11-04 | Panasonic Corp | 電流検出回路 |

| WO2012077165A1 (ja) * | 2010-12-08 | 2012-06-14 | パナソニック株式会社 | 電力供給回路、電力供給方法及び電力供給システム |

| EP2515126A1 (en) | 2011-04-19 | 2012-10-24 | Dialog Semiconductor GmbH | Bidirectional current sense |

| US10041982B2 (en) | 2012-08-15 | 2018-08-07 | Texas Instruments Incorporated | Switch mode power converter current sensing apparatus and method |

| JP2014226026A (ja) * | 2013-04-15 | 2014-12-04 | ローム株式会社 | Dc/dcコンバータおよびそれを用いた電子機器 |

| US20140361790A1 (en) * | 2013-06-11 | 2014-12-11 | Advantest Corporation | Drive circuit, switch apparatus, and test apparatus |

| US10128749B2 (en) * | 2014-05-12 | 2018-11-13 | Texas Instruments Incorporated | Method and circuitry for sensing and controlling a current |

| US10156592B2 (en) | 2015-12-30 | 2018-12-18 | Nxp Usa, Inc. | Current sensing circuit and method |

| US9742398B2 (en) * | 2016-01-13 | 2017-08-22 | Texas Instruments Incorporated | Methods and apparatus for sensing current through power semiconductor devices with reduced sensitivity to temperature and process variations |

| JP7008478B2 (ja) * | 2017-11-15 | 2022-01-25 | 新日本無線株式会社 | 電流センスアンプ回路及びスイッチング電源装置 |

| JP6937705B2 (ja) * | 2018-01-30 | 2021-09-22 | ルネサスエレクトロニクス株式会社 | 半導体装置、電流検出方法および負荷駆動システム |

| JP7079158B2 (ja) * | 2018-06-27 | 2022-06-01 | エイブリック株式会社 | ボルテージレギュレータ |

| CN109254188B (zh) * | 2018-10-09 | 2023-12-01 | 成都铱通科技有限公司 | 一种适用于开关电源的高速电流检测电路 |

| KR102052947B1 (ko) * | 2019-04-17 | 2020-01-22 | 시스트로닉스 주식회사 | IoT 기반 온열매트 제어 장치 및 그 제어 장치에서 신호 처리 방법 |

| JP7560722B2 (ja) | 2020-09-09 | 2024-10-03 | ミツミ電機株式会社 | 電流検出回路、スイッチ回路 |

| JP7434129B2 (ja) * | 2020-09-24 | 2024-02-20 | 株式会社東芝 | 電流検出回路、電流検出システム、および電源回路 |

| CN113534884B (zh) * | 2021-08-10 | 2022-08-12 | 江苏应能微电子有限公司 | 一种低功耗采样mosfet功率管电流的电路 |

| CN115833560B (zh) * | 2022-11-24 | 2023-07-25 | 华南理工大学 | 一种SenseFET型全波电感电流传感器 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3577019A (en) * | 1968-09-24 | 1971-05-04 | Gen Electric | Insulated gate field effect transistor used as a voltage-controlled linear resistor |

| JPH04134271A (ja) | 1990-09-27 | 1992-05-08 | Nec Corp | 出力回路 |

| JP2000166279A (ja) * | 1998-12-01 | 2000-06-16 | Mitsubishi Electric Corp | 電流検出回路 |

| JP2000092824A (ja) | 1998-09-10 | 2000-03-31 | Matsushita Electric Ind Co Ltd | スイッチングレギュレータおよびlsiシステム |

| EP1115203B1 (en) | 1999-06-18 | 2006-11-08 | Matsushita Electric Industrial Co., Ltd. | Output controller |

| US6166528A (en) | 1999-11-02 | 2000-12-26 | Fairchild Semiconductor Corporation | Lossless current sensing in buck converters working with low duty cycles and high clock frequencies |

| JP2002281743A (ja) | 2001-03-19 | 2002-09-27 | Hitachi Ltd | 半導体集積回路および携帯用電子機器 |

| CN100480940C (zh) * | 2002-04-03 | 2009-04-22 | 国际整流器公司 | 同步降压转换器改进 |

| US6850401B2 (en) * | 2002-05-28 | 2005-02-01 | Matsushita Electric Industrial Co., Ltd. | DC-DC converter |

| JP4360833B2 (ja) | 2002-05-28 | 2009-11-11 | パナソニック株式会社 | Dc−dcコンバータ |

| US6798177B1 (en) * | 2002-10-15 | 2004-09-28 | Arques Technology, Inc. | Boost-buck cascade converter for pulsating loads |

| US7102415B1 (en) * | 2004-03-26 | 2006-09-05 | National Semiconductor Corporation | Trip-point detection circuit |

| US7268526B1 (en) * | 2004-04-21 | 2007-09-11 | National Semiconductor Corporation | Switch mode power supply control circuit |

| US7327149B2 (en) * | 2005-05-10 | 2008-02-05 | Power-One, Inc. | Bi-directional MOS current sense circuit |

-

2004

- 2004-08-02 JP JP2004226094A patent/JP4097635B2/ja not_active Expired - Lifetime

-

2005

- 2005-08-02 US US11/195,835 patent/US7323850B2/en not_active Expired - Lifetime

-

2007

- 2007-08-23 US US11/843,896 patent/US7479771B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US7479771B2 (en) | 2009-01-20 |

| US20060028192A1 (en) | 2006-02-09 |

| US7323850B2 (en) | 2008-01-29 |

| JP2006050724A (ja) | 2006-02-16 |

| US20080018387A1 (en) | 2008-01-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4097635B2 (ja) | 電流検出回路及びそれを用いたスイッチング電源 | |

| US7868599B2 (en) | Method of optimum current blanking time implementation in current sense circuit | |

| US8193793B2 (en) | DC-DC converter | |

| KR101037306B1 (ko) | 스위칭 레귤레이터 및 그 펄스폭 조정 방법 | |

| JP6039327B2 (ja) | スイッチング電源装置 | |

| US20060113979A1 (en) | Power supply driver circuit | |

| TW200843306A (en) | Current detector circuit and current mode switching regulator | |

| US7403365B2 (en) | Over-current detection circuit and method for power-supply device | |

| JP2005086931A (ja) | スイッチング電源装置とそれに用いられる半導体集積回路 | |

| JP2010136510A (ja) | 降圧型スイッチングレギュレータ | |

| US7436162B2 (en) | Buck converter having improved transient response to load step down | |

| JP2009207242A (ja) | 電源装置 | |

| JP2009071920A (ja) | 同期整流型スイッチングレギュレータ | |

| WO2007114466A1 (ja) | スイッチング制御回路 | |

| JP6610468B2 (ja) | 半導体装置 | |

| US7683593B2 (en) | Current sensing in a power converter | |

| WO2021054027A1 (ja) | 電源装置 | |

| JP4717449B2 (ja) | スイッチング・レギュレータ回路 | |

| JP2008092618A (ja) | 昇圧コンバータ | |

| JP2007053892A (ja) | Dc−dcコンバータ | |

| US10020733B2 (en) | Adaptive controller for a voltage converter | |

| JP6588634B2 (ja) | スイッチングレギュレータ、半導体集積回路、及び電子機器 | |

| JP4644826B2 (ja) | スイッチング電源回路 | |

| JP2007501598A (ja) | 同期整流器の出力電圧制御 | |

| JP2003111394A (ja) | Dc−dcコンバータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070202 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070814 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071015 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20071015 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080311 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4097635 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110321 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110321 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120321 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130321 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130321 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140321 Year of fee payment: 6 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |