JP4097510B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4097510B2 JP4097510B2 JP2002336236A JP2002336236A JP4097510B2 JP 4097510 B2 JP4097510 B2 JP 4097510B2 JP 2002336236 A JP2002336236 A JP 2002336236A JP 2002336236 A JP2002336236 A JP 2002336236A JP 4097510 B2 JP4097510 B2 JP 4097510B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- thin film

- semiconductor thin

- etching

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/435—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material

- B41J2/447—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using arrays of radiation sources

- B41J2/45—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using arrays of radiation sources using light-emitting diode [LED] or laser arrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/49105—Connecting at different heights

- H01L2224/49109—Connecting at different heights outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0093—Wafer bonding; Removal of the growth substrate

Description

【発明の属する技術分野】

本発明は、例えば、電子写真式プリンタに使用されるLEDプリントヘッドのような半導体装置及びその製造方法に関する。

【0002】

【従来の技術】

図26は、従来のLEDプリントヘッド900の一部を概略的に示す斜視図であり、図27は、図26のLEDプリントヘッドに備えることができるLEDアレイチップの一例としてLEDアレイチップ902の一部を示す平面図である。図示されたLEDプリントヘッド900は、基板901上に備えられたLEDアレイチップ902の電極パッド903と、基板901上に備えられた駆動ICチップ904の電極パッド905とをボンディングワイヤ906で接続し、駆動ICチップ904の電極パッド909と基板901の電極パッド910とをボンディングワイヤ911で接続した構造を持つ。

【0003】

また、下記の特許文献1には、薄膜構造の発光素子が開示されている。この特許文献1には、発光素子を構成する各層を成長させた後に、エッチング液により素子分離を行うことが記載されている。

【0004】

【特許文献1】

特開平10−063807号公報(図11、段落0034及び0035)

【0005】

【発明が解決しようとする課題】

しかしながら、LEDプリントヘッド900では、LEDアレイチップ902と駆動ICチップ904とをボンディングワイヤ906によって接続していたので、LEDアレイチップ902と駆動ICチップ904のそれぞれにワイヤボンド用の大きな(例えば、100μm×100μm)電極パッド903及び905を設ける必要があった。このため、LEDアレイチップ902の面積を小さくすることが困難であり、その結果、材料コストを削減することが困難であった。また、LEDアレイチップ902において発光部907として機能する領域は、表面から5μm程度の深さの領域である。しかし、LEDプリントヘッド900では、安定したワイヤボンドの歩留まりを確保するために、LEDアレイチップ902の厚さは駆動ICチップ904の厚さ(例えば、250μm〜300μm)と同程度にする必要があった。このため、LEDプリントヘッド900においては、LEDアレイチップ902の材料コストを削減することが困難であった。

【0006】

さらに、特許文献1には、薄膜構造の発光素子が開示されているが、発光素子にはハンダボール用の電極パッドが備えられており、この電極パッドにハンダボールを介して個別電極が接続されている。このように、特許文献1の薄膜構造の発光素子は電極パッドを備えているので、その面積を縮小することが困難であった。

【0007】

さらにまた、特許文献1には、エッチング液により素子分離を行うことが記載されている。しかし、半導体薄膜を構成する各層の材料又はエッチング液の種類によっては、半導体薄膜を分離又は剥離するためにエッチングすべき部分以外の部分が、例えば、半導体薄膜が含む半導体素子が備えている、層間絶縁膜や配線材料などがエッチングされてしまうという技術的な課題についての記載はない。

【0008】

そこで、本発明は上記したような従来技術の課題を解決するためになされたものであり、その目的とするところは、小型化及び材料コストの低減を図ることができる半導体装置及びLEDヘッド、並びに、小型化及び材料コストの低減を図ることができる且つエッチング処理に起因する歩留まりの低下の少ない半導体装置の製造方法を提供することにある。

【0009】

【課題を解決するための手段】

本発明に係る半導体装置の製造方法は、第2の基板上に剥離層を形成する工程と、剥離層上に、半導体素子の全部又は一部の構造を含む半導体薄膜を形成する工程と、半導体薄膜上の所定領域に誘電体膜を形成する工程と、半導体薄膜上の誘電体膜を覆う領域に保護層を形成する工程とを有する。さらに、本発明に係る半導体装置の製造方法は、半導体薄膜の保護層で覆われていない領域をエッチングして剥離層に届くエッチング溝を形成することによって、半導体薄膜を分離する工程と、剥離層をエッチングして半導体薄膜を剥離可能な個別の半導体薄膜にする工程と、誘電体膜を備えた個別の半導体薄膜を保持し、第1の基板の表面に貼り付ける工程と、個別の半導体薄膜を貼り付ける工程の前又は後に、保護層を除去する工程とを有する。また、保護層は、エッチング溝の形成工程及び剥離層のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される。ここで、耐エッチング性とは、保護層となる材料そのものが、エッチング溝の形成工程及び剥離層のエッチング工程において使用されるエッチング剤によって、溶解、分解、破壊されないこと、また、保護層と、保護層が接する半導体薄膜表面との界面に該エッチング液が浸透することによって、該界面の密着性が破壊されないこと、あるいは、該エッチング液が保護層を浸透し保護層と半導体薄膜界面に到達することによって、該界面の密着性が破壊されないこと、など保護層が半導体薄膜表面を保護する機能が失われないことを意味する。

【0010】

【発明の実施の形態】

<第1の実施形態>

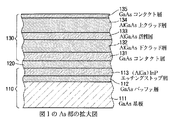

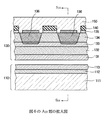

図1から図8までは、本発明の第1の実施形態に係る半導体装置の製造方法(即ち、LED/駆動IC複合チップ100の製造プロセス)を概略的に示す断面図である。また、図9は、図1のA9部の拡大図であり、図10は、図3のA10部の拡大図である。さらに、図11は、図5の概略的な斜視図であり、図12は、図5のA12部の拡大平面図である。さらにまた、図13は、図6のA13部の拡大図であり、図14は、図13をS14−S14線で切る面を概略的に示す断面図である。また、図15は、図8の拡大平面図であり、図16は、図8のA16部の概略的な斜視図である。

【0011】

図に基づいて、第1の実施形態に係るLED/駆動IC複合チップ100の製造プロセスを説明する。先ず、図1に示されるように、半導体薄膜製造用の基板110を用意し、この基板110上に剥離層120を形成し、この剥離層120上に半導体薄膜としてのエピタキシャルフィルム130を形成する。ここで、エピタキシャルフィルム130は、半導体薄膜として半導体薄膜製造用基板から剥離する予定の、あるいは、半導体薄膜として半導体薄膜製造用基板から剥離した、半導体素子として機能させるための半導体エピタキシャル層を示している。エピタキシャルフィルム130の製造は、有機金属化学蒸着法(MOCVD法)や分子線エピタキシー法(MBE法)等によって行うことができる。

【0012】

図1に示される製造プロセスを、図9を参照して詳細に説明する。図9に示されるように、基板110は、例えば、GaAs基板111上に、GaAsバッファ層112、及び剥離層のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される(AlGa)InPエッチングストップ層113を順に成膜した構造を持つ。また、図9に示されるように、剥離層120は、例えば、AlAs剥離層である。さらにまた、図9に示されるように、エピタキシャルフィルム130は、剥離層120上に、GaAsコンタクト層(1)131(例えば、n型GaAs層131)、AlGaAs下クラッド層132(n型AlxGa1−xAs層132)、AlGaAs活性層133(n型AlyGa1−yAs層133)、AlGaAs上クラッド層134(n型AlzGa1−zAs層134)、及びGaAsコンタクト層(2)135(n型GaAs層135)を順に成膜した構造を持つ。なお、0<x≦1、0≦y<1、0<z≦1である。また、Al組成は、y<x且つy<z(例えば、x=z=0.4、y=0.1)とすることができる。n型GaAs層131の厚さは、約10nm(=約0.01μm)であり、n型AlxGa1−xAs層132の厚さは、約0.5μmであり、n型AlyGa1−yAs層133の厚さは、約1μmであり、n型AlzGa1−zAs層134の厚さは、約0.5μmであり、n型GaAs層135の厚さは、約10nm(=約0.01μm)である。この場合には、エピタキシャルフィルム130の厚さは、約2.02μmとなる。ただし、各層の厚さは、上記値に限定されない。また、エピタキシャルフィルム130の材料として、(AlxGa1−x)yIn1−yP(ここで、0<x<1且つ0<y<1である。)、GaN、AlGaN、InGaN等の他の材料を含む半導体エピタキシャル層を用いてもよい。また、基板110は、(AlxGa1−x)yIn1−yP層113を設けない構造などの変形も可能である。

【0013】

次に、図2に示されるように、エピタキシャルフィルム130の半導体素子形成領域130bにLED(図12の発光領域130c)を形成する。次に、図3に示されるように、エピタキシャルフィルム130上の所定領域に誘電体膜140を形成する。誘電体膜140は、例えば、SiO2、Si3O4、SiN、酸化アルミニウム、窒化アルミニウムの内のいずれかの材料で構成することができる。誘電体膜140は、例えば、LED上に開口部を持つ。

【0014】

LEDの形成方法としては、図10に示されるように、n型AlyGa1−yAs層133、n型AlzGa1−zAs層134、及びn型GaAs層135に固相拡散法等により亜鉛(Zn)からなるP型不純物を拡散しZn拡散領域136を形成する方法がある。その後、固相拡散時に用いた拡散源膜は除去する。その後、GaAsコンタクト層のZn拡散領域表面を露出させる。次に、GaAsコンタクト層内に形成されたpn接合面を含む領域を除去することが望ましい。なお、素子作製において最終的には、電極配線によって、pn間のショートが発生しないように、n型AlzGa1−zAs層134の表面及びAlzGa1−zAs層に形成されたZn拡散領域表面の一部(AlzGa1−zAs層表面のpn接合領域を含むpn接合近傍の領域)を被覆するように層間絶縁膜を設けてから個別電極配線などを形成する必要があることは言うまでもない。第1の実施形態においては、n型AlzGa1−zAs層134の表面及びAlzGa1−zAs層に形成されたZn拡散領域表面の一部(AlzGa1−zAs層表面のpn接合領域を含むpn接合近傍の領域)を被覆するように絶縁膜140が形成されている。Zn拡散領域136の拡散フロントを、n型AlyGa1−yAs層133の内部に位置するように構成することにより、pn接合を介して注入された少数キャリアは、n型AlyGa1−yAs層133内に閉じ込められ、高い発光効率が得られる。即ち、図10に示されるような構造を採用することによって、エピタキシャルフィルム130の厚さを約2μmと薄くすることができ、発光効率を高くすることができる。なお、上記説明においては、エピタキシャル層としてホモ接合型LEDの製造方法を説明したが、ヘテロ接合型LEDとすることもできる。ここで、ホモ接合型とは、pn接合面が単一の半導体層内に形成されている接合方式を指し示しており、本実施形態の説明で具体的に説明した、同一導電型の半導体積層構造に逆導電型の不純物を選択的にドーピングしたような接合形態も含む。また、ヘテロ接合型とは、pn接合面が異種半導体界面に位置する接合方式を指し示しており、例えば、n型AlxGa1−xAs層132とp型AlyGa1−yAs層をエピタキシャル成長により積層した構造を備えたような接合形態を意味する。

【0015】

次に、図4に示されるように、エピタキシャルフィルム130上の誘電体膜140を覆う領域に保護層150を形成する。保護層150は、後述するエッチング溝の形成工程及び剥離層120のエッチング工程において使用されるエッチング液に対して耐エッチング性を持つ材料で構成される。保護層150は、有機材料、例えば、レジスト材料などのポリマー材料やワックス材料から構成される。

【0016】

次に、図5及び図11に示されるように、エッチング液を用いてエピタキシャルフィルム130の保護層150で覆われていない領域をエッチングして剥離層120に届くエッチング溝160を形成して、エピタキシャルフィルム130を分離し、個別のエピタキシャルフィルム130aとする。エッチング液としては、燐酸過水(燐酸、過酸化水素水を含む水溶液)を用いる。なお、エッチング液として、クエン酸及び過酸化水素水を含むエッチング液を用いることもできる。

【0017】

次に、図6、図13及び図14に示されるように、エッチング液を用いてエピタキシャルフィルム130aの下の剥離層120をエッチングして除去して、エピタキシャルフィルム130aを剥離可能にする。エッチング液として、例えば、フッ酸(10%HF液)を用いる。

【0018】

図12に示されるように、誘電体膜140の短辺の端部140aは、エピタキシャルフィルム130aの端部より距離L1だけ内側に位置する。また、図12に示されるように、誘電体膜140の長辺の端部140bは、エピタキシャルフィルム130aの端部より距離L2だけ内側に位置する。距離L1及びL2の長さは、▲1▼エッチング液(又はエッチングガス)の種類や特性、▲2▼エッチング時間、▲3▼誘電体膜140の材料、▲4▼保護層150の材料や厚さ等の各種要因に基づいて決定すればよく、少なくとも、エッチング液が保護層150を浸透して誘電体膜140に達しない長さとする。

【0019】

次に、図7(a)及び(b)に示されるように、集積回路171が形成されたシリコン基板170を用意し、その表面の集積回路171に隣接する領域にメタル層180を密着形成する。次に、メタル層180上に、図6の製造プロセスで剥離可能となった個別のエピタキシャルフィルム130aを貼り付ける。個別のエピタキシャルフィルム130aの保持方法、すなわち、個別のエピタキシャルフィルム130aを貼り付ける予定の位置まで搬送し、位置合わせを行い、所定の位置にエピタキシャルフィルム130aを置くためのエピタキシャルフィルムの移送方法、としては、エピタキシャルフィルムを移送治具に吸着/脱離が可逆的に複数回行える保持方法(例えば、気圧差を利用する吸着(吸引)、磁気的吸着、電気的吸着、接着剤等のいずれかを用いて保持部材に保持する方法)を用いる。なお、シリコン基板170にエピタキシャルフィルム130aを貼り付ける工程の前又は後に、保護層150を除去する。また、エピタキシャルフィルム130aの厚さが厚くなると、個別配線層190に段切れが発生する確率が高くなる。このような不良の発生を回避するためには、エピタキシャルフィルム130の厚さを、約10μm以下にすることが望ましい。ただし、ポリイミドなどを使って段差領域の平坦化を図るなどの段差領域を横切る配線の断線防止のための方策を実施するなどして、エピタキシャルフィルム130の厚さを、10μmを超える厚さにすることもできる。

【0020】

メタル層180は、例えば、パラジウム若しくは金、又は、パラジウムと金の積層膜等からなる。メタル層180は、その上に貼り付けられたエピタキシャルフィルム130aをシリコン基板170の集積回路102形成領域近傍に固定する機能と、エピタキシャルフィルム130aの下面の共通端子領域(図示せず)とシリコン基板170の共通端子領域(図示せず)とを電気的に接続する機能とを持つ。メタル層180とエピタキシャルフィルム130a内の共通端子領域との間、及び、メタル層180とシリコン基板170の共通端子領域との間には、オーミックコンタクトが形成されることが望ましい。ここで、LEDエピタキシャルフィルム(LEDエピフィルム)130a内の共通端子領域とは、メタル層180と接するエピタキシャル層全面を示しており、本実施形態で具体的に述べれば、n型GaAs層131の共通電位側(n電極側)となる表面全面を意味する。また、Si基板170の共通端子領域とは、メタル層180と接するSi基板の表面領域を示しており、本実施形態で具体的に述べれば、LEDを駆動するための共通電位側(n電極側)となる領域を意味する。メタル層180は、何らかの手段によって、例えば、メタル配線によって、素子を駆動するための集積回路の共通電位端子と接続されている。なお、メタル層180を、シリコン基板170表面の集積回路102が形成されている領域上に(全部又は一部が重なるように)、絶縁膜(図示せず)を介して、形成してもよい。

【0021】

次に、図8、図15、及び図16に示されるように、LED130cから誘電体膜140上を経由してシリコン基板170の集積回路171の端子領域171a上まで達する個別配線層190を形成する。ここで、Zn拡散によってGaAs層135内に形成されたpn接合領域を含む領域を除去し、Znが拡散されている島状のGaAs層を形成する際に露出したn型AlzGa1−zAs層134の表面及びAlzGa1−zAs層に形成されたZn拡散領域表面の一部(AlzGa1−zAs層表面のpn接合領域を含むpn接合近傍の領域)は、個別配線層190を形成する前に被覆するように絶縁膜140が形成されている。個別配線層190は、例えば、薄膜のメタル配線である。個別配線層190としては、Au層、Ti/Pt/Au積層層、Au/Zn積層層、Au/Ge積層層、Ni/Au積層層、AuGeNi/Au積層層、Pd層、Pd/Au積層層、Mg/Au積層層、Al層、Al/Ni積層層、ポリシリコン層、ITO層、及びZnO層の内のひとつ又は2つ以上を組み合わせた材料から構成される材料を用いることができる。個別配線層190は、フォトリソグラフィ技術を用いて一括形成することが望ましい。個別配線層190は、薄膜配線であるので、配線が長くなれば配線における電圧降下の影響が大きくなる。また、複数のLED130cを高密度に配列する場合には、複数のLED130cの配列ピッチが小さくなるため、個別配線層190の幅が制限される。個別配線層190の幅が5μmであり、厚さが0.5μmであり、数mAの駆動電流を流す場合には、個別配線層190の長さは、約200μm以下にすることが望ましい。

【0022】

以上説明したように、第1の実施形態に係る製造方法によれば、シリコン基板170上にメタル層180を挟んで貼り付けられたエピタキシャルフィルム130とシリコン基板170に形成された集積回路171とをフォトリソグラフィ技術により形成された薄膜の個別配線層190により電気的に接続しているので、エピタキシャルフィルム130aにワイヤボンド用の電極パッドを設ける必要がない。このため、エピタキシャルフィルム130aの面積を小さくでき、その結果、LED/駆動IC複合チップ100の小型化を実現できる。また、エピタキシャルフィルム130の面積を小さくできるので、材料コストの低減を図ることができる。

【0023】

また、第1の実施形態に係る製造方法によれば、シリコン基板170上に貼り付けられたエピタキシャルフィルム130aとシリコン基板170に形成された集積回路171とをフォトリソグラフィ技術により形成された薄膜の個別配線層190により電気的に接続しているので、エピタキシャルフィルム130aの厚さをワイヤボンドを考慮して厚くする必要がない。このように、エピタキシャルフィルム130aの厚さを薄くできるので、材料コストの低減を図ることができる。

【0024】

さらに、第1の実施形態に係る製造方法によれば、誘電体膜140の端部140a,140bをエピタキシャルフィルム130aの端部よりも内側にし、その上を保護層150で覆った状態で、エッチング溝160形成予定領域及び剥離層120のエッチング処理を行う。このため、分離されたエピタキシャルフィルム130a内のLED130c(発光領域)及びエピタキシャルフィルム130a表面の誘電体膜140にエッチング液による損傷を与えることはなく、エピタキシャルフィルム130を剥離可能な個別のエピタキシャルフィルム130aとすることができる。

【0025】

<第2の実施形態>

図17は、本発明の第2の実施形態に係る製造方法により製造されたLED/駆動IC複合チップ200の一部を概略的に示す平面図である。また、図18(a)から(c)までは、第2の実施形態に係るLED/駆動IC複合チップ200の集積回路薄膜220の製造プロセスを概略的に示す断面図である。

【0026】

図17において、図15(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。図17に示されたLED/駆動IC複合チップ200は、基板270上に集積回路薄膜220を貼り付け、個別配線層(図示せず)によって基板270の配線領域220aと接続している点が、第1の実施形態に係るLED/駆動IC複合チップ100と相違する。ここで、基板270は、例えば、ガラス基板、プラスチック基板、ポリマーシート、酸化物や窒化物を含む絶縁体基板、シリコン等の半導体層を含む基板、ステンレス、銅、アルミニウム等の金属等を使うことができる。金属基板を用いる場合は、表面を酸化させたり、コーティング層を設ければ、放熱特性の良い絶縁基板として用いることができる。なお、上記層を絶縁させない場合は、共通配線層としての役割を持たせることもできる。基板270上には、一つ又は複数のエピタキシャルフィルム130aと、該エピタキシャルフィルム内の半導体素子を駆動するための一つ又は複数の集積回路膜270を設けることができる。なお、配線領域220aとは、集積回路薄膜の信号や電源などの入出力端子と外部の回路とを接続するために設けられた接続用のパッド、又は、配線パターンが設けられた領域を意味する。

【0027】

集積回路薄膜220の製造には、SOI基板(SOIウェハ)210を用いる。SOI基板210は、シリコン基板211と、その上に形成された埋め込みSiO2層(BOX層)212と、その上に形成されたシリコン層(SOI層)213とを有する。集積回路薄膜220の製造に際しては、先ず、図18(a)に示されるように、シリコン層213の表面付近に集積回路213aを形成する。次に、図18(b)に示されるように、SiO2層212をHF液でエッチングし、図18(c)に示されるように、シリコン層213を剥離し、基板270上に貼り付ける。剥離されたシリコン層213の保持方法としては、可逆的な保持方法(例えば、気圧差を利用する吸着(吸引)、磁気的吸着、電気的吸着、接着剤等のいずれかを用いて保持部材に保持する方法)を用いる。なお、実際の製造においては、SOI基板210上に多数の集積回路薄膜220を形成し、これらを個別の集積回路薄膜220に分離するプロセスが含まれる。なお、集積回路薄膜220の製造工程においても、エピタキシャルフィルム130aの製造方法と同様に、集積回路表面に形成されている種々の誘電体膜やメタル配線膜などが、集積回路薄膜220を個別の集積回路薄膜220に分割する工程及び集積回路薄膜220を剥離するためのエッチング工程エッチング液によっても破壊されないように保護膜を設けることが望ましい。この場合の保護層としても、エピタキシャルフィルム130aの製造方法で説明したエッチングに対する特性(耐エッチング性)を備えた材料を使用することができる。

【0028】

第2の実施形態に係る製造方法によれば、第1の実施形態の場合と同様の効果が得られる。なお、第2の実施形態において、上記以外の点は、上記第1の実施形態の場合と同じである。

【0029】

<第3の実施形態>

図19は、本発明の第3の実施形態に係る製造方法により製造されたLED/駆動IC複合チップ300の一部を概略的に示す平面図である。

【0030】

図19において、図15(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。図19に示されたLED/駆動IC複合チップ300は、絶縁層140上に発光領域130cと電気的に接続した電極パッド310を備えた点が、第1の実施形態に係るLED/駆動IC複合チップ100と相違する。この場合には、各LED130cとの電気配線としてワイヤボンディングを使用できる。

【0031】

第3の実施形態に係る製造方法によれば、LED/駆動IC複合チップ300が電極パッド310を備えるため、エピタキシャルフィルム130の面積は大きくなる。しかし、第3の実施形態に係る製造方法によれば、誘電体膜140の端部をエピタキシャルフィルム130aの端部よりも内側にし、その上を保護層150で覆った状態で、エッチング処理を行う。このため、分離されたエピタキシャルフィルム130a内のLED130c及び誘電体膜140にエッチング液による損傷を与えることはなく、エピタキシャルフィルム130を剥離可能な個別のエピタキシャルフィルム130aとすることができる。

【0032】

なお、第3の実施形態において、上記以外の点は、上記第1及び第2の実施形態の場合と同じである。

【0033】

<第4の実施形態>

図20は、本発明の第4の実施形態に係る製造方法により製造されたLED/駆動IC複合チップ400の一部を概略的に示す平面図である。

【0034】

図20において、図15(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。また、図21において、図16(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。図20及び図21に示されたLED/駆動IC複合チップ400は、第1の実施形態の集積回路171に代えて、集積回路薄膜410を基板170に貼り付けた点が、上記第1の実施形態の場合と相違する。また、配線領域220aを設けていない点が第2の実施形態と異なる。集積回路薄膜410の製造方法は、図18の集積回路薄膜210製造方法と同様である。また、エピタキシャルフィルム130a及び集積回路薄膜410の厚さが厚くなると、個別配線層190に段切れが発生する確率が高くなる。このような不良の発生を回避するためには、エピタキシャルフィルム130a及び集積回路薄膜410の厚さを、約10μm以下にすることが望ましい。ただし、ポリイミドなどを使って段差領域の平坦化を図るなどの段差領域を横切る配線の断線防止のための方策を実施するなどして、エピタキシャルフィルム130a及び集積回路薄膜410の厚さを、10μmを超える厚さにすることもできる。外部回路の間と電源や制御するための信号の入出力を行うための接続用パッドは、集積回路薄膜410内に設ける。

【0035】

第4の実施形態に係る製造方法によれば、第1の実施形態の場合と同様の効果が得られる。なお、第4の実施形態において、上記以外の点は、上記第1から第3までの実施形態の場合と同じである。

【0036】

<第5の実施形態>

図22は、本発明の第5の実施形態に係る半導体装置の製造方法(即ち、LED/駆動IC複合チップの製造プロセス)を概略的に示す断面図である。また、図23は、第5の実施形態に係る製造方法により製造されたLED/駆動IC複合チップ500の一部を概略的に示す平面図である。

【0037】

図22において、図5(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。また、図23において、図15(第1の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。第5の実施形態に係る製造方法が、第1の実施形態に係る製造方法と相違する点は、誘電体膜140を覆うパッシベーション膜510を形成する工程と、その上に保護層520を形成する工程を有する点である。保護層520及びパッシベーション膜510のそれぞれは、エッチング溝160の形成工程及び剥離層120のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される。ここで、パッシベーション膜510の耐エッチング性とは、パッシベーション膜となる材料そのものが、エッチング溝の形成工程及び剥離層のエッチング工程において使用されるエッチング剤によって、溶解、分解、破壊されないこと、また、パッシベーション膜と、パッシベーション膜が接する半導体薄膜表面との界面に該エッチング液が浸透することによって、該界面の密着性や誘電体膜140が破壊されないこと、あるいは、該エッチング液がパッシベーション膜を浸透しパッシベーション膜と半導体薄膜界面に到達することによって、該界面の密着性や誘電体膜140が破壊されないこと、などパッシベーション膜が半導体薄膜表面及び半導体薄膜表面に設けられている誘電体膜などを被覆保護する機能が失われないことを意味する。また、保護層520の耐エッチング性とは、保護層となる材料そのものが、エッチング溝の形成工程及び剥離層のエッチング工程において使用されるエッチング剤によって、溶解、分解、破壊されないこと、また、保護層と、保護層が接するパッシベーション膜表面との界面に該エッチング液が浸透することによって、該界面の密着性が破壊されないこと、あるいは、該エッチング液が保護層を浸透しパッシベーション膜界面に到達することによって、該界面の密着性が破壊されないこと、など保護層がパッシベーション膜表面への密着性を保持し、エピタキシャルフィルム130aを保護する機能が失われないことを意味する。パッシベーション膜510は、例えば、ポリイミド及び窒化アルミニウムの内のいずれかの材料から構成される。保護層520は、有機材料、例えば、レジスト材料などのポリマー材料やワックス材料から構成される。なお、保護層520は、エピタキシャルフィルム130aをシリコン基板170に貼り付ける工程の前又は後に、除去する。また、パッシベーション膜510の端部は、個別のエピタキシャルフィルム130aの端部とほぼ一致する。

【0038】

第5の実施形態に係る製造方法によれば、第1の実施形態の場合と同様の効果が得られる。また、第5の実施形態に係る製造方法によれば、保護層520にピンホールなどの欠陥があった場合であっても、誘電体膜140に損傷を与えることがなく、製造された装置の信頼性が高い。なお、第5の実施形態において、上記以外の点は、上記第1から第4までの実施形態の場合と同じである。

【0039】

<第6の実施形態>

図24は、本発明の第6の実施形態に係る半導体装置の製造方法(即ち、LED/駆動IC複合チップの製造プロセス)を概略的に示す断面図である。

【0040】

図24において、図22(第5の実施形態)の構成と同一又は対応する構成には、同じ符号を付す。第6の実施形態は、誘電体膜140を形成しない点のみが第5の実施形態と相違する。第6の実施形態の場合には、例えば、エピタキシャルフィルム130上に発光部形成予定領域に開口部を有する、例えば、酸化アルミニウム、窒化アルミニウム、酸化珪素、窒化珪素などの、誘電体膜を形成した後、例えば、固相拡散法によって該開口部を介してZnを拡散した後、拡散源膜及び誘電体膜を除去し、Zn拡散によってGaAs層135内に形成されたpn接合領域を含む領域を除去する。その後、例えば、Znが拡散されている島状のGaAs層表面の一部を露出する開口部を備えた絶縁膜を形成し、パッシベーション610とする。ここで、パッシベーション610の開口部は、n型AlzGa1−zAs層114の表面及びn型AlzGa1−zAs層に形成されたZn拡散領域表面の一部(AlzGa1−zAs層表面のpn接合領域を含むpn接合近傍の領域)が露出しないように形成することが望ましい。第6の実施形態に係る製造方法が、第5の実施形態に係る製造方法と相違する点は、誘電体膜140を残さずに、パッシベーション膜610を形成する工程と、その上に保護層620を形成する工程を有する点である。保護層620及びパッシベーション膜610のそれぞれは、エッチング溝160の形成工程及び剥離層120のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される。パッシベーション膜610は、例えば、ポリイミド及び窒化アルミニウムの内のいずれかの材料から構成される。保護層620は、有機材料、例えば、レジスト材料などのポリマー材料やワックス材料から構成される。なお、保護層620は、エピタキシャルフィルム130aをシリコン基板170に貼り付ける工程の前又は後に、除去する。また、パッシベーション膜610の端部は、個別のエピタキシャルフィルム130aの端部とほぼ一致する。

【0041】

第6の実施形態に係る製造方法によれば、パッシベーション膜610が、誘電体層としての機能を併せ持つように構成したので、第1の実施形態の場合と同様の効果が得られる。また、第6の実施形態に係る製造方法によれば、保護層620にピンホールなどの欠陥があった場合であっても、半導体素子に損傷を与えることがなく、製造された装置の信頼性が高い。なお、第6の実施形態において、上記以外の点は、上記第1から第5までの実施形態の場合と同じである。

【0042】

<本発明が適用されたLEDプリントヘッド>

図25は、本発明の製造方法によって製造された半導体装置を組み込んだLEDプリントヘッド700を概略的に示す断面図である。図25に示されるように、LEDプリントヘッド700は、ベース部材701と、ベース部材701に固定されたLEDユニット702と、柱状の光学素子を多数配列したロッドレンズアレイ703と、ロッドレンズアレイ703を保持するホルダ704と、これらの構成701〜704を固定するクランプ705とを有する。LEDユニット702には、上記実施形態の製造方法によって製造された半導体装置702aであるLED/駆動ICチップ又はLEDアレイチップが搭載されている。LEDユニット702で発生した光はロッドレンズアレイ703を通して照射される。LEDプリントヘッド700は、電子写真プリンタや電子写真コピー装置等の露光装置として用いられる。

【0043】

<可能な変形例>

上記実施形態においては、シリコン基板170上にメタル層180を形成した場合を説明したが、メタル層180に代えてポリシリコン等の金属以外の導電性薄膜層を用いてもよい。

【0044】

また、上記実施形態においては、シリコン基板170上にメタル層180を形成し、その上にエピタキシャルフィルム130aを貼り付けた場合を説明したが、メタル層180を形成せずに、シリコン基板170上に直接エピタキシャルフィルム130aを貼り付けてもよい。この場合には、シリコン基板170の上面とエピタキシャルフィルム130の下面を、適当な化学的方法で表面処理し(鏡面化し)、両面を密着させ、加圧・加熱工程を経ることにより、両面を強固に接着(密着)することができる。強固な接着に必要な加熱温度は、メタル層を介した接着の場合に比べ高い温度になるが、メタル層を設ける場合と比較して、LEDエピフィルムとSi基板表面の間に、第3の層(メタル層)を設けることに起因した、メタル層の欠陥発生に伴うようなボンディングの欠陥発生確率を除外することができる。また、メタル層180を導入することにより、駆動IC配列に対してアライメントされたメタル層180のパターンに対してLEDエピフィルムのボンディング位置合わせをするので、LEDエピフィルムのICパターンに対する位置合わせずれの大きさが増大する要因が増える。したがって、メタル層を設けない場合は、メタル層を設ける場合と比較して、駆動IC配列に対する位置合わせマージンを小さくすることができる。また、シリコン基板上に設けた絶縁膜、例えば、酸化シリコン、の上にエピタキシャルフィルムを貼り付ける変形も可能である。

【0045】

また、上記実施形態においては、メタル層180を含む導電性薄膜層が長方形に描いているが、角の切欠き部や、辺の凹凸部を備える形状にしてもよい。この場合には、製造プロセスにおいて、切欠き部をチップの向きを判断する基準部として用いることができ、凹凸部をLEDの位置判定用の基準部として用いることができる。

【0046】

また、上記実施形態においては、シリコン基板170にエピタキシャルフィルム130aを貼り付ける場合を説明したが、基板170の材料には、アモルファスシリコン、単結晶シリコン、ポリシリコンの他、化合物半導体、有機半導体、及び絶縁体材料(ガラスやサファイヤ等)のような他の材料を用いることもできる。また、基板270についても、同様の変形が可能である。

【0047】

また、上記実施形態においては、半導体薄膜としてのエピタキシャルフィルム130aに備えられた半導体素子が、LEDである場合を説明したが、半導体素子は、レーザー等の他の発光素子、受光素子、ホール素子、及びピエゾ素子等のような他の素子であってもよい。

【0048】

また、上記第実施形態においては、半導体薄膜がエピタキシャル層である場合を説明したが、エピタキシャル層ではない半導体薄膜を採用してもよい。

【0049】

また、エピタキシャルフィルム130aの構成を、p型AlxGa1−xAs層、p型AlyGa1−yAs層、n型AlzGa1−zAs層、及びn型GaAs層を順に形成した構造としてもよい。

【0050】

また、上記第実施形態においては、誘電体膜140が1層の場合を説明したが、誘電体膜を多層備えてもよい。

【0051】

【発明の効果】

以上に説明したように、本発明によれば、基板の端子領域を有する面上に半導体薄膜を貼り付け、これらを薄膜の個別配線層で電気的に接続する構造を採用したので、半導体装置の小型化及び材料コストの低減を図ることができる。

【0052】

また、本発明の製造方法によれば、保護層又はパッシベーション膜によってエピタキシャルフィルムの所定領域を覆った状態でエッチングを行うので、エッチング処理に起因する半導体素子又は誘電体層の損傷は生じ難く、その結果、装置の製造歩留まりを向上させることができる。

【図面の簡単な説明】

【図1】 本発明の第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その1)を概略的に示す断面図である。

【図2】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その2)を概略的に示す断面図である。

【図3】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その3)を概略的に示す断面図である。

【図4】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その4)を概略的に示す断面図である。

【図5】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その5)を概略的に示す断面図である。

【図6】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その6)を概略的に示す断面図である。

【図7】 (a)及び(b)はそれぞれ、第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その7)を概略的に示す断面図及び平面図である。

【図8】 第1の実施形態に係るLED/駆動IC複合チップの製造プロセス(その8)を概略的に示す平面図である。

【図9】 図1のA9部の拡大図である。

【図10】 図3のA10部の拡大図である。

【図11】 図5の概略的な斜視図である。

【図12】 図5のA12部の拡大平面図である。

【図13】 図6のA13部の拡大図である。

【図14】 図13をS14−S14線で切る面を概略的に示す断面図である。

【図15】 図8の拡大平面図である。

【図16】 図8のA16部の概略的な斜視図である。

【図17】 本発明の第2の実施形態に係る製造方法で製造されたLED/駆動IC複合チップを概略的に示す平面図である。

【図18】 (a)から(c)までは、第2の実施形態に係る集積回路薄膜の製造プロセスを概略的に示す断面図である。

【図19】 本発明の第3の実施形態に係る製造方法で製造されたLEDアレイチップを概略的に示す平面図である。

【図20】 本発明の第4の実施形態に係る製造方法で製造されたLED/駆動IC複合チップを概略的に示す平面図である。

【図21】 図20の一部を概略的に示す斜視図である。

【図22】 本発明の第5の実施形態に係るLED/駆動IC複合チップの製造プロセスを概略的に示す断面図である。

【図23】 第5の実施形態に係る製造方法で製造されたLED/駆動IC複合チップの一部を概略的に示す平面図である。

【図24】 本発明の第6の実施形態に係るLED/駆動IC複合チップの製造プロセスを概略的に示す断面図である。

【図25】 本発明の製造方法によって製造された装置を組み込んだLEDプリントヘッドを概略的に示す断面図である。

【図26】 従来のLEDプリントヘッドの一部を概略的に示す斜視図である。

【図27】 図26のLEDプリントヘッドに備えられたLEDアレイチップの一部を示す平面図である。

【符号の説明】

100,200,400,500 LED/駆動IC複合チップ(半導体装置)、

300 メタル層に貼り付けたLEDアレイチップ(半導体装置)、

110 エピタキシャルフィルム製造用の基板、

120 剥離層、

130 分離前のエピタキシャルフィルム、

130a 分離後のエピタキシャルフィルム、

130b 半導体素子形成領域、

130c LED(発光領域)、

131 GaAsコンタクト層(1)(n型GaAs層)、

132 AlGaAs下クラッド層(n型AlxGa1−xAs層)、

133 AlGaAs活性層(n型AlyGa1−yAs層)、

134 AlGaAs上クラッド層(n型AlzGa1−zAs層)、

135 GaAsコンタクト層(2)(n型GaAs層)、

136 Zn拡散領域、

140 誘電体膜、

140a,140b 誘電体膜の端部、

150 保護層、

160 エッチング溝、

170 シリコン基板、

171 集積回路、

180 メタル層、

190 個別配線層、

210 SOI基板、

211 シリコン基板、

212 埋め込みSiO2層(BOX層)、

213 シリコン層(SOI層)、

213a 集積回路、

220,410 集積回路薄膜、

510,610 パッシベーション膜、

520,620 保護層、

700 LEDプリントヘッド

702 LEDユニット

703 ロッドレンズアレイ。

Claims (15)

- 第1の基板とその表面に貼り付けられた個別の半導体薄膜とを有する半導体装置を製造する方法であって、

第2の基板上に剥離層を形成する工程と、

前記剥離層上に、半導体素子の全部又は一部の構造を含む半導体薄膜を形成する工程と、

前記半導体薄膜上において前記個別の半導体薄膜に区画される領域の内側の所定領域に誘電体膜を形成する工程と、

前記半導体薄膜上の前記誘電体膜を覆う様に前記個別の半導体薄膜に区画される領域全体に保護層を形成する工程と、

前記半導体薄膜の前記保護層で覆われていない領域をエッチングして前記剥離層に届くエッチング溝を形成することによって、前記半導体薄膜を分離する工程と、

前記剥離層をエッチングして前記半導体薄膜を剥離可能な個別の半導体薄膜にする工程と、

前記誘電体膜を備えた前記個別の半導体薄膜を保持し、前記第1の基板の表面に貼り付ける工程と、

前記個別の半導体薄膜を貼り付ける工程の前又は後に、前記保護層を除去する工程と

を有し、

前記保護層が、前記エッチング溝の形成工程及び前記剥離層のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される

ことを特徴とする半導体装置の製造方法。 - 第1の基板とその表面に貼り付けられた個別の半導体薄膜とを有する半導体装置を製造する方法であって、

第2の基板上に剥離層を形成する工程と、

前記剥離層上に、半導体素子の全部又は一部の構造を含む半導体薄膜を形成する工程と、

前記半導体薄膜上において前記個別の半導体薄膜に区画される領域の内側の所定領域に誘電体膜を形成する工程と、

前記半導体薄膜上の前記誘電体膜を覆う様に前記個別の半導体薄膜に区画される領域全体にパッシベーション膜を形成する工程と、

前記パッシベーション膜上で前記誘電体膜面全体を覆う様に前記個別の半導体薄膜に区画される領域全体に保護層を形成する工程と、

前記半導体薄膜の前記保護層及び前記パッシベーション膜で覆われていない領域をエッチングして前記剥離層に届くエッチング溝を形成することによって、前記半導体薄膜を分離する工程と、

前記剥離層をエッチングして前記半導体薄膜を剥離可能な個別の半導体薄膜にする工程と、

前記誘電体膜及び前記パッシベーション膜を備えた前記個別の半導体薄膜を保持し、前記第1の基板の表面に貼り付ける工程と、

前記個別の半導体薄膜を貼り付ける工程の前又は後に、前記保護層を除去する工程と

を有し、

前記保護層及び前記パッシベーション膜のそれぞれが、前記エッチング溝の形成工程及び前記剥離層のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成される

ことを特徴とする半導体装置の製造方法。 - 前記第1の基板が、アモルファスシリコン、単結晶シリコン、ポリシリコン、化合物半導体、有機半導体、及び絶縁体材料の内のいずれかの材料を含むことを特徴とする請求項1又は2に記載の半導体装置の製造方法。

- 前記第1の基板が、集積回路を有するシリコン基板であることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

- 前記第2の基板が、その最上層に、前記剥離層のエッチング工程において使用されるエッチング剤に対して耐エッチング性を持つ材料で構成されるエッチングストップ層を有することを特徴とする請求項1から4までのいずれかに記載の半導体装置の製造方法。

- 前記半導体薄膜が、化合物半導体エピタキシャル層から構成されることを特徴とする請求項1から5までのいずれかに記載の半導体装置の製造方法。

- 前記半導体素子が、発光素子、受光素子、ホール素子、及びピエゾ素子の内のいずれかの素子であることを特徴とする請求項1から6までのいずれかに記載の半導体装置の製造方法。

- 前記誘電体膜が、酸化珪素、窒化珪素、酸化アルミニウム、窒化アルミニウムの内のいずれかの材料から構成されることを特徴とする請求項1から7までのいずれかに記載の半導体装置の製造方法。

- 前記パッシベーション膜が、ポリイミド及び窒化アルミニウムの内のいずれかの材料から構成されることを特徴とする請求項2に記載の半導体装置の製造方法。

- 前記保護層が、有機材料から構成されることを特徴とする請求項1から9までのいずれかに記載の半導体装置の製造方法。

- 前記第1の基板の前記個別の半導体薄膜が貼り付けられる領域に導電性材料層を形成する工程を有し、

前記個別の半導体薄膜が、前記導電性材料層上に貼り付けられる

ことを特徴とする請求項1から10までのいずれかに記載の半導体装置の製造方法。 - 前記エッチング溝の形成工程において、エッチング剤として燐酸過水又は、クエン酸及び過酸化水素水を含むエッチング液が用いられ、

前記剥離層のエッチング工程において、エッチング剤としてフッ酸が用いられる

ことを特徴とする請求項1から11までのいずれかに記載の半導体装置の製造方法。 - 前記第1の基板に貼り付けられた前記個別の半導体薄膜の前記半導体素子に電気的に接続され、前記誘電体層又は前記パッシベーション膜上に延びる個別配線層をフォトリソグラフィ技術を用いて形成する工程を有することを特徴とする請求項2又は9に記載の半導体装置の製造方法。

- 前記個別配線層が、Au層、Ti/Pt/Au積層層、Au/Zn積層層、Au/Ge積層層、Ni/Au積層層、AuGeNi/Au積層層、Pd層、Pd/Au積層層、Mg/Au積層層、Al層、Al/Ni積層層、ポリシリコン層、ITO層、及びZnO層の内のひとつ又は2つ以上を組み合わせた材料から構成されることを特徴とする請求項13に記載の半導体装置の製造方法。

- 前記半導体薄膜に前記エッチング溝を形成する工程が、前記保護層を前記エッチング溝を形成するためのエッチングマスクとして使用し、前記保護層の端部と前記エッチング溝形成後の前記半導体薄膜の端部とをほぼ一致させる工程であることを特徴とする請求項1から14までのいずれかに記載の半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002336236A JP4097510B2 (ja) | 2002-11-20 | 2002-11-20 | 半導体装置の製造方法 |

| US10/716,601 US6790695B2 (en) | 2002-11-20 | 2003-11-20 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002336236A JP4097510B2 (ja) | 2002-11-20 | 2002-11-20 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004172351A JP2004172351A (ja) | 2004-06-17 |

| JP2004172351A5 JP2004172351A5 (ja) | 2005-07-28 |

| JP4097510B2 true JP4097510B2 (ja) | 2008-06-11 |

Family

ID=32462609

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002336236A Expired - Lifetime JP4097510B2 (ja) | 2002-11-20 | 2002-11-20 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6790695B2 (ja) |

| JP (1) | JP4097510B2 (ja) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2816445B1 (fr) | 2000-11-06 | 2003-07-25 | Commissariat Energie Atomique | Procede de fabrication d'une structure empilee comprenant une couche mince adherant a un substrat cible |

| US7087446B2 (en) * | 2000-11-16 | 2006-08-08 | Schott Glas | Method of mounting optoelectronic devices on an optical element and article |

| US7239337B2 (en) * | 2002-11-13 | 2007-07-03 | Oki Data Corporation | Combined semiconductor apparatus with thin semiconductor films |

| JP2004207479A (ja) * | 2002-12-25 | 2004-07-22 | Pioneer Electronic Corp | 半導体レーザ装置及びその製造方法 |

| TWI226138B (en) * | 2003-01-03 | 2005-01-01 | Super Nova Optoelectronics Cor | GaN-based LED vertical device structure and the manufacturing method thereof |

| JP4130158B2 (ja) * | 2003-06-09 | 2008-08-06 | 三洋電機株式会社 | 半導体装置の製造方法、半導体装置 |

| JP4518886B2 (ja) * | 2004-09-09 | 2010-08-04 | シャープ株式会社 | 半導体素子の製造方法 |

| JP2006093367A (ja) * | 2004-09-24 | 2006-04-06 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP4906256B2 (ja) * | 2004-11-10 | 2012-03-28 | 株式会社沖データ | 半導体複合装置の製造方法 |

| DE102005055293A1 (de) * | 2005-08-05 | 2007-02-15 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung von Halbleiterchips und Dünnfilm-Halbleiterchip |

| US7608471B2 (en) * | 2005-08-09 | 2009-10-27 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Method and apparatus for integrating III-V semiconductor devices into silicon processes |

| KR20070047114A (ko) * | 2005-11-01 | 2007-05-04 | 주식회사 엘지화학 | 플렉서블 기판을 구비한 소자의 제조방법 및 이에 의해제조된 플렉서블 기판을 구비한 소자 |

| JP4908837B2 (ja) * | 2005-12-13 | 2012-04-04 | キヤノン株式会社 | 発光素子アレイ及び画像形成装置 |

| DE102007004303A1 (de) * | 2006-08-04 | 2008-02-07 | Osram Opto Semiconductors Gmbh | Dünnfilm-Halbleiterbauelement und Bauelement-Verbund |

| JP5171016B2 (ja) | 2006-10-27 | 2013-03-27 | キヤノン株式会社 | 半導体部材、半導体物品の製造方法、その製造方法を用いたledアレイ |

| DE102007004304A1 (de) * | 2007-01-29 | 2008-07-31 | Osram Opto Semiconductors Gmbh | Dünnfilm-Leuchtdioden-Chip und Verfahren zur Herstellung eines Dünnfilm-Leuchtdioden-Chips |

| US7858493B2 (en) * | 2007-02-23 | 2010-12-28 | Finisar Corporation | Cleaving edge-emitting lasers from a wafer cell |

| JP2008235318A (ja) * | 2007-03-16 | 2008-10-02 | Oki Data Corp | 窒化物半導体ウェハ及び薄膜半導体装置の製造方法 |

| JP2009094144A (ja) * | 2007-10-04 | 2009-04-30 | Canon Inc | 発光素子の製造方法 |

| US9318441B2 (en) | 2007-12-14 | 2016-04-19 | Stats Chippac, Ltd. | Semiconductor device and method of forming sacrificial adhesive over contact pads of semiconductor die |

| US8183095B2 (en) | 2010-03-12 | 2012-05-22 | Stats Chippac, Ltd. | Semiconductor device and method of forming sacrificial protective layer to protect semiconductor die edge during singulation |

| US8456002B2 (en) | 2007-12-14 | 2013-06-04 | Stats Chippac Ltd. | Semiconductor device and method of forming insulating layer disposed over the semiconductor die for stress relief |

| US8343809B2 (en) | 2010-03-15 | 2013-01-01 | Stats Chippac, Ltd. | Semiconductor device and method of forming repassivation layer with reduced opening to contact pad of semiconductor die |

| US7767496B2 (en) | 2007-12-14 | 2010-08-03 | Stats Chippac, Ltd. | Semiconductor device and method of forming interconnect structure for encapsulated die having pre-applied protective layer |

| JP5288852B2 (ja) | 2008-03-21 | 2013-09-11 | スタンレー電気株式会社 | 半導体素子の製造方法 |

| JP5291499B2 (ja) * | 2009-03-10 | 2013-09-18 | 株式会社沖データ | 半導体複合装置の製造方法 |

| US9548240B2 (en) | 2010-03-15 | 2017-01-17 | STATS ChipPAC Pte. Ltd. | Semiconductor device and method of forming repassivation layer for robust low cost fan-out semiconductor package |

| TW201137960A (en) * | 2010-04-20 | 2011-11-01 | Raydium Semiconductor Corp | Integrated circuit wafer dicing method |

| JP5603812B2 (ja) | 2011-03-11 | 2014-10-08 | スタンレー電気株式会社 | 半導体素子の製造方法 |

| JP5612516B2 (ja) | 2011-03-11 | 2014-10-22 | スタンレー電気株式会社 | 半導体素子の製造方法 |

| JP5658604B2 (ja) | 2011-03-22 | 2015-01-28 | スタンレー電気株式会社 | 半導体発光素子の製造方法 |

| TWI585990B (zh) * | 2011-08-26 | 2017-06-01 | 行政院原子能委員會核能研究所 | 用於光電元件之基板的剝離結構 |

| US8445361B1 (en) * | 2011-09-28 | 2013-05-21 | Paul C. Lindsey, Jr. | Method of dividing a semiconductor wafer having semiconductor and metal layers into separate devices |

| JP5393751B2 (ja) * | 2011-09-28 | 2014-01-22 | 株式会社沖データ | 発光装置、発光素子アレイ、および画像表示装置 |

| GB201209142D0 (en) * | 2012-05-24 | 2012-07-04 | Lumejet Holdings Ltd | Media exposure device |

| DE112014006625T5 (de) * | 2014-04-29 | 2017-02-09 | Enraytek Optoelectronics Co., Ltd. | Vertikales LED-Array-Element, das LED epitaktische Strukturen mit einem LED-Paket-Substrat integriert |

| JP6783990B2 (ja) * | 2017-09-07 | 2020-11-11 | 豊田合成株式会社 | Iii族窒化物半導体素子の製造方法および基板の製造方法 |

| JP7151620B2 (ja) * | 2019-05-15 | 2022-10-12 | 株式会社デンソー | 半導体装置の製造方法 |

| TWI740212B (zh) * | 2019-09-19 | 2021-09-21 | 國立陽明交通大學 | 微型發光二極體晶片的製作方法 |

| CN111244227B (zh) * | 2020-01-19 | 2023-07-18 | 中国科学院上海微系统与信息技术研究所 | 一种硅基光子集成模块及其制备方法 |

| CN112967967B (zh) * | 2020-05-18 | 2022-03-25 | 重庆康佳光电技术研究院有限公司 | 一种发光芯片的转移方法及显示装置 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5827751A (en) * | 1991-12-06 | 1998-10-27 | Picogiga Societe Anonyme | Method of making semiconductor components, in particular on GaAs of InP, with the substrate being recovered chemically |

| JP3360919B2 (ja) * | 1993-06-11 | 2003-01-07 | 三菱電機株式会社 | 薄膜太陽電池の製造方法,及び薄膜太陽電池 |

| JP3156896B2 (ja) * | 1994-01-28 | 2001-04-16 | 富士通株式会社 | 半導体装置の製造方法およびかかる製造方法により製造された半導体装置 |

| DE19536438A1 (de) * | 1995-09-29 | 1997-04-03 | Siemens Ag | Halbleiterbauelement und Herstellverfahren |

| US5858814A (en) * | 1996-07-17 | 1999-01-12 | Lucent Technologies Inc. | Hybrid chip and method therefor |

| JPH1063807A (ja) | 1996-08-23 | 1998-03-06 | Hitachi Ltd | カード型情報制御装置 |

| US6071795A (en) * | 1998-01-23 | 2000-06-06 | The Regents Of The University Of California | Separation of thin films from transparent substrates by selective optical processing |

| FR2781925B1 (fr) * | 1998-07-30 | 2001-11-23 | Commissariat Energie Atomique | Transfert selectif d'elements d'un support vers un autre support |

| FR2782843B1 (fr) * | 1998-08-25 | 2000-09-29 | Commissariat Energie Atomique | Procede d'isolation physique de regions d'une plaque de substrat |

| US6744800B1 (en) * | 1998-12-30 | 2004-06-01 | Xerox Corporation | Method and structure for nitride based laser diode arrays on an insulating substrate |

| US6423560B1 (en) * | 1999-10-22 | 2002-07-23 | Teraconnect, Incoporated | Method of making an optoelectronic device using multiple etch stop layers |

| US6485993B2 (en) * | 1999-12-02 | 2002-11-26 | Teraconnect Inc. | Method of making opto-electronic devices using sacrificial devices |

| US6344664B1 (en) * | 1999-12-02 | 2002-02-05 | Tera Connect Inc. | Electro-optical transceiver system with controlled lateral leakage and method of making it |

| JP3906653B2 (ja) * | 2000-07-18 | 2007-04-18 | ソニー株式会社 | 画像表示装置及びその製造方法 |

| JP3502036B2 (ja) * | 2000-11-08 | 2004-03-02 | シャープ株式会社 | 半導体素子の製造方法および半導体素子 |

| US6518079B2 (en) * | 2000-12-20 | 2003-02-11 | Lumileds Lighting, U.S., Llc | Separation method for gallium nitride devices on lattice-mismatched substrates |

| US6555405B2 (en) * | 2001-03-22 | 2003-04-29 | Uni Light Technology, Inc. | Method for forming a semiconductor device having a metal substrate |

| JP2003197881A (ja) * | 2001-12-27 | 2003-07-11 | Seiko Epson Corp | 半導体集積回路、半導体集積回路の製造方法、半導体素子部材、電気光学装置、電子機器 |

| US6562127B1 (en) * | 2002-01-16 | 2003-05-13 | The United States Of America As Represented By The Secretary Of The Navy | Method of making mosaic array of thin semiconductor material of large substrates |

| US7535100B2 (en) * | 2002-07-12 | 2009-05-19 | The United States Of America As Represented By The Secretary Of The Navy | Wafer bonding of thinned electronic materials and circuits to high performance substrates |

-

2002

- 2002-11-20 JP JP2002336236A patent/JP4097510B2/ja not_active Expired - Lifetime

-

2003

- 2003-11-20 US US10/716,601 patent/US6790695B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6790695B2 (en) | 2004-09-14 |

| US20040110316A1 (en) | 2004-06-10 |

| JP2004172351A (ja) | 2004-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4097510B2 (ja) | 半導体装置の製造方法 | |

| JP3813123B2 (ja) | 半導体装置及びledヘッド | |

| JP5599916B2 (ja) | 半導体装置の製造方法、半導体装置及びそれを用いた光プリントヘッド、及び画像形成装置 | |

| JP5415191B2 (ja) | 半導体複合装置、光プリントヘッド、及び画像形成装置 | |

| US6998642B2 (en) | Series connection of two light emitting diodes through semiconductor manufacture process | |

| JP3641122B2 (ja) | 半導体発光素子、半導体発光モジュール、およびこれらの製造方法 | |

| US20040124428A1 (en) | Light emitting diode and method of making the same | |

| JP4179866B2 (ja) | 半導体複合装置及びledヘッド | |

| JP5148336B2 (ja) | 発光ダイオードチップおよびその製造方法 | |

| JP2004207325A (ja) | 半導体装置 | |

| JP2004179641A (ja) | 半導体装置、光プリントヘッド、及び画像形成装置 | |

| JP2010225852A (ja) | 半導体素子及びその製造方法 | |

| JP4393306B2 (ja) | 半導体発光素子およびその製造方法並びに半導体装置 | |

| KR20010088929A (ko) | AlGaInN계 반도체 LED 소자 및 그 제조 방법 | |

| JP2004179646A (ja) | 半導体複合装置、光プリントヘッド、及び画像形成装置 | |

| US8507938B2 (en) | Light-emitting diode structure and method for manufacturing the same | |

| JP4573867B2 (ja) | 半導体装置 | |

| JP2005079369A (ja) | 半導体複合装置の製造方法 | |

| JP5171764B2 (ja) | 半導体複合装置の製造方法 | |

| JP2002232004A (ja) | Ledアレイ | |

| JP3784267B2 (ja) | Ledアレイ | |

| KR100665302B1 (ko) | 다수의 발광셀이 어레이된 플립칩형 발광소자 | |

| JP2001185759A (ja) | 半導体発光装置 | |

| JP2001320088A (ja) | 半導体発光装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070905 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071023 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071219 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080311 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080311 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4097510 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110321 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110321 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120321 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130321 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140321 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |