JP3881248B2 - 液晶表示装置および画像表示装置 - Google Patents

液晶表示装置および画像表示装置 Download PDFInfo

- Publication number

- JP3881248B2 JP3881248B2 JP2002008283A JP2002008283A JP3881248B2 JP 3881248 B2 JP3881248 B2 JP 3881248B2 JP 2002008283 A JP2002008283 A JP 2002008283A JP 2002008283 A JP2002008283 A JP 2002008283A JP 3881248 B2 JP3881248 B2 JP 3881248B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- common electrode

- liquid crystal

- electrode

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134363—Electrodes characterised by their geometrical arrangement for applying an electric field parallel to the substrate, i.e. in-plane switching [IPS]

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【発明の属する技術分野】

本発明は液晶表示装置に係り、特に薄膜トランジスタ(TFT)方式等のアクティブマトリクス型液晶表示装置及びその製造方法に関するものである。

【0002】

【従来の技術】

IPSモードの液晶表示装置では、広視野角を実現できる方式として特開平7−36058号等に公知である。また特開平9−230378号では、有機系の樹脂上に画素電極及び共通電極を前記樹脂に開口したスルーホールを介して配置させる方式が提案されている。さらに、スイッチングさせるためのアクティブ素子として、アモルファスシリコンを用いたTFT以外に、ポリシリコンを用いたTFTが知られている。

【0003】

【発明が解決しようとする課題】

IPS型液晶表示装置ではTN方式より開口率が低いという課題があり、開口率の向上という課題がある。また大型サイズでの液晶テレビを含む映像デジタルメディア対応のためには高輝度化の実現、さらに大画面サイズで配線遅延の影響を低減して均一な表示を実現するという課題がある。

【0004】

さらにIPS表示の液晶表示装置の画面サイズが大型化し、その解像度が高精細化された場合は、輝度むら、スメアなどが悪化し、画質が劣化するという課題がある。アクティブマトリクス型の駆動を用いるIPS表示装置では、各画素の画素電極と共通電極間に印加された横電界で液晶を駆動する。画素電極は各画素毎に独立駆動であるため、各々の画素内での遅延時間は画素TFTの液晶容量と保持容量の総和に対する駆動能力で決まる。IPS表示装置では、TN表示装置に比べて液晶容量は小さく保持容量の値が大きい。一方、共通電極は画面内の結線された配線であり、その電極材料の比抵抗や他の配線との容量値の負荷に対する配線遅延が画質を悪化させる遅延時間となる。各画素毎に見れば保持容量が配線遅延の最大要因になる。従って、画質向上には共通電極の配線遅延時間を小さくする必要があることが特に有効であることを見出した。

【0005】

さらに、ドレイン配線を駆動する回路をガラスなどのTFT基板上に内蔵し外部の駆動IC数を削減するためには、ドレイン配線の配線遅延を小さくすることが必要であることが判明した。このためには、ドレイン配線容量を低減するという課題がある。

【0006】

以上の課題の1つあるいは複数を解決することが本願の目的であり、その第1の目的は開口率を向上したIPS型液晶表示装置を提供することである。第2の目的は高輝度化を実現したIPS型液晶表示装置を提供することである。第3の目的は大画面でも配線遅延の影響を低減し、画質を改善できる液晶表示装置を提供することにある。

【0007】

本願の解決の目的とする他の課題は本願明細書において明らかとなるであろう。

【0008】

【課題を解決するための手段】

本発明による課題を解決するための手段の主な例を挙げると、以下のようになる。

【0009】

(手段1)

透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成されそれぞれの画素は少なくとも共通電極配線と共通電極と画素電極とを有する液晶表示装置において、

前記共通電極配線は、前記画素領域で前記ゲート配線延在方向に延在された第1の共通電極配線と前記ドレイン配線延在方向に延在された第2の共通電極配線を含み、該第1の共通電極配線と該第2の共通電極配線は第1の絶縁膜で離間され、該第1の共通電極配線と該第2の共通電極配線は第1の絶縁膜に設けられた開口部で接続され、該開口部上には第2の絶縁膜を形成する。

【0010】

(手段2)

手段1において、前記第1の共通電極配線と第2の共通電極配線は前記画素領域で前記共通電極との間に少なくとも前記第2の絶縁膜を有し、かつ前記共通電極は前記ドレイン配線上に少なくとも前記第2の絶縁膜を介して前記ドレイン配線より幅広く配置されている部分を含むよう構成する。

【0011】

(手段3)

透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と画素電極とを有する液晶表示装置において、

前記画素領域に第1の島状の電極を有し、第1の島状の電極を被覆する第1の絶縁膜に開口部を有し、前記ドレイン配線延在方向に延在された共通電極配線を有し、該第1の島状の電極と該共通電極配線が前記開口部で接続され、該第1の島状の電極が下部電極を構成し、前記薄膜トランジスタのソースに接続され前記第1絶縁膜上に形成された第2の島状の電極が上部電極を構成し保持容量を構成する。

【0012】

(手段4)

手段3において、前記第1の基板上に、前記ドレイン配線上に被覆された絶縁膜上に構成された共通電極を有し、該共通電極は隣接する画素間でマトリクス状に接続して構成され、かつ該共通電極は前記ドレイン配線上に被覆された絶縁膜上で前記ドレイン配線より幅広く配置されている部分を含むよう構成する。

【0013】

(手段5)

手段3において、前記保持容量の絶縁膜は前記薄膜トランジスタのゲート配線を被覆する無機絶縁膜とする。

【0014】

(手段6)

手段3において、前記第1の島状の電極は前記薄膜トランジスタの半導体層で構成され、前記保持容量の絶縁膜は少なくとも前記薄膜トランジスタのゲート絶縁膜を含むよう構成する。

【0015】

(手段7)

第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と共通電極と画素電極とを有する液晶表示装置において、

前記共通電極配線として前記ドレイン配線延在方向に延在された共通電極配線を有し、前記薄膜トランジスタのソースに接続された島状金属画素電極を有し、前記画素領域は隣接するドレイン配線間で6分割以上にされた開口部を有し、前記島状金属画素電極と前記隣接するドレイン配線のうちの一方との間は少なくとも1つの開口部を有し、前記共通電極配線と前記隣接するドレイン配線のうちの他方のドレイン配線との間は少なくとも2つの開口部を有し、前記島状の金属画素電極と前記共通電極配線との間は少なくとも3つの開口部を有する。

【0016】

(手段8)

第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と共通電極と画素電極とを有する液晶表示装置において、

前記共通電極配線として前記ドレイン配線延在方向に延在された共通電極配線を有し、前記薄膜トランジスタのソースに接続された島状金属画素電極を有し、前記画素領域は隣接するドレイン配線間で8分割以上にされた開口部を有し、前記島状金属画素電極と前記隣接するドレイン配線のうちの一方との間は少なくとも3つの開口部を有し、前記共通電極配線と前記隣接するドレイン配線のうちの他方のドレイン配線との間は少なくとも2つの開口部を有し、前記島状の金属画素電極と前記共通電極配線との間は少なくとも3つの開口部を有する。

【0017】

(手段9)

第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と透明共通電極と透明画素電極とを有する液晶表示装置において、

前記透明共通電極と前記透明画素電極は前記ドレイン配線より上層に同層で形成され、前記共通電極配線として前記ドレイン配線延在方向に延在された共通電極配線を有し、前記薄膜トランジスタのソースに接続された金属画素電極を有し、前記画素領域は前記画素領域は隣接するドレイン配線間で6分割以上にされた開口部を有し、前記金属画素電極は前記隣接するドレイン配線のうちの一方のドレイン配線に最隣接する透明画素電極の下部に配置され、前記共通電極配線は前記隣接配置するドレイン配線のうちの他方のドレイン配線に隣接しかつ他方のドレイン配線上ではない透明共通電極の下部に配置され、前記金属画素電極と前記共通電極配線の間に少なくとも1個以上の透明共通電極あるいは透明画素電極を有する。

【0018】

(手段10)

第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と共通電極と画素電極とを有する液晶表示装置において、

隣接するドレイン配線に挟まれた領域に配置された金属画素電極を有し、前記共通電極として前記ドレイン配線延在方向に延在した共通電極を有し、前記隣接するドレイン配線のうちの一方と該金属画素電極の間、該金属画素電極と該共通電極の間、該共通電極と前記隣接するドレイン配線のうちの他方のドレイン配線との間を画素領域の分割数に対しほぼ均等の間隔で配置する。

【0019】

(手段11)

手段7ないし10において、共通電極配線として前記ゲート配線延在方向に延在された第1の共通電極配線と、前記ドレイン配線延在方向に延在された第2の共通電極配線を有し、前記第1の共通電極配線と第2の共通電極配線は画素領域で互いに絶縁膜の開口部で接続する。

【0020】

(手段12)

手段10において、前記画素領域の分割数に対しほぼ均等な間隔が、隣接する映像信号線の間の領域の分割数が8分割の構成の液晶表示装置においては3+3+2、隣接する映像信号線の間の領域の分割数が10分割の構成の液晶表示装置においては3+3+4、隣接する映像信号線の間の領域の分割数が12分割の構成の液晶表示装置においては5+4+3であるよう構成する。

【0021】

(手段13)

透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも保持電極配線と画素電極とを有する液晶表示装置において、

前記画素領域に第1の島状の電極を有し、第1の島状の電極を被覆する第1の絶縁膜に開口部を有し、前記ドレイン配線延在方向に延在された保持電極配線を有し、該第1の島状の電極と該保持電極配線が前記開口部で接続され、該第1の島状の電極が下部電極を構成し、前記薄膜トランジスタのソースに接続され前記第1絶縁膜上に形成された第2の島状の電極が上部電極を構成し保持容量を構成する。

【0022】

(手段14)

手段13において、前記ゲート配線延在方向に延在された第2の保持容量配線を有し、該第2の保持容量配線と前記ドレイン配線延在方向に延在された保持容量配線を前記第1絶縁膜に形成されたスルーホールにより電気的に接続する。

【0023】

(手段15)

手段13において、前記ゲート配線延在方向に延在された第2の保持容量配線を有し、該第2の保持容量配線が前記第1の島状の電極を兼ねる。

【0024】

(手段16)

透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は共通電極配線と透明共通電極と画素電極とを有する液晶表示装置において、

前記ゲート配線はその上部に絶縁膜を有し、さらにその上部に前記透明共通電極が前記ゲート配線の幅より広く被覆してある領域を有し、該ゲート配線より幅の広い透明電極配線は液晶表示装置のブラックマトリクスの役割を果す。

【0025】

(手段17)

手段16において、前記ゲート配線より幅の広い透明電極配線は薄膜トランジスタの半導体層も被覆する。

【0026】

(手段18)

手段16において、前記絶縁膜がアクリルなどの有機絶縁膜である。

【0027】

(手段19)

手段1、2、4、7ないし10、12のいずれかにおいて、前記共通電極と画素電極は透明電極で構成し、双方が前記第1の基板の配向膜下の最上層に形成する。

【0028】

(手段20)

手段1ないし10、12ないし18の液晶表示装置が横電界方式の液晶表示装置である。

【0029】

(手段21)

手段1ないし10、12ないし18のいずれかにおいて、前記薄膜トランジスタの半導体層をポリシリコンで構成する。

【0030】

(手段22)

手段1ないし10、12ないし18のいずれかを適用したアクティブマトリクス型液晶表示装置を用いて液晶テレビとして用いられる画像表示装置を構成する。

【0031】

(手段23)

手段1ないし10、12ないし18のいずれかを適用したアクティブマトリクス型液晶表示装置を用いて液晶モニタとして用いられる画像表示装置を構成する。

【0032】

(手段24)

手段1ないし10、12ないし18のいずれかを適用したアクティブマトリクス型液晶表示装置を用いて一体型パソコンとして用いられる画像表示装置を構成する。

【0033】

本発明の更なる手段は請求項を含む本願明細書において明らかとなるであろう。

【0034】

【発明の実施の形態】

本発明の特徴を示す代表的な構造を、以下実施例により説明する。

【0035】

(実施例1)

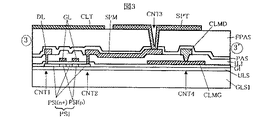

図1〜図5は本発明の一実施例の液晶表示装置に係る画素の平面および断面図である。図2、図3、図4はそれぞれ図1における2−2’、3−3’、4−4’として一点鎖線で示した切断線での断面を示す。図面では切断部を分かりやすくするため、数字を○で囲い切断部を示している。なお図は説明用に要部を記載した物であり、配向膜は図からは省略している図もある。また対向基板側の構成も省略している図もある。以下、順を追って示す。

【0036】

図1は画素の模式平面パターンを示す。隣接するゲート配線GL、隣接するドレイン配線DLに囲まれて1画素を構成する。ゲート配線GLはポリシリコンPSIで構成されたTFTのゲート電極としても作用し、TFTをオンさせる電圧を供給する。ドレイン線はポリシリコンPSIへの電流を供給する、すなわち前記ゲート電圧GLがオン電圧を供給したタイミングで印加された映像電圧(ドレイン電圧)を1画素の液晶容量、保持容量に給電し、結果的に金属画素電極SPM及びこれに連結された透明画素電極SPTの電位が映像電位となる。

【0037】

前記電流の流れはドレイン配線DLから第1のコンタクトホールCNT1を通じてポリシリコンPSIに繋がり、このポリシリコン中の電流は第2のコンタクトホールCNT2を通じて、金属画素電極SPMに流れる。さらに金属画素電極SPMから第3のコンタクトホールCNT3を介して、絶縁膜上の透明画素電極SPTに至る。

【0038】

図1では、DLとPSIのコンタクトホールCNT1の周囲でDLを局部的に太く構成した。これにより、CNT1の接続抵抗の低減と安定したコンタクトが実現する。むろん、コンタクトが正常に出来ればDLの太さは同じでも良い。

【0039】

画素電極と共に液晶容量あるいは保持容量を構成するもう一方の電極の共通電極電位は以下の経路を持ち印加される。隣接するゲート配線間のほぼ中央に配置された横共通電極配線CLMGと、隣接するドレイン配線間のほぼ中央に配置された縦共通電極配線CLMDにまず共通電位が印加される。これらの共通電極配線は画面外部の電源から供給されている。さらに、この横共通電極配線CLMGはゲート配線GLと同一材料で同一工程で形成されている。一方、縦共通電極配線CLMDはドレイン配線DLと同一材料で同一工程で形成されている。

【0040】

本平面構造の1つは、この横共通電極配線CLMGと縦共通電極配線CLMDは第4のコンタクトホールCNT4で互いに結線されている点である。従って、液晶表示装置画面領域から見ると、低抵抗のメッシュ状の共通電極配線が結線された状態で極めて配線遅延が小さくなる。これらの金属で構成された共通電極配線は金属画素電極SPMと横共通電極配線が平面的に重なった面積領域で規定される保持容量に主に電位を給電する役割を果す。保持容量を構成する絶縁膜はゲート配線GLとドレイン配線を絶縁分離する層間絶縁膜である。このように縦共通電極配線CLMDをドレイン配線と同層で形成し、横共通電極配線CLMGをゲート配線と同層で形成し、両者の共通電極配線を各画素で接続することによりゲート配線、ドレイン配線と共通電極配線間の寄生容量を低減でき、マトリクス状の給電の効果も含め、供給する共通電極電位が安定化するため、輝度むら、スメアを大幅に低減した安定した表示が実現する。さらに、該共通電極配線の配置では縦共通電極配線CLMDは同層のドレイン配線と平行方向に、横共通電極配線CLMGはゲート配線と平行方向となる為、同層の電極間での短絡の確率も低減でき、歩留りも高いものとすることが出来る。さらに、ドレイン配線による映像信号は、ドレイン配線が多数のゲート配線を横切って給電される為、容量結合によるゲート配線の影響を含んだものとなる。本実施例では縦共通電極配線CLMDをドレイン配線と同層に形成したことにより、縦方向から供給される共通電位が映像信号に類似した影響をゲート配線から受けたものとなる。この結果、保持容量部に書き込まれる電圧は両者の差電圧となる為、ゲート配線の影響がキャンセルされる方向に働く効果を奏する。このため、さらに表示むらの低減、スメアの低減を図ることが出来る。また図3に明らかなように、横共通電極配線CLMGと縦共通電極配線CLMDを接続するスルーホールCNT4はその上部をPASで保護される為、接続部の信頼性も高いものとすることが出来る。さらにFPASで平坦化できるため、ラビングへの影響も生じない。また横共通電極配線CLMGをゲート配線層で、縦共通電極配線CLMDをドレイン配線層で形成することにより、両者の間のコンタクトホールは無機絶縁膜に形成することが可能となる。このため、コンタクトホールの大きさを低減でき、開口率の一層の向上が実現する。

【0041】

一方、各画素領域には上記メッシュ状に電気的に接続された金属による共通電極配線とは別に、ゲート配線GL及びドレイン配線DL上を低誘電率の絶縁膜を介してその上部に上記配線をシールドするように配置された透明共通電極CLTがあり、隣接する画素間でメッシュ状に構成されている。透明共通電極CLTは画素内へは分岐し、液晶を画素電極SPTと共に駆動する共通電極の役割を果す。透明共通電極CLTは画素内では金属で形成された横共通電極配線CLMGや縦共通電極配線CLMDとは接続されておらず、画面周辺領域で接続結線されている。また、この透明共通電極CLTは、横共通電極配線CLMGや縦共通電極配線CLMDが保持容量を主に充電する配線であるのに対して、液晶容量を充電する役割を果す。IPS液晶表示装置では液晶容量は例えば図1の透明共通電極CLTと透明画素電極SPT間で規定される値となるため、その値は対向する基板面の大部分の領域に形成された電極間で液晶容量を形成するTN液晶表示装置に比べて半分以下という小さい値となる。この結果、透明共通電極CLTの配線抵抗仕様はかなり高い値でも液晶容量に充電することが可能となり、各種透明導電体、すなわちITO(Indium−Tin−Oxide),IZO(Indium−Zinc−Oxide),ITZO(Indium−Tin−Zinc−Oxide),SnO2、In2O3などが使用でき、かつ輝度むらはスメアを抑制した良質の画質が得られる。

【0042】

上記共通電極及び共通電極配線の電位は、フレーム毎に交流化される画素電位のほぼ中点電位が設定される(図14で再度詳細を説明する)。TFTを用いた液晶表示装置の場合、飛び込み電圧による変動を考慮して設定することが望ましい。この画素電極電位と共通電極電位により液晶容量および保持容量が構成されると共に、この電位間の電位差により電界を液晶層内に生じせしめ、前記ドレイン配線DLから供給された映像電圧と前記共通電圧で映像を表示する。図1における主な透過部は2−2’線に沿って設けられた4つの開口部である。

【0043】

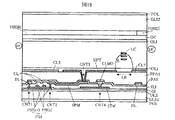

以下、各部の構成を断面図を用いて詳細に説明する。図2は図1の2−2’線に沿った断面図であり、隣接するドレイン線DL間の1画素領域を横切る部分である。歪点約670℃の無アルカリTFTガラス基板GLS1上に膜厚50nmのSi3N4膜と膜厚120nmのSiO2膜からなる下地絶縁膜ULSが形成されている。下地絶縁膜ULSはTFTガラス基板GLS1からのNa等の不純物の拡散を防止する役割を持つ。下地絶縁膜ULS上には、SiO2からなるゲート絶縁膜GIが成膜されている。

【0044】

上記を覆うようにSiO2からなる層間絶縁膜ILIが形成され。層間絶縁膜ILI上にはTi/Al/Tiのように3層金属膜よりなるドレイン配線DLが形成されている。上記ドレイン配線DLと同一材料、同一工程で形成された金属画素電極SPMは、図1においてTFTの第2のコンタクトホールCNT2から画素電位を給電する電極である。また、同層上には平行して、前記ドレイン配線DLと同一材料、同一工程で形成された縦共通電極配線CLMD配置されてあり、これは保持容量に対して共通電位を給電する役割を果す。

【0045】

その上層には膜厚200nmのSi3N4からなる保護絶縁膜PASと膜厚2μmのアクリル系樹脂を主成分とする有機保護膜FPASにより被覆されている。有機保護膜FPAS上では、まずドレイン配線DLの幅より広く、インジウム−スズ酸化物(ITO)よりなる透明共通電極CLTが形成されている。同一工程、同一材料で作製されたITOからなる透明画素電極SPTも前記有機絶縁膜FPAS上に形成されている。

【0046】

上記説明中、配線材料は特に限定する物ではない。

【0047】

主な透過領域は(1)ドレイン線DL上の透明共通電極CLTと透明画素電極SPT間、(2)前記透明画素電極SPTと図1の平面図において縦共通電極配線CLMDを被覆するように配置され、ゲート配線GL上側から上下に延びた透明共通電極配線CLTの間、(3)前記透明共通電極CLTと透明画素電極SPTとの間、(4)前記透明画素電極SPTとドレイン配線DL上の透明共通電極CPTの間の4つの領域である。上記透明画素電極SPT、透明共通電極CPTが液晶を駆動する電極である。

【0048】

一方、液晶LCを封止する対向の基板はカラーフィルタ(CF)基板GLS2である。CFガラス基板GLS2は、液晶側に色表示を行う顔料を分散した有機膜材料から構成された色フィルタ(FIL)がその画素毎に割り当てられた色に応じて、青(B)、赤(R)、緑(G)の透過光を表現する色フィルタ(赤ではFIL(R))となっている。その内側には有機材料からなるオーバコート膜OC膜が形成されている。OC膜は無くても良いが、平坦性を向上する目的ではあるほうが望ましい。CF基板GLS2及びTFT基板GLS1の液晶LCに対して接している面には配向膜OLIが印刷されて所定のラビングが施され、初期配向方向を制御している。また上記、CFガラス基板GLS2及びTFTガラス基板GLS1の外側の面にはそれぞれ偏光板POLが貼られる。この偏光板は互いのガラス基板間で偏向軸が直交するいわゆるクロスニコル状態が形成されている。

【0049】

ラビング方向と偏光板の角度の関係を図16に示す。偏光軸の一方PD2はGLと同方向に、他方PD1はGLと直交方向としている。またラビング方向RDは上下基板ともGLと直交する方向とした。これによりノーマリーブラックモードの配置となり、さらに図1のような屈曲形状の画素パターンによりマルチドメイン化を行っている。むろん、非マルチドメインの場合も本願の範疇に含むものであり、その場合でも偏光板配置がクロスニコルになるようにすることが必要である。

【0050】

本断面のCF基板GLS2には、いはゆる、ブラックマトリクスBMが形成されていない。カラーフィルタFILの色のつなぎあわせは、ドレイン配線DLを被覆するように配置された透明共通電極配線CLT上で行う。

【0051】

本断面構造の特徴の1つは、有機絶縁膜FPAS上の透明画素電極SPT及び透明共通電極CPTにより液晶LCに対して、1画素が少なくとも4分割の開口(主な透過領域)を持つことである。

【0052】

また別の特徴は、有機保護膜FPAS上に、液晶表示電圧を印加するように間隔を開けて配置された所定の幅を有する透明画素電極SPTと透明共通電極CLTの下部に、有機絶縁膜FAPS及び保護膜PASの積層絶縁膜を挟んで金属画素電極SPM、縦共通電極配線CLMD及びドレイン配線DLが配置されていることである。それぞれの透明電極幅は以下のように設定される。

【0053】

ドレイン配線DLを被覆する透明共通電極配線CLT幅はドレイン配線幅の少なくとも2倍以上必要である、これは、IPS液晶表示装置が基本的に液晶に共通電極電位と画素電位以外の電界が加わるとスメアやドメインが生じるため、そのシールドが必要なためである。一方、金属画素電極SPMと縦共通電極配線CLMD上の透明電極SPT及びCLTの幅は、これらが下部の金属電極と同電位であるため、金属電極であるSPM、CLMDの幅に制約されない。但し、ポジ型の液晶材料を用いたIPS液晶表示装置では透明電極上であっても光が透過しない。これは幅の広い電極上では横電界がかからず液晶分子が回転しないためである。これに対し、透明電極の端部からその幅の内部に向かって1.5μmまでの領域はフリンジの横電界がかかり透過する。以上の点で、金属画素電極SPM及び縦共通電極配線の幅は基本的に、それぞれその上部の透明画素電極SPT及び透明共通電極配線CLTと同じ幅かそれより狭く設定される。また、縦共通電極配線CLMDはその配線材料がドレイン配線DLと同じで基本的に低抵抗のTi/Al/Ti配線であり、その幅はプロセスルールで決まる最小値を設定しても配線遅延が小さくでき、開口率を低下させることはない特徴がある。特に、本実施例では、液晶駆動に不可欠な透明電極配線CLT下部に配置されており、新たに開口率を低下させないことも特徴の1つになっている。

【0054】

図3は図1の3−3’の線に沿った断面図である。本断面図は図1の平面図においてドレイン配線DL〜第1のコンタクトホールCNT1〜TFTのポリシリコン層PSI〜第2のコンタクトホールCNT2〜横共通電極配線CLMG上に層間絶縁膜ILIを介して乗り越え配置された金属画素電極SPM〜第3のコンタクトホールCNT3〜横共通電極配線CLMGと縦共通電極配線CLMDを接続する第4のコンタクトホールCNT4の断面を示す。図3の断面図の左側はTFTの断面である。ドレイン配線DL、金属画素電極SPMをいわゆるドレイン電極、ソース電極とし、ゲート配線GLをゲート電極として、ゲート絶縁膜GIを有するいわゆるMOS型TFTである。ULS上にp−Si層があり、ドレイン配線DL及び金属画素電極SPMはゲート絶縁膜GI及び層間絶縁膜ILIに開けられた第1のコンタクトホールCNT1及び第2のコンタクトホールCNT2を各々通じて、低温ポリシリコンPSIのリンを不純物としてドープされた高濃度n型層PSI(n+)に接続されている。該高濃度n型層PSI(n+)は導電性が高く、擬似的に配線部として働く。一方GL下のPSIはボロンを不純物としてドープされたp型層PSI(p)となっており、いわゆる半導体層として働き、GLにON電位で導通状態、OFF電位で非導通状態となるスイッチング動作を示す。ゲート配線GLにオン電圧が印加された場合、ゲート配線GL下部でゲート絶縁膜GI下部であり、ボロンを不純物としてドープされたp型層PSI(p)のゲート絶縁膜GI界面のポテンシャルが反転してチャネル層が形成され、n型化されTFTにオン電流が流れ、結果的に金属画素電極SPMへ電流が流れ液晶容量及び保持容量が充電される。保持容量Cstgは同図ように横共通電極配線CLMGを一方の電極、絶縁膜として層間絶縁膜ILI、他方の電極を金属画素電極SPMとして形成されている。保持容量Cstgは、同図のTFTのポリシリコンPSIに対してTFTガラス基板GLS1側からの表示のバックライトによる光照射で発生する電子、正孔のペヤで増加するリーク電流に対して液晶容量で決まる画像表示期間(保持期間)中の電位を保つために設定されている。この値を大きく設定できれば、表示画面上の均一性を極めて良好に保つことができる。

【0055】

図4は図1の4−4’の線に沿った断面図である。本断面図は主に、ゲート配線GLとTFTの低温ポリシリコンPSI及びこれらを有機保護膜を介して被覆している透明共通電極配線CLTから透過領域に至る断面構造を表す。

【0056】

図4の断面構造は左手側にゲート配線GL、右手側が透過領域である。ゲート配線GL及び低温ポリシリコンPSIは保護膜PAS及び有機保護膜FPAS上に配置された透明共通電極CLTで被覆されている。これはゲート配線GLの電位が透明共通電極CLTおよび透明画素電極SPTで挟まれた透過領域に、ゲート配線GLの電気力線が漏れ、表示の誤動作を起こさないようにするためである。

【0057】

本構造の特徴は上記ゲート配線及び低温ポリシリコン層を被覆するように配置された透明共通電極配線CLTが透明電極ながら極めて良質なブラックマトリクスBMの効果を示す点にある。図2に示すように、液晶を駆動させる電界Eは透明共通電極配線CLTと透明画素電極SPTの横電界である。IPS型液晶表示装置では、この横電界で液晶分子LCを回転させ直交する偏光板POLに対して透過率を変える。無電界あるいは横方向電界が小さい状態では偏光板がクロスニコル配置されているため、黒表示となる。電界が印加されると楕円偏光の透過が発生し、電界に応じて透過する。従って、無電界や横方向電界が小さい領域では、透明共通電極CLTがITOのような透明電極で形成された場合においてもTFTガラス基板GLS1側からのバックライト光は透過せず、観察者側であるCF基板GLS2から見ても良好な黒状態となる。一方、電圧印加状態では、透明電極の端部から電極内部へ約1.5μmの領域(例えばGL上のCLTの場合での領域の例を図4にWTとして示す)では、フリンジ状態の横電界成分があり、透過に寄与する。

【0058】

従って、TFTガラス基板GLS1側からのバックライト光の画像に対しては、図1の平面構造において、少なくとも低温ポリシリコンPSIを含むTFTとゲート配線GLを覆うように幅広く設定された透明共通電極CLTは、人間の目視時に、各画素の輪郭を明瞭にし、画像をくっきりとさせるBM同様の働きをする。図4において、その透明共通電極CLT上のWN領域、すなわち透明電極単体が存在し、かつ透明電極端部から1.5μm以上内側の領域は横方向電界成分がほとんどなく、液晶層透過中に光の偏向状態は影響を受けないため、最終的にCF基板上の偏光板POLで遮光される。例えば、低温ポリシリコンPSIが赤色着色してみえるはずが、完全な黒表示状態のBMに見える。ゲート配線GLの領域WRで,はこの金属で完全に遮光されるので、電界に係わらず黒状態になる。

【0059】

図4の断面図で示す通り、本実施例構造ではCF基板GLS2には従来のBMが形成されていない。このため本実施例構造を用いたIPS型の液晶表示装置はBM層形成工程が不要となるため、コスト低減が実現できる。外光に対しては、前記透明共通電極CLTは、極めて良好な反射の少ないBMの役割を果す。これは透明電極を遮光層として用いるからこその効果であり、かつその遮光層が観察側基板と対向する基板にあることで、一層反射が低減する。透明共通電極CLTのWNの領域では外光はCLT自身の吸収、保護膜PAS、有機保護膜FPAS、などで吸収されるが、反射率の高い金属層がないため観察者側への反射は少ない。一方、ゲート配線GL上はその材料はMoWであり、例えば、Alに比べては小さいが若干の反射は存在するが、上層の保護膜がPASなどを2回通過することとクロスニコル状態の偏光板POLの効果もあり小さい反射に止まる。このように、透明共通電極CLTをブラックマトリクスBMとして使用した場合、極めて反射の少ないBMが形成できる。さらに、CF基板にBMを形成する必要がなくなるため、上下基板の合わせ裕度が拡大し、生産性の向上が実現する。また合わせずれを見越した設計が不要となるため、従来BMとして遮光が必要な領域より合わせ裕度を見越して余分にBMで遮光されていた領域が透過領域となるため、開口率の向上が実現する。さらに、透明電極端部での遮光領域が黒表示時は電極上全領域、白表示時は電極端から1.5μmまでは透過領域となるため、くっきりと画像を表示する必要がある黒表示状態と、明るい表示が必要な白表示状態とで、動的かつ自動的に遮光領域が変化し、黒表示では遮光領域が広く、白表示では遮光領域が狭くなるまさに理想的なBMとして透明電極による遮光層は働く。これにより、画像のくっきりさの向上、コントラストの向上、及び輝度の向上という一見相反する事象を両立することが可能となった。

【0060】

次に、図3に示すようなNMOS型TFTの製造工程を図5〜図9及び図3を用いて説明する。

【0061】

厚さ0.7mm、サイズ730mm×920mmの歪点約670℃の無アルカリTFTガラス基板GLS1を洗浄後、SiH4とNH3とN2の混合ガスを用いたプラズマCVD法により膜厚50nmのSi3N4膜、続いて、テトラエトキシシランとO2の混合ガスを用いたプラズマCVD法により、膜厚120nmのSiO2膜の積層の下地絶縁膜ULSを形成する。本絶縁膜ULSは多結晶シリコン膜へのTFTガラス基板GLS1からのNa拡散を防止するためである。Si3N4、SiO2ともに形成温度は400℃である。なお、本願では半導体層として多結晶シリコンで代表するが、巨大結晶シリコン、連続粒界シリコン、アモルファスシリコンでもよい。

【0062】

次に、上にSiH4、Arの混合ガスを用いたプラズマCVD法によりほぼ真性(イントリンシック)の水素化非晶質シリコン膜を50nm形成する。成膜温度は400℃で、成膜直後水素量は約5at%である。次に基板を450℃で約30分アニールすることにより、水素化非晶質シリコン膜中の水素を放出させる。アニ−ル後の水素量は約1at%である。

【0063】

次に、波長308nmのエキシマレーザ光LASERを前記非晶質シリコン膜にフルエンス400mJ/cm2、で照射し、非晶質シリコン膜を溶融再結晶化させて、ほぼ真性の多結晶シリコン膜を得る。この時レーザビームは幅0.3mm、長さ200mmの細線状の形状であり、ビームの長手方向とほぼ垂直な方向に基板を10μmピッチで移動しながら照射した。照射時は窒素雰囲気とした。

【0064】

通常のホトリソグラフィ法により所定のレジストパターンを多結晶シリコン膜上に形成しCF4とO2の混合ガスを用いたリアクティブイオンエッチング法により多結晶シリコン膜PSIを所定の形状に加工する(図5)。

【0065】

次に、テトラエトキシシランと酸素の混合ガスを用いたプラズマCVD法により膜厚100nmのSiO2を形成しゲート絶縁膜GIを得る。この時のテトラエトキシシランとO2の混合比は1:50、形成温度は400℃である。引き続きイオン注入法によりよりBイオンを加速電圧33KeV、ドーズ量1E12(cm−2)で打ちこみ、n型TFTのチャネル領域のポリシリコン膜PSI(p)を形成する。

【0066】

次にスパッタリング法により、金属配線、例えばMoあるいはMoW膜を200nm形成後、通常のホトリソグラフィ法により所定のレジストパターンをMo膜上に形成し、混酸を用いたウェットエッチング法によりMo膜を所定の形状に加工し走査配線GLおよび第2の横共通電極配線CLMGを得る。

【0067】

エッチングに用いたレジストパターンを残したまま、イオン注入法によりよりPイオンを加速電圧60KeV、ドーズ量1E15(cm−2)で打ちこみ、n型TFTのソース、ドレイン領域PSI(n+)を形成する(図6)。上記でn型TFTのソース、ドレインがn+型の低温ポリシリコン膜PSI(n+)及びp型のチャネル領域のポリシリコン膜PSI(p)ができあがるが、以下のようにp型とn+型の間にPイオン濃度がn+型より少ないn型のLDD領域を作り、TFTのリーク電流を低減することができる(図示していない)。すなわち、エッチングに用いたレジストパターンを除去後、再度イオン注入法によりPイオンを加速電圧65KeV、ドーズ量2E13(cm−2)で打ちこみ、n型TFTのLDD領域を形成する。LDD領域の長さはMoをウェットエッチングしたときのサイドエッチング量で定められる。本実施例の場合約0.8μmである。この長さはMoのオーバーエッチング時間を変化させることで制御できる。

【0068】

次に、基板にエキシマランプまたはメタルハライドランプの光を照射するラピッドサーマルアニール(RAT)法により打ち込んだ不純物を活性化する。エキシマランプまたはメタルハライドランプ等の紫外光を多く含む光を用いてアニールすることにより、多結晶シリコン層PSIのみを選択的に加熱でき、ガラス基板が加熱されることによるダメージを回避できる。不純物の活性化は、基板収縮や曲がり変形等が問題にならない範囲で、450℃程度以上の温度での熱処理によっても可能である(図6)。

【0069】

次に、テトラエトキシシランと酸素の混合ガスを用いたプラズマCVD法により膜厚500nmのSiO2を形成し層間絶縁膜ILIを得る。この時のテトラエトキシシランとO2の混合比は1:5、形成温度は350℃である。

【0070】

次に、所定のレジストパターンを形成後、混酸を用いたウェットエッチング法により、前記層間絶縁膜に第1のコンタクトスルーホールCNT1、第2のコンタクトホールCNT2及び図1の平面図の第4のコンタクトホールCNT4を開孔する(図7)。

【0071】

続いて、スパッタリング法により、Tiを50nm、Al−Si合金を500nm、Tiを50nmを順次積層形成した後に所定のレジストパターンを形成し、その後BCl3とCl2の混合ガスを用いたリアクティブイオンエッチング法により一括エッチングし、ドレイン配線DL、金属画素電極SPM、縦共通電極配線CLMDを得る(図8)。

【0072】

SiH4とNH3とN2の混合ガスを用いたプラズマCVD法により膜厚300nmのSi3N4膜である保護膜PASを形成し、さらに、スピン塗布法によりアクリル系感光性樹脂を約3.5μmの膜厚で塗布し、所定のマスクを用いて露光、現像して前記アクリル系樹脂にスルーホールを形成する。次に230℃で20分ベークすることで、アクリル樹脂を焼成し、膜厚2.0μmの平坦化有機保護膜FPASを得る。続いて、前記有機保護膜FPASに設けたスルーホールパターンをマスクとして下層のSi3N4膜をCF4を用いたリアクティブイオンエッチング法により加工し、Si3N4膜に第3のコンタクトホールCNT3を形成する(図9)。

【0073】

このように有機保護膜FPASをマスクとして用いて下層の絶縁膜を加工することにより、一回のホトリソグラフィ工程で2層の膜をパターニングでき、工程を簡略化できる。

【0074】

最後にスパッタリング法によりITO膜等の透明導電膜を70nm形成し、混酸を用いたウェットエッチングにより所定の形状に加工して透明共通電極配線CLTおよび透明画素電極SPTを形成しアクティブマトリクス基板が完成する(図3)。以上6回のホトリソグラフィ工程で多結晶シリコンTFTが形成される。

【0075】

次に液晶パネルの概観の平面構造について説明する。図10は上下のガラス基板GLS1、GLS2を含む表示パネルのマトリクス(AR)周辺の要部平面を示す図である。このパネルの製造では、小さいサイズであればスループット向上のため1枚のガラス基板で複数個分のデバイスを同時に加工してから分割し、大きいサイズであれば製造設備の共用のためどの品種でも標準化された大きさのガラス基板を加工してから各品種に合ったサイズに小さくし、いずれの場合も一通りの工程を経てからガラスを切断する。

【0076】

図10は後者の例を示すもので、上下基板GLS1、GLS2の切断後を表している。いずれの場合も、完成状態では外部接続端子群Tg、Tdが存在する部分(図で上辺)はそれらを露出するように上側基板GLS2の大きさが下側基板GLS1よりも内側に制限されている。端子群Tg、Tdはそれぞれ後述するTFTガラス基板GLS1上で表示部ARの左右に配置された低温ポリシリコンTFTの走査回路GSCLへ供給する電源及びタイミングデータに関する接続端子、表示領域ARの上部でTFTガラス基板GLS1上に低温ポリシリコンTFTの映像信号回路DDCへの映像データあるいは電源データを供給するため端子Tdである。引出配線部を集積回路チップCHIが搭載されたテープキャリアパッケージTCP(図11)の単位に複数本まとめて名付けたものである。各群のマトリクス部から映像信号回路DDCを経て外部接続端子部に至るまでの引出配線は、両端に近づくにつれ傾斜している。これは、パッケージTCPの配列ピッチ及び各パッケージTCPにおける接続端子ピッチに表示パネルの映像信号端子Tdを合わせるためである。

【0077】

透明ガラス基板GLS1、GLS2の間にはその縁に沿って、液晶封入口INJを除き、液晶LCを封止するようにシールパターンSLが形成される。シール材は例えばエポキシ樹脂から成る。

【0078】

図2の断面構造で示した配向膜ORI層は、一例としてシールパターンSLの内側に形成される。液晶LCは液晶分子の向きを設定する下部配向膜ORIと上部配向膜ORIとの間でシールパターンSLで仕切られた領域に封入されている。

【0079】

この液晶表示装置は、下部透明TFTガラス基板GLS1側、上部透明CFガラス基板GLS2側で別個に種々の層を積み重ね、シールパターンSLを基板GLS2側に形成し、下部透明ガラス基板SUB1と上部透明ガラス基板GLS2とを重ね合わせ、シール材SLの開口部INJから液晶LCを注入し、注入口INJをエポキシ樹脂などで封止し、上下基板を切断することによって組み立てられる。

【0080】

図11は、図10に示した表示パネルに映像信号駆動ICを搭載したTCPとTFT基板GLS1上に低温ポリシリコンTFTで形成した信号回路DDCとの接続及びTFT基板GLS1に低温ポリシリコンTFTで形成した走査回路GSCLと外部とを接続した状態を示す上面図である。

【0081】

TCPはテープキャリアパッケージであり、駆動用ICチップがテープ・オートメイティド・ボンディング法により実装されたものである。PCB1は上記TCPやコントロールICであるTCON、その他電源用のアンプ、抵抗、コンデンサ等が実装された駆動回路基板である。CJはパソコンなどからの信号や電源を導入するコネクタ接続部分である。

【0082】

図12はテープキャリアパッケージTCPを液晶表示パネルの、信号回路用端子Tdに接続した状態を示す要部断面図である。テープキャリアパッケージTCPは異方性導電膜ACFによって液晶表示パネル接続される。TCPは電気的にはその出力端子がパネル側の接続端子Tdと接続され、TFTの保護膜PASおよび有機保護膜FPASの開口部を覆うように形成され、かつ透明共通電極CLTと同一工程で形成された透明電極ITOと接続されている。シールパターンSLの外側の上下ガラス基板の隙間は洗浄後エポキシ樹脂EPX等により保護され、TCPと上側CF基板GLS2の間には更にシリコン樹脂が充填され保護が多重化されている(図示していない)。また上下のガラス基板GLS2、GLS1の液晶LCに対するギャップは有機膜で形成された支柱SPCあるいはファイバでその高さが決定されている。

【0083】

表示マトリクス部の等価回路とその周辺回路の結線図を図13に示す。図中、DLはドレイン線を意味しDL1、DL2、DL3とその数字が画面左からの画面内のドレイン配線(映像信号線)を意味する、添字R、GおよびBがそれぞれ赤、緑および青画素に対応して付加されている。GLはゲート配線GLを意味し、GL1、GL2、とその数字が画面上部からの画面内のゲート線を意味する。添字1、2、は走査タイミングの順序に従って付加されている。CLXは横共通電極配線CLMGを意味し、CLX1、CLX2とその数字が画面上部からの画面内の共通電極配線を意味する。一方、CLYは縦共通電極配線CLMDを意味し、CLY1、CLY2とその数字が画面上部からの画面内の共通電極配線を意味する。

【0084】

ゲート配線GL(添字省略)はガラス基板上の走査回路GSCLに繋がれ、その走査回路への電源あるいはタイミング信号はガラス基板外部のPCB上に形成された電源及びタイミング回路SCCから供給される。 上記において低温ポリシリコンTFTで構成されたガラス基板上の走査回路は、冗長性を高めるために1本のゲート線(走査線)に対して左右の両側から給電されているが、画面サイズなどに応じて片側から給電しても良い。

【0085】

一方、ドレイン配線DLへの給電はガラス基板上の低温ポリシリコンTFTで構成された信号回路DDCから給電される。信号回路DDCはガラス基板の映像信号回路ICで構成された回路よりの映像データをR、G、Bの色データに応じて分配する機能を持つ。従って、ガラス基板上の信号回路からの接続端子数は画面内のドレイン配線数の三分の一である。

また、共通電極配線は、本実施例では、金属で構成された横共通電極配線CLX、縦共通電極配線CLY、と透明共通電極がある。横共通電極配線と縦共通配線は、図1で示したように、画素内で結線されマトリクス状の金属配線となっている。横共通電極配線CLXは、画面の左右に引き出され、まとめてインピーダンスの低い共通電極母線CLBに結線され、電源及びタイミング回路ICのSCCに結線される。縦共通電極配線CLYは下部に引き出され、インピーダンスの低い共通電極母線CLBに結線され、同じく電源回路SCCに至る。透明共通電極は、図1に示したように、画面内では前記横共通電極配線、縦共通電極配線と結線されず、画面外周で、左右方向では横共通電極配線、下部では縦共通電極配線と結線され、共通電極母線CLBに結線され同様に外部電源SCCにつながれる。図13では図示していないが、マトリクス状に構成されている。この共通電極は、画面内の画素のコモン電位を与える。

【0086】

画面内の低温ポリシリコンTFTは、n型のTFTであり、ゲート配線GLにゲート電圧を印加し、そのタイミングでドレイン線DLに給電されたドレイン電圧(データ)を共通電極配線との間の液晶容量Clcに給電することにより表示を行う。液晶容量Clcの電位を表示期間中に維持する能力を向上するために、横共通電極配線CLMGと図3に示すように金属画素電極SPMとの間に保持容量Cstgを形成する。CCはドレイン配線DLの断線を検査する低温ポリシリコンTFTで形成した検査回路であり、CPADは検査端子である。

【0087】

図14に本発明の液晶表示装置の駆動波形を示す。共通電極電圧Vcomを直流電圧とした場合の例を示す。ゲート電圧Vgは1ゲート線毎に順次走査し、ドレイン電位Vdに対して、画素の低温ポリシリコンTFTのしきい電圧を更に加算した電圧が印加された際に画素TFTがオン状態になり、図13に示した液晶容量Clcに充電される。 上記共通電極電圧Vcom、ゲート電圧Vg、ドレイン電圧Vdはそれぞれ図13の横共通電極配線CLX,縦共通電極配線CLY、図1に示した透明共通電極CLT、ゲート配線GL、ドレイン配線DLに印加される。本実施例では、ドレイン電圧Vdは、例えば、ノーマルブラックモードでの液晶表示で白表示を行う場合を示しており、ゲート線は1ライン毎に選択され、そのライン毎に共通電極電圧Vcomに対してプラス、マイナスの極性反転される。画素電位VpはTFTを通じて液晶容量Clcに充電されるが、奇数、偶数フレームで共通電極電位Vcomに対して反転される。特定のアドレスのTFTのゲート配線GLに対して、ゲート配線が選択されVgがVdより大きくなると液晶容量Clcに画像に対応する電位が充電されるが、上記のように次ぎのフレームになり、共通電極電位Vcomに対して反転されたVdが印加されるまで液晶容量Clcの電位は保持されなければならない。この保持率はTFTのオフ(リーク)電流が大きくなると低下する。これを防止するには、図13の等価回路の保持容量Cstgを大きく設定する必要がある。この保持容量Cstg大きくした場合、共通電極配線の寄生容量が大きい場合、配線遅延が増大し、輝度むら、スメア、さらには残像やフリッカの画面内均一性が保てなくなるが、図1、図3の平面及び断面構造に示すように、金属材料の横共通電極配線CLMGと縦共通電極配線CLMDを画面内で結線し、マトリクス状にして抵抗を小さくする構成としている。一方、透明共通電極CLTは画面内では有機絶縁膜状に画素間を繋ぐように結線され、画面内ではCLTと金属共通電極配線CLMG、CLMDは直接は結線されていない。しかしCLTの役割は影響容量の充電のみであり、前述のように抵抗の比較的高い材料でも適用可能である。さらに画面外部で低インピーダンスの図13の共通電極母線CLBに接続され、低抵抗化されている。これらの効果により、本願では保持容量Cstgを増加させた場合でも画面の画質均一性を高めることができる。

【0088】

図15は、液晶表示モジュールMDLの各構成部品を示す分解斜視図である。SHDは金属板から成る枠状のシールドケース(メタルフレーム)、LCWはその表示窓、PNLは液晶表示パネル、SPBは光拡散板、LCBは導光体、RMは反射板、BLはバックライト蛍光管、LCAはバックライトケースであり、図に示すような上下の配置関係で各部材が積み重ねられてモジュールMDLが組み立てられる。

【0089】

モジュールMDLは、シールドケースSHDに設けられた爪とフックによって全体が固定されるようになっている。バックライトケースLCAはバックライト蛍光管BL、光拡散板SPB光拡散板、導光体LCB、反射板RMを収納する形状になっており、導光体LCBの側面に配置されたバックライト蛍光管BLの光を、導光体LCB、反射板RM、光拡散板SPBにより表示面で一様なバックライトにし、液晶表示パネルPNL側に出射する。バックライト蛍光管BLにはインバータ回路基板PCB2が接続されており、バックライト蛍光管BLの電源となっている。

【0090】

(実施例2)

図17は本発明の第2の実施例を示す画素の平面図であり、図18はその図17における18−18’として一点鎖線で示した切断線での断面を示す。図面では切断部を分かりやすくするため、数字を○で囲い切断部を示している。

【0091】

図17は実施例1と同様にドレイン配線DLを横切る方向に主な透過部を4つもつIPS方式の画素パターンである。構成は実施例1に近いが大きな特徴は金属で構成された共通電極配線は、縦共通電極配線CLMDのみが配線されている点であり、図1で配置されていた横方向共通電極配線が除去されている。従って、保持容量形成に新たな構成を用いている。さらに、該構造により、開口率が実施例1に比べて向上することが出来た。

【0092】

保持容量Cstgは以下のような構成となっている。まず、ゲート配線GLと同一工程、材料で構成された保持容量電極STMを島状に加工する。これを第4のコンタクトホールCNT4を介して縦共通電極配線CLMDと結線する。一方、低温ポリシリコンPSIで構成されたTFTの第2のコンタクトホールCNT2から延びた金属画素電極SPMは、保持容量電極STM上に延びる。この金属画素電極SPMと保持容量電極STMは層間絶縁膜を介してその重なる面積部分が保持容量を構成する。透明画素電極SPTは第3のコンタクトホールCNT3を介して金属画素電極SPMと結線され、画素電位が液晶に給電させる。一方、透明共通電極配線CLTは、画面内では縦共通電極配線CLMDとは結線されないが、画面領域外で結線され共通電位を液晶に給電する。

【0093】

上記の構成により、新たに、2つの効果が得られる。第1は、図17の画素の平面図の4つの透過領域の内、ドレイン配線DLを被覆する透明電極配線CLTとその画素内の内側の透明画素電極SPTで規定される新たな開口部が、実施例1の図1の横共通電極配線が除去されることにより、形成されることである(図17のLL、LRで規定される領域)。これにより、明るいIPS型の液晶表示装置が提供できる。第2は、ドレイン配線DLと交差する横共通電極配線CLMGが除去されることで、ドレイン配線DLの寄生容量が低減される。これにより、図13のドレイン分割回路DDCの内蔵回路の分割数を増やすことができ、図11に示したTCPで構成された部材数を少なくできコストが低減できる。

【0094】

図17の18−18’切断線における断面図が図18である。映像信号となるドレイン電圧は、ドレイン配線DLから第1のコンタクトホールCNT1を介して低温ポリシリコンPSIで伝えられる。ゲート電圧GLにオン電圧が印加させるとMOS型TFTが動作し、映像電圧が、第2のコンタクトホールCNT2を介して接続された金属画素電極SPMへ伝えられ、最終的に第3のコンタクトホールを介して接続された透明画素電極SPTに伝えられ、液晶容量の一方の電位の画素電位となる。液晶を駆動する他方の電位である共通電圧は、透明共通電極配線CLTに印加される。図17のLRで示した新たな開口部は、この透明画素電極SPTと透明共通電極配線CLTに印加される横電界で新たな透過領域となり、明るい液晶表示装置が提供できる。

【0095】

さらに、本図でも明らかなように、CF基板にはブラックマトリクスは形成されておらず、低温ポリシリコンで形成されたTFTおよびゲート配線GLは有機保護膜FPAS上に配置された透明共通電極配線で覆われ、透明電極であるが、横電界がかからない領域を形成し、良好なブラックマトリクスの役目を果している。

【0096】

さらに本実施例では除去する共通電極配線を横共通電極配線CLMGとしたため、実施例1で説明した縦共通電極配線CLMDがドレイン配線DLと同層で、かつゲート配線GLを横切るために得られる保持容量に対してのゲート電位のキャンセル効果はそのまま奏することが出来る。

【0097】

(実施例3)

図19は本発明の第3の実施例を示す画素の平面図であり、図20は図19における20−20’として一点鎖線で示した切断線での断面を示す。図面では切断部を分かりやすくするため、数字を○で囲い切断部を示している。

【0098】

図19は実施例2と同様にドレイン配線DLを横切る方向に主な透過部を4つもつIPS方式の画素パターンである。構成は実施例2に近いが大きな特徴は、保持容量の下部電極がポリシリコンPSIで構成されて、このポリシリコンPSIは第5のコンタクトホールを介して縦共通電極配線CLMDと接続されて点である。これに伴い、保持容量を構成する絶縁膜のショート欠陥率が低減し、歩留りを一層向上した液晶表示装置となっている。

【0099】

保持容量Cstgは以下のような構成となっている。まず、薄膜トランジスタの低温ポリシリコンPSIを島状に加工する。これを第5のコンタクトホールCNT5を介して縦共通電極配線CLMDと結線する。一方、低温ポリシリコンPSIで構成されたTFTの第2のコンタクトホールCNT2から延びた金属画素電極SPMは、保持容量の下部電極を構成する低温ポリシリコンPSI上に延びる。この金属画素電極SPMと保持容量の下部電極を構成する低温ポリシリコンPSIはゲート絶縁膜と層間絶縁膜を介してその重なる面積部分が保持容量を構成する。透明画素電極SPTは第3のコンタクトホールCNT3を介して金属画素電極SPMと結線され、画素電位が液晶に給電させる。一方、透明共通電極CLTは、画面内では縦共通電極配線CLMDとは結線されないが、画面領域外で結線され共通電位を液晶に給電する。

【0100】

図19の20−20’切断線における断面図が図20である。映像信号となるドレイン電圧は、ドレイン配線DLから第1のコンタクトホールCNT1を介して低温ポリシリコンPSIで伝えられる。ゲート電圧GLにオン電圧が印加させるとMOS型TFTが動作し、映像電圧が、第2のコンタクトホールCNT2を介して接続された金属画素電極SPMへ伝えられ、最終的に第3のコンタクトホールを介して接続された透明画素電極SPTに伝えられ、液晶容量の一方の電位の画素電位となる。液晶を駆動する他方の電位である共通電圧は、透明共通電極配線CLTに印加される。図19のLRで示した新たな開口部は、この透明画素電極SPTと透明共通電極配線CLTに印加される横電界で新たな透過領域となり、明るい液晶表示装置が提供できる。

【0101】

保持容量Cstgの下部電極は低温ポリシリコンPSI(n+)で構成されているため、その絶縁膜はゲート絶縁膜GIと層間絶縁膜ILIの積層膜となるため、その絶縁耐圧は実施例3の保持容量の層間絶縁膜ILIの単層膜に比べて高い。これにより、ショート不良による点欠陥の少ないIPS型の液晶表示装置が提供できる。

【0102】

(実施例4)

図21は本発明の第4の実施例における画素の平面図、図22および図23は図21の平面図における21−21’線、22−22’線における断面構造である。

【0103】

図21の画素の平面パターンは、1画素のサイズの大きく、しかも画面サイズの大きい液晶テレビにて開口率を向上する構成を提供する。図21は横方向に10個の透過領域を有し、その10分割された櫛歯電極間の寸法はL1、L2、L3、L4、L5、L6、L7、L8、L9、L10と表記されている。各櫛歯電極間の間隔Lは、実施例1の図1とおおよそ同じである。本実施例は、大画面の高輝度タイプの液晶テレビに対して好適なIPS液晶表示装置での画素パターンである。低温ポリシリコンPSIを用いたTFTでは、図3に示すようにバックライトはTFTガラス基板側に配置されており、その光は直接低温ポリシリコンPSIに照射される。そのため、光照射リーク電流が増加して、画素電位が低下する問題がある。これに対処するには、1画素の保持容量を大きくして、さらにそれに伴い増加する共通電極配線の配線遅延を低減することが必要である。

【0104】

図21の画素では隣り合うドレイン配線DLとゲート配線GLに囲まれた1画素領域で、ドレイン配線DLと同一工程、材料で構成された縦共通電極配線CLMDはドレイン配線とほぼ平行して、透明共通電極配線CLTの下部に配置されている。縦共通電極配線CLMDは共通電位が印加されているので、その断面構造に対しては、図22に示すように、透明共通電極配線CLT下部に配置されなければならない。透明画素電極SPT下部に配置されると、画素電極SPTと透明共通電極配線CLTで規定される映像データを乱してしまうためである。従って、縦共通電極配線CLMDは、ドレイン配線DLから、1つの目の透明画素電極SPTより少なくとも1つの櫛歯間隔(図21におけるL9)を経て、その内側に平面的に配置させる必要がある。また、縦共通電極配線CLMDとドレイン配線は製造プロセス上は、同一工程、材料で構成させるので、製造工程中のゴミによりショートしやすく、ショートした場合は線上の欠陥となる。その点で、ドレイン配線DLより、画素内側に少なくとも2つの開口部(図21のL9、L10)を経て配置されるのは歩留り上も有利である。

【0105】

前記縦共通電極配線CLMDは第4のコンタクトホールを介して、横共通電極配線CLMGと接続され、画面上において金属のマトリクス配線となり、大きな保持容量を形成した場合でも配線遅延が少なく均一の画面表示が実現できている。保持容量は、図21の平面図においては、低温ポリシコンPSIのTFT部の第2のコンタクトホールCNT2に接続された金属画素電極SPMを上部電極とし、横共通電極配線CLMGを下部電極とする容量である。金属画素電極SPMと縦共通電極配線CLMDは同一工程、材料で構成されているため、互いに交差できない。従って、より大きい値の保持容量を得るには、図21の平面図および図22の断面図において、金属画素電極SPMは左側のドレイン配線DLに近い櫛歯状の透明画素電極SPTの下部に、縦共通電極配線CLMDは右側のドレイン配線DLに近い櫛歯状の透明共通電極配線CLT下部に配置される必要がある。そして、前記金属画素電極SPTと縦共通電極配線CLMDの間に少なくとも1個以上の透明共通電極CLTあるいは透明画素電極SPTを配置する構成とすることにより、保持容量をさらに大きい値とすることができ、液晶TV用途のような高輝度を要求される用途、これはすなわちバックライトの輝度が高く、保持容量としてより大きな値が要求される用途にて輝度むら、スメア、残像、フリッカの少ないIPS型液晶表示装置を提供することが出来る。

【0106】

上述の配置は(1)1画素の透過領域を6分割以上とし、(2)金属画素電極SPMを一方のドレイン配線DLに最隣接する櫛歯状の透明画素電極SPTの下部に配置し、(3)縦共通電極配線CLMDを他方のドレイン配線DL側で、かつ該ドレイン配線上とは異なる透明共通電極CLT下部に配置し、(4)金属画素電極SPTと縦共通電極配線CLMDの間に少なくとも1個以上の透明共通電極CLTあるいは透明画素電極SPTを配置する、ことにより実現できる。本実施例では図21、図22で示すように、10個の透過領域を有し、金属画素電極SPMと縦共通電極CLMDの間に6個の櫛歯状透明電極を有している。

【0107】

図23は横共通電極配線CLMGに沿った断面であり、保持容量の断面構成を示す。低温ポリシリコンPSIで構成したTFTに接続された金属画素電極SPMを上部電極とし、下部電極を横共通電極配線CLMGとし、絶縁膜は層間絶縁膜ILIとして構成している。横共通電極配線CLMGは保護膜PAS下部の縦共通電極配線CLMDと第4のコンタクトホールCNT4を介して接続され、その配線遅延時間を小さくしている。また、第3のコンタクトホールCNT3を介して金属画素電極SPMの電位は有機保護膜FPAS上の透明画素電極SPTに伝えられ液晶を駆動している。前述のように、縦共通電極配線CLMDは、金属画素電極SPMと同一層上配置のため、右手側のドレイン配線DLに近い位置に配置され、横共通電極配線CLMG上の金属画素電極SPMの面積を大きく、すなわち保持容量を大きくできている。

【0108】

(実施例5)

図24は本発明の第5の実施例における1画素の平面図、図25は図24の25−25’線に沿った断面構造である。

【0109】

図24の画素の平面パターンは、1画素のサイズの大きく、しかも画面サイズの大きい液晶テレビ対応に対応する。図24は10個の透過領域を有し、その10分割された櫛歯電極間の寸法はL1、L2、L3、L4、L5、L6、L7、L8、L9、L10と表記されている。各櫛歯間隔Lは、図21とおおよそ同じである。本実施例は、実施例4同様に、大画面の高輝度タイプの液晶テレビに対して好適なIPS液晶表示装置での画素パターンであるが、さらに低温ポリシリコンPSIを用いた回路をTFTガラス基板上に配置した場合にその駆動能力を最大限に活かした画素方式である。

【0110】

実施例1の図13に示すように、画素領域のドレイン配線DLはTFTガラス基板上の信号側内蔵回路DDCを経て、外部回路IDCに接続されている。実施例1では3本のドレイン線DLを一本のドレイン端子Tdを経て外部に接続される。従って、ガラス基板上に信号側内蔵回路DDCを内蔵しないアモルファスシリコンTFTを用いた液晶表示装置に比べて、外部回路IDCに使用するドライバICを1/3に減らせるのでコスト低減できる。一方、この場合、ドレイン配線DLはアモルファスシリコンTFTの液晶表示装置に比べて3倍の時間で映像電圧を書きこむ必要がある。このためドレイン配線DLの配線抵抗や容量を低減する必要がある。

【0111】

実施例4の図21に示すように、横共通電極配線CLMGはドレイン配線DLと絶縁膜を介して交差しており、該交差領域はドレイン配線の寄生容量となる。したがって、該交差領域を排除できればドレイン配線の寄生容量が低減でき、ドレイン配線の遅延時間を低減できる。

【0112】

図24は上記の目的に対応した1画素の平面図である。縦方向に延びる2本のドレイン配線DLの間には、10個の透過領域(その間隔をL1,L2…L10と表記)を有する。実施例4と同様、金属画素電極SPMは低温ポリシリコンPSIのTFTが配置された左手側のドレイン配線DLに近く配置され、L1とL2の透過領域に挟まれた透明画素電極SPT下部に配置されている。一方、縦共通電極配線CLMDは右手側のドレイン配線DL上でなく、かつ最も近い透明共通電極CLTであるL8とL9に挟まれた透明共通電極CLT下部に配置されている。このような配置は、透過領域が6分割以上の画素を有するIPS型の液晶表示装置で保持容量を最大化できる。

【0113】

保持容量は、平面パターン的には、以下の構成となる。すなわち、ゲート配線GLと同一工程、材料で構成した保持容量電極STMを形成する。この電極は、ドレイン配線DLとは交差配置せず、このためドレイン配線の遅延時間を低減することが出来る。前記保持容量電極STMが保持容量の一方の電極となり、第4のコンタクトホールCNT4を通じて縦共通電極配線CLMDと接続され共通電位が与えられる。保持容量の他方の電極は、実施例4と同様に低温ポリシリコンPSIの第2のコンタクトホールCNT2から延びる金属画素電極SPMである。これにより、前記保持容量電極STMと金属画素電極SPMの交差面積部分が保持容量を構成する。

【0114】

上記の構成の画素では、ゲート配線GLを除き、ドレイン配線DLと交差する保持容量配線が除かれておりドレイン配線容量が低減され、ドレイン配線を駆動するTFTガラス基板上の信号側回路が良好な動作を行う。

【0115】

さらに、上記のように、実施例4に比べて、横共通電極配線CLMGが除去された部分(図24の平面図のLL,LRの間隔で決まる透過領域)が新たな透過領域を形成し、より明るいIPS型液晶表示装置を提供できる。

【0116】

図25にその断面構造を示す。隣接するドレイン配線DLと保持容量電極STMを横切る断面図である。ドレイン配線DL間のゲート絶縁膜GI上にゲート配線GLと同一工程、材料で構成した保持容量電極STMを配置する。この電極はドレイン配線DL下部には延在されず容量を形成しない。一方、層間絶縁膜ILIに配置されたドレイン配線DLと同一工程、材料で構成した縦共通電極配線CLMDは、層間絶縁膜ILIに開口した第4のコンタクトホールCNT4を通じて、前記保持容量電極STMに共通電位を給電する。一方、金属画素電極SPMはTFTより画素電位を供給され、さらに有機保護膜FPASに開口された第3のコンタクトホールCNT3を通じて、透明画素電極SPTに画素電位を与える。保持容量Cstgは前記金属画素電極SPMを上部電極、絶縁膜を層間絶縁膜ILI、保持容量電極STMを下部電極として構成する。

【0117】

図25には、図24の画素平面図の新たな透過領域の断面構造が示されている。液晶の駆動電圧は、前記の透明画素電極SPTと透明共通電極CLTにより供給される。透明共通電極CLTは、画素内では、図24に示すように縦共通電極配線CLMDとは結線されていない。これは有機保護膜FPAS上にゲート配線GLのブラックマトリクスを兼用するように配置、さらにドレイン配線をも覆うように配置されており、画素領域全域としては網の目状に配置されている。透明共通電極CLTへの給電は、実施例1の図13に示したものと同様に、画面領域外の共通電極母船CLBにTFT基板GLS1上では最終的に接続され、外部電源回路SCCから共通電位が与えられる。上記2つの透明電極により、ドレイン配線DLと保持容量電極STMの間隙LL及びLRの新たな透過領域に液晶の駆動電圧が印加され、明るいIPS型の液晶表示装置が提供できる。

【0118】

(実施例6)

図26は本発明の第6の実施例における1画素の平面図、図27、図28は図26の27−27’線、28−28’線に沿った断面構造である。

【0119】

図26の画素の平面パターンは、1画素のサイズが大きく、しかも画面サイズの大きい液晶テレビ対応に対応する。図26は10個の透過領域を有し、その10分割された櫛歯電極間の寸法はL1、L2、L3、L4、L5、L6、L7、L8、L9、L10と表記されている。各櫛歯間隔Lは、実施例4の図21とおおよそ同じである。本実施例は、実施例4同様に、大画面の高輝度タイプの液晶テレビに対して好適なIPS液晶表示装置での画素パターンであるが、画面上の線欠陥や点欠陥の発生を低減した液晶表示装置を実現するものである。

【0120】

図26は、ドレイン配線DLと同一工程、材料で構成された金属の櫛歯電極あるいは電極配線間のショートで発生する線欠陥、点欠陥を低減する画素平面パターンである。隣合うゲート配線GL、ドレイン配線DL間に挟まれた1画素領域でドレイン配線DLと同一工程、材料で構成されているのは、低温ポリシリコンPSIのTFTの第2のコンタククトホールCNT2から横共通電極配線CLMG上へ延び、さらに透明画素電極SPTに第3のコンタクトホールCNT3を通じて画素電位を供給する金属画素電極SPMと、ドレイン配線DLとほぼ平行して縦方向へ伸び、第4のコンタクトホールCLMDを通じて横共通電極配線CLMGと接続されて共通電位を供給する縦共通電極配線CLMDである。

【0121】

上記、金属画素電極SPMは左手のドレイン配線DLとショートすると点欠陥であり、縦共通電極配線CLMDはドレイン配線DLとショートすると線欠陥である。また、金属画素電極SPMと縦共通電極配線CLMDが互いにショートすると点欠陥になる。

【0122】

製造工程中の微細な塵等の異物により確率的に発生するショート不良を低減するには、同一平面上で対向する金属電極あるいは配線の長さを短くするか、対向する電極間の距離を長くする必要がある。対向する電極間の距離が短い場合は、対向する長さが短くすれば良い。

【0123】

図26の画素平面構造では、縦共通電極配線CLMDと右手側のドレイン配線DLは4つの透過領域であるL7、L8、L9、L10と3つの透明電極でその間隔が構成されてショート確率が低減されている。一方、左手側のドレイン配線DLと金属画素電極SPMは3つの透過領域であるL1、L2、L3と2つの透明電極でその間隔が構成されている。また、前記金属画素電極SPMと縦共通電極配線CLMDは3つの透過領域L4、L5、L6と2つの透明電極でその間隔が形成されている。上記のように、隣り合うドレイン配線DL間に挟まれた金属画素電極SPM、縦方向共通電極配線CLMD及びドレイン配線DL間を画素の分割数に対しほぼ均等の間隔で配置されている。透過領域の数は4,3,3となり、完全には一致してはいないが、透過領域合計が10である場合には、分割数に対しほぼ均等な間隔ということが出来る。何故なら、上記4,3,3の分割に次いで近い分割数は4,4,2、あるいは5,3,2となり、いずれの場合でも分割数間に2以上の差が出てしまい、差が1である4,3,3の場合よりも分割数の差が拡大してしまうためである。

【0124】

さらに、上記のような、隣り合うドレイン配線DL間に挟まれた金属画素電極SPM、縦方向共通電極CLMD及びドレイン配線DL間を画素の分割数に対しほぼ均等の間隔で配置するには、少なくとも、2つの透過電極と3つの透過領域が金属画素電極SPMと隣接するドレイン配線DL間、及び金属画素電極SPMと縦共通電極配線CLMD間に配置される必要がある。これは画素分割数を8以上とすることが必要である。これにより、例えば8分割の場合では3,3,2として分割でき、差を1としてほぼ均等に配置することが出来る。また12分割の場合は、3,5,4として分割することにより、12分割の配置の中ではほぼ均等とすることが出来る。何故なら、4,4,4として分割するとSPMの下にSPTを配置することが出来ず、また5,5,2、として分割すると差が拡大するため、3,5,4の分割が均等な値となる。このように、可能な配置の中で実質的な均等配置を実現することにより、歩留りを最大とすることができる。なお、上記配置による歩留り向上の効果は、上記ドレイン配線、金属画素電極、縦共通電極の場合に限られるものではなく、同層で形成された電極間の構成であれば適用することにより同様の効果を奏することが出来る。

【0125】

例えば隣り合うドレイン配線DL間に金属の縦共通配線CLMDを有し、さらにTFTから画素電位を電圧する金属画素電極SPMを有する8分割以上の透過領域を有する画素構成の場合、それぞれの金属電極間に2つの透明電極の櫛歯と3つの透過領域を有する画素パターンが、金属電極間のショート不良の発生を最小にできるIPS型の液晶表示装置を提供できる。横共通電極配線CLMGパターン上の金属画素電極SPMと縦共通電極配線CLMD及び金属画素電極SPMと左手側のドレイン配線DLの間隔は狭いが、対向する長さは画素領域に及んでいない短い値であるため、ここでのショート確率は低い。

【0126】

図27は隣り合うドレイン配線間の断面図である。TFTガラス基板GLS1上の層間絶縁膜ILI上には、ドレイン配線DLの間に金属画素電極SPM及び縦共通電極配線CLMDが配置されている。ドレイン配線DL、金属画素電極SPM、縦共通電極配線CLMDはほぼ均等の間隔に配置され、前述のようにショート不良が発生しにくい配置となっている。各電極あるいは配線間には少なくとも2つ以上の透過領域が形成されている。また、金属画素電極SPM上には有機保護膜FPASを介して透明画素電極SPTが被覆され、SPTにはSPMと同一の電圧が印加される。縦共通電極配線CLMD上には有機保護膜FPASを介して透明共通電極CLTが被覆され、CLTにはCLMDと同一の電圧が印加されている。これにより有機保護膜FPAS上のそれぞれの櫛歯透明電極からの印加電圧が誤差なく液晶に電界Eを印加できることになる。

【0127】

図28は横共通電極配線CLMGに沿った断面図である。TFT基板GLS1上にはゲート配線GLと同一工程で形成された横共通電極配線CLMGが形成され、これを被覆する層間絶縁膜ILIに開口された縦共通電極配線と第4のコンンタクトホールCNT4で接続され低抵抗化されている。一方、金属画素電極SPMはその上部の有機保護膜FPASに開口された第3のコンタクトホールCNT3を通じて透明画素電極SPTと接続されている。ドレイン配線DLを被覆する有機保護膜FPAS上には透明共通電極CLTが被覆され、ドレイン配線DLの不要な電界を液晶に印加して誤動作しないような配置となっている。保持容量Cstgは下部電極を横共通電極配線CLMG、上部電極を金属画素電極SPM、絶縁膜を層間絶縁膜ILIとして構成されている。

【0128】

(実施例7)

図29は実施例1から実施例6のうちのいずれかを適用した液晶表示装置を搭載して液晶TVを構成した例である。液晶表示装置LCMがスピーカSPと共に配置され、画像、音声双方の出力を実現する。これにより、広視野角、高輝度、高コントラストで画面がくっきりとした表示を実現できた。さらに画面の輝度均一性も高いものとすることができた。また生産性が高く、歩留りが高いため、より低価格での液晶TVを提供することを可能とした。

【0129】

(実施例8)

図30は実施例1から実施例6のうちのいずれかを適用した液晶表示装置を搭載して液晶モニタを構成した例である。液晶表示装置LCMがパソコンなどからの情報を表示し、低消費電力、高輝度のモニタを実現する。これにより、広視野角、高輝度、高コントラストで画面がくっきりとした表示を実現できた。さらに画面の輝度均一性も高いものとすることができた。また生産性が高く、歩留りが高いため、より低価格での液晶モニタを提供することを可能とした。

【0130】

(実施例9)

図31は実施例1から実施例6のうちのいずれかを適用した液晶表示装置を搭載して一体型パソコンを構成した例である。図はノートPCの例であり、キーボードKBまで一体に構成されている。むろんこれに限らず、いわゆる液晶パソコンのような、液晶部と演算装置部が同一の筐体中に構成されていれば良い。液晶表示装置LCMがパソコンなどからの情報を表示し、低消費電力、高輝度の表示を実現する。これにより、広視野角、高輝度、高コントラストで画面がくっきりとした表示を実現できた。さらに画面の輝度均一性も高いものとすることができた。また生産性が高く、歩留りが高いため、より低価格での一体型パソコンを提供することを可能とした。

【0131】

(実施例10)

本実施例では実施例1から9のうちのいずれかに開示の思想を用いて縦電界方式、すなわちTN方式、VA方式、PVA方式、MVA方式、OCB方式、ASV方式などで保持容量の増加により安定した表示と歩留りの向上を実現した。なお、該TN方式、VA方式、PVA方式、MVA方式、OCB方式、ASV方式の方式自体はいずれも公知のものであり、そこに本願の実施例開示の思想を適用した点に違いがある。

【0132】

上述の実施例の効果は、かならずしも横電界型に限定されるものとは限らず、上記各縦電界方式でもその効果の一部もしくは全部を奏することが出来る。この場合、共通電極配線は保持容量配線として機能することとなり、TFT基板上の画素電極の代わりに対向するCF基板上に共通電極を形成することとなる。

【0133】

本願の各実施例で開示の技術思想は、その思想の範囲内であれば本願明細書の開示範囲である。

【0134】

【発明の効果】

以上詳述したように、本発明の主に低温ポリシリコンTFTで構成されたIPS表示方式の液晶表示装置により、明るく、環境に対する安定性が高く、生産性が高く、歩留りが高く、輝度均一性に優れ、コントラスト比が高く、さらに画像間の区切りが明確になる高画質で信頼性の高い液晶表示装置を提供することができる。

【図面の簡単な説明】

【図1】本発明の一実施例によるTFT液晶表示装置の画素の要部平面図である。

【図2】図1の2−2’線に沿った画素の要部断面図である。

【図3】図1の3−3’線に沿った画素の要部断面図である。

【図4】図1の4−4’線に沿った画素の要部断面図である。

【図5】本発明の一実施例によるTFT液晶表示装置のTFT基板の第1ホト工程後までの製造方法を説明するための断面図である。

【図6】本発明の一実施例によるTFT液晶表示装置のTFT基板の第2ホト工程後までの製造方法を説明するための断面図である。

【図7】本発明の一実施例によるTFT液晶表示装置のTFT基板の第3ホト工程後までの製造方法を説明するための断面図である。

【図8】本発明の一実施例によるTFT液晶表示装置のTFT基板の第4ホト工程後までの製造方法を説明するための断面図である。

【図9】本発明の一実施例によるTFT液晶表示装置のTFT基板の第5ホト工程後までの製造方法を説明するための断面図である。

【図10】LCDセルの全体平面図である。

【図11】LCDセルにPCB基板とTABを接続した全体平面図である。

【図12】LCDセルのTABとドレイン側引き出し端子部付近の断面図である。

【図13】本発明の一実施例のTFT―LCDの概略の等価回路を表す平面図である。

【図14】本発明の一実施例のTFT―LCDの画素の駆動波形を表すタイミングチャートである。

【図15】本発明のモジュール構成の一例を示す説明図である。

【図16】本発明の一実施例による偏光板と初期配向方向の関係を説明する図である。

【図17】本発明の他の実施例によるTFT液晶表示装置の画素の平面図である。

【図18】図17の18−18’に沿った要部断面図である。

【図19】本発明の他の実施例によるTFT液晶表示装置の画素の平面図である。

【図20】図19の20−20’に沿った要部断面図である。

【図21】本発明の他の実施例を表すTFT液晶表示装置の画素の平面図である。

【図22】図21の22−22’の線に沿った要部断面図である。

【図23】図21の23−23’線に沿った要部断面図である。

【図24】本発明の他の実施例によるTFT液晶表示装置の画素の平面図である。

【図25】図24の25−25’線に沿った要部断面図である。

【図26】本発明の他の実施例によるTFT液晶表示装置の画素の平面図である。

【図27】図26の27−27’線に沿った要部断面図である。

【図28】図26の28−28’線に沿った要部断面図である。

【図29】本発明を適用した液晶TVの模式図である。

【図30】本発明を適用した液晶モニタの模式図である。

【図31】本発明を適用した一体型パソコンの模式図である。

【符号の説明】

CJ…コネクタ部、CLMD…縦共通電極配線、CLMG…横共通電極配線、CLT…透明共通電極、CPAD…検査パッド、CNT1…ドレイン配線とSiアイランドをつなぐコンタクトホール、CNT2…金属画素電極とSiアイランドをつなぐコンタクトホール、CNT3…金属画素電極と透明画素電極をつなぐコンタクトホール、CNT4…縦共通電極配線と横共通電極配線をつなぐコンタクトホール、Cstg…保持容量、DDC…ガラス基板上のドレイン分割回路、DL…ドレイン配線、EPX…エポキシ樹脂、CF…カラーフィルタ層、FIL…カラーフィルタ層、FPAS…有機保護膜、GFPC…ゲートFPC、GI…ゲート絶縁膜、GL…ゲート配線、GLS1…TFTガラス基板、GLS2…CFガラス基板、IDC…外付けのドレイン回路、INJ…封入口、ILI…層間絶縁膜、LC…液晶(分子)、LCB…導光板、MDL…モジュール、OC…カラーフィルタのオーバコート膜、OLI…配向膜、PAS…保護絶縁膜、POL…偏光板、PSI…p−Siアイランド、PSI(p)…p型p−Si半導体層、PSI(n+)…n+型p−Si半導体層、RM…反射板、SPB…拡散フィルム、SPC…支柱、SHD…シャーシ、SPM…金属画素電極、SPT…透明画素電極、STM…保持容量電極、SSC…電源、コントロール回路、TCP…テープキャリアパッケージ、ULS…下地絶縁膜、SP…スピーカ、LCM…液晶表示装置、SW…スイッチ、KB…キーボード。

Claims (6)

- 透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成されそれぞれの画素は少なくとも共通電極配線と共通電極と画素電極とを有する液晶表示装置において、

前記共通電極配線は、前記画素領域で前記ゲート配線延在方向に延在された第1の共通電極配線と前記ドレイン配線延在方向に延在された第2の共通電極配線を含み、該第1の共通電極配線と該第2の共通電極配線は第1の絶縁膜で離間され、該第1の共通電極配線と該第2の共通電極配線は第1の絶縁膜に設けられた開口部で接続され、該開口部上には第2の絶縁膜が形成されていることを特徴とする液晶表示装置。 - 前記第1の共通電極配線と第2の共通電極配線は前記画素領域で前記共通電極との間に少なくとも前記第2の絶縁膜を有し、かつ前記共通電極は前記ドレイン配線上に少なくとも前記第2の絶縁膜を介して前記ドレイン配線より幅広く配置されている部分を含むことを特徴とする請求項1記載の液晶表示装置。

- 透明な第1の基板と第2の基板に挟まれた液晶層とカラーフィルタ層とを有し、

前記第1の基板上には複数のゲート配線と、前記複数のゲート配線とマトリクス状に交差する複数のドレイン配線と、前記ゲート配線とドレイン配線のそれぞれの交点に対応して形成された薄膜トランジスタを有し、隣接するゲート配線とドレイン配線とで囲まれる領域で画素領域が構成され、それぞれの画素は少なくとも共通電極配線と画素電極とを有する液晶表示装置において、

前記画素領域に第1の島状の電極を有し、第1の島状の電極を被覆する第1の絶縁膜に開口部を有し、前記ドレイン配線延在方向に延在された共通電極配線を有し、該第1の島状の電極と該共通電極配線が前記開口部で接続され、該第1の島状の電極が下部電極を構成し、前記薄膜トランジスタのソースに接続され前記第1絶縁膜上に形成された第2の島状の電極が上部電極を構成し保持容量を構成することを特徴とする液晶表示装置。 - 前記第1の基板上に、前記ドレイン配線上に被覆された絶縁膜上に構成された共通電極を有し、該共通電極は隣接する画素間でマトリクス状に接続して構成され、かつ該共通電極は前記ドレイン配線上に被覆された絶縁膜上で前記ドレイン配線より幅広く配置されている部分を含むことを特徴とする請求項3記載の液晶表示装置。

- 前記保持容量の絶縁膜は前記薄膜トランジスタのゲート配線を被覆する無機絶縁膜であることを特徴とする請求項3記載の液晶表示装置。

- 前記第1の島状の電極は前記薄膜トランジスタの半導体層で構成され、前記保持容量の絶縁膜は少なくとも前記薄膜トランジスタのゲート絶縁膜を含むことを特徴とする請求項3記載の液晶表示装置。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002008283A JP3881248B2 (ja) | 2002-01-17 | 2002-01-17 | 液晶表示装置および画像表示装置 |

| TW091135042A TW591282B (en) | 2002-01-17 | 2002-12-03 | Liquid crystal display device and image display device |

| US10/310,915 US20030133066A1 (en) | 2002-01-17 | 2002-12-06 | Liquid crystal display device and image display device |

| KR10-2003-0001644A KR20030063131A (ko) | 2002-01-17 | 2003-01-10 | 액정 표시 장치 및 화상 표시 장치 |

| CNB031015182A CN1220909C (zh) | 2002-01-17 | 2003-01-16 | 液晶显示装置和图像显示装置 |

| CNB2005100916042A CN100390624C (zh) | 2002-01-17 | 2003-01-16 | 液晶显示装置和图像显示装置 |

| CNB200610100017XA CN100428029C (zh) | 2002-01-17 | 2003-01-16 | 液晶显示装置 |

| US11/503,977 US7304708B2 (en) | 2002-01-17 | 2006-08-15 | Liquid crystal display device and image display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002008283A JP3881248B2 (ja) | 2002-01-17 | 2002-01-17 | 液晶表示装置および画像表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003207797A JP2003207797A (ja) | 2003-07-25 |

| JP2003207797A5 JP2003207797A5 (ja) | 2005-06-16 |

| JP3881248B2 true JP3881248B2 (ja) | 2007-02-14 |

Family

ID=19191407

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002008283A Expired - Fee Related JP3881248B2 (ja) | 2002-01-17 | 2002-01-17 | 液晶表示装置および画像表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US20030133066A1 (ja) |

| JP (1) | JP3881248B2 (ja) |

| KR (1) | KR20030063131A (ja) |

| CN (3) | CN100390624C (ja) |

| TW (1) | TW591282B (ja) |

Families Citing this family (73)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20050014414A (ko) | 2003-07-31 | 2005-02-07 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치 |

| JP4604145B2 (ja) * | 2003-08-20 | 2010-12-22 | 奇美電子股▲ふん▼有限公司 | Ips液晶ディスプレイ及び輝点の滅点化方法 |

| KR101080356B1 (ko) * | 2003-10-13 | 2011-11-04 | 삼성전자주식회사 | 박막 트랜지스터, 박막 트랜지스터 표시판 및 표시 장치 |

| KR100959367B1 (ko) * | 2003-10-13 | 2010-05-25 | 엘지디스플레이 주식회사 | 횡전계형 액정표시장치 |

| KR100958246B1 (ko) * | 2003-11-26 | 2010-05-17 | 엘지디스플레이 주식회사 | 횡전계 방식의 액정표시장치 및 그 제조방법 |

| JP3914913B2 (ja) | 2003-11-28 | 2007-05-16 | 鹿児島日本電気株式会社 | 液晶表示装置 |

| CN100356252C (zh) * | 2003-12-27 | 2007-12-19 | 鸿富锦精密工业(深圳)有限公司 | 有源矩阵型液晶显示装置 |

| KR101071711B1 (ko) * | 2003-12-29 | 2011-10-12 | 엘지디스플레이 주식회사 | 횡전계형 액정표시장치 |

| JP4627148B2 (ja) * | 2004-04-09 | 2011-02-09 | 株式会社 日立ディスプレイズ | 表示装置 |

| JP4516348B2 (ja) * | 2004-04-21 | 2010-08-04 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| KR101055202B1 (ko) * | 2004-08-05 | 2011-08-08 | 엘지디스플레이 주식회사 | 횡전계방식 액정표시소자 |

| KR100672216B1 (ko) * | 2004-11-03 | 2007-01-22 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 |

| KR20070004229A (ko) * | 2005-07-04 | 2007-01-09 | 삼성전자주식회사 | 박막트랜지스터기판 및 이의 제조방법 |

| JP2007171938A (ja) * | 2005-11-24 | 2007-07-05 | Seiko Epson Corp | 液晶装置、電子機器 |

| EP1793266B1 (en) | 2005-12-05 | 2017-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Transflective Liquid Crystal Display with a Horizontal Electric Field Configuration |

| JP2007226175A (ja) * | 2006-01-26 | 2007-09-06 | Epson Imaging Devices Corp | 液晶装置及び電子機器 |

| EP2924498A1 (en) | 2006-04-06 | 2015-09-30 | Semiconductor Energy Laboratory Co, Ltd. | Liquid crystal desplay device, semiconductor device, and electronic appliance |

| TWI641897B (zh) | 2006-05-16 | 2018-11-21 | 日商半導體能源研究所股份有限公司 | 液晶顯示裝置 |

| US7847904B2 (en) | 2006-06-02 | 2010-12-07 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic appliance |

| KR20080003078A (ko) * | 2006-06-30 | 2008-01-07 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

| JP2008065300A (ja) * | 2006-08-11 | 2008-03-21 | Nec Lcd Technologies Ltd | 液晶表示装置 |

| JP4952425B2 (ja) * | 2006-08-21 | 2012-06-13 | ソニー株式会社 | 液晶装置および電子機器 |

| WO2008038432A1 (en) * | 2006-09-27 | 2008-04-03 | Sharp Kabushiki Kaisha | Active matrix substrate and liquid crystal display device provided with same |

| KR20080046039A (ko) * | 2006-11-21 | 2008-05-26 | 삼성전자주식회사 | 액정조성물과 이를 포함하는 액정표시장치 |

| US7872720B2 (en) * | 2007-03-01 | 2011-01-18 | Seiko Epson Corporation | Liquid crystal device and projector |

| JP5151212B2 (ja) * | 2007-03-30 | 2013-02-27 | Nltテクノロジー株式会社 | 液晶パネル |

| KR101391884B1 (ko) | 2007-04-23 | 2014-05-07 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| KR101396720B1 (ko) * | 2007-04-23 | 2014-05-20 | 엘지디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| KR101341008B1 (ko) * | 2007-08-09 | 2013-12-13 | 엘지디스플레이 주식회사 | 횡전계 액정 표시 장치 |

| CN101339341B (zh) * | 2007-07-06 | 2011-08-24 | 奇美电子股份有限公司 | 液晶显示面板及其制作方法及使用其的液晶显示装置 |

| JP2009020374A (ja) * | 2007-07-13 | 2009-01-29 | Hitachi Displays Ltd | 液晶表示装置 |

| EP2023195B1 (en) * | 2007-08-09 | 2017-04-05 | LG Display Co., Ltd. | Liquid crystal display device |

| KR101308462B1 (ko) * | 2007-08-09 | 2013-09-16 | 엘지디스플레이 주식회사 | 액정 표시 장치 |

| KR101473839B1 (ko) | 2007-10-17 | 2014-12-18 | 엘지디스플레이 주식회사 | 횡전계방식 액정표시장치 및 그 제조방법 |

| US8047442B2 (en) * | 2007-12-03 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US7659627B2 (en) * | 2007-12-05 | 2010-02-09 | Fujifilm Corporation | Photodiode |

| KR20090080009A (ko) * | 2008-01-19 | 2009-07-23 | 삼성전자주식회사 | 패널형 디스플레이장치 |

| JP5132341B2 (ja) * | 2008-02-01 | 2013-01-30 | 株式会社ジャパンディスプレイウェスト | 液晶表示パネル |

| KR101570532B1 (ko) * | 2008-10-30 | 2015-11-20 | 엘지디스플레이 주식회사 | 액정표시장치 |

| US8681305B2 (en) * | 2008-12-24 | 2014-03-25 | Lg Display Co., Ltd. | Liquid crystal display device comprising a common line pattern formed correspond to the conductive seal pattern, a transparent electrode pattern overlapping the common line pattern with an insulating layer interposed there between, the transparent electrode pattern having a width equal to or less than that of the common line pattern |

| KR101609597B1 (ko) * | 2009-02-16 | 2016-04-07 | 삼성디스플레이 주식회사 | 회로기판 및 이를 갖는 표시패널 어셈블리 |

| US20110085121A1 (en) * | 2009-10-08 | 2011-04-14 | Hydis Technologies Co., Ltd. | Fringe Field Switching Mode Liquid Crystal Display Device and Method of Fabricating the Same |

| JP5642978B2 (ja) * | 2010-02-12 | 2014-12-17 | 株式会社ジャパンディスプレイ | 液晶表示装置および電子機器 |

| JP2012053372A (ja) * | 2010-09-03 | 2012-03-15 | Hitachi Displays Ltd | 液晶表示装置 |

| JP2012078692A (ja) * | 2010-10-05 | 2012-04-19 | Hitachi Displays Ltd | 表示装置 |

| JP5530971B2 (ja) * | 2011-04-19 | 2014-06-25 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| JP5555663B2 (ja) * | 2011-05-19 | 2014-07-23 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| TWI451179B (zh) * | 2011-11-17 | 2014-09-01 | Au Optronics Corp | 畫素結構及其製造方法 |

| CN103176315A (zh) * | 2011-12-20 | 2013-06-26 | 群康科技(深圳)有限公司 | 显示装置和电子装置 |

| JP2013190662A (ja) * | 2012-03-14 | 2013-09-26 | Japan Display Inc | 液晶表示装置 |

| KR101888034B1 (ko) * | 2012-05-31 | 2018-09-11 | 엘지디스플레이 주식회사 | 횡전계형 액정표시장치용 어레이 기판 및 이를 구비한 입체 영상 표시장치 |

| KR20140088810A (ko) * | 2013-01-03 | 2014-07-11 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| JP2014178490A (ja) * | 2013-03-14 | 2014-09-25 | Japan Display Inc | 液晶表示装置 |

| JP2014209212A (ja) | 2013-03-29 | 2014-11-06 | 株式会社ジャパンディスプレイ | 液晶表示装置及び電子機器 |

| KR102081827B1 (ko) * | 2013-07-02 | 2020-04-16 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| US20150035741A1 (en) * | 2013-07-30 | 2015-02-05 | Samsung Display Co., Ltd. | Display apparatus |

| TWI509337B (zh) * | 2013-09-16 | 2015-11-21 | Au Optronics Corp | 畫素結構及其製造方法以及顯示面板 |

| JP2015090434A (ja) * | 2013-11-06 | 2015-05-11 | 株式会社ジャパンディスプレイ | 液晶表示装置およびその製造方法 |

| KR102140815B1 (ko) * | 2013-12-09 | 2020-08-04 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| KR102046848B1 (ko) * | 2013-12-20 | 2019-11-20 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR20150078308A (ko) * | 2013-12-30 | 2015-07-08 | 삼성디스플레이 주식회사 | 표시 장치 및 그 리페어 방법 |

| JP2015203775A (ja) * | 2014-04-14 | 2015-11-16 | 株式会社ジャパンディスプレイ | 表示装置及び電子機器 |

| CN103969859B (zh) * | 2014-04-22 | 2016-08-24 | 京东方科技集团股份有限公司 | 一种显示用基板及显示装置 |

| KR20150136685A (ko) * | 2014-05-27 | 2015-12-08 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| CN104880873B (zh) | 2015-06-29 | 2019-04-02 | 合肥鑫晟光电科技有限公司 | 像素结构、显示面板和像素结构的制作方法 |

| KR102477984B1 (ko) * | 2015-12-11 | 2022-12-15 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| CN105652547A (zh) * | 2016-04-15 | 2016-06-08 | 京东方科技集团股份有限公司 | 阵列基板、其制造方法、显示面板及显示装置 |

| TWI637624B (zh) * | 2017-05-09 | 2018-10-01 | 友達光電股份有限公司 | 畫素陣列 |

| CN107132711A (zh) * | 2017-06-20 | 2017-09-05 | 深圳市华星光电技术有限公司 | 阵列基板和液晶显示面板 |

| JP7062490B2 (ja) * | 2018-03-29 | 2022-05-06 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP2019184864A (ja) * | 2018-04-12 | 2019-10-24 | シャープ株式会社 | 表示装置 |

| CN110596976A (zh) * | 2019-08-22 | 2019-12-20 | 武汉华星光电技术有限公司 | 一种显示面板及其显示装置 |

| CN115917421A (zh) * | 2020-09-07 | 2023-04-04 | 京东方科技集团股份有限公司 | 阵列基板及显示面板 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2701698B2 (ja) * | 1993-07-20 | 1998-01-21 | 株式会社日立製作所 | 液晶表示装置 |

| CN1154490A (zh) * | 1995-12-08 | 1997-07-16 | Lg半导体株式会社 | 薄膜晶体管的液晶显示装置及其制造方法 |

| US5852485A (en) * | 1996-02-27 | 1998-12-22 | Sharp Kabushiki Kaisha | Liquid crystal display device and method for producing the same |

| JP3199221B2 (ja) * | 1996-02-27 | 2001-08-13 | シャープ株式会社 | 液晶表示装置およびその製造方法 |

| TW412659B (en) * | 1996-03-14 | 2000-11-21 | Citizen Watch Co Ltd | Liquid crystal display |

| JP3481074B2 (ja) | 1997-04-25 | 2003-12-22 | 松下電器産業株式会社 | 液晶表示素子 |

| KR100268104B1 (ko) * | 1997-08-13 | 2000-10-16 | 윤종용 | 공통 전극 라인을 갖는 평면 구동 방식 액정 표시 장치 및그 제조 방법 |

| KR100477130B1 (ko) * | 1997-09-25 | 2005-08-29 | 삼성전자주식회사 | 평면구동방식액정표시장치의박막트랜지스터기판및제조방법 |

| JPH11125840A (ja) | 1997-10-24 | 1999-05-11 | Sharp Corp | 液晶表示装置の製造方法及び液晶表示装置 |

| KR100519205B1 (ko) * | 1998-03-19 | 2005-10-06 | 세이코 엡슨 가부시키가이샤 | 액정장치, 투사형 표시장치 및 전자기기 |

| JP3458382B2 (ja) * | 1998-11-26 | 2003-10-20 | セイコーエプソン株式会社 | 電気光学装置及びその製造方法並びに電子機器 |

| KR20060064020A (ko) * | 1999-06-11 | 2006-06-12 | 마쯔시다덴기산교 가부시키가이샤 | 액정 표시 장치 |

| KR100736114B1 (ko) * | 2000-05-23 | 2007-07-06 | 엘지.필립스 엘시디 주식회사 | 횡전계 방식의 액정표시장치 및 그 제조방법 |

| JP2002131767A (ja) * | 2000-10-27 | 2002-05-09 | Hitachi Ltd | 液晶表示装置 |

| TW469496B (en) * | 2001-01-19 | 2001-12-21 | Hannstar Display Corp | Electrode arrangement structure of In-Plane switching mode LCD |

| US6917406B2 (en) * | 2001-03-16 | 2005-07-12 | Hannstar Display Corp. | Electrode array structure of IPS-LCD |

| JP4019697B2 (ja) * | 2001-11-15 | 2007-12-12 | 株式会社日立製作所 | 液晶表示装置 |

-

2002

- 2002-01-17 JP JP2002008283A patent/JP3881248B2/ja not_active Expired - Fee Related

- 2002-12-03 TW TW091135042A patent/TW591282B/zh not_active IP Right Cessation

- 2002-12-06 US US10/310,915 patent/US20030133066A1/en not_active Abandoned

-

2003

- 2003-01-10 KR KR10-2003-0001644A patent/KR20030063131A/ko not_active Application Discontinuation

- 2003-01-16 CN CNB2005100916042A patent/CN100390624C/zh not_active Expired - Lifetime

- 2003-01-16 CN CNB200610100017XA patent/CN100428029C/zh not_active Expired - Lifetime

- 2003-01-16 CN CNB031015182A patent/CN1220909C/zh not_active Expired - Lifetime

-

2006

- 2006-08-15 US US11/503,977 patent/US7304708B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20060274250A1 (en) | 2006-12-07 |

| CN100390624C (zh) | 2008-05-28 |

| US7304708B2 (en) | 2007-12-04 |

| KR20030063131A (ko) | 2003-07-28 |

| CN100428029C (zh) | 2008-10-22 |

| TW591282B (en) | 2004-06-11 |

| CN1432855A (zh) | 2003-07-30 |

| US20030133066A1 (en) | 2003-07-17 |

| CN1721934A (zh) | 2006-01-18 |

| CN1877429A (zh) | 2006-12-13 |

| TW200304009A (en) | 2003-09-16 |

| JP2003207797A (ja) | 2003-07-25 |

| CN1220909C (zh) | 2005-09-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3881248B2 (ja) | 液晶表示装置および画像表示装置 | |

| KR100511817B1 (ko) | 액정 표시 장치 | |

| JP4085170B2 (ja) | 液晶表示装置 | |

| JP4019697B2 (ja) | 液晶表示装置 | |

| US7630046B2 (en) | Liquid crystal display device | |

| JPH10186410A (ja) | 液晶表示装置 | |

| JP2804261B2 (ja) | 液晶表示装置 | |

| JP2801591B2 (ja) | 液晶表示装置 | |

| JPH1124104A (ja) | 液晶表示装置 | |

| JPH1055000A (ja) | 液晶表示装置 | |

| JPH10206897A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040915 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040915 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061023 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061109 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3881248 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101117 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S631 | Written request for registration of reclamation of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313631 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313121 Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111117 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121117 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121117 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131117 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |