JP2015516693A - 電子集積のための3次元モジュール - Google Patents

電子集積のための3次元モジュール Download PDFInfo

- Publication number

- JP2015516693A JP2015516693A JP2015512167A JP2015512167A JP2015516693A JP 2015516693 A JP2015516693 A JP 2015516693A JP 2015512167 A JP2015512167 A JP 2015512167A JP 2015512167 A JP2015512167 A JP 2015512167A JP 2015516693 A JP2015516693 A JP 2015516693A

- Authority

- JP

- Japan

- Prior art keywords

- module

- cavity

- substrate

- contact

- conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000010354 integration Effects 0.000 title description 2

- 239000000758 substrate Substances 0.000 claims abstract description 146

- 238000004891 communication Methods 0.000 claims abstract description 10

- 239000011810 insulating material Substances 0.000 claims abstract description 10

- 238000000034 method Methods 0.000 claims description 55

- 239000003990 capacitor Substances 0.000 claims description 18

- 238000004519 manufacturing process Methods 0.000 claims description 15

- 238000009966 trimming Methods 0.000 claims description 12

- 230000008878 coupling Effects 0.000 claims 5

- 238000010168 coupling process Methods 0.000 claims 5

- 238000005859 coupling reaction Methods 0.000 claims 5

- 230000000149 penetrating effect Effects 0.000 claims 1

- 238000013461 design Methods 0.000 description 23

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 239000000919 ceramic Substances 0.000 description 10

- 239000000463 material Substances 0.000 description 9

- 238000013459 approach Methods 0.000 description 6

- 238000005553 drilling Methods 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 230000001939 inductive effect Effects 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000010276 construction Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000007650 screen-printing Methods 0.000 description 3

- 238000005245 sintering Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 2

- 238000003780 insertion Methods 0.000 description 2

- 230000037431 insertion Effects 0.000 description 2

- 238000001465 metallisation Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000005457 optimization Methods 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 238000002360 preparation method Methods 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 229910000859 α-Fe Inorganic materials 0.000 description 2

- 238000010146 3D printing Methods 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 238000004026 adhesive bonding Methods 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000012938 design process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 239000012777 electrically insulating material Substances 0.000 description 1

- 230000005672 electromagnetic field Effects 0.000 description 1

- 239000008393 encapsulating agent Substances 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000000696 magnetic material Substances 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- SWELZOZIOHGSPA-UHFFFAOYSA-N palladium silver Chemical compound [Pd].[Ag] SWELZOZIOHGSPA-UHFFFAOYSA-N 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- GGCZERPQGJTIQP-UHFFFAOYSA-N sodium;9,10-dioxoanthracene-2-sulfonic acid Chemical compound [Na+].C1=CC=C2C(=O)C3=CC(S(=O)(=O)O)=CC=C3C(=O)C2=C1 GGCZERPQGJTIQP-UHFFFAOYSA-N 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0284—Details of three-dimensional rigid printed circuit boards

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/13—Mountings, e.g. non-detachable insulating substrates characterised by the shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

- H01L23/14—Mountings, e.g. non-detachable insulating substrates characterised by the material or its electrical properties

- H01L23/15—Ceramic or glass substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5381—Crossover interconnections, e.g. bridge stepovers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5384—Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0652—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/14—Structural association of two or more printed circuits

- H05K1/144—Stacked arrangements of planar printed circuit boards

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/183—Components mounted in and supported by recessed areas of the printed circuit board

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/306—Lead-in-hole components, e.g. affixing or retention before soldering, spacing means

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/36—Assembling printed circuits with other printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4697—Manufacturing multilayer circuits having cavities, e.g. for mounting components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/146—Mixed devices

- H01L2924/1461—MEMS

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

- H01L2924/15155—Shape the die mounting substrate comprising a recess for hosting the device the shape of the recess being other than a cuboid

- H01L2924/15156—Side view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/162—Disposition

- H01L2924/1627—Disposition stacked type assemblies, e.g. stacked multi-cavities

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/16—Inspection; Monitoring; Aligning

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/17—Post-manufacturing processes

- H05K2203/171—Tuning, e.g. by trimming of printed components or high frequency circuits

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49004—Electrical device making including measuring or testing of device or component part

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49126—Assembling bases

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/4913—Assembling to base an electrical component, e.g., capacitor, etc.

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/4913—Assembling to base an electrical component, e.g., capacitor, etc.

- Y10T29/49139—Assembling to base an electrical component, e.g., capacitor, etc. by inserting component lead or terminal into base aperture

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/53—Means to assemble or disassemble

- Y10T29/53022—Means to assemble or disassemble with means to test work or product

Abstract

Description

本出願は2012年5月17日出願の米国暫定特許出願61/648,098(特許文献1);2012年6月3日出願の米国暫定特許出願61/654,888(特許文献2);および2012年7月12日出願の米国暫定特許出願61/670,616(特許文献3)の恩恵を主張する。これら全ての暫定出願はここに参照として採り入れられる。

これらの矛盾する要求はチップ設計やパッケージに対する高度に集積したアプローチの開発へと導いた。例えばマルチチップモジュール(MCMs)は一般的に単一基板上に多重の集積回路(ICs)または半導体ダイスを含み、場合によってはさらにディスクリート部品を含む。マルチチップモジュール(MCMs)基板はその後プリント回路基板上に単一部品として組み立てられる。いくつかの先進MCMは「チップスタック」パッケージを使用し、その中では半導体ダイスは垂直構造に積み重ねられ、それによりMCM足跡のサイズを減少させている(高さ増加のコストを払って)。この種の設計のいくつかは「システムインパッケージ」とも呼ばれる。

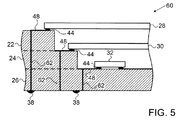

従って本発明の1実施形態によれば、空洞を内包する絶縁材料からなる基板を含む電子モジュールが提供される。空洞内の第1の導電性接点は空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成される。空洞を取り囲む基板の表面上の第2の導電性接点は、空洞の上をまたいで搭載される少なくとも1つの第2の電子部品に接触するように構成される。基板内の導電性トレースは第1と第2の導電性接点と電気通信する。

少なくとも1つの第2の電子部品が、その空洞の上をまたいで、その空洞を取り囲む基板の表面上に、第2の導電性接点と接触して搭載される。

本明細書に記載される本発明の実施形態は新規のタイプの電子モジュールを提供する。それは多重のICチップおよび他の部品(受動ディスクリート部品および微小電気機械部品、光学部品および他の多機能部品を含む)が高い部品密度で3次元(3D)組立体の中に一緒に搭載されることを可能にする。このようなモジュールは異なる制作工程で生産される部品に適したプラットフォームを形成し、そして特殊材料の3D設計の中への組み込みをサポートする。このモジュール設計はまた熱拡散を最適化し、したがってシステムの電力特性を向上させ、一方で集積した相互配線は高いレベルの信頼性を確実にする。本発明の実施形態によるモジュールはシステムの性能の最適化および製品の市場までのコストと時間の削減に有用である。

・異なる機能、材料および生産工程の部品を分離する。

・各部品の性能およびコストの最適化。

・多機能部品の3D絶縁フレーム上での容易な組立て。

・最小の数の信頼できる標準相互配線。

・改良された熱拡散と向上した信頼性。

1.広範囲の絶縁材料が使用可能であり、それには例えば、積層板およびセラミック(低温同時焼成セラミックス−LTCC)の両方を含む。

2.フレームの生産にコスト効率のよい生産技術が使用可能である。

3.フレームが、無線周波数(RF)回路の用途で使用される優れた高周波特性を持つ。

4.フレーム上に部品を組み立てる際に既存組立技術が使用可能である。

5.フレームの開口空洞設計により電子部品のみならず微小電気機械システム(MEMS)および光学部品の使用に適している。

6.以下の実施例に示されるような異なるサイズの開口空洞により、高い部品密度の真の3D多重層構造を構築するための、底部層の小さな部品からトップ層の大きめのICおよびインターポーザまでのチップの同時搭載が、高コストのチップ埋め込みの必要なく可能である。

7.接地面がフレームの裏面に形成できる。

8.部品組み立ての後、選択肢としてフレームが既存の技術および材料を使用してカプセル封入されてもよい。

9.柔軟な設計原則により、各部品(ディスクリート部品およびICを両方含む)が最適な材料および製造技術を使用して生産されることが可能になり、それによりモジュール性能の最適化が可能になる。従って各部品の性能は設計の初期段階で最適化される。内部の、非誘導性接続は部品の高速、低損失の相互配線を可能にする。

10.フレーム設計が高い信頼性をサポートする。各部品は事前試験が可能である。その設計は組み立てられたモジュール全体のトリミングを可能にし、そしてそれによりモジュールの性能を向上させることができる。熱拡散が適切な相互配線および高い熱伝導率の特殊材料を使用して最適化できる。フリップチップまたはチップスケール形状因子のICがコスト効率化および信頼性のために使用可能である。モジュールは前述のようにカプセル封入できる。

11.以下に記載するように、単一のフレームが3D構築ブロックとして機能できる。これらの構築ブロックは大きめの、より複雑な、高ハイアラーキの多次元構造の構築と組立を可能にする。

12.これら実施形態のモジュール性は、コスト、電力経費、機械的応力除去、速度の向上、および試験プログラムの標準化などのシステム特性に関して他の多くの利点を提供する。

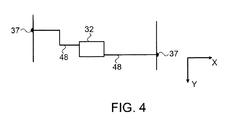

ビアのパターンはそれぞれの特定のモジュールに対して特別に設計されそして生産されうるが、しかし類似のパッケージに対し標準ビアパターンを提供することにより設計工程は簡略化でき、生産コストは低減できる。このような標準パターンに対しては使用可能な全てのビアが形成されるが、しかしそれらのいくつかだけがモジュールの電気スキームに依存して導電線で接続される。

1.個々の層の調製(空洞を含む)。

2.導電線と接点パッドの必要なパターンを作るための各層に対する金属パターニング。

3.積み重ね。

4.垂直ビアの掘削とメッキ。

5.外部終端の追加。

6.部品の組み立て。

1.すべての層に対しグリーンセラミックテープの調製(必要な空洞及びビアを有する)−すべての層に対する導電線、ビアおよび接点パッドのスクリーン印刷を含む。

2.個々の層を押圧し多層構造を形成する。

3.焼結。

4.外部端末の追加。

5.部品の組み立て。

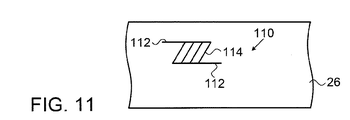

図1で図解されたように、基板21は、抵抗器、コンデンサ、およびインダクタなどの埋め込みコンポーネント34を含んでもよい。このような部品は、実質的に任意の種類の電子モジュールで使用可能であるが、しかしそれらはフィルタ、バラン及び変圧器のような様々なタイプのRF回路やチップの構築に特に有用である。埋め込まれた部品は、部品32(図1)のような基板の実装面の上に配置された他のディスクリート部品と組み合わせて使用することができる。この組み合わせは、フィルタやマルチプレクサのようなより複雑な種類のRF(およびその他の)モジュールの構築を可能にする。

図1に示され、そしてそれに続くいくつかの図に繰り返されるフレーム外形は、本発明の原理に基づいて形成できる構造を代表しているが、それらは例示のためだけに示され、そして制限するものではない。以下の図では多くのさらなる事例が示される。他の代替的な空洞ベースの、多重レベルのモジュール設計は本明細書を読んだ後の当業者には明白であり、それらは本発明の範囲内にあると見做される。

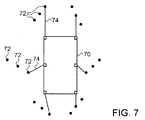

例えば図18は本発明の代替的実施形態による、多重の多重レベル電子モジュール192,194,196からなる組立体190の図解的側面図である。この場合、モジュール196は、モジュール196の側面とそれぞれモジュール192と194のそれぞれトップ面と底面にある接点パッド178を使用して、モジュール192と194の間に垂直に搭載される。この配置はモジュールにより囲まれた中央空洞198を画定する。

Claims (58)

- 電子モジュールであって、

空洞を内包する絶縁材料からなる基板と;

前記空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成された前記空洞内の第1の導電性接点と;

前記空洞の上をまたいで搭載される少なくとも1つの第2の電子部品に接触するように構成される、前記空洞を取り囲む前記基板の表面上の第2の導電性接点と;そして

前記第1と第2の導電性接点と電気通信する前記基板内の導電性トレースと;

を有することを特徴とする、モジュール。 - 前記導電性接点は、物理的および電気的に前記電子部品の下面上の第2の接点パッドに接触するように構成される、前記基板上の第1の接点パッドを有する、ことを特徴とする請求項1に記載のモジュール。

- 前記第2の電子部品は、集積回路チップおよびインターポーザからなる部品のグループから選択される、ことを特徴とする請求項1または2に記載のモジュール。

- 前記少なくとも1つの第1の電子部品は、さらなる集積回路チップおよびディスクリート部品からなるさらなる部品のグループから選択される、ことを特徴とする請求項3に記載のモジュール。

- 前記導電性トレースは、前記空洞を取り囲む前記基板の表面に直角な方向に前記基板を貫通するビアを有する、ことを特徴とする請求項1−4のいずれかに記載のモジュール。

- 前記ビアは事前設定された格子の上にレイアウトされる、ことを特徴とする請求項5に記載のモジュール。

- 前記ビアはそれぞれの前記接点に対して事前に設定された1組の角度で配置される、ことを特徴とする請求項5に記載のモジュール。

- 少なくとも1つの前記ビアは前記第1の導電性接点と前記第2の導電性接点とを接続するように構成される、ことを特徴とする請求項5に記載のモジュール。

- 前記基板の外部表面上にプリント回路基板に接触するための複数の接点パッドを有し、ここにおいて少なくとも1つの前記ビアは、前記導電性接点の1つと前記外部表面上の前記接点パッドの1つとを接続するように構成される、ことを特徴とする請求項5に記載のモジュール。

- 前記導電性トレースは、前記空洞を取り囲む前記基板の表面に平行な1つまたはそれ以上の平面に配置される導電線を有する、ことを特徴とする請求項1−9のいずれかに記載のモジュール。

- 前記導電線は均一でない厚みを有する、ことを特徴とする請求項10に記載のモジュール。

- 前記空洞を取り囲む前記基板の表面に直角な前記基板の側面に複数の接点パッドを有し、ここにおいて少なくとも1つの前記導電線は、前記導電性接点の1つと前記基板の側面の前記接点パッドの1つとを接続するように構成される、ことを特徴とする請求項10に記載のモジュール。

- 前記導電線は少なくとも、前記空洞の内部表面により画定される第1の平面に配置される第1の線と、前記空洞を取り囲む前記基板の前記表面を含む第2の平面に配置される第2の線と、を有することを特徴とする請求項10に記載のモジュール。

- 前記基板の外部表面の中または上に埋め込まれた1つまたはそれ以上のディスクリート電子部品を有する、ことを特徴とする請求項1−13のいずれかに記載のモジュール。

- 前記ディスクリート電子部品は前記部品または前記モジュール全体が事前設定の動作特性に適合するように構成されそしてトリミングされる、ことを特徴とする請求項14に記載のモジュール。

- 前記基板の外部表面の中または上に埋め込まれた前記部品は、抵抗、フラットコンデンサ、櫛歯型コンデンサ、インダクタ、および他のトリミング可能な部品からなる部品グループから選択される、ことを特徴とする請求項14に記載のモジュール。

- 前記第1の導電性接点が配置される前記空洞は内部空洞であり、ここにおいて、前記第2導電性接点が配置される、前記内部空洞を取り囲む前記基板の表面は内部表面であり、ここにおいて、

前記基板は、前記少なくとも1つの第2の電子部品を含み、そして前記基板の外部表面に取り囲まれるように構成される外部空洞を有し、前記外部表面の上に第3の導電性接点が配置され、前記第3の導電性接点は前記外部空洞の上をまたいで搭載される少なくとも1つの第3の電子部品と接触するように構成される、

ことを特徴とする請求項1−16のいずれかに記載のモジュール。 - 前記空洞は前記基板の第1の側に形成され、そして前記基板は、前記基板の前記第1の側とは反対側の第2の側の上に1つまたはそれ以上の第3の電子部品を搭載するように構成される、ことを特徴とする請求項1−17のいずれかに記載のモジュール。

- 前記基板の前記第1の側に形成された空洞は第1の空洞であり、そして第2の空洞は、前記基板の第2の側に形成され、前記第2の空洞内に搭載される少なくとも1つの前記第3の電子部品を含むように構成される、ことを特徴とする請求項18に記載のモジュール。

- 前記基板の前記第2の側は、少なくとも別の1つの前記第3の電子部品が前記第2の空洞の上をまたいで搭載されるように構成される、ことを特徴とする請求項19に記載のモジュール。

- 電気的および機械的に結合した少なくとも第1と第2のモジュールを含む電子組立体であって、それぞれの前記モジュールは:

空洞を内包する絶縁材料からなる基板と;

前記空洞内に搭載された少なくとも1つの第1の電子部品と接触するように構成された前記空洞内の第1の導電性接点と;

前記空洞の上をまたいで搭載される少なくとも1つの第2の電子部品に接触するように構成される、前記空洞を取り囲む前記基板の表面上の第2の導電性接点と;そして

前記第1と第2の導電性接点と電気通信する前記基板内の導電性トレースと;

を有する、ことを特徴とする組立体。 - 少なくとも前記第1と第2のモジュールは前記モジュールの外部表面にそれぞれ接点パッドを有し、前記接点パッドは、前記導電性トレースと接続しそして少なくとも前記第1と第2のモジュール間の電気通信を提供するため前記組立体内で結合されている、ことを特徴とする請求項21に記載の組立体。

- 少なくとも前記第1のモジュールは前記組立体内で前記第2のモジュールの上に積み重ねられている、ことを特徴とする請求項21または22に記載の組立体。

- 前記第1のモジュールは、前記第1のモジュール内の前記空洞とは反対側の、前記第1のモジュールの基板の下面が、前記第2のモジュール内に形成された前記空洞の上をまたぎそして塞ぐように積み重ねられる、ことを特徴とする請求項23に記載の組立体。

- 前記第1のモジュールは、前記第1のモジュール内の前記空洞が前記第2のモジュール内に形成された前記空洞に対面するように積み重ねられる、ことを特徴とする請求項23に記載の組立体。

- 前記第1のモジュールは、前記第1のモジュール内の前記空洞を取り囲む前記第1のモジュールの前記基板の前記表面に直角な、前記第1のモジュールの側面上の接点パッドにより、前記第2のモジュールに接続される、ことを特徴とする請求項23に記載の組立体。

- 前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に平行なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項26に記載の組立体。

- 前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に直角なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項26に記載の組立体。

- 絶縁性ベースを有し、ここにおいて少なくとも前記第1と第2のモジュールが前記絶縁ベースの表面上に並んで搭載され、前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が前記表面に直角な向きに開口する、ことを特徴とする請求項21または22に記載の組立体。

- 電子モジュールを作成する方法であって、

空洞を内包する絶縁材料からなる基板であって、前記空洞内の第1の導電性接点と、前記空洞を取り囲む前記基板の表面上の第2の導電性接点と、そして前記第1と第2の導電性接点と電気的に通信する前記基板内の導電性トレースと、を有する基板を提供するステップと;

少なくとも1つの第1の電子部品を前記第1の導電性接点と接触して前記空洞内に搭載するステップと;そして

少なくとも1つの第2の電子部品を、前記空洞の上をまたいで前記空洞を取り囲む前記基板の前記表面上に前記第2の導電性接点と接触して搭載するステップと;

を有することを特徴とする方法。 - 前記基板を提供するステップは、前記基板上に第1の接点パッドを形成するステップを有し、前記第1の接点パッドは物理的および電気的に前記電子部品の下面上の第2の接点パッドに接触するように構成される、ことを特徴とする請求項30に記載の方法。

- 前記第2の電子部品は、集積回路チップおよびインターポーザからなる部品のグループから選択される、ことを特徴とする請求項30または31に記載の方法。

- 前記少なくとも1つの第1の電子部品はさらなる集積回路チップおよびディスクリート部品からなるさらなる部品のグループから選択される、ことを特徴とする請求項32に記載の方法。

- 前記導電性トレースは、前記空洞を取り囲む前記基板の表面に直角な方向に前記基板を貫通するビアを有する、ことを特徴とする請求項30−33のいずれかに記載の方法。

- 前記ビアは事前設定された格子の上にレイアウトされる、ことを特徴とする請求項34に記載の方法。

- 前記ビアはそれぞれの前記接点に対して1組の事前に設定された角度で配置される、ことを特徴とする請求項34に記載の方法。

- 少なくとも1つの前記ビアは前記第1の導電性接点と前記第2の導電性接点とを接続するように構成される、ことを特徴とする請求項34に記載の方法。

- 前記基板を提供するステップは、前記基板の外部表面上にプリント回路基板に接触するための複数の接点パッドを形成するステップを有し、ここにおいて少なくとも1つの前記ビアは、前記導電性接点の1つと前記外部表面上の前記接点パッドの1つとを接続するように構成される、ことを特徴とする請求項34に記載の方法。

- 前記導電性トレースは、前記空洞を取り囲む前記基板の表面に平行な1つまたはそれ以上の平面に配置される導電線を有する、ことを特徴とする請求項30−38のいずれかに記載の方法。

- 前記導電線は均一でない厚みを有する、ことを特徴とする請求項39に記載の方法。

- 前記基板を提供するステップは、前記空洞を取り囲む前記基板の表面に直角な前記基板の側面に複数の接点パッドを形成するステップを有し、ここにおいて少なくとも1つの前記導電線は、前記導電性接点の1つと前記基板の側面上の前記接点パッドの1つとを接続するように構成される、ことを特徴とする請求項39に記載の方法。

- 前記導電線は少なくとも、前記空洞の内部表面により画定される第1の平面に配置される第1の線と、前記空洞を取り囲む前記基板の前記表面を含む第2の平面に配置される第2の線と、を有することを特徴とする請求項39に記載の方法。

- 前記基板を提供するステップは、前記基板の外部表面の中または上に1つまたはそれ以上のディスクリート電子部品を埋め込むステップを有する、ことを特徴とする請求項30−42のいずれかに記載の方法。

- 前記1つまたはそれ以上のディスクリート電子部品を埋め込むステップは、前記部品または前記モジュール全体が事前設定の動作特性に適合するように前記埋め込まれた部品の少なくとも1つをトリミングするステップを有する、ことを特徴とする請求項43に記載の方法。

- 前記基板の外部表面の中または上に埋め込まれた前記部品は、抵抗、フラットコンデンサ、櫛歯型コンデンサ、インダクタ、および他のトリミング可能な部品からなる部品グループから選択される、ことを特徴とする請求項43に記載の方法。

- 前記第1の導電性接点が配置される前記空洞は内部空洞であり、ここにおいて、前記第2導電性接点が配置される、前記内部空洞を取り囲む前記基板の前記表面は内部表面であり、ここにおいて、

前記基板を提供するステップは、前記少なくとも1つの第2の電子部品を含み、そして前記基板の外部表面に取り囲まれるように構成される外部空洞を形成するステップを有し、前記外部表面の上に第3の導電性接点が配置され、前記第3の導電性接点は前記外部空洞の上をまたいで搭載される少なくとも1つの第3の電子部品と接触するように構成される、

ことを特徴とする請求項30−45のいずれかに記載の方法。 - 前記空洞は前記基板の第1の側に形成され、そして前記方法は、前記基板の前記第1の側とは反対側の第2の側の上に1つまたはそれ以上の第3の電子部品を搭載するステップを有する、ことを特徴とする請求項30−46のいずれかに記載の方法。

- 前記基板の前記第1の側に形成された空洞は第1の空洞であり、そして前記基板を提供するステップは、少なくとも1つの前記第3の電子部品を含むように構成される第2の空洞を前記基板の第2の側に形成するステップを有し、ここに前記第3の電子部品は前記第2の空洞内に搭載されることを特徴とする請求項47に記載の方法。

- 前記1つまたはそれ以上の第3の電子部品を搭載するステップは、少なくとも1つの別の前記第3の電子部品を前記第2の空洞の上をまたいで搭載するステップを有する、ことを特徴とする請求項48に記載の方法。

- 電子組立体を作成する方法であって、請求項30−49のいずれかの方法に従って作成された、少なくとも第1と第2のモジュールを電気的および機械的に結合させるステップを有する、ことを特徴とする方法。

- 前記少なくとも第1と第2のモジュールを結合させるステップは、前記モジュールの外部表面上のそれぞれの接点パッドを使用して少なくとも前記第1と第2のモジュールを結合させるステップを有し、前記接点パッドは、前記導電性トレースと接続し、そして少なくとも前記第1と第2のモジュール間の電気通信を提供するため前記組立体内で結合されている、ことを特徴とする請求項50に記載の方法。

- 前記少なくとも前記第1と第2のモジュールを結合させるステップは、少なくとも前記第1のモジュールを前記組立体内の前記第2のモジュールの上に積み重ねるステップを有する、ことを特徴とする請求項50または51に記載の方法。

- 前記第1のモジュールは、前記第1のモジュール内の前記空洞と反対側の、前記第1のモジュールの基板の下面が、前記第2のモジュール内に形成された前記空洞の上をまたぎそしてふさぐように積み重ねられる、ことを特徴とする請求項52に記載の方法。

- 前記第1のモジュールは、前記第1のモジュール内の空洞が前記第2のモジュール内に形成された空洞に対面するように積み重ねられる、ことを特徴とする請求項52に記載の方法。

- 前記少なくとも前記第1のモジュールを前記第2のモジュールの上に積み重ねるステップは、前記第1のモジュール内の前記空洞を取り囲む前記第1のモジュールの基板の表面に直角な、前記第1のモジュールの側面の上の接点パッドにより、前記第1のモジュールを前記第2のモジュールに接続するステップを有する、ことを特徴とする請求項52に記載の方法。

- 前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に平行なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項55に記載の方法。

- 前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞が相互に直角なそれぞれの向きに開口するように、前記第1のモジュールが配向する、ことを特徴とする請求項55に記載の方法。

- 前記少なくとも第1と第2のモジュールを結合させるステップは、少なくとも前記第1と第2のモジュールを前記絶縁ベースの表面上に並んで搭載するステップを有し、一方で前記第1のモジュール内の前記空洞と前記第2のモジュール内の前記空洞は前記表面に直角な向きに開口する、ことを特徴とする請求項50または51に記載の方法。

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201261648098P | 2012-05-17 | 2012-05-17 | |

| US61/648,098 | 2012-05-17 | ||

| US201261654888P | 2012-06-03 | 2012-06-03 | |

| US61/654,888 | 2012-06-03 | ||

| US201261670616P | 2012-07-12 | 2012-07-12 | |

| US61/670,616 | 2012-07-12 | ||

| PCT/IB2013/053749 WO2013171636A1 (en) | 2012-05-17 | 2013-05-09 | Three-dimensional modules for electronic integration |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015516693A true JP2015516693A (ja) | 2015-06-11 |

| JP2015516693A5 JP2015516693A5 (ja) | 2016-05-19 |

Family

ID=49583222

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015512167A Pending JP2015516693A (ja) | 2012-05-17 | 2013-05-09 | 電子集積のための3次元モジュール |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US20150131248A1 (ja) |

| EP (1) | EP2850649A4 (ja) |

| JP (1) | JP2015516693A (ja) |

| CN (1) | CN104285278A (ja) |

| TW (1) | TW201411800A (ja) |

| WO (1) | WO2013171636A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2018123414A1 (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | インターポーザ基板、回路モジュール、インターポーザ基板の製造方法 |

| JP2019509631A (ja) * | 2016-02-24 | 2019-04-04 | マジック リープ, インコーポレイテッドMagic Leap,Inc. | 光エミッタのための薄型相互接続子 |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9155198B2 (en) | 2012-05-17 | 2015-10-06 | Eagantu Ltd. | Electronic module allowing fine tuning after assembly |

| US9156680B2 (en) * | 2012-10-26 | 2015-10-13 | Analog Devices, Inc. | Packages and methods for packaging |

| DE102013219833B4 (de) * | 2013-09-30 | 2020-02-13 | Infineon Technologies Ag | Halbleitermodul mit leiterplatte und vefahren zur hertellung eines halbleitermoduls mit einer leiterplatte |

| JP6320231B2 (ja) * | 2014-08-04 | 2018-05-09 | 株式会社ワコム | 位置指示器及びその製造方法 |

| WO2016051533A1 (ja) * | 2014-09-30 | 2016-04-07 | 富士機械製造株式会社 | 部品実装装置 |

| US9516756B2 (en) * | 2014-12-25 | 2016-12-06 | Ezek Lab Company Limited | Circuit module system |

| US20160197417A1 (en) * | 2015-01-02 | 2016-07-07 | Voxel8, Inc. | Electrical communication with 3d-printed objects |

| US10406801B2 (en) | 2015-08-21 | 2019-09-10 | Voxel8, Inc. | Calibration and alignment of 3D printing deposition heads |

| US20180315911A1 (en) * | 2015-10-23 | 2018-11-01 | Heptagon Micro Optics Pte. Ltd. | Electrical-Contact Assemblies |

| WO2017160282A1 (en) | 2016-03-15 | 2017-09-21 | Intel Corporation | Parasitic-aware integrated substrate balanced filter and apparatus to achieve transmission zeros |

| DE112016006610T5 (de) * | 2016-03-15 | 2018-12-13 | Intel Corporation | Integriertes Substratkommunikations-Frontend |

| US20170283247A1 (en) * | 2016-04-04 | 2017-10-05 | Infineon Technologies Ag | Semiconductor device including a mems die |

| US20170325327A1 (en) * | 2016-04-07 | 2017-11-09 | Massachusetts Institute Of Technology | Printed circuit board for high power components |

| US11355427B2 (en) * | 2016-07-01 | 2022-06-07 | Intel Corporation | Device, method and system for providing recessed interconnect structures of a substrate |

| TWI612861B (zh) * | 2016-09-02 | 2018-01-21 | 先豐通訊股份有限公司 | 晶片埋入式電路板結構及其製造方法 |

| CN108962846B (zh) * | 2018-07-27 | 2020-10-16 | 北京新雷能科技股份有限公司 | 一种厚膜混合集成电路的封装结构及其制作方法 |

| CN110943050B (zh) * | 2018-09-21 | 2023-08-15 | 中兴通讯股份有限公司 | 一种封装结构及堆叠式封装结构 |

| US11540395B2 (en) * | 2018-10-17 | 2022-12-27 | Intel Corporation | Stacked-component placement in multiple-damascene printed wiring boards for semiconductor package substrates |

| CN109887886A (zh) * | 2019-04-10 | 2019-06-14 | 中国电子科技集团公司第十三研究所 | 信号连接用三维垂直互联结构及方法 |

| US11587839B2 (en) | 2019-06-27 | 2023-02-21 | Analog Devices, Inc. | Device with chemical reaction chamber |

| CN111785691B (zh) * | 2020-05-13 | 2022-03-11 | 中国电子科技集团公司第五十五研究所 | 一种射频微系统三维封装外壳结构以及制作方法 |

| JP2023132708A (ja) * | 2022-03-11 | 2023-09-22 | キオクシア株式会社 | 配線基板および半導体装置 |

| CN115831880A (zh) * | 2023-02-13 | 2023-03-21 | 成都华兴大地科技有限公司 | 新型芯片集成封装结构 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02501873A (ja) * | 1987-01-05 | 1990-06-21 | アーヴィン・センサーズ・コーポレーション | 高密度電子パッケージ及びその製造方法 |

| JP2005079408A (ja) * | 2003-09-01 | 2005-03-24 | Olympus Corp | 小型高密度実装モジュール及びその製造方法 |

| JP2005353925A (ja) * | 2004-06-14 | 2005-12-22 | Idea System Kk | 多層配線基板および電子装置用基板 |

| JP2007201286A (ja) * | 2006-01-27 | 2007-08-09 | Kyocera Corp | 表面実装モジュールの製造方法および表面実装モジュール |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2792473B2 (ja) * | 1995-07-06 | 1998-09-03 | 日本電気株式会社 | マルチチップモジュール |

| KR100206893B1 (ko) * | 1996-03-11 | 1999-07-01 | 구본준 | 반도체 패키지 및 그 제조방법 |

| FR2756133B1 (fr) | 1996-11-21 | 1999-06-11 | Alsthom Cge Alcatel | Assemblage de modules electroniques multi-niveaux |

| FR2785450B1 (fr) * | 1998-10-30 | 2003-07-04 | Thomson Csf | Module de composants superposes dans un meme boitier |

| JP2002076252A (ja) * | 2000-08-31 | 2002-03-15 | Nec Kyushu Ltd | 半導体装置 |

| US7116557B1 (en) | 2003-05-23 | 2006-10-03 | Sti Electronics, Inc. | Imbedded component integrated circuit assembly and method of making same |

| US7339278B2 (en) | 2005-09-29 | 2008-03-04 | United Test And Assembly Center Ltd. | Cavity chip package |

| KR20070101579A (ko) | 2006-04-11 | 2007-10-17 | 엘지이노텍 주식회사 | 모듈 대 모듈 연결구조를 갖는 패키지 시스템 |

| US9337116B2 (en) | 2010-10-28 | 2016-05-10 | Stats Chippac, Ltd. | Semiconductor device and method of forming stepped interposer for stacking and electrically connecting semiconductor die |

-

2013

- 2013-05-09 JP JP2015512167A patent/JP2015516693A/ja active Pending

- 2013-05-09 EP EP13790666.5A patent/EP2850649A4/en not_active Withdrawn

- 2013-05-09 US US14/397,903 patent/US20150131248A1/en not_active Abandoned

- 2013-05-09 WO PCT/IB2013/053749 patent/WO2013171636A1/en active Application Filing

- 2013-05-09 CN CN201380024952.0A patent/CN104285278A/zh active Pending

- 2013-05-17 TW TW102117606A patent/TW201411800A/zh unknown

-

2014

- 2014-04-13 US US14/251,606 patent/US20140218883A1/en not_active Abandoned

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02501873A (ja) * | 1987-01-05 | 1990-06-21 | アーヴィン・センサーズ・コーポレーション | 高密度電子パッケージ及びその製造方法 |

| JP2005079408A (ja) * | 2003-09-01 | 2005-03-24 | Olympus Corp | 小型高密度実装モジュール及びその製造方法 |

| JP2005353925A (ja) * | 2004-06-14 | 2005-12-22 | Idea System Kk | 多層配線基板および電子装置用基板 |

| JP2007201286A (ja) * | 2006-01-27 | 2007-08-09 | Kyocera Corp | 表面実装モジュールの製造方法および表面実装モジュール |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019509631A (ja) * | 2016-02-24 | 2019-04-04 | マジック リープ, インコーポレイテッドMagic Leap,Inc. | 光エミッタのための薄型相互接続子 |

| JP6991981B2 (ja) | 2016-02-24 | 2022-01-13 | マジック リープ, インコーポレイテッド | 光エミッタのための薄型相互接続子 |

| US11264548B2 (en) | 2016-02-24 | 2022-03-01 | Magic Leap, Inc. | Low profile interconnect for light emitter |

| US11811011B2 (en) | 2016-02-24 | 2023-11-07 | Magic Leap, Inc. | Low profile interconnect for light emitter |

| WO2018123414A1 (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | インターポーザ基板、回路モジュール、インターポーザ基板の製造方法 |

| JPWO2018123414A1 (ja) * | 2016-12-28 | 2019-07-18 | 株式会社村田製作所 | インターポーザ基板、回路モジュール |

| US11032904B2 (en) | 2016-12-28 | 2021-06-08 | Murata Manufacturing Co., Ltd. | Interposer substrate and circuit module |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201411800A (zh) | 2014-03-16 |

| WO2013171636A1 (en) | 2013-11-21 |

| US20140218883A1 (en) | 2014-08-07 |

| CN104285278A (zh) | 2015-01-14 |

| WO2013171636A9 (en) | 2014-01-30 |

| EP2850649A4 (en) | 2015-12-23 |

| EP2850649A1 (en) | 2015-03-25 |

| US20150131248A1 (en) | 2015-05-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2015516693A (ja) | 電子集積のための3次元モジュール | |

| KR100821374B1 (ko) | 반도체 패키지 | |

| US10854575B2 (en) | Three-dimensional (3D) package structure having an epoxy molding compound layer between a discrete inductor and an encapsulating connecting structure | |

| EP2894950B1 (en) | Embedded heat slug to enhance substrate thermal conductivity | |

| US5943213A (en) | Three-dimensional electronic module | |

| JP2909704B2 (ja) | 誘電体テープから形成されたディスクリートなチップキャリアを有する垂直なicチップ積層体 | |

| US8064213B2 (en) | Module with a built-in component, and electronic device with the same | |

| JP5970564B2 (ja) | 三次元的な、複数の受動部品による構造 | |

| KR20180011481A (ko) | 임베딩된 트레이스 인터커넥트들을 갖는 라미네이팅된 인터포저들 및 패키지들 | |

| CN101587847B (zh) | 利用pcb基板进行垂直互连的多芯片组件封装方法 | |

| KR101145041B1 (ko) | 반도체칩 패키지, 반도체 모듈 및 그 제조 방법 | |

| US9324633B2 (en) | Multi-level package assembly having conductive vias coupled to chip carrier for each level and method for manufacturing the same | |

| US8791501B1 (en) | Integrated passive device structure and method | |

| US11257765B2 (en) | Chip package structure including connecting posts and chip package method | |

| CN113178440A (zh) | 一种陶瓷基双面rdl 3d封装方法及结构 | |

| CN100472780C (zh) | 电子零部件及其制造方法 | |

| US9155198B2 (en) | Electronic module allowing fine tuning after assembly | |

| JP2005244211A (ja) | 部品内蔵モジュールおよび部品内蔵モジュールを備えた電子機器 | |

| KR101394964B1 (ko) | 반도체 패키지 및 그 제조 방법 | |

| CN111312703A (zh) | 三维立体混合集成电路封装结构及装配方法 | |

| US8324727B2 (en) | Low profile discrete electronic components and applications of same | |

| CN115527975A (zh) | 一种芯片封装结构及芯片封装方法 | |

| EP2061289A1 (en) | Interconnection of embedded passive components and substrates | |

| KR100913722B1 (ko) | 멀티 칩 패키지 및 그 제조방법 | |

| WO2023070488A1 (zh) | 一种封装结构、封装方法以及功率放大器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160324 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160324 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161130 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170802 |