JP2010098235A - 不揮発性半導体記憶装置、及びその製造方法 - Google Patents

不揮発性半導体記憶装置、及びその製造方法 Download PDFInfo

- Publication number

- JP2010098235A JP2010098235A JP2008269804A JP2008269804A JP2010098235A JP 2010098235 A JP2010098235 A JP 2010098235A JP 2008269804 A JP2008269804 A JP 2008269804A JP 2008269804 A JP2008269804 A JP 2008269804A JP 2010098235 A JP2010098235 A JP 2010098235A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- memory device

- semiconductor memory

- protruding

- nonvolatile semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/10—EEPROM devices comprising charge-trapping gate insulators characterised by the top-view layout

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/20—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels

- H10B43/23—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels

- H10B43/27—EEPROM devices comprising charge-trapping gate insulators characterised by three-dimensional arrangements, e.g. with cells on different height levels with source and drain on different levels, e.g. with sloping channels the channels comprising vertical portions, e.g. U-shaped channels

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

【解決手段】不揮発性半導体記憶装置100は、メモリストリングスMS、ロウ方向に第1幅を有し且つ基板Baの上方に突出して形成された突出層50を備える。メモリストリングスMSは、基板Baに積層された第1〜第4ワード線導電層31a〜31dと、それらを貫通するように形成されたメモリ柱状半導体層36と、第1〜第4ワード線導電層31a〜31dとメモリ柱状半導体層36との間に形成された電荷蓄積層35bとを備える。第1〜第4ワード線導電層31a〜31dは、基板Baに対して平行に延びる第1〜第4底部311a〜311dと、それらの端部にて突出層50に沿って基板Baに対して上方に延びる第1〜第4側部312a〜312dとを備える。ロウ方向の突出層50の幅は、積層方向の突出層50の長さ以下である。

【選択図】図4

Description

(第1実施形態に係る不揮発性半導体記憶装置100の構成)

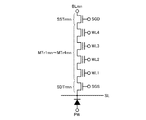

図1は、本発明の第1実施形態に係る不揮発性半導体記憶装置100の概略図を示す。図1に示すように、第1実施形態に係る不揮発性半導体記憶装置100は、主として、メモリトランジスタ領域(第1の領域)12、ワード線駆動回路13、ソース側選択ゲート線(SGS)駆動回路14、ドレイン側選択ゲート線(SGD)駆動回路15、センスアンプ16を有する。メモリトランジスタ領域12は、データを記憶するメモリトランジスタを有する。ワード線駆動回路13は、ワード線WLにかける電圧を制御する。ソース側選択ゲート線(SGS)駆動回路14は、ソース側選択ゲート線SGSにかける電圧を制御する。ドレイン側選択ゲート線(SGD)駆動回路15は、ドレイン側選択ゲート線(SGD)にかける電圧を制御する。センスアンプ16は、メモリトランジスタから読み出した電位を増幅する。なお、上記の他、第1実施形態に係る不揮発性半導体記憶装置100は、ビット線BLにかける電圧を制御するビット線駆動回路、ソース線SLにかける電圧を制御するソース線駆動回路を有する(図示略)。

次に、図4を参照して、第1実施形態に係る不揮発性半導体記憶装置100の更に具体的構成を説明する。図4は、第1実施形態に係る不揮発性半導体記憶装置のロウ方向の断面図である。

次に、図8〜図14を参照して、第1実施形態に係る不揮発性半導体記憶装置100の製造工程について説明する。ここで、図8、図9A、図10、図11A、図13〜図15は、第1実施形態に係る不揮発性半導体記憶装置100の製造工程を示すロウ方向断面図である。図9B、図11B、及び図12は、第1実施形態に係る不揮発性半導体記憶装置100の製造工程を示す上面図である。なお、図9Bは、図9Aに対応する上面図であり、図11Bは、図11Aに対応する上面図である。

次に、第1実施形態に係る不揮発性半導体記憶装置100の効果について説明する。上記のように第1実施形態に係る不揮発性半導体記憶装置100において、第1〜第4ワード線導電層31a〜31dは、半導体基板Baに対して平行に延びる第1〜第4底部311a〜311dと、その第1〜第4底部311a〜311dのロウ方向の端部にて突出層30に沿って半導体基板Baに対して直交方向上方に延びる第1〜第4側部312a〜312dとを備える。第1〜第4側部312a〜312dの上面は、同一平面内に揃えて形成されている。第1〜第4側部312a〜312dは、ロウ方向に第1〜第4ワード線間絶縁層32a〜32dを設けて形成されている。よって、コンタクト層72は、同一平面の第1〜第4側部312a〜312dの上面に接するように形成すれば良いので、コンタクト層72の径は、所定の径よりも大きくする必要はない。コンタクト層72は、第1〜第4ワード線間絶縁層32a〜32dの間隔をもって形成される。したがって、第1実施形態に係る不揮発性半導体記憶装置100は、ワード線導電層の端部を階段状に形成する従来例よりも、その占有面積を縮小化することができる。

(第2実施形態に係る不揮発性半導体記憶装置100aの具体的構成)

次に、図16を参照して、第2実施形態に係る不揮発性半導体記憶装置100aの具体的構成を説明する。図16は、第2実施形態に係る不揮発性半導体記憶装置100aのロウ方向の断面図である。なお、第2実施形態において、第1実施形態と同様の構成については、同一符号を付し、その説明を省略する。

次に、第2実施形態に係る不揮発性半導体記憶装置100aの効果について説明する。第2実施形態に係る不揮発性半導体記憶装置100aは、第1実施形態と略同様の構成を有する。したがって、第2実施形態に係る不揮発性半導体記憶装置100aは、第1実施形態と同様の効果を奏する。

(第3実施形態に係る不揮発性半導体記憶装置100bの具体的構成)

次に、図17A〜図17Dを参照して、第3実施形態に係る不揮発性半導体記憶装置100bの具体的構成を説明する。図17Aは、第3実施形態に係る不揮発性半導体記憶装置100bのメモリトランジスタ層30Bの概略上面図である。図17Bは、図17AのA部拡大図である。図17Cは、メモリトランジスタ層30B、コンタクト層72a、及び配線層76aを示す上面概略図である。図17Dは、各第1〜第4ワード線導電層31ab〜31dbを示す上面概略図である。なお、第3実施形態において、第1及び第2実施形態と同様の構成については、同一符号を付し、その説明を省略する。

次に、図18〜図20を参照して、第3実施形態に係る不揮発性半導体記憶装置100bの製造工程について説明する。ここで、図18〜図20は、第3実施形態に係る不揮発性半導体記憶装置100bの製造工程を示す上面図である。

次に、第3実施形態に係る不揮発性半導体記憶装置100bの効果について説明する。第3実施形態に係る不揮発性半導体記憶装置100bは、第1実施形態と略同様の構成を有する。したがって、第3実施形態に係る不揮発性半導体記憶装置100bは、第1実施形態と同様の効果を奏する。

(第4実施形態に係る不揮発性半導体記憶装置100cの具体的構成)

次に、図21を参照して、第4実施形態に係る不揮発性半導体記憶装置100cの具体的構成を説明する。図21は、第3実施形態における不揮発性半導体記憶装置100bのロウ方向断面図である。なお、第4実施形態において、第1〜第3実施形態と同様の構成については、同一符号を付し、その説明を省略する。

次に、図22〜図24を参照して、第4実施形態に係る不揮発性半導体記憶装置100cの製造工程について説明する。

次に、第4実施形態に係る不揮発性半導体記憶装置100cの効果について説明する。第4実施形態に係る不揮発性半導体記憶装置100cは、第1実施形態と略同様の構成を有する。したがって、第4実施形態に係る不揮発性半導体記憶装置100cは、第1実施形態と同様の効果を奏する。

(第5実施形態に係る不揮発性半導体記憶装置100dの具体的構成)

次に、図25及び図26を参照して、第5実施形態に係る不揮発性半導体記憶装置100dの具体的構成を説明する。図25は、第5実施形態に係る不揮発性半導体記憶装置100dの

ロウ方向断面図である。図26は、図25のB部拡大図である。なお、第5実施形態において、第1〜第4実施形態と同様の構成については、同一符号を付し、その説明を省略する。

次に、図27〜図29を参照して、第5実施形態に係る不揮発性半導体記憶装置100dの製造工程について説明する。図27〜図29は、第5実施形態に係る不揮発性半導体記憶装置100dの製造工程を示すロウ方向断面図である。

次に、第5実施形態に係る不揮発性半導体記憶装置100dの効果を説明する。第5実施形態に係る不揮発性半導体記憶装置100dは、第1実施形態と同様の構成を有する。したがって、第5実施形態に係る不揮発性半導体記憶装置100dは、第1実施形態と同様の効果を奏する。

以上、不揮発性半導体記憶装置の実施形態を説明してきたが、本発明は、上記実施形態に限定されるものではなく、発明の趣旨を逸脱しない範囲内において種々の変更、追加、置換等が可能である。

Claims (5)

- 電気的に書き換え可能であり且つ直列接続された複数のメモリセルを含むメモリストリングスを備える不揮発性半導体記憶装置であって、

基板に対して上方に突出して形成された突出層を備え、

前記メモリストリングスは、

前記基板上に積層された複数の導電層と、

当該複数の導電層を貫通するように形成された半導体層と、

前記導電層と前記半導体層との間に形成され且つ電荷を蓄積可能に構成された電荷蓄積層とを備え、

前記複数の導電層は、

前記基板に対して平行に延びる底部と、

当該底部の端部にて前記突出層に沿って前記基板に対して上方に延びる側部とを備え、

前記基板に平行な第1方向の前記突出層の幅は、積層方向の前記突出層の長さ以下である

ことを特徴とする不揮発性半導体記憶装置。 - 前記突出層は、台形状に形成され、

前記側部は、前記突出層に沿って前記基板に対して所定の角度をもって傾斜して上方に延びるように形成されている

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。 - 前記複数の導電層は、前記突出層を取り囲むように形成されている

ことを特徴とする請求項1又は請求項2記載の不揮発性半導体記憶装置。 - 前記突出層は、階段状に、且つ当該突出層の前記第1方向の幅が下層から上層へと大きくなるように形成されている

ことを特徴とする請求項1乃至請求項3のいずれか1項記載の不揮発性半導体記憶装置。 - 電気的に書き換え可能であり且つ直列接続された複数のメモリセルを含むメモリストリングスを有する不揮発性半導体記憶装置の製造方法であって、

基板に平行な第1方向の幅が積層方向の長さ以下であり且つ前記基板に対して上方に突出する突出層を形成する工程と、

前記基板上に前記突出層を覆うように複数の導電層を積層する工程と、

積層した複数の前記導電層を前記突出層の上面まで平坦化する工程と

を備えることを特徴とする不揮発性半導体記憶装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269804A JP5388537B2 (ja) | 2008-10-20 | 2008-10-20 | 不揮発性半導体記憶装置、及びその製造方法 |

| US12/556,242 US8237211B2 (en) | 2008-10-20 | 2009-09-09 | Non-volatile semiconductor storage device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269804A JP5388537B2 (ja) | 2008-10-20 | 2008-10-20 | 不揮発性半導体記憶装置、及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010098235A true JP2010098235A (ja) | 2010-04-30 |

| JP5388537B2 JP5388537B2 (ja) | 2014-01-15 |

Family

ID=42107961

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008269804A Expired - Fee Related JP5388537B2 (ja) | 2008-10-20 | 2008-10-20 | 不揮発性半導体記憶装置、及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8237211B2 (ja) |

| JP (1) | JP5388537B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8633104B2 (en) | 2011-07-11 | 2014-01-21 | Samsung Electronics Co., Ltd. | Methods of manufacturing three-dimensional semiconductor devices |

| US8884356B2 (en) | 2012-09-05 | 2014-11-11 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method for manufacturing same |

| US9953993B2 (en) | 2016-07-25 | 2018-04-24 | Toshiba Memory Corporation | Semiconductor memory device |

| US10115627B2 (en) | 2016-08-31 | 2018-10-30 | Toshiba Memory Corporation | Semiconductor device |

| US10262936B2 (en) | 2017-02-08 | 2019-04-16 | Toshiba Memory Corporation | Semiconductor device and manufacturing method thereof |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5016832B2 (ja) * | 2006-03-27 | 2012-09-05 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| JP5388537B2 (ja) * | 2008-10-20 | 2014-01-15 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| JP4922370B2 (ja) * | 2009-09-07 | 2012-04-25 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| JP5297342B2 (ja) * | 2009-11-02 | 2013-09-25 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP5259552B2 (ja) | 2009-11-02 | 2013-08-07 | 株式会社東芝 | 不揮発性半導体記憶装置及びその駆動方法 |

| KR101559958B1 (ko) * | 2009-12-18 | 2015-10-13 | 삼성전자주식회사 | 3차원 반도체 장치의 제조 방법 및 이에 따라 제조된 3차원 반도체 장치 |

| JP5670704B2 (ja) | 2010-11-10 | 2015-02-18 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| JP2012204430A (ja) * | 2011-03-24 | 2012-10-22 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP5411193B2 (ja) * | 2011-03-25 | 2014-02-12 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

| KR101808822B1 (ko) | 2011-08-04 | 2017-12-14 | 삼성전자주식회사 | 반도체 소자 및 그 제조방법 |

| JP2013055142A (ja) * | 2011-09-01 | 2013-03-21 | Toshiba Corp | 不揮発性半導体記憶装置 |

| KR101865566B1 (ko) * | 2011-09-08 | 2018-06-11 | 삼성전자주식회사 | 수직형 메모리 장치의 제조 방법 |

| KR102024723B1 (ko) | 2013-01-02 | 2019-09-24 | 삼성전자주식회사 | 3차원 반도체 장치 |

| US8981567B2 (en) | 2013-03-13 | 2015-03-17 | Macronix International Co., Ltd. | 3-D IC device with enhanced contact area |

| KR102083483B1 (ko) * | 2013-08-12 | 2020-03-02 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 제조 방법 |

| KR20150021742A (ko) * | 2013-08-21 | 2015-03-03 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그 제조 방법 |

| JP2016035991A (ja) | 2014-08-04 | 2016-03-17 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| US9608001B2 (en) | 2015-03-13 | 2017-03-28 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US9698150B2 (en) | 2015-10-26 | 2017-07-04 | Kabushiki Kaisha Toshiba | Semiconductor memory device and method for manufacturing the same |

| KR20170130009A (ko) | 2016-05-17 | 2017-11-28 | 삼성전자주식회사 | 3차원 반도체 장치 |

| KR102613511B1 (ko) | 2016-06-09 | 2023-12-13 | 삼성전자주식회사 | 수직형 메모리 소자를 구비한 집적회로 소자 및 그 제조 방법 |

| KR102650995B1 (ko) | 2016-11-03 | 2024-03-25 | 삼성전자주식회사 | 수직형 메모리 장치 |

| KR102635182B1 (ko) | 2018-07-12 | 2024-02-08 | 삼성전자주식회사 | 반도체 메모리 장치 |

| JP2021136270A (ja) * | 2020-02-25 | 2021-09-13 | キオクシア株式会社 | 半導体記憶装置およびその製造方法 |

| WO2024261305A1 (de) | 2023-06-23 | 2024-12-26 | Semron Gmbh | Anordnung von gestapelten kapazitiven speicherbauelementen, insbesondere zur gewichteten multiplikation in künstlichen neuronalen netzen |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326952A (ja) * | 1992-05-21 | 1993-12-10 | Toshiba Corp | 半導体装置およびその製造方法 |

| JPH08330586A (ja) * | 1995-05-26 | 1996-12-13 | Samsung Electron Co Ltd | バーチカルトランジスタ及びその製造方法 |

| JP2007266143A (ja) * | 2006-03-27 | 2007-10-11 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008103429A (ja) * | 2006-10-17 | 2008-05-01 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008192857A (ja) * | 2007-02-05 | 2008-08-21 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008244485A (ja) * | 2007-03-27 | 2008-10-09 | Samsung Electronics Co Ltd | 不揮発性メモリ素子及びその製造方法 |

| US20080253183A1 (en) * | 2007-04-11 | 2008-10-16 | Makoto Mizukami | Semiconductor memory device |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US96682A (en) * | 1869-11-09 | Improvement in hose-pipes | ||

| JP3403231B2 (ja) * | 1993-05-12 | 2003-05-06 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| US5990509A (en) * | 1997-01-22 | 1999-11-23 | International Business Machines Corporation | 2F-square memory cell for gigabit memory applications |

| US6897116B2 (en) * | 2003-09-12 | 2005-05-24 | United Microelectronics Corp. | Method and structure to improve the gate coupling ratio (GCR) for manufacturing a flash memory device |

| US20050199937A1 (en) * | 2004-03-11 | 2005-09-15 | Chang Augustine W. | 3D flash EEPROM cell and methods of implementing the same |

| US7271063B2 (en) * | 2005-10-13 | 2007-09-18 | Elite Semiconductor Memory Technology, Inc. | Method of forming FLASH cell array having reduced word line pitch |

| JP4817984B2 (ja) * | 2006-06-20 | 2011-11-16 | 株式会社東芝 | 不揮発性半導体記憶装置及びその製造方法 |

| KR20080010900A (ko) * | 2006-07-28 | 2008-01-31 | 삼성전자주식회사 | 비휘발성 메모리 소자, 그 동작 방법 및 그 제조 방법 |

| US7821045B2 (en) * | 2006-12-28 | 2010-10-26 | Intel Corporation | Apparatus, system, and method for multiple-segment floating gate |

| JP2008172164A (ja) * | 2007-01-15 | 2008-07-24 | Toshiba Corp | 半導体装置 |

| US7795080B2 (en) * | 2007-01-15 | 2010-09-14 | Sandisk Corporation | Methods of forming integrated circuit devices using composite spacer structures |

| KR101283539B1 (ko) * | 2007-08-29 | 2013-07-15 | 삼성전자주식회사 | 역전 구조의 비휘발성 메모리 소자, 그 스택 모듈 및 그제조 방법 |

| JP5142692B2 (ja) | 2007-12-11 | 2013-02-13 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7910973B2 (en) * | 2008-03-17 | 2011-03-22 | Kabushiki Kaisha Toshiba | Semiconductor storage device |

| US7915664B2 (en) * | 2008-04-17 | 2011-03-29 | Sandisk Corporation | Non-volatile memory with sidewall channels and raised source/drain regions |

| JP5112201B2 (ja) * | 2008-07-11 | 2013-01-09 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP5388537B2 (ja) * | 2008-10-20 | 2014-01-15 | 株式会社東芝 | 不揮発性半導体記憶装置、及びその製造方法 |

| JP5388600B2 (ja) * | 2009-01-22 | 2014-01-15 | 株式会社東芝 | 不揮発性半導体記憶装置の製造方法 |

-

2008

- 2008-10-20 JP JP2008269804A patent/JP5388537B2/ja not_active Expired - Fee Related

-

2009

- 2009-09-09 US US12/556,242 patent/US8237211B2/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326952A (ja) * | 1992-05-21 | 1993-12-10 | Toshiba Corp | 半導体装置およびその製造方法 |

| JPH08330586A (ja) * | 1995-05-26 | 1996-12-13 | Samsung Electron Co Ltd | バーチカルトランジスタ及びその製造方法 |

| JP2007266143A (ja) * | 2006-03-27 | 2007-10-11 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008103429A (ja) * | 2006-10-17 | 2008-05-01 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008192857A (ja) * | 2007-02-05 | 2008-08-21 | Toshiba Corp | 不揮発性半導体記憶装置及びその製造方法 |

| JP2008244485A (ja) * | 2007-03-27 | 2008-10-09 | Samsung Electronics Co Ltd | 不揮発性メモリ素子及びその製造方法 |

| US20080253183A1 (en) * | 2007-04-11 | 2008-10-16 | Makoto Mizukami | Semiconductor memory device |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8633104B2 (en) | 2011-07-11 | 2014-01-21 | Samsung Electronics Co., Ltd. | Methods of manufacturing three-dimensional semiconductor devices |

| US8884356B2 (en) | 2012-09-05 | 2014-11-11 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method for manufacturing same |

| US9953993B2 (en) | 2016-07-25 | 2018-04-24 | Toshiba Memory Corporation | Semiconductor memory device |

| US10115627B2 (en) | 2016-08-31 | 2018-10-30 | Toshiba Memory Corporation | Semiconductor device |

| US11004731B2 (en) | 2016-08-31 | 2021-05-11 | Kioxia Corporation | Semiconductor device |

| US11848228B2 (en) | 2016-08-31 | 2023-12-19 | Kioxia Corporation | Semiconductor device |

| US12347723B2 (en) | 2016-08-31 | 2025-07-01 | Kioxia Corporation | Semiconductor device |

| US10262936B2 (en) | 2017-02-08 | 2019-04-16 | Toshiba Memory Corporation | Semiconductor device and manufacturing method thereof |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100096682A1 (en) | 2010-04-22 |

| US8237211B2 (en) | 2012-08-07 |

| JP5388537B2 (ja) | 2014-01-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5388537B2 (ja) | 不揮発性半導体記憶装置、及びその製造方法 | |

| JP5253875B2 (ja) | 不揮発性半導体記憶装置、及びその製造方法 | |

| JP5142692B2 (ja) | 不揮発性半導体記憶装置 | |

| US11355194B2 (en) | Non-volatile memory device | |

| JP5193551B2 (ja) | 不揮発性半導体記憶装置、及びその製造方法 | |

| JP5148242B2 (ja) | 不揮発性半導体記憶装置、及びその製造方法 | |

| JP4455615B2 (ja) | 不揮発性半導体記憶装置及びその製造方法 | |

| JP5317664B2 (ja) | 不揮発性半導体記憶装置の製造方法 | |

| JP4468433B2 (ja) | 不揮発性半導体記憶装置 | |

| TWI449133B (zh) | 非揮發性半導體記憶裝置及其製造方法 | |

| US7910432B2 (en) | Non-volatile semiconductor storage device and method of manufacturing the same | |

| JP5364336B2 (ja) | 半導体記憶装置 | |

| CN110416220B (zh) | 半导体存储装置 | |

| JP2009212280A (ja) | 不揮発性半導体記憶装置の製造方法 | |

| JP2009164433A (ja) | 不揮発性半導体記憶装置 | |

| JP2009200443A (ja) | 不揮発性半導体記憶装置、及びその製造方法 | |

| KR20110093309A (ko) | 3차원 구조의 비휘발성 메모리 소자 및 그 제조 방법 | |

| JP2009224468A (ja) | 不揮発性半導体記憶装置 | |

| JP2009224574A (ja) | 不揮発性半導体記憶装置及びその製造方法 | |

| JP2010212518A (ja) | 不揮発性半導体記憶装置 | |

| CN103187421B (zh) | 非易失性存储器件及其操作方法和制造方法 | |

| US20130248975A1 (en) | Non-volatile semiconductor memory device and its manufacturing method | |

| TWI691050B (zh) | 半導體記憶裝置 | |

| TWI777089B (zh) | 半導體記憶裝置 | |

| JP2021034720A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110309 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20130221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130910 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131008 |

|

| LAPS | Cancellation because of no payment of annual fees |