JP2008066567A - 配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 - Google Patents

配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 Download PDFInfo

- Publication number

- JP2008066567A JP2008066567A JP2006243988A JP2006243988A JP2008066567A JP 2008066567 A JP2008066567 A JP 2008066567A JP 2006243988 A JP2006243988 A JP 2006243988A JP 2006243988 A JP2006243988 A JP 2006243988A JP 2008066567 A JP2008066567 A JP 2008066567A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- pattern

- wiring pattern

- wiring

- conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/12—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using thick film techniques, e.g. printing techniques to apply the conductive material or similar techniques for applying conductive paste or ink patterns

- H05K3/1208—Pretreatment of the circuit board, e.g. modifying wetting properties; Patterning by using affinity patterns

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/464—Lateral top-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/466—Lateral bottom-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/10—Deposition of organic active material

- H10K71/12—Deposition of organic active material using liquid deposition, e.g. spin coating

- H10K71/13—Deposition of organic active material using liquid deposition, e.g. spin coating using printing techniques, e.g. ink-jet printing or screen printing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/60—Forming conductive regions or layers, e.g. electrodes

- H10K71/611—Forming conductive regions or layers, e.g. electrodes using printing deposition, e.g. ink jet printing

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09272—Layout details of angles or corners

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1173—Differences in wettability, e.g. hydrophilic or hydrophobic areas

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/12—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using thick film techniques, e.g. printing techniques to apply the conductive material or similar techniques for applying conductive paste or ink patterns

- H05K3/1241—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using thick film techniques, e.g. printing techniques to apply the conductive material or similar techniques for applying conductive paste or ink patterns by ink-jet printing or drawing by dispensing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/20—Changing the shape of the active layer in the devices, e.g. patterning

- H10K71/231—Changing the shape of the active layer in the devices, e.g. patterning by etching of existing layers

- H10K71/233—Changing the shape of the active layer in the devices, e.g. patterning by etching of existing layers by photolithographic etching

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

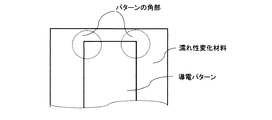

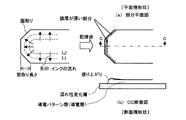

【解決手段】濡れ性変化層2に、エネルギーを付与して高表面エネルギー部3とし、その上に導電性液体により導電パターン5を形成して配線パターン1とする。その際、導電パターンの平面視形状は角部に面取りが施された矩形の配線形状とし、その断面視形状は該角部の盛り上がりが少なく、パターン中央部となだらかに連なり全体が略平坦な形状とする。配線パターン1を用いて積層配線パターン、積層配線基板を構成する。又は濡れ性変化層2の低表面エネルギー部に接して半導体層を設け、電子素子、有機半導体素子を構成する。

【選択図】図6

Description

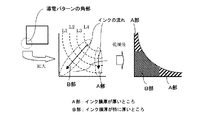

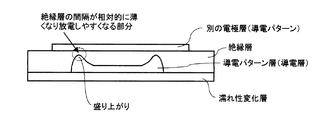

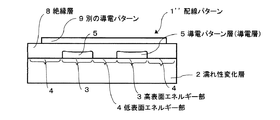

そして、濡れ性変化層の高表面エネルギー部上に導電パターン層が形成されてなる構成体、いわゆる配線パターン上に絶縁膜を成膜し、その上にさらに電極層(別の導電パターン層)を形成して積層配線基板とした場合、導電パターン層の膜厚に大きな盛り上がりがあると、その盛り上がり部分で電極間の絶縁膜厚さが相対的に薄くなって電界が集中しやすくなる。そのため、絶縁膜の絶縁破壊が生じやすくなり、積層配線基板として機能しなくなるといった問題点がある。図5に、膜厚の盛り上がり部において電極間の電界が集中しやすくなる様子を説明するための断面模式図を示す。

前記導電パターン層の平面視形状は角部に面取りが施された矩形の配線からなる形状であることを特徴とする配線パターンである。

また、上記角部に面取りが施された導電パターンの形成には、印刷法のような低コストで、材料使用効率の高い方法が適用でき、高表面エネルギー部全域にインクが濡れ広がりながらも低表面エネルギー部にインクが付与されることがなく形成されるため、微細で高精度の配線パターンが提供される。この配線パターンを用いることにより、各種の電子素子、有機半導体素子、積層配線パターンあるいは積層配線基板などが構成できる。

請求項

前記導電パターン層の平面視形状は角部に面取りが施された矩形の配線からなる形状であることを特徴とする有機半導体素子である。

さらに、上記構成に絶縁層を介して別の導電パターンを設ければ、積層配線パターン、積層配線基板、あるいは各種電子素子(ダイオード、トランジスタ、光電変換素子、熱電変換素子等)の構成要素として好適に利用することができる配線パターンとすることが可能である。

半導体層として有機半導体層を設ければ、半導体特性向上がより顕著に現れて移動度が高く、しかも省資源、低コスト、かつ歩留まり良く有機半導体素子とすることができる。有機半導体素子を薄膜トランジスタ構成とすれば、積層部分においても絶縁不良等のない動作特性の優れたTFT素子が提供される。

上記配線パターンを複数積層した構成とすれば、耐電圧特性等の絶縁特性に優れた多層配線構造の積層配線パターンが提供され、上記各種の電子素子や表示装置等に適用することができる。あるいは、配線パターンを基板上に設けた構成とすれば、各種電子素子や表示装置等の配線基板として好適に利用することができる。

前記導電パターン層の平面視形状は角部に面取りが施された矩形の配線からなる形状であることを特徴とするものである。

すなわち、本発明における導電パターン層は、インクを高表面エネルギー部に濡れ広がらせて角部に面取りが施された矩形の配線(平面視形状)を形成するものであり、該面取り形状と、高表面エネルギー部表面との相互関係を好適に保ち、その断面視形状において、角部に大きな凸状の膜厚ピーク、いわゆる「盛り上がり」を形成させず、この盛り上がりとパターン中央部が丘陵状になだらかに連なり、パターン全体が3次元的に起伏の少ない形状とするものである。パターン断面形状全体が略平坦な形状に近いものが好ましい。

[配線パターン]

図6は、配線パターンの原理的構成例を示す部分平面図(a)および(a)におけるAA断面を示す断面図である。図6において、配線パターン1は、濡れ性変化層2の高表面エネルギー部3上に導電性液体により形成された導電パターン層(導電層)5を有する構成体からなる。

すなわち、濡れ性変化層2には、エネルギーを付与されたより臨界表面張力の大きな高表面エネルギー部3と、エネルギーを付与されない臨界表面張力の小さな低表面エネルギー部4とを有しており、高表面エネルギー部3上に導電パターン層5が設けられている。各高表面エネルギー部3の距離は、例えば、1〜5μm程度の微小ギャップに設定されている。また、濡れ性変化層2は、エネルギーの付与によって臨界表面張力、いわゆる表面エネルギーが変化する材料によって形成される。

なお、インクを乾燥、あるいは必要により焼成して成膜することにより、導電性パターン層が形成される。

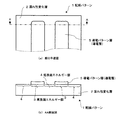

図11に、濡れ性変化層の高表面エネルギー部上に導電性液体により形成された導電パターンを有する構成体(図6)上に絶縁層を介して別の導電パターンを設けた配線パターン1’’の断面模式図を示す。このような構成とすれば、積層配線パターンあるいは積層配線基板の構成要素として好適に適用できる。

なお、図示しないが図10の低表面エネルギー部に接するようにして半導体層を設け、この構成体に絶縁層を介して別の導電パターンを設けた配線パターンとすれば、例えば、ダイオード、トランジスタ、光電変換素子、熱電変換素子など各種の電子素子の構成要素として好適に適用できる。濡れ性変化層自身を絶縁層として別の導電パターンを設ければ、さらに低コストな電子素子の構成要素として好適に適用できる。

図6に示すように濡れ性変化層2は、エネルギーの付与によって臨界表面張力(表面エネルギー)が変化する材料により形成されるが、このような材料としては、単一の材料からなっていても良いし、2種類以上の材料から構成されていても良い。2種類以上の材料から構成する場合には、具体的には、電気絶縁性のより大きな材料と、濡れ性変化のより大きな材料を混合することにより、電気絶縁性に優れ、かつ、濡れ性変化にも優れた濡れ性変化層2を形成することが可能となる。

ここで、導電性材料を含有する導電性液体(インク)とは;

1:導電性材料を溶媒に溶解したもの、

2:導電性材料の前駆体若しくは前駆体を溶媒に溶解したもの、

3:導電性材料粒子を溶媒に分散したもの、

4:導電性材料の前駆体粒子を溶媒に分散したもの、

等を言う。

濡れ性変化層2は、熱、紫外線、電子線、プラズマ等のエネルギーを与えることによって、臨界表面張力が変化する材料からなる層で、エネルギー付与前後での臨界表面張力の変化量が大きいものが好ましい。このような材料の場合、濡れ性変化層2の一部分にエネルギーを付与し、高表面エネルギー部3と低表面エネルギー部4とからなる臨界表面張力の異なるパターンを形成することにより、導電性材料を含有する導電性液体(インク)が、高表面エネルギー部3には付着しやすく(親液性)、低表面エネルギー部4には付着しにくく(疎液性)なるため、パターン形状に従ってインクが親液性である高表面エネルギー部3に選択的に付着し、それを固化することにより導電層5が形成される。

式(1)中、γSは固体11の表面張力、γSLは固体11と液体(液滴12)の界面張力、γLは液体(液滴12)の表面張力である。

液滴法には;

(a):読取顕微鏡を液滴12に向け、顕微鏡内のカーソル線を液滴12の接点に合わせて角度を読取る接線法、

(b):十字のカーソルを液滴12の頂点に合わせ、一端を液滴12と固体11試料の接する点に合わせた時のカーソル線の角度を2倍することにより求めるθ/2法、

(c):モニター画面に液滴12を映し出し、円周上の1点(できれば頂点)と液滴12と固体11試料の接点(2点)をクリックしてコンピュータで処理する3点クリック法、

がある。(a)→(b)→(c)の順に精度が高くなる。

図19から紫外線未照射部の臨界表面張力γCは約24mN/m、紫外線照射部の臨界表面張力γCは約45mN/mであり、その差ΔγCは約21mN/mであることが判る。

図20中、Aは側鎖付ポリイミド、Bはポリビニルフェノール、Cは有機シリカ、Dは熱酸化膜、Eはポリイミド、FはSiO2(スパッタ膜)である。ただし、ソース電極5aとドレイン電極5bとはAu蒸着膜をリフトオフすることにより形成した。

ここで、臨界表面張力(γC)が20mN/mより小さいと、ほとんどの溶媒をはじいてしまう。このため、半導体層6を塗布によって形成する場合には、臨界表面張力(γC)は20mN/m以上であることが望ましい。

上記材料については特開平3−178478号公報等に詳しく記載されて周知であり、加熱状態で液体又は固体と接触させたときに親液性となり、空気中で加熱すると疎液性となる性質もある。このように、接触媒体の選択と熱エネルギーの付与によって臨界表面張力を変化させることもできる。

当然、上記一般式(I)〜(V)で示されないジアミン化合物から誘導される疎水性基を含むポリイミドを用いることもできる。

界面特性が良好であるとは;

(a):半導体が結晶質である場合には結晶粒が大きくなり、移動度が増大する、

(b):半導体が非晶質(高分子)である場合には、界面準位密度が減少し、移動度が増大する、

(c):半導体が高分子であり、長鎖アルキル基等の側鎖を有する場合には、その配向が規制されることによりπ共役主鎖の分子軸を概ね一方向に配列させることができ、移動度が増大する、

等の現象が出現することを指す。

まず、図22(a)に示すように、ガラスやポリカーボネート、ポリアリレート、ポリエーテルスルフォン等のプラスチック、シリコンウェハ、金属等からなる基板7上に濡れ性変化層2を形成する。濡れ性変化層2は、例えば、紫外線の照射によって臨界表面張力が増加し、低表面エネルギー(疎液性)状態から高表面エネルギー(親液性)状態へ変化する材料からなる。その好ましい構造については前述した通りであるが、本発明者らの実験によれば、主鎖がポリイミド骨格よりなり側鎖に長鎖アルキル基を有するものが、特に紫外線照射による濡れ性変化が大きかったものである。

上記プロセスにより、基板7上に、本発明の配線パターン1が作製される。

その上に半導体層6が蒸着法、スピンコート法、ディップコート法、キャスト法等により形成される。半導体層6としては、前述のように有機半導体が特に好ましい。

絶縁体層32としては、無機絶縁体及び有機絶縁体が使用可能であるが、半導体層6が有機半導体である場合には、特にその層にダメージを与えない形成方法を採用する必要がある。例えば、高温や高速イオン、活性ラジカル、有機半導体が可溶な溶媒等の使用を伴うものは避けるのが望ましい。そのような観点からは蒸着法によるSiO2、水に可溶なPVA(ポリビニルアルコール)、アルコールに可溶なPVP(ポリビニルフェノール)、フッ素系溶媒に可溶なパーフルオロポリマー等が好適に使用できる。

電極層33としては、各種の導電性薄膜が使用でき、全面に成膜した後に通常のフォトリソグラフィー法やマイクロコンタクトプリンティング法でパターニングしてもよいし、導電性材料を含有する液体をインクジェット法等で供給して直接描画してもよい。

図24に示す電子素子41では、ガラスやポリカーボネート、ポリアリレート、ポリエーテルスルフォン等のプラスチック、シリコンウェハ、金属等からなる基板7上に、まず、電極層42が蒸着法、CVD法、スピンコート法、ディップコート法、キャスト法等により形成される。電極層42としては、各種の導電性薄膜が使用でき、全面に成膜した後に通常のフォトリソグラフィー法やマイクロコンタクトプリンティング法でパターニングしてもよいし、導電性材料を含有する液体をインクジェット法等で供給して直接描画してもよい。

そして、最後に、前記と同様に半導体層6が形成される。図24では、全面に半導体層6が形成されているが、少なくともチャネル領域を含む島状に半導体層6が形成されていてもよい。

なお、図24において、電極層42を形成する前に基板7上に、濡れ性変化層2とは別の第2の濡れ性変化層(図示せず)を設け、電極層42のパターニングに利用してもよい。

ここで、導電パターン層における配線の角部に面取りが施された矩形が、それぞれ他の配線パターンと積層断面方向で重ならないように形成されれば、層間の絶縁特性がさらに向上して信頼性が向上するとともに、絶縁層の薄膜化が図れ、コンパクトな多層配線構造体とすることができる。

このような構成の積層配線基板は、配線パターン上に絶縁層を介して積層配線構造とした場合においても絶縁不良を回避することができるため、各種電子素子や表示装置等の配線基板として好適に利用することが可能である。

ガラス基板上に、焼成後に下記構造式(VI)及び下記構造式(VII)で表される構造体となる前駆体を溶解した混合溶液をスピンコート法により塗布し、280℃で焼成して成膜し濡れ性変化層(以下、濡れ性制御膜と表現することがある。)を設けた。

また、AFMで膜厚プロファイルを測定したところ、導電パターン中央部の膜厚が100nmであるのに対して導電パターン輪郭部の膜厚は200nmであった。すなわち、配線パターンの導電パターンの平面視形状は角部に面取りが施され、断面視形状は角部とパターン中央部がなだらかに連なった起伏の少ない形状を呈していた。

実施例1において、面取りなしの形状(線幅80μmの矩形状)のパターン(開口部)を施したマスクを介して紫外線を照射により濡れ性領域を形成した以外は、実施例1と同様にしてインクジェット法で銀ナノメタルインクを供給、乾燥、焼成を行って導電パターンを形成した。

実施例1と同様に、顕微鏡観察を実施した結果、導電パターンの角部の膜厚増大(盛り上がり)は大きく、盛り上がりに伴うヒケ(窪み)も発生していることが確認された。さらに、AFMで膜厚プロファイルを測定したところ、パターン中央部の膜厚が100nmであるのに対して、パターン角部の膜厚は700nmであった。すなわち、断面視形状は角部が突起状に隆起し、パターン中央部に対して起伏の大きい連なり形状を呈していた。

実施例1の構成とした導電パターン上(以下、一層目パターンと記す)にポリイミドをスピンコートし、これを焼成して絶縁膜を形成した後、さらに実施例1と同じ濡れ性制御膜を形成した。ポリイミド絶縁膜と濡れ性制御膜を合計した膜厚を500nmとした。形成される濡れ性パターンが一層目パターンと交差するようにマスクを配置して紫外線を照射し、二層目の濡れ性パターンを形成した。この二層目の濡れ性パターンに、インクジェット法で銀ナノメタルインクを付与、乾燥、焼成して二層目の導電パターンを形成した。

一層目の導電パターンと二層目の導電パターンの間に1MV/cmの電圧を印加したところ、絶縁破壊することなく良好な絶縁性が得られた。

比較例1の構成とした導電パターン上にポリイミドをスピンコート、焼成して絶縁膜を形成した後、さらに実施例1と同じ濡れ性制御膜を形成した。ポリイミド絶縁膜と濡れ性制御膜を合計した膜厚を500nmとした。形成される濡れ性パターンが一層目パターンと交差するようにマスクを配置して紫外線を照射し、二層目の濡れ性パターンを形成した。この二層目の濡れ性パターンに、インクジェット法で銀ナノメタルインクを付与、乾燥、焼成して二層目の導電パターンを形成した。

一層目の導電パターンと二層目の導電パターンの間に1MV/cmの電圧を印加したところ、絶縁破壊が起こった。

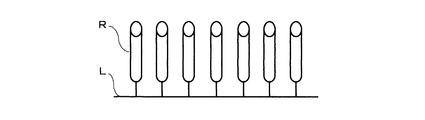

図25の平面模式図に示す電極構成(b)を有する薄膜トランジスタ(TFT)を次の条件で10素子作製した。

まず、図25(a)に示すような、パターン角部にR40μmのラウンドの面取りを施した線幅80μmの導電パターン(ゲートパターン)を、実施例1と同様の材料を用い、同様の方法で形成した。次に、実施例1と同様のポリイミドをスピンコートし、乾燥、焼成により成膜して濡れ性変化層(濡れ性制御層)を形成した。次に、マスクを介して紫外線を照射し、銀ナノメタルインクを付与、乾燥、焼成して、図25(b)に示すソースとドレインパターンを形成した。

最後に、下記化学式(VIII)に示すようなスキームにより合成した有機半導体である重合体1をトルエンに溶解した溶液をスピンコート法にて塗布し、乾燥させて半導体層を形成した。

実施例3において角部に面取りを施さないゲート電極形状でゲート電極を形成した以外は、実施例3と同様にしてTFTを10素子作製した。

作製したTFTについて実施例3と同様に動作を評価したところ、10素子全てのゲート電極とソース電極間、あるいはゲート電極とドレイン電極間でショートしており動作しなかった。

したがって、本発明の配線パターンを構成要素として用いれば、電子素子、有機半導体素子、積層配線パターン、積層配線基板を提供することが可能である。

2 濡れ性変化層

3 高表面エネルギー部

4 低表面エネルギー部

5 導電パターン層(導電層)

5a、5b 電極層

6 半導体層

7 基板

31 電子素子

32 絶縁体層

33 電極層

41 電子素子

42 電極層

Claims (14)

- エネルギーの付与により低表面エネルギー部から高表面エネルギー部に変化して液体に対する濡れ性が向上する濡れ性変化層と、該高表面エネルギー部上に導電性液体により形成された導電パターン層と、を有する配線パターンにおいて、

前記導電パターン層の平面視形状は角部に面取りが施された矩形の配線からなる形状であることを特徴とする配線パターン。 - 前記低表面エネルギー部に接して半導体層が設けられていることを特徴とする請求項1に記載の配線パターン。

- 前記半導体層が有機半導体層であることを特徴とする請求項2に記載の配線パターン。

- 前記配線パターンの一面上に、絶縁層を介して別の導電パターンが設けられていることを特徴とする請求項1〜3のいずれかに記載の配線パターン。

- 前記別の導電パターンが、濡れ性変化層の高表面エネルギー部上に導電性液体を用いて形成されたものであることを特徴とする請求項4に記載の配線パターン。

- 前記平面視形状における角部に施された面取りが、ラウンド形状であることを特徴とする請求項1〜5のいずれかに記載の配線パターン。

- 前記導電パターンが、濡れ性変化層の高表面エネルギー部上に導電性液体を用いてインクジエット法により形成されたものであることを特徴とする請求項1〜6のいずれかに記載の配線パターン。

- 請求項1〜7のいずれかに記載の配線パターンを構成要素として有することを特徴とする電子素子。

- エネルギーの付与により低表面エネルギー部から高表面エネルギー部に変化して液体に対する濡れ性が向上する濡れ性変化層と、該高表面エネルギー部上に導電性液体により形成された導電パターン層と、該低表面エネルギー部に接して設けられた有機半導体層と、を有する配線パターンの一面上に、濡れ性変化層を介するか、もしくは有機半導体層上に絶縁層を形成し、該絶縁層を介して別の導電パターンを設けてなる有機半導体素子であって、

前記導電パターン層の平面視形状は角部に面取りが施された矩形の配線からなる形状であることを特徴とする有機半導体素子。 - 前記平面視形状における角部に施された面取りが、ラウンド形状であることを特徴とする請求項9に記載の有機半導体素子。

- 前記有機半導体素子が、薄膜トランジスタ(TFT)であることを特徴とする請求項9または10に記載の有機半導体素子。

- 請求項1〜7のいずれかに記載の配線パターンが絶縁膜を介して複数積層したことを特徴とする積層配線パターン。

- 前記配線の角部に面取りが施された矩形が、それぞれ他の配線パターンと積層断面方向で重ならないように形成されていることを特徴とする請求項12に記載の積層配線パターン。

- 請求項1〜7のいずれかに記載の配線パターンが、基板上に形成されたことを特徴とする積層配線基板。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006243988A JP2008066567A (ja) | 2006-09-08 | 2006-09-08 | 配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 |

| EP07115110A EP1898478B1 (en) | 2006-09-08 | 2007-08-28 | Wiring pattern, electronic device, organic semiconductor device, layered wiring pattern, and layered wiring substrate using the wiring pattern |

| US11/846,092 US7816672B2 (en) | 2006-09-08 | 2007-08-28 | Wiring pattern, electronic device, organic semiconductor device, layered wiring pattern, and layered wiring substrate using the wiring pattern |

| DE602007011546T DE602007011546D1 (de) | 2006-09-08 | 2007-08-28 | Verdrahtungsmuster, elektronische Vorrichtung, organisches Halbleiterbauelement, geschichtetes Verdrahtungsmuster und geschichtetes Verdrahtungssubstrat mit dem Verdrahtungsmuster |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006243988A JP2008066567A (ja) | 2006-09-08 | 2006-09-08 | 配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008066567A true JP2008066567A (ja) | 2008-03-21 |

| JP2008066567A5 JP2008066567A5 (ja) | 2009-08-13 |

Family

ID=38844951

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006243988A Pending JP2008066567A (ja) | 2006-09-08 | 2006-09-08 | 配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7816672B2 (ja) |

| EP (1) | EP1898478B1 (ja) |

| JP (1) | JP2008066567A (ja) |

| DE (1) | DE602007011546D1 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8269216B2 (en) | 2010-02-19 | 2012-09-18 | Seiko Epson Corporation | Semiconductor device, method of manufacturing semiconductor device, and electronic apparatus |

| JP2014053587A (ja) * | 2012-08-09 | 2014-03-20 | Denso Corp | 有機半導体薄膜の製造方法、それを適用した有機半導体装置の製造方法および有機半導体装置 |

| US8779434B2 (en) | 2007-10-15 | 2014-07-15 | Ricoh Company, Ltd. | Thin film transistor array and displaying apparatus |

| KR101557102B1 (ko) | 2009-03-12 | 2015-10-13 | 삼성전자주식회사 | 반도체 소자의 금속 연결배선 |

| US9224763B2 (en) | 2011-03-28 | 2015-12-29 | Samsung Display Co., Ltd. | Display device and method of manufacturing the same |

| WO2016080263A1 (ja) * | 2014-11-21 | 2016-05-26 | デクセリアルズ株式会社 | 配線基板の製造方法、及び配線基板 |

| KR20170045287A (ko) | 2014-09-26 | 2017-04-26 | 후지필름 가부시키가이샤 | 도포 재료, 패턴 형성 방법 및 전자 디바이스의 그 제조 방법 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8309955B2 (en) * | 2008-01-07 | 2012-11-13 | The Johns Hopkins University | Devices having high dielectric constant, ionically-polarizable materials |

| JP5386852B2 (ja) * | 2008-05-07 | 2014-01-15 | 株式会社リコー | 積層構造体、半導体装置、積層構造体の製造方法及び半導体装置の製造方法 |

| JP4971241B2 (ja) * | 2008-05-09 | 2012-07-11 | 株式会社リコー | 画像表示装置 |

| WO2010011658A2 (en) * | 2008-07-21 | 2010-01-28 | The Johns Hopkins University | Pyromellitic diimide organic semiconductors and devices |

| GB0913456D0 (en) | 2009-08-03 | 2009-09-16 | Cambridge Entpr Ltd | Printed electronic device |

| JP5899606B2 (ja) * | 2010-03-04 | 2016-04-06 | 株式会社リコー | 積層構造体の製造方法 |

| JP6115008B2 (ja) | 2011-06-09 | 2017-04-19 | 株式会社リコー | 配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。 |

| US8679984B2 (en) * | 2011-06-30 | 2014-03-25 | Samsung Electronics Co., Ltd. | Method of manufacturing electric device, array of electric devices, and manufacturing method therefor |

| CN112268840B (zh) * | 2020-11-05 | 2023-02-03 | 国网山东省电力公司电力科学研究院 | 一种检验涂层抗润湿性的试验装置及方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004063359A (ja) * | 2002-07-31 | 2004-02-26 | Dainippon Printing Co Ltd | エレクトロルミネッセンス表示装置および製造方法 |

| JP2004089754A (ja) * | 2002-08-29 | 2004-03-25 | Canon Inc | 塗布膜形成方法及び塗布膜形成物 |

| JP2004295135A (ja) * | 2001-11-21 | 2004-10-21 | Seiko Epson Corp | アクティブマトリクス基板、電気光学装置および電子機器 |

| JP2005268761A (ja) * | 2004-02-17 | 2005-09-29 | Semiconductor Energy Lab Co Ltd | パターン形成方法、薄膜トランジスタ、表示装置及びそれらの作製方法、並びにテレビジョン装置 |

| JP2005310962A (ja) * | 2003-06-02 | 2005-11-04 | Ricoh Co Ltd | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 |

| JP2006060113A (ja) * | 2004-08-23 | 2006-03-02 | Ricoh Co Ltd | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 |

| JP2006114585A (ja) * | 2004-10-13 | 2006-04-27 | Seiko Epson Corp | 隔壁構造体、隔壁構造体の形成方法、デバイス、電気光学装置及び電子機器 |

| JP2006178208A (ja) * | 2004-12-22 | 2006-07-06 | Sharp Corp | 表示装置用基板及びその製造方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2796575B2 (ja) | 1989-03-31 | 1998-09-10 | 株式会社リコー | 記録方法 |

| JP3178478B2 (ja) | 1991-08-27 | 2001-06-18 | 三菱マテリアル株式会社 | 超電導線の製造方法 |

| JP3978754B2 (ja) | 1997-12-29 | 2007-09-19 | チッソ株式会社 | ポリアミド酸組成物、液晶配向膜、及び液晶表示素子 |

| JP3978755B2 (ja) | 1997-12-29 | 2007-09-19 | チッソ株式会社 | ポリアミド酸組成物、液晶配向膜、および液晶表示素子 |

| JP4029452B2 (ja) | 1997-12-29 | 2008-01-09 | チッソ株式会社 | ポリアミド酸組成物、液晶配向膜及び液晶表示素子 |

| US6734029B2 (en) | 2000-06-30 | 2004-05-11 | Seiko Epson Corporation | Method for forming conductive film pattern, and electro-optical device and electronic apparatus |

| JP2002162630A (ja) | 2000-11-29 | 2002-06-07 | Chisso Corp | ジアミン化合物およびこれを用いた高分子材料、該高分子材料を用いた液晶配向膜、および該配向膜を具備した液晶表示素子 |

| JP4728515B2 (ja) | 2001-03-21 | 2011-07-20 | 株式会社リコー | 光路素子、空間光変調器および画像表示装置 |

| JP4894120B2 (ja) | 2001-09-27 | 2012-03-14 | Jnc株式会社 | フェニレンジアミン誘導体、液晶配向膜および液晶表示素子 |

| JP4039035B2 (ja) | 2001-10-31 | 2008-01-30 | セイコーエプソン株式会社 | 線パターンの形成方法、線パターン、電気光学装置、電子機器、非接触型カード媒体 |

| JP4140252B2 (ja) | 2002-03-13 | 2008-08-27 | チッソ株式会社 | シロキサン部位を有するフェニレンジアミン、これを用いたポリマーを含む液晶配向材および該液晶配向材を含む液晶表示素子 |

| JP2004039897A (ja) * | 2002-07-04 | 2004-02-05 | Toshiba Corp | 電子デバイスの接続方法 |

| US7166689B2 (en) | 2003-02-13 | 2007-01-23 | Ricoh Company, Ltd. | Aryl amine polymer, thin film transistor using the aryl amine polymer, and method of manufacturing the thin film transistor |

| JP3966293B2 (ja) | 2003-03-11 | 2007-08-29 | セイコーエプソン株式会社 | パターンの形成方法及びデバイスの製造方法 |

| JP4742487B2 (ja) | 2003-05-09 | 2011-08-10 | セイコーエプソン株式会社 | 膜パターン形成方法 |

| JP2005079560A (ja) | 2003-09-04 | 2005-03-24 | Hitachi Ltd | 薄膜トランジスタ,表示装置、およびその製造方法 |

| KR101127889B1 (ko) | 2004-02-17 | 2012-03-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 박막 트랜지스터, 표시장치 및 그것들의 제조 방법 |

| JP4557755B2 (ja) * | 2004-03-11 | 2010-10-06 | キヤノン株式会社 | 基板、導電性基板および有機電界効果型トランジスタの各々の製造方法 |

| JP4877865B2 (ja) | 2004-03-26 | 2012-02-15 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法及び表示装置の作製方法 |

| WO2005117157A1 (ja) * | 2004-05-27 | 2005-12-08 | Sharp Kabushiki Kaisha | 両末端に脱離反応性の異なる異種官能基を有する有機化合物、有機薄膜、有機デバイスおよびそれらの製造方法 |

| EP1653294B1 (en) | 2004-11-02 | 2013-08-21 | Ricoh Company, Ltd. | Fixing solution, capsule, fixing method, fixing device and image forming apparatus |

| JP5209844B2 (ja) | 2004-11-30 | 2013-06-12 | 株式会社リコー | 電子素子及びその製造方法、演算素子並びに表示素子 |

| US7508078B2 (en) | 2005-01-06 | 2009-03-24 | Ricoh Company, Ltd. | Electronic device, method for manufacturing electronic device, contact hole of electronic device, method for forming contact hole of electronic device |

| US7858451B2 (en) * | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7566633B2 (en) * | 2005-02-25 | 2009-07-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP4994727B2 (ja) | 2005-09-08 | 2012-08-08 | 株式会社リコー | 有機トランジスタアクティブ基板とその製造方法および該有機トランジスタアクティブ基板を用いた電気泳動ディスプレイ |

-

2006

- 2006-09-08 JP JP2006243988A patent/JP2008066567A/ja active Pending

-

2007

- 2007-08-28 DE DE602007011546T patent/DE602007011546D1/de active Active

- 2007-08-28 EP EP07115110A patent/EP1898478B1/en not_active Not-in-force

- 2007-08-28 US US11/846,092 patent/US7816672B2/en not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004295135A (ja) * | 2001-11-21 | 2004-10-21 | Seiko Epson Corp | アクティブマトリクス基板、電気光学装置および電子機器 |

| JP2004063359A (ja) * | 2002-07-31 | 2004-02-26 | Dainippon Printing Co Ltd | エレクトロルミネッセンス表示装置および製造方法 |

| JP2004089754A (ja) * | 2002-08-29 | 2004-03-25 | Canon Inc | 塗布膜形成方法及び塗布膜形成物 |

| JP2005310962A (ja) * | 2003-06-02 | 2005-11-04 | Ricoh Co Ltd | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 |

| JP2005268761A (ja) * | 2004-02-17 | 2005-09-29 | Semiconductor Energy Lab Co Ltd | パターン形成方法、薄膜トランジスタ、表示装置及びそれらの作製方法、並びにテレビジョン装置 |

| JP2006060113A (ja) * | 2004-08-23 | 2006-03-02 | Ricoh Co Ltd | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 |

| JP2006114585A (ja) * | 2004-10-13 | 2006-04-27 | Seiko Epson Corp | 隔壁構造体、隔壁構造体の形成方法、デバイス、電気光学装置及び電子機器 |

| JP2006178208A (ja) * | 2004-12-22 | 2006-07-06 | Sharp Corp | 表示装置用基板及びその製造方法 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8779434B2 (en) | 2007-10-15 | 2014-07-15 | Ricoh Company, Ltd. | Thin film transistor array and displaying apparatus |

| KR101557102B1 (ko) | 2009-03-12 | 2015-10-13 | 삼성전자주식회사 | 반도체 소자의 금속 연결배선 |

| US8269216B2 (en) | 2010-02-19 | 2012-09-18 | Seiko Epson Corporation | Semiconductor device, method of manufacturing semiconductor device, and electronic apparatus |

| US9224763B2 (en) | 2011-03-28 | 2015-12-29 | Samsung Display Co., Ltd. | Display device and method of manufacturing the same |

| JP2014053587A (ja) * | 2012-08-09 | 2014-03-20 | Denso Corp | 有機半導体薄膜の製造方法、それを適用した有機半導体装置の製造方法および有機半導体装置 |

| KR20170045287A (ko) | 2014-09-26 | 2017-04-26 | 후지필름 가부시키가이샤 | 도포 재료, 패턴 형성 방법 및 전자 디바이스의 그 제조 방법 |

| WO2016080263A1 (ja) * | 2014-11-21 | 2016-05-26 | デクセリアルズ株式会社 | 配線基板の製造方法、及び配線基板 |

| JP2016100490A (ja) * | 2014-11-21 | 2016-05-30 | デクセリアルズ株式会社 | 配線基板の製造方法、及び配線基板 |

| US10136521B2 (en) | 2014-11-21 | 2018-11-20 | Dexerials Corporation | Wiring board and method for manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| US7816672B2 (en) | 2010-10-19 |

| DE602007011546D1 (de) | 2011-02-10 |

| EP1898478B1 (en) | 2010-12-29 |

| EP1898478A1 (en) | 2008-03-12 |

| US20080061288A1 (en) | 2008-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008066567A (ja) | 配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板 | |

| US8049211B2 (en) | Laminate structure and its manufacturing method, including wettability variable layer of material of variable critical surface tension | |

| US9153524B2 (en) | Method of forming stacked-layer wiring, stacked-layer wiring, and electronic element | |

| US8253137B2 (en) | Laminate structure, electronic device, and display device | |

| JP6115008B2 (ja) | 配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。 | |

| JP2007150246A (ja) | 有機トランジスタ及び表示装置 | |

| JP5168845B2 (ja) | 積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置 | |

| CN101595568B (zh) | 薄膜半导体装置的制作方法及薄膜半导体装置 | |

| JP4678574B2 (ja) | 積層構造体、積層構造体を用いた電子素子、電子素子アレイ及び表示装置 | |

| JP5868757B2 (ja) | 薄膜トランジスタとその製造方法及び表示装置 | |

| US8101945B2 (en) | Laminated structure, forming method of the same, wiring board, matrix substrate and electronic display apparatus | |

| JP2006060113A5 (ja) | ||

| JP5332145B2 (ja) | 積層構造体、電子素子、電子素子アレイ及び表示装置 | |

| JP2006021491A (ja) | 積層構造体、積層構造体を用いた光学素子、表示素子、演算素子及びこれらの製造方法 | |

| JP5449736B2 (ja) | ボトムゲート型有機薄膜トランジスタ及びその製造方法 | |

| JP2009026901A (ja) | 積層構造体、電子素子、電子素子アレイ及び表示装置 | |

| JP6259390B2 (ja) | 有機トランジスタの製造方法、有機トランジスタ | |

| JP5412765B2 (ja) | 積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置及び積層構造体の製造方法 | |

| JP5811522B2 (ja) | 薄膜トランジスタの製造方法 | |

| JP4691545B2 (ja) | 半導体装置の製造方法 | |

| JP2009026900A (ja) | 積層構造体、電子素子及びそれらの製造方法、表示装置 | |

| JP2006049803A (ja) | 電子素子の製造方法、コンタクトホールの形成方法、コンタクトホール、電子素子、表示素子、表示装置、半導体演算素子およびコンピュータ | |

| JP2011173429A (ja) | 積層構造体 | |

| JP2009290237A (ja) | 有機トランジスタの製造方法 | |

| JP2006114850A (ja) | 薄膜の形成方法および有機薄膜トランジスタの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090626 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090626 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120618 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121002 |