JP2004241755A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2004241755A JP2004241755A JP2003295234A JP2003295234A JP2004241755A JP 2004241755 A JP2004241755 A JP 2004241755A JP 2003295234 A JP2003295234 A JP 2003295234A JP 2003295234 A JP2003295234 A JP 2003295234A JP 2004241755 A JP2004241755 A JP 2004241755A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- region

- layer

- semiconductor

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 158

- 239000012535 impurity Substances 0.000 claims abstract description 113

- 238000002955 isolation Methods 0.000 claims abstract description 73

- 230000015572 biosynthetic process Effects 0.000 claims description 31

- 239000000758 substrate Substances 0.000 claims description 26

- 150000001875 compounds Chemical class 0.000 claims 3

- 229910052710 silicon Inorganic materials 0.000 abstract description 103

- 239000010703 silicon Substances 0.000 abstract description 103

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 101

- 238000004519 manufacturing process Methods 0.000 abstract description 85

- 230000009467 reduction Effects 0.000 abstract description 5

- 238000009413 insulation Methods 0.000 abstract 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 46

- 229920005591 polysilicon Polymers 0.000 description 46

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 40

- 229910052814 silicon oxide Inorganic materials 0.000 description 40

- 238000005468 ion implantation Methods 0.000 description 37

- 229920002120 photoresistant polymer Polymers 0.000 description 37

- 229910021332 silicide Inorganic materials 0.000 description 30

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 30

- 229910052581 Si3N4 Inorganic materials 0.000 description 28

- 238000005530 etching Methods 0.000 description 28

- 238000000034 method Methods 0.000 description 28

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 28

- 230000000694 effects Effects 0.000 description 26

- 239000010941 cobalt Substances 0.000 description 25

- 229910017052 cobalt Inorganic materials 0.000 description 25

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 25

- 238000002513 implantation Methods 0.000 description 17

- 238000000206 photolithography Methods 0.000 description 15

- 238000001312 dry etching Methods 0.000 description 12

- 230000007423 decrease Effects 0.000 description 10

- 230000003071 parasitic effect Effects 0.000 description 9

- 230000015556 catabolic process Effects 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 6

- 239000000463 material Substances 0.000 description 5

- 230000002411 adverse Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- -1 silicon ions Chemical class 0.000 description 4

- 230000007547 defect Effects 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- XKRFYHLGVUSROY-UHFFFAOYSA-N argon Substances [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66545—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using a dummy, i.e. replacement gate in a process wherein at least a part of the final gate is self aligned to the dummy gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28035—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities

- H01L21/28044—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities the conductor comprising at least another non-silicon conductive layer

- H01L21/28052—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being silicon, e.g. polysilicon, with or without impurities the conductor comprising at least another non-silicon conductive layer the conductor comprising a silicide layer formed by the silicidation reaction of silicon with a metal layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823807—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823814—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41766—Source or drain electrodes for field effect devices with at least part of the source or drain electrode having contact below the semiconductor surface, e.g. the source or drain electrode formed at least partially in a groove or with inclusions of conductor inside the semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4916—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a silicon layer, e.g. polysilicon doped with boron, phosphorus or nitrogen

- H01L29/4925—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a silicon layer, e.g. polysilicon doped with boron, phosphorus or nitrogen with a multiple layer structure, e.g. several silicon layers with different crystal structure or grain arrangement

- H01L29/4933—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET the conductor material next to the insulator being a silicon layer, e.g. polysilicon doped with boron, phosphorus or nitrogen with a multiple layer structure, e.g. several silicon layers with different crystal structure or grain arrangement with a silicide layer contacting the silicon layer, e.g. Polycide gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/665—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using self aligned silicidation, i.e. salicide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/6656—Unipolar field-effect transistors with an insulated gate, i.e. MISFET using multiple spacer layers, e.g. multiple sidewall spacers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66575—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate

- H01L29/6659—Lateral single gate silicon transistors where the source and drain or source and drain extensions are self-aligned to the sides of the gate with both lightly doped source and drain extensions and source and drain self-aligned to the sides of the gate, e.g. lightly doped drain [LDD] MOSFET, double diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7834—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with a non-planar structure, e.g. the gate or the source or the drain being non-planar

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

- H01L29/7845—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate the means being a conductive material, e.g. silicided S/D or Gate

Abstract

【解決手段】 凹部14を形成することによってシリコン層3が予め薄膜化された後に、不純物導入領域11が形成される。従って、素子分離絶縁膜5の底面とBOX層2の上面との間に位置している部分のp型のシリコン層3内に、n型の不純物が注入されないため、分離耐圧が低下することを回避できる。しかも、不純物導入領域11はBOX層2の上面に到達して形成されるため、ソース・ドレイン領域12の接合容量が増加することもない。

【選択図】 図1

Description

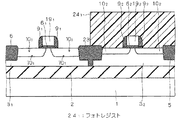

図1は、本発明の実施の形態1に係る半導体装置の構造を示す断面図である。SOI基板4は、シリコン基板1、BOX(buried oxide)層2、及びp型のシリコン層3がこの順に積層された構造を有している。シリコン層3の上面内には、いわゆる部分分離型の素子分離絶縁膜5が部分的に形成されている。素子分離絶縁膜5の材質は、例えばシリコン酸化膜である。素子分離絶縁膜5の底面とBOX層2の上面とによって、シリコン層3の一部が挟まれている。

図9は、本発明の実施の形態2に係る半導体装置の構造を示す断面図である。サイドウォール9の底面は、ゲート絶縁膜6の底面よりも下方に位置している。即ち、サイドウォール9が形成されている部分のシリコン層3の膜厚は、ゲート絶縁膜6が形成されている部分のシリコン層3の膜厚よりも薄い。

図17,18は、図7に示した構造のうち、凹部14が形成されている付近の構造を拡大して示す断面図である。図17を参照して、ゲート絶縁膜6が形成されている部分のシリコン層3の上面と、凹部14の側面とが成す角度αは、90°よりも大きい。角度αは、Cl2やHBr等のエッチングガスに添加するO2ガスの量によって調整することができる。

凹部14の深さは、エッチング時間によって調整することができる。

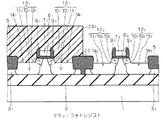

図19は、本発明の実施の形態4に係る半導体装置の構造を示す断面図である。SOI基板4内には、NMOSトランジスタとPMOSトランジスタとが形成されている。NMOSトランジスタは、p型のシリコン層31、ゲート絶縁膜61、ゲート電極71、コバルトシリサイド層81,131、サイドウォール91、及びn型のソース・ドレイン領域121を備えている。ソース・ドレイン領域121は、不純物導入領域101,111を有している。NMOSトランジスタに関しては、上記実施の形態1と同様に、凹部141の底面内にソース・ドレイン領域121が形成された構造(以下、本明細書において「リセスソース・ドレイン構造」と称する)が採用されている。

図29は、本発明の実施の形態5に係る半導体装置の構造を示す断面図である。SOI基板4内には、比較的低い電源電圧(例えば1.0V)で動作するMOSトランジスタ(以下「低電圧動作トランジスタ」と称する)と、比較的高い電源電圧(例えば3.3V)で動作するMOSトランジスタ(以下「高電圧動作トランジスタ)とが形成されている。低電圧動作トランジスタは、例えばCPUコアを構成するトランジスタである。高電圧動作トランジスタは、例えば入出力回路を構成するトランジスタである。

図31は、本発明の実施の形態6に係る半導体装置の製造方法の一工程を示す断面図である。上記実施の形態1等では、ポリシリコン膜19上に形成されたシリコン酸化膜20が除去された後に、凹部14を形成するためのエッチングが行われた。そのため、図7に示したように、エッチングによってポリシリコン膜19が薄膜化された結果として、ゲート電極7が形成された。

図32,33は、本発明の実施の形態7に係る半導体装置の製造方法を工程順に示す断面図である。図32を参照して、図31に示す構造を得た後、CVD法によって、シリコン窒化膜又はシリコン酸化膜を全面に形成する。次に、そのシリコン窒化膜又はシリコン酸化膜をエッチバックすることにより、サイドウォール41,42を形成する。サイドウォール41は、サイドウォール9の側面に接して、凹部14の底面上に形成されている。サイドウォール42は、素子分離絶縁膜5の側面に接して、凹部14の底面上に形成されている。

図34,35は、本発明の実施の形態8に係る半導体装置の製造方法を工程順に示す断面図である。図34を参照して、図8に示す構造を得た後、選択的エピタキシャル成長法によって、ゲート電極7上及びソース・ドレイン領域12上に、シリコン層50,51をそれぞれ形成する。次に、イオン注入法によって、シリコン層50,51内にn型の不純物を高濃度で注入する。

図36〜38は、本発明の実施の形態9に係る半導体装置の製造方法を工程順に示す断面図である。図36を参照して、図4に示す構造を得た後、CVD法によって、シリコン窒化膜60を全面的に形成する。次に、写真製版法によって、素子分離絶縁膜5の上方に位置する部分のシリコン窒化膜60上に、フォトレジスト61を形成する。

図39は、本発明の実施の形態10に係る半導体装置の構造を示す断面図である。図1に示した上記実施の形態1に係る半導体装置を基礎として、n型の不純物導入領域70が、シリコン層3の上面内にさらに形成されている。すなわち、ソース・ドレイン領域12は、いずれもn型の不純物導入領域10,11,70を有している。

上記実施の形態10では、NMOSトランジスタのみを形成する例について述べたが、本実施の形態11では、上記実施の形態10に係る発明をCMOSトランジスタの形成に適用する場合の製造方法について説明する。

図57は、本発明の実施の形態12に係る半導体装置の製造方法の一工程を示す断面図である。まず、上記実施の形態1と同様の方法により、図6に示した構造を得る。

Claims (11)

- 半導体基板、絶縁層、及び第1導電型の半導体層がこの順に積層された構造を有するSOI基板と、

前記半導体層の主面内に部分的に形成され、前記絶縁層とによって前記半導体層の一部を挟む底面を有する素子分離絶縁膜と、

前記素子分離絶縁膜によって規定される素子形成領域内において、前記半導体層の前記主面上に部分的に形成されたゲート構造と、

前記素子形成領域内において、前記ゲート構造から露出している部分の前記半導体層の前記主面内に形成され、前記ゲート構造の下方のチャネル形成領域を挟んで対を成す凹部と、

前記凹部の底面内に形成され、前記チャネル形成領域を挟んで対を成し、その底面又はその空乏層が前記絶縁層に到達し、前記第1導電型とは異なる第2導電型のソース・ドレイン領域と

を備える、半導体装置。 - 前記ゲート構造が形成されている部分の前記半導体層の前記主面と、前記凹部の側面とが成す角度は、90°よりも大きい、請求項1に記載の半導体装置。

- 前記凹部の端部は、前記ゲート構造の端部の下方に潜り込んでいる、請求項1又は2に記載の半導体装置。

- 前記ソース・ドレイン領域は、

前記半導体層の前記主面内に形成された、比較的低濃度の第1の不純物導入領域と、

前記第1の不純物導入領域よりも深く形成された、比較的高濃度の第2の不純物導入領域と

を有し、

前記半導体層の前記主面から前記凹部の前記底面までの深さは、前記半導体層の前記主面から前記第1の不純物導入領域の底面までの深さよりも浅い、請求項1〜3のいずれか一つに記載の半導体装置。 - 前記ソース・ドレイン領域は、前記第2の不純物導入領域よりも浅く前記半導体層の前記主面内に形成された第3の不純物導入領域をさらに有する、請求項4に記載の半導体装置。

- 前記ソース・ドレイン領域は、

前記半導体層の前記主面内に形成された、比較的低濃度の第1の不純物導入領域と、

前記第1の不純物導入領域よりも深く形成された、比較的高濃度の第2の不純物導入領域と、

前記半導体層の前記主面内に形成された第3の不純物導入領域と

を有し、

前記半導体層の前記主面から前記第3の不純物導入領域の底面までの深さは、前記半導体層の前記主面から前記第1の不純物導入領域の底面までの深さよりも深く、

前記半導体層の前記主面から前記凹部の前記底面までの深さは、前記半導体層の前記主面から前記第3の不純物導入領域の前記底面までの深さよりも浅い、請求項1〜3のいずれか一つに記載の半導体装置。 - 前記ゲート構造は、

前記半導体層の前記主面上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

前記ゲート電極の側面に形成された第1のサイドウォールと

を有し、

前記半導体装置は、

前記第1のサイドウォールに接して前記凹部の前記底面上に形成された第2のサイドウォールと、

前記第2のサイドウォールから露出している部分の前記ソース・ドレイン領域上に形成された、金属−半導体化合物層と

をさらに備える、請求項1〜6のいずれか一つに記載の半導体装置。 - 前記素子分離絶縁膜に接して前記凹部の前記底面上に形成された第3のサイドウォールをさらに備え、

前記金属−半導体化合物層は、前記第2及び第3のサイドウォールから露出している部分の前記ソース・ドレイン領域上に形成されている、請求項7に記載の半導体装置。 - 前記凹部の底面上に形成された半導体領域と、

前記半導体領域上に形成された金属−半導体化合物層と

をさらに備える、請求項1〜6のいずれか一つに記載の半導体装置。 - 前記SOI基板内にはNMOSトランジスタ及びPMOSトランジスタが形成されており、

前記半導体装置は、前記NMOSトランジスタ及び前記PMOSトランジスタのうちのいずれか一方である、請求項1〜9のいずれか一つに記載の半導体装置。 - 前記SOI基板内には、比較的低い電源電圧で動作する第1のトランジスタと、比較的高い電源電圧で動作する第2のトランジスタとが形成されており、

前記半導体装置は、前記第1及び第2のトランジスタのうちのいずれか一方である、請求項1〜9のいずれか一つに記載の半導体装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003295234A JP2004241755A (ja) | 2003-01-15 | 2003-08-19 | 半導体装置 |

| KR10-2004-0000165A KR100523310B1 (ko) | 2003-01-15 | 2004-01-03 | 반도체 장치 |

| US10/754,539 US7067881B2 (en) | 2003-01-15 | 2004-01-12 | Semiconductor device |

| TW093100764A TWI231044B (en) | 2003-01-15 | 2004-01-13 | Semiconductor device |

| CNB2004100018675A CN100336228C (zh) | 2003-01-15 | 2004-01-15 | 半导体器件 |

| US11/197,397 US20050275021A1 (en) | 2003-01-15 | 2005-08-05 | Semiconductor device |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003006641 | 2003-01-15 | ||

| JP2003295234A JP2004241755A (ja) | 2003-01-15 | 2003-08-19 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004241755A true JP2004241755A (ja) | 2004-08-26 |

| JP2004241755A5 JP2004241755A5 (ja) | 2006-09-28 |

Family

ID=32964739

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003295234A Pending JP2004241755A (ja) | 2003-01-15 | 2003-08-19 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7067881B2 (ja) |

| JP (1) | JP2004241755A (ja) |

| KR (1) | KR100523310B1 (ja) |

| CN (1) | CN100336228C (ja) |

| TW (1) | TWI231044B (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006310772A (ja) * | 2005-03-28 | 2006-11-09 | Toshiba Corp | Fin型チャネルトランジスタおよびその製造方法 |

| JP2007042964A (ja) * | 2005-08-05 | 2007-02-15 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2007173356A (ja) * | 2005-12-20 | 2007-07-05 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2007201240A (ja) * | 2006-01-27 | 2007-08-09 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP2008515205A (ja) * | 2004-09-29 | 2008-05-08 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法 |

| CN102208448A (zh) * | 2011-05-24 | 2011-10-05 | 西安电子科技大学 | 多晶Si1-xGex/金属并列覆盖双栅SSGOI nMOSFET器件结构 |

| JP2015073138A (ja) * | 2006-12-05 | 2015-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| JP2015073137A (ja) * | 2006-12-05 | 2015-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

Families Citing this family (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100543472B1 (ko) * | 2004-02-11 | 2006-01-20 | 삼성전자주식회사 | 소오스/드레인 영역에 디플리션 방지막을 구비하는 반도체소자 및 그 형성 방법 |

| US8669145B2 (en) * | 2004-06-30 | 2014-03-11 | International Business Machines Corporation | Method and structure for strained FinFET devices |

| JP4175650B2 (ja) * | 2004-08-26 | 2008-11-05 | シャープ株式会社 | 半導体装置の製造方法 |

| JP4440080B2 (ja) * | 2004-11-12 | 2010-03-24 | 株式会社東芝 | 半導体装置およびその製造方法 |

| JP4081071B2 (ja) * | 2004-11-26 | 2008-04-23 | 株式会社東芝 | 半導体記憶装置とその製造方法 |

| US7465972B2 (en) | 2005-01-21 | 2008-12-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | High performance CMOS device design |

| KR100632460B1 (ko) * | 2005-02-03 | 2006-10-11 | 삼성전자주식회사 | 반도체 소자의 제조 방법 |

| JP4718894B2 (ja) * | 2005-05-19 | 2011-07-06 | 株式会社東芝 | 半導体装置の製造方法 |

| US7118954B1 (en) * | 2005-05-26 | 2006-10-10 | United Microelectronics Corp. | High voltage metal-oxide-semiconductor transistor devices and method of making the same |

| JP2007005575A (ja) * | 2005-06-24 | 2007-01-11 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP4822791B2 (ja) * | 2005-10-04 | 2011-11-24 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| TW200733244A (en) * | 2005-10-06 | 2007-09-01 | Nxp Bv | Semiconductor device |

| US7659172B2 (en) * | 2005-11-18 | 2010-02-09 | International Business Machines Corporation | Structure and method for reducing miller capacitance in field effect transistors |

| US20070212861A1 (en) * | 2006-03-07 | 2007-09-13 | International Business Machines Corporation | Laser surface annealing of antimony doped amorphized semiconductor region |

| US8188543B2 (en) * | 2006-11-03 | 2012-05-29 | Freescale Semiconductor, Inc. | Electronic device including a conductive structure extending through a buried insulating layer |

| US7820519B2 (en) | 2006-11-03 | 2010-10-26 | Freescale Semiconductor, Inc. | Process of forming an electronic device including a conductive structure extending through a buried insulating layer |

| US7572706B2 (en) * | 2007-02-28 | 2009-08-11 | Freescale Semiconductor, Inc. | Source/drain stressor and method therefor |

| DE102007030053B4 (de) * | 2007-06-29 | 2011-07-21 | Advanced Micro Devices, Inc., Calif. | Reduzieren der pn-Übergangskapazität in einem Transistor durch Absenken von Drain- und Source-Gebieten |

| GB0717976D0 (en) * | 2007-09-14 | 2007-10-31 | Tavkhelldze Avto | Quantum interference depression effect MOS transistor |

| US7687862B2 (en) * | 2008-05-13 | 2010-03-30 | Infineon Technologies Ag | Semiconductor devices with active regions of different heights |

| CN101728263B (zh) * | 2008-10-24 | 2011-07-06 | 中芯国际集成电路制造(上海)有限公司 | 控制源/漏结电容的方法和pmos晶体管的形成方法 |

| DE102008054075B4 (de) * | 2008-10-31 | 2010-09-23 | Advanced Micro Devices, Inc., Sunnyvale | Halbleiterbauelement mit Abgesenktem Drain- und Sourcebereich in Verbindung mit einem Verfahren zur komplexen Silizidherstellung in Transistoren |

| WO2010049086A2 (en) * | 2008-10-31 | 2010-05-06 | Advanced Micro Devices, Inc. | Recessed drain and source areas in combination with advanced silicide formation in transistors |

| US7759142B1 (en) | 2008-12-31 | 2010-07-20 | Intel Corporation | Quantum well MOSFET channels having uni-axial strain caused by metal source/drains, and conformal regrowth source/drains |

| US8105887B2 (en) * | 2009-07-09 | 2012-01-31 | International Business Machines Corporation | Inducing stress in CMOS device |

| US9209098B2 (en) | 2011-05-19 | 2015-12-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | HVMOS reliability evaluation using bulk resistances as indices |

| US8748285B2 (en) | 2011-11-28 | 2014-06-10 | International Business Machines Corporation | Noble gas implantation region in top silicon layer of semiconductor-on-insulator substrate |

| US8603868B2 (en) * | 2011-12-19 | 2013-12-10 | International Business Machines Corporation | V-groove source/drain MOSFET and process for fabricating same |

| JP6083930B2 (ja) * | 2012-01-18 | 2017-02-22 | キヤノン株式会社 | 光電変換装置および撮像システム、光電変換装置の製造方法 |

| US8872228B2 (en) * | 2012-05-11 | 2014-10-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Strained-channel semiconductor device fabrication |

| JP5944266B2 (ja) * | 2012-08-10 | 2016-07-05 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US9698024B2 (en) | 2012-12-06 | 2017-07-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Partial SOI on power device for breakdown voltage improvement |

| US9202916B2 (en) * | 2013-12-27 | 2015-12-01 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device structure |

| US9941388B2 (en) * | 2014-06-19 | 2018-04-10 | Globalfoundries Inc. | Method and structure for protecting gates during epitaxial growth |

| CN105762106B (zh) * | 2014-12-18 | 2021-02-19 | 联华电子股份有限公司 | 半导体装置及其制作工艺 |

| US10050147B2 (en) * | 2015-07-24 | 2018-08-14 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR102619874B1 (ko) | 2016-06-23 | 2024-01-03 | 삼성전자주식회사 | 불순물 영역을 갖는 반도체 소자 |

| US9741850B1 (en) * | 2016-08-12 | 2017-08-22 | United Microelectronics Corp. | Semiconductor device and method for forming the same |

| US20230157007A1 (en) * | 2021-11-17 | 2023-05-18 | Nanya Technology Corporation | Memory array structure with contact enhancement sidewall spacers |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5710450A (en) * | 1994-12-23 | 1998-01-20 | Intel Corporation | Transistor with ultra shallow tip and method of fabrication |

| FR2749977B1 (fr) * | 1996-06-14 | 1998-10-09 | Commissariat Energie Atomique | Transistor mos a puits quantique et procedes de fabrication de celui-ci |

| US5889331A (en) * | 1996-12-31 | 1999-03-30 | Intel Corporation | Silicide for achieving low sheet resistance on poly-Si and low Si consumption in source/drain |

| JP3070501B2 (ja) | 1997-01-20 | 2000-07-31 | 日本電気株式会社 | 半導体装置 |

| US6518155B1 (en) * | 1997-06-30 | 2003-02-11 | Intel Corporation | Device structure and method for reducing silicide encroachment |

| US6777759B1 (en) | 1997-06-30 | 2004-08-17 | Intel Corporation | Device structure and method for reducing silicide encroachment |

| JP4823408B2 (ja) * | 2000-06-08 | 2011-11-24 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| JP2002141420A (ja) * | 2000-10-31 | 2002-05-17 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

-

2003

- 2003-08-19 JP JP2003295234A patent/JP2004241755A/ja active Pending

-

2004

- 2004-01-03 KR KR10-2004-0000165A patent/KR100523310B1/ko not_active IP Right Cessation

- 2004-01-12 US US10/754,539 patent/US7067881B2/en not_active Expired - Fee Related

- 2004-01-13 TW TW093100764A patent/TWI231044B/zh not_active IP Right Cessation

- 2004-01-15 CN CNB2004100018675A patent/CN100336228C/zh not_active Expired - Fee Related

-

2005

- 2005-08-05 US US11/197,397 patent/US20050275021A1/en not_active Abandoned

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008515205A (ja) * | 2004-09-29 | 2008-05-08 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法 |

| JP2006310772A (ja) * | 2005-03-28 | 2006-11-09 | Toshiba Corp | Fin型チャネルトランジスタおよびその製造方法 |

| JP2007042964A (ja) * | 2005-08-05 | 2007-02-15 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2007173356A (ja) * | 2005-12-20 | 2007-07-05 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2007201240A (ja) * | 2006-01-27 | 2007-08-09 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| US8350331B2 (en) | 2006-01-27 | 2013-01-08 | Renesas Electronics Corporation | Semiconductor device and manufacturing method for the same |

| JP2015073138A (ja) * | 2006-12-05 | 2015-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| JP2015073137A (ja) * | 2006-12-05 | 2015-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| CN102208448A (zh) * | 2011-05-24 | 2011-10-05 | 西安电子科技大学 | 多晶Si1-xGex/金属并列覆盖双栅SSGOI nMOSFET器件结构 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050275021A1 (en) | 2005-12-15 |

| CN1519946A (zh) | 2004-08-11 |

| KR20040065998A (ko) | 2004-07-23 |

| KR100523310B1 (ko) | 2005-10-24 |

| TWI231044B (en) | 2005-04-11 |

| US7067881B2 (en) | 2006-06-27 |

| US20040227185A1 (en) | 2004-11-18 |

| CN100336228C (zh) | 2007-09-05 |

| TW200414547A (en) | 2004-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2004241755A (ja) | 半導体装置 | |

| US10263078B2 (en) | Method of manufacturing a MISFET on an SOI substrate | |

| US20080064173A1 (en) | Semiconductor device, cmos device and fabricating methods of the same | |

| JP5153121B2 (ja) | 電界効果トランジスタ・デバイスとその形成方法 | |

| JP2701762B2 (ja) | 半導体装置及びその製造方法 | |

| US20080090360A1 (en) | Methods for fabricating multiple finger transistors | |

| KR20030004144A (ko) | 반도체장치 및 그 제조방법 | |

| US7648880B2 (en) | Nitride-encapsulated FET (NNCFET) | |

| KR101326393B1 (ko) | 반도체 장치 | |

| JP2009158677A (ja) | 半導体装置の製造方法及び混成トランジスタ用半導体装置の製造方法 | |

| JP2002353449A (ja) | 半導体素子の製造方法 | |

| US7723777B2 (en) | Semiconductor device and method for making same | |

| US7514747B2 (en) | Silicon-on-insulator semiconductor device | |

| JP2003060064A (ja) | Mosfet、半導体装置及びその製造方法 | |

| JP6574885B2 (ja) | 半導体装置の製造方法 | |

| TWI626678B (zh) | 用於類比應用之高增益電晶體 | |

| JP2006049365A (ja) | 半導体装置 | |

| JP2005259945A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP3038740B2 (ja) | 半導体装置の製造方法 | |

| KR101231229B1 (ko) | 반도체 소자의 트랜지스터 제조 방법 | |

| KR100943133B1 (ko) | 반도체 소자의 트랜지스터 및 그 형성 방법 | |

| JP2018148244A (ja) | 半導体装置 | |

| JP2004031529A (ja) | 半導体装置及びその製造方法 | |

| JP2005101064A (ja) | 半導体装置の製造方法 | |

| KR20070001592A (ko) | 반도체 소자의 게이트 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060811 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060811 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090707 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090709 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20091104 |