JP2007005575A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2007005575A JP2007005575A JP2005184295A JP2005184295A JP2007005575A JP 2007005575 A JP2007005575 A JP 2007005575A JP 2005184295 A JP2005184295 A JP 2005184295A JP 2005184295 A JP2005184295 A JP 2005184295A JP 2007005575 A JP2007005575 A JP 2007005575A

- Authority

- JP

- Japan

- Prior art keywords

- source

- ions

- semiconductor device

- drain region

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 72

- 238000004519 manufacturing process Methods 0.000 title claims description 26

- 150000002500 ions Chemical class 0.000 claims abstract description 126

- 238000002955 isolation Methods 0.000 claims abstract description 84

- 239000012535 impurity Substances 0.000 claims abstract description 77

- 229910021332 silicide Inorganic materials 0.000 claims description 44

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 44

- 238000000034 method Methods 0.000 claims description 33

- 238000002513 implantation Methods 0.000 claims description 14

- 239000012212 insulator Substances 0.000 claims description 12

- 238000010438 heat treatment Methods 0.000 claims description 5

- 239000000758 substrate Substances 0.000 abstract description 16

- 239000010410 layer Substances 0.000 description 120

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 32

- 229910052814 silicon oxide Inorganic materials 0.000 description 32

- 238000010586 diagram Methods 0.000 description 23

- 238000000137 annealing Methods 0.000 description 15

- 238000005468 ion implantation Methods 0.000 description 15

- 238000009826 distribution Methods 0.000 description 14

- 230000005465 channeling Effects 0.000 description 10

- 238000012986 modification Methods 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 6

- 210000000746 body region Anatomy 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 238000005530 etching Methods 0.000 description 6

- 239000011229 interlayer Substances 0.000 description 6

- 230000000149 penetrating effect Effects 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 229920005591 polysilicon Polymers 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 229910052751 metal Inorganic materials 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 150000004767 nitrides Chemical class 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- 125000006850 spacer group Chemical group 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 230000007423 decrease Effects 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 229910015900 BF3 Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000001174 ascending effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/66772—Monocristalline silicon transistors on insulating substrates, e.g. quartz substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78609—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device for preventing leakage current

Abstract

【課題】SOI基板に形成され、素子間分離として部分トレンチ分離を有する半導体装置において、トランジスタのソースドレインの低抵抗化およびリーク電流の低減を図る。

【解決手段】埋込酸化膜層(BOX層)2上に形成されたSOI層3には、分離絶縁膜5で規定された活性領域にMOSトランジスタ10が形成されている。分離絶縁膜5は、BOX層2に達していない部分トレンチ分離であり、ソースドレイン領域17は、互いに質量数が異なる第1および第2不純物イオンにより形成されている。

【選択図】図2

【解決手段】埋込酸化膜層(BOX層)2上に形成されたSOI層3には、分離絶縁膜5で規定された活性領域にMOSトランジスタ10が形成されている。分離絶縁膜5は、BOX層2に達していない部分トレンチ分離であり、ソースドレイン領域17は、互いに質量数が異なる第1および第2不純物イオンにより形成されている。

【選択図】図2

Description

本発明は、SOI(Silicon-On-Insulator)構造を有する半導体装置およびその製造方法に関するものである。

近年、半導体装置の性能を向上させることが可能なデバイスとして、支持基板、絶縁体層、シリコン層(SOI層)が積層して成るSOI基板を用いたSOIデバイスが注目されている。例えばSOI基板に形成されたMOS(Metal-Oxide Semiconductor)トランジスタは、そのソースドレイン領域の寄生容量が小さく、高速かつ低消費電力の動作が可能である。

その一方で、バルクのシリコン基板に形成されたMOSトランジスタの性能向上も図られており、例えば下記の特許文献1〜5では、MOSトランジスタのソースドレイン領域の形成に2種類の不純物イオンの注入を行うことが提案されている。

SOIデバイスにおいて、トランジスタ等の各素子間を分離するトレンチ分離としては、SOI層を完全に切り離す完全トレンチ分離(FTI:Full Trench Isolation)と、SOI層の上部のみに形成される部分トレンチ分離(PTI:Partial Trench Isolation)とがある。

特にPTIを有するデバイス構造では、PTIその下に残存するSOI層を通して、トランジスタが形成されたウェル(「ボディ」と呼ばれる)の電位を制御することができる。そのため、ボディ電位を制御するための端子をトランジスタと同一の活性領域内に形成しなくてよく、トランジスタの寄生容量の増大を防止することができる。なおボディ電位は、トランジスタの動作安定化のために通常は一定の値に固定されるが、トランジスタの用途によっては動的に制御される場合もある。

また、トランジスタの寄生容量をさらに低減させるために、SOI層は更に薄膜化される傾向にあり、それに合わせてPTIも薄くする必要が生じている。PTIが薄くなると、トランジスタのソースドレイン領域を形成するための不純物イオンの注入の際に、当該不純物イオンがPTIを突き抜けてその下のSOI層にまで達してしまうことが懸念される。不純物イオンがPTIを突き抜けることにより、PTIの下のSOI層にソースドレイン領域と同じ導電型の不純物層が形成されてしまうと、PTIの素子分離機能が損なわれ問題となる。

よってPTIが薄い場合には、ソースドレイン領域形成のための不純物イオン注入は、極めて低エネルギーで行うことが必要になる。そのため、ソースドレイン領域は従来のものよりも浅く形成されることとなり、その不純物濃度分布は表面部分のみが高いものとなってしまう。

その場合、ソースドレイン領域の低抵抗化を目的として、当該領域上部をシリサイド化すると、不純物濃度の高い表面部分がシリサイド化されてしまう。つまり、形成されたシリサイド層とソースドレイン領域との界面での不純物濃度が低くなってしまう。その結果、シリサイド層とソースドレイン領域との接続抵抗が高くなり、シリサイド化の本来の目的であるソースドレイン領域の低抵抗化を図ることができなくなるという問題が生じる。

また、ソースドレイン領域が浅いので、その底部におけるpn接合面とシリサイド層との距離は近くなる。それにより、ソースドレイン領域における接合容量が大きくなり、リーク電流が増大してしまうという問題が生じる。

本発明は以上のような課題を解決するためになされたものであり、SOI基板に形成され素子間分離としてPTI構造を有する半導体装置において、SOI層の薄膜化を図りつつ、トランジスタのソースドレインの低抵抗化およびリーク電流の低減が可能な半導体装置を提供することを目的とする。

本発明に係る半導体装置は、絶縁体層上に形成された半導体層と、前記半導体層に形成され、当該半導体層における活性領域を規定する分離絶縁膜と、前記活性領域に形成されたソースドレイン領域を有するトランジスタと、前記トランジスタの前記ソースドレイン領域上部に形成されたシリサイド層とを備える半導体装置であって、前記分離絶縁膜は、前記絶縁体層に達していない部分を有しており、前記ソースドレイン領域は、互いに質量数が異なる第1および第2不純物イオンにより形成されているものである。

本発明にかかる半導体装置の製造方法は、(a)絶縁体層上に形成された半導体層に、当該半導体層における活性領域を規定する分離絶縁膜を形成する工程と、(b)前記活性領域に、トランジスタのゲート電極を形成する工程と、(c)前記活性領域に、比較的質量数の小さい第1不純物イオンおよび比較的質量数の大きい第2不純物イオンを、質量数の小さい順に注入することによって、前記トランジスタのソースドレイン領域を形成する工程と、(d)熱処理によって、前記ソースドレイン領域の前記第1および第2不純物イオンを拡散させる工程と、(e)前記ソースドレイン領域上部にシリサイド層を形成する工程とを備える半導体装置の製造方法であって、前記工程(a)において、前記分離絶縁膜は、少なくともその一部が前記絶縁体層にまで達しないように形成され、前記工程(c)における前記第1および第2不純物イオンの注入条件は、前記工程(d)および(e)後における前記シリサイド層と前記ソースドレイン領域との界面において、前記第1不純物イオンの濃度が前記第2不純物イオンの濃度以上になるよう設定されることを特徴とする。

本発明に係る半導体装置によれば、ソースドレイン領域が、互いに質量数が異なる第1および第2不純物イオンにより形成されるので、ソースドレイン領域は、高濃度で且つ緩やかな不純物濃度分布および深いプロファイルを有するようになる。つまり、ソースドレイン領域におけるシリサイド層との界面の深さにおける不純物濃度を高くできると共に、ソースドレイン領域底部のpn接合面とシリサイド層との距離を離すことができる。従って、シリサイド層−ソースドレイン領域間の低抵抗化を図ることができると共に、ソースドレイン領域の接合容量によるリーク電流を削減することが可能である。

本発明に係る半導体装置の製造方法によれば、熱処理後におけるシリサイド層とソースドレイン領域との界面において、第1不純物イオンの濃度が第2不純物イオンの濃度以上になるので、当該界面の不純物濃度が高くなるので、シリサイド層−ソースドレイン領域間の低抵抗化を図ることができる。また、第1および第2不純物イオンを、質量数の小さい順に注入するので、チャネリングにより低エネルギーで第1不純物イオンをより深く注入することができる。よって、ソースドレイン領域を深いプロファイルを形成できるので、ソースドレイン領域底部のpn接合面とシリサイド層との距離を離すことができ、ソースドレイン領域の接合容量によるリーク電流を削減できる。

<実施の形態1>

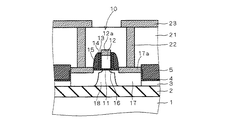

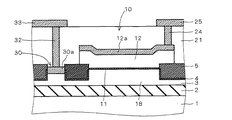

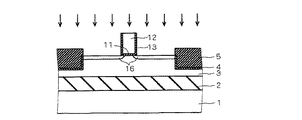

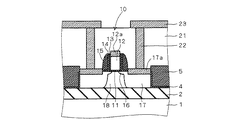

図1〜図3は本発明の実施の形態1に係る半導体装置の構造を示す図である。図1は当該半導体装置が備えるMOSトランジスタの上面図であり、図2および図3はそれぞれ図1のA−A線およびB−B線に沿った断面図である。これらの図を通して、同一の要素には同一の符号を付してある。

図1〜図3は本発明の実施の形態1に係る半導体装置の構造を示す図である。図1は当該半導体装置が備えるMOSトランジスタの上面図であり、図2および図3はそれぞれ図1のA−A線およびB−B線に沿った断面図である。これらの図を通して、同一の要素には同一の符号を付してある。

図1の如く本実施の形態に係る半導体装置は、SOI基板100上に、MOSトランジスタ10並びにそのボディ電位を設定するための端子(ボディ端子)であるボディ電位固定用セル30を有している。ここでは説明の便宜上、MOSトランジスタ10はnチャネル型トランジスタ(nMOSトランジスタ)であると仮定して説明する。但し、後でも述べるが、本発明はpチャネル型トランジスタ(pMOSトランジスタ)に対しても適用可能である。

図2および図3を参照し、上記SOI基板100は、シリコンの支持基板1、絶縁体層としての埋込酸化膜(以下「BOX層」)2、半導体層としてのシリコン層(以下「SOI層」)3とが積層して構成されている。支持基板1には、分離絶縁膜5が形成されており、当該分離絶縁膜5は支持基板1との境界面にシリコン酸化膜4を有している。分離絶縁膜5は、SOI層3の下のBOX層2にまで達しておらず、即ちPTIである。

MOSトランジスタ10は、SOI層3において分離絶縁膜5で規定される活性領域に形成される。MOSトランジスタ10は、SOI層3上に形成されたゲート絶縁膜11および当該ゲート絶縁膜11上に形成されたゲート電極12を有している。ゲート電極12の上部にはシリサイド層12aが形成されており、ゲート電極12の両側面にはそれぞれスペーサ酸化膜13、サイドウォール酸化膜14、サイドウォール窒化膜15が設けられている。またMOSトランジスタ10は、SOI層3内に、ソースドレイン領域17およびエクステンション領域16を有しており、ソースドレイン領域17の上部にはシリサイド層17aが形成されている。

MOSトランジスタ10がnMOSトランジスタである場合、そのエクステンション領域16およびソースドレイン領域17はn型領域であり、ボディ領域18はp型領域である。また図3を参照し、分離絶縁膜5の下のSOI層3およびボディ電位固定用セル30はp型領域である。即ち、ボディ電位固定用セル30は、分離絶縁膜5の下のSOI層3を介してMOSトランジスタ10のボディ領域18に電気的に接続しており、当該ボディ領域18の電位を設定可能なボディ端子として機能する。ボディ電位固定用セル30の上部にはシリサイド層30aが形成されている。

またSOI層3上にはMOSトランジスタ10およびボディ電位固定用セル30を覆うように層間絶縁膜21が形成されている。層間絶縁膜21内には、コンタクト22,24,32が形成されており、それぞれ層間絶縁膜21上に形成された配線23,25,33に接続している。図2の如く、ソースドレイン領域17はシリサイド層17aを介してコンタクト22に接続し、図3の如く、ゲート電極12はシリサイド層12aを介してコンタクト24に接続し、ボディ電位固定用セル30はシリサイド層30aを介してコンタクト32に接続している。

本実施の形態において、MOSトランジスタ10のソースドレイン領域17は、互いに質量数が異なる2種のn型の不純物イオンにより形成されている。より具体的には、比較的質量数が小さい第1不純物イオンとしての燐(P)イオン、並びに、比較的質量数が大きい第2不純物イオンとしての砒素(As)イオンにより形成されている。

Pイオンは比較的質量数が小さいため飛程が長く、またチャネリングを起こしやすい。そのため低エネルギーでも深く注入されてしまい、高濃度のソースドレイン領域を形成するのは困難である。それに対しAsイオンは比較的質量数が大きいため飛程が短く、またチャネリングを起こしにくいので、ソースドレイン領域を容易に高濃度且つ浅く形成できる。よって、SOI層の厚さが薄くなり(例えば100nm以下程度)PTIを薄くした場合においては、ソースドレイン領域の形成には通常Pイオンは使用されず、Asイオンが使用されていた。

しかし、Asイオンのみにより形成されたソースドレイン領域では、不純物の活性化のためのアニールにおいてAsイオンが殆ど拡散しないため、結果的にソースドレイン領域の表面部分のみが高濃度になってしまう。そのため先に述べたように、ソースドレイン領域の上部をシリサイド化したときに、シリサイド層とソースドレイン領域との界面での不純物濃度が低くなり、当該シリサイド層とソースドレイン領域との接続抵抗が高くなってしまうという問題や、ソースドレイン領域底部のpn接合面とシリサイド層との距離が近くなることによりリーク電流が増大してしまうという問題が生じていた。

本実施の形態によれば、ソースドレイン領域17が、互いに質量数が異なるPイオンおよびAsイオンの2つにより形成されるので、Pイオンのみでは困難であった高濃度な不純物濃度分布を実現できる。またPイオンは熱処理により熱拡散しやすいので、従来のAsイオンのみでは困難であった緩やかな不純物濃度分布および深いプロファイルを実現できる。つまり本実施の形態によれば、ソースドレイン領域17におけるシリサイド層17aとの界面の深さ(SOI層3から約50nmの深さ)における不純物濃度を高くできると共に、ソースドレイン領域17底部のpn接合面とシリサイド層17aとの距離を離すことができる。従って、シリサイド層17a−ソースドレイン領域17間の低抵抗化を図ることができると共に、ソースドレイン領域17の接合容量によるリーク電流を削減することが可能である。

つまり、シリサイド層17a−ソースドレイン領域17間の高抵抗化およびリーク電流の増大という上記2つの問題を回避しつつ、MOSトランジスタ10の寄生容量をさらに低減させることができ、半導体装置の高速化並びに低消費電力化に大きく寄与できる。なお、従来のMOSトランジスタにおいては、SOI層の厚さが100nm以下程度に薄くなった場合に、上記2つの問題が顕著になる傾向にあった。よって本実施の形態は、100nm以下の薄いSOI層への適用が特に効果的であると言える。

本実施の形態において、特に図2の如くソースドレイン領域17をその底部がBOX層2にまで達するよう拡散させれば、当該底部にpn接合が形成されないので、ソースドレイン領域17における接合容量を極めて小さくでき、リーク電流の削減により高い効果が得られる。

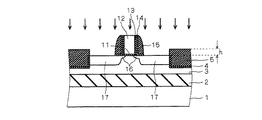

次に、図4〜図10および図12,図13に示す工程図を参照して、本実施の形態に係るMOSトランジスタ10の形成方法について説明する。なお、これらの工程図において、図1〜図3と同様の要素には、同一符号を付してある。

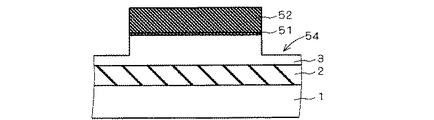

まず、支持基板1、BOX層2、SOI層3が積層して成るSOI基板を用意する。SOI層3の膜厚は、例えば30nm〜200nm程度である。そしてSOI層3上に、シリコン酸化膜51、シリコン窒化膜52を順次成膜し、その後全面にレジスト膜を塗布して写真製版技術(フォトリソグラフィ技術)により、レジストパターン53を形成する(図4)。

そして、レジストパターン53をマスクとしてシリコン窒化膜52、シリコン酸化膜51、SOI層3をエッチングすることにより、分離絶縁膜5を形成するためのトレンチ54を形成する。分離絶縁膜5はPTIであるので、このときのエッチング深さは、トレンチ54の下にSOI層3が残る程度にする(図5)。

なお、SOI層3が薄い場合であっても、トレンチ54を深くすれば分離絶縁膜5の膜厚をある程度稼ぐことはできる。しかし、図3に示したように分離絶縁膜5の下のSOI層3は、ボディ電位固定用セル30の電位をボディ領域18に印加するための配線として機能するので、分離絶縁膜5の下のSOI層3を過度に薄くするとそれが高抵抗化されてしまいボディ領域18の電位が不安定になってしまう。そのため分離絶縁膜5の下のSOI層3の厚さとしては、少なくとも30nm程度を確保することが望ましい。

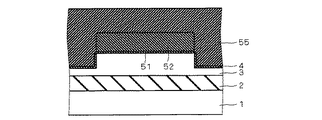

続いて、トレンチ54の内壁を酸化して、膜厚5nm〜50nm程度のシリコン酸化膜4を形成する(分離絶縁膜5の表面にシリコン酸化膜4が不要な場合は、この工程をこの工程は行わなくてもよい)。そしてトレンチ54を埋めるように、全面にシリコン酸化膜55を形成する(図6)。このとき必要に応じて、500℃から1300℃のアニールにより焼き締めを行う。

CMP法により、シリコン窒化膜52が上面に現れる程度までシリコン酸化膜55を除去することで分離絶縁膜5を形成し、その後エッチングによりシリコン窒化膜52を除去する。そして、ウェル形成のためのイオン注入を行ってから、シリコン酸化膜51を除去する(図7)。

そしてSOI層3上面に薄いシリコン酸化膜56を形成し、その上にポリシリコン膜57を堆積する(図8)。フォトリソグラフィ技術を用いたエッチングによりシリコン酸化膜56並びにポリシリコン膜57をパターニングして、ゲート絶縁膜11並びにゲート電極12を形成する。そしてゲート電極12の側面ににスペーサ酸化膜13を形成し、SOI層3にAsイオンを注入してエクステンション領域16(n−領域)を形成する(図9)。そして、必要に応じてポケット注入を行う。

その後、全面にシリコン酸化膜およびシリコン窒化膜を順次形成して、それらをエッチバックすることにより、ゲート電極12の側面にサイドウォール酸化膜14およびサイドウォール窒化膜15形成する。そしてイオン注入により、n+領域であるソースドレイン領域17を形成する(図10)。

上述したように本実施の形態のソースドレイン領域17は、互いに質量数が異なる不純物イオンであるPイオンとAsイオンにより形成される。特に本実施の形態では、Pイオン(第1不純物イオン)およびAsイオン(第2不純物イオン)を質量数が小さい方から順に注入する。即ち、最初にPイオンの注入を行う。このときPイオンが分離絶縁膜5を突き抜けて分離絶縁膜5の分離特性を劣化させない程度の注入エネルギーにする。次いでAsイオンの注入を行う。このときも当該Asイオンが分離絶縁膜5を突き抜けて分離絶縁膜5の分離特性を劣化させない程度の注入エネルギーにする。

注入の順序として先に質量数の小さいPイオンの注入を行うのは、その注入の際にチャネリングを起こさせ、低いエネルギーでSOI層3により深くPイオンを注入するためである。即ち、先にAsイオンを大量に注入するとSOI層3がアモルファス化してしまい、その後にPイオンを注入してもチャネリングが生じにくくなるので望ましくない。

なお本実施の形態では、ソースドレイン領域17の形成工程に先立って、Asイオン注入によるエクステンション領域16の形成工程(図9)が行われるが、その工程におけるAsイオンの注入量は、SOI層3がアモルファス化されない程度であるため、ソースドレイン領域17形成のためのPイオン注入におけるチャネリングの妨げにはならない。

従ってPイオンの注入は、その注入方向がSOI層3の結晶方向に沿うように、SOI層3の上面に対して垂直方向から行う必要がある。なお、分離絶縁膜5内ではチャネリングは生じないため、SOI層3でチャネリングが起こるようにPイオンを注入することで、Pイオンが分離絶縁膜5を突き抜けることを防止しつつ、SOI層3の活性領域に深く注入することができる。

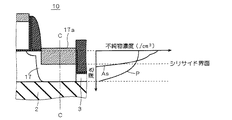

図11は、MOSトランジスタ10のソースドレイン領域17形成のためのPイオンおよびAsイオンの注入工程直後における当該ソースドレイン領域17の不純物濃度分布を示す図である。具体的には、図11に示すC−C線に沿ったソースドレイン領域17の深さに対するPイオンおよびAsイオンそれぞれの不純物濃度分布を示している。同図の如く、PイオンおよびAsイオンの注入工程においては、それらは分離絶縁膜5の底部にまで達しない深さ(即ち、分離絶縁膜5を突き抜けない深さ)まで注入される。また、注入時のチャネリングにより、Pイオンの方がAsイオンよりも深く注入される。

ここで、PイオンおよびAsイオンの分離絶縁膜5の突き抜けを防止するためには、分離絶縁膜5が厚い方が望ましい。しかし、分離絶縁膜5の下のSOI層3を適度な厚さ(例えば約30nm以上)を確保する必要があるため、分離絶縁膜5を深く形成するには限界がある。そこで図10のように、分離絶縁膜5をSOI層3から上方に突出させるて厚くしている。但し、この分離絶縁膜5の突出部分の高さhが高過ぎると、ゲート電極12のパターニングの際、SOI層3と分離絶縁膜5との段差部分にポリシリコンの残骸が残ることが懸念される。よって上記高さhは、それが防止される範囲でできるだけ高いことが望ましい(約50nm程度)。

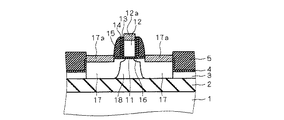

ソースドレイン領域17の形成後、注入したPイオンおよびAsイオンを活性化させるためのアニールを行う。またこのアニールは、ソースドレイン領域17内のPイオンおよびAsイオンは拡散させる効果もある。本実施の形態のソースドレイン領域17には、熱により拡散しやすいPイオンが注入されているため、ソースドレイン領域17はBOX層2に達するにまで拡散する(図12)。

続いて、MOSトランジスタ10上にコバルトやニッケル等の金属を堆積して反応させることにより、ゲート電極12およびソースドレイン領域17の上部にそれぞれシリサイド層12a,17aを形成する(図13)。

そして未反応の金属を除去した後、シリコン酸化膜により層間絶縁膜21を形成し、CMPによりその上面の平坦化を行う。そしてフォトリソグラフィ技術を用いて層間絶縁膜21内にコンタクトホールを形成し、それにタングステン等の金属を埋め込むことでコンタクト22,24,32を形成する。最後に、層間絶縁膜21上に銅などの配線材を堆積し、フォトリソグラフィ技術によりパターニングすることにより配線23,25,33を形成することにより、図2に示したMOSトランジスタ10が形成される。

図14は、上記のアニール工程およびシリサイド形成工程の後におけるソースドレイン領域17の不純物濃度分布を示す図であり、具体的には同図に示すC−C線に沿ったソースドレイン領域17の深さに対するPイオンおよびAsイオンそれぞれの不純物濃度分布を示している。図11と比較して分かるように、Asイオンはアニールを経てもそれほど拡散しないが、Pイオンは当該アニールにより大きく拡散する。

図15に、従来の半導体装置におけるソースドレイン領域17の不純物濃度分布を示す。上述のように、分離絶縁膜5としてPTIを採用した場合、ソースドレイン領域17の形成にはAsイオンのみが使用されていた。Asイオンはアニールを経てもそれほど拡散しないため、図15のようにシリサイド層17aとソースドレイン領域17との界面(シリサイド界面)における不純物濃度が低くなっていた。そのため、シリサイド層17a−ソースドレイン領域17間の接続抵抗が高くなるという問題が生じていた。

それに対し、本実施の形態においては、ソースドレイン領域17にPイオンとAsイオンとが注入されるので、シリサイド層17aとソースドレイン領域17との界面における不純物濃度(Pイオン濃度とAsイオン濃度の和)は高くなる。従って、シリサイド層17a−ソースドレイン領域17間の接続抵抗を低く抑えることができる。

また、ソースドレイン領域17が熱拡散しやすいPイオンを含むため、アニールによりソースドレイン領域17を従来よりも深いプロファイルにすることができる。その結果、ソースドレイン領域17底部のpn接合面とシリサイド層17aとの距離が離れ、ソースドレイン領域17の接合容量に起因するリーク電流を削減することが可能になる。特に、図14のようにPイオンの拡散がBOX層2にまで達するようすれば、ソースドレイン領域17の底部にpn接合が形成されないので、ソースドレイン領域17における接合容量を極めて小さくでき、リーク電流の削減により高い効果が得られる。

また本発明者等は、この発明の効果がより良く得られる条件を定めるために、実際に形成したMOSトランジスタのソースドレイン領域における不純物濃度分布を測定する実験を行った。図16は、その実験結果の一例を示すグラフであり、ソースドレイン領域の深さ方向に対するPイオンおよびAsイオンの濃度分布を二次イオン質量分析法 (SIMS:Secondary Ion Mass Spectrometry)を用いて測定した得たものである。なお、当該測定は、ソースドレイン領域を形成してアニール処理を行った後(PイオンおよびAsイオンの熱拡散後)に行われている。上記実験の結果、図16のようにアニール後のソースドレイン領域におけるシリサイド層界面の深さ(SOI層3表面から約50nmの深さ)において、Pイオン濃度がAsイオン濃度以上になるような場合に、ソースドレイン領域とシリサイド層との接続抵抗を十分に低くすることができる結果が得られた。

なお、本発明はPTIを有する半導体装置に向けられたものであるが、図1〜図3に示したようにMOSトランジスタ10の活性領域を規定する分離絶縁膜5の全体がPTIである必要はない。即ち、分離絶縁膜5は、少なくとも一部にPTI構造(BOX層2に達していない構造)を有していれば本発明の効果は得られる。言い換えれば、分離絶縁膜5として、PTIとFTIとを組み合わせたハイブリッドトレンチ分離(HTI:hybrid trench isolation)を採用してもよい。

図17〜図19は、本実施の形態の変形例を示す図であり、分離絶縁膜5としてHTIを採用した例である。図17は当該変形例のMOSトランジスタの上面図であり、図18および図19はそれぞれ図17のA−A線およびB−B線に沿った断面図である。これらの図において、図1〜図3に示したものに対応する要素にはそれと同一の符号を付してあるので、ここでの詳細な説明は省略する。

この変形例では、図17のように、MOSトランジスタ10とボディ電位固定用セル30との間の部分をPTIにし、それ以外の部分をFTIにしている。即ち、A−A線に沿った断面では、分離絶縁膜5はBOX層2にまで達した構造なる(図18)。また、B−B線に沿った断面では、分離絶縁膜5は、MOSトランジスタ10のボディ電位固定用セル30側ではBOX層2に達しないがその反対側ではBOX層2まで達した構造になる。この変形例のように、分離絶縁膜5の部分的にPTIである場合でも、当該PTIの部分における分離特性を劣化させることなく、シリサイド層17a−ソースドレイン領域17間の接続抵抗を小さくすることが可能であることは明らかである。

以上の説明においては、MOSトランジスタ10をnMOSトランジスタとして説明したが、本発明はpMOSトランジスタに対しても適用可能である。その場合も、ソースドレイン領域17を形成するためのイオンとして、互いに質量数の異なる2種を採用すればよい。またソースドレイン領域17の形成の際には、チャネリングを起こさせるために質量数の小さいものから順に注入することが望ましい。具体的には、比較的質量数の小さい第1イオンとしてB(硼素)イオンを採用し、比較的質量数の大きい第2イオンとしてBF2(フッ化硼素)またはIn(インジウム)イオンを採用することが考えられる。

<実施の形態2>

先に述べたように、分離絶縁膜5にPTIを採用した場合、その分離特性の劣化を防止するためにソースドレイン領域17形成の際に注入する不純物イオンが分離絶縁膜5を突き抜けないようにする必要がある。この突き抜けを抑制するために分離絶縁膜5を厚くすることが考えられるが、当該分離絶縁膜5の下のSOI層3は適度な厚さを確保する必要があるため、分離絶縁膜5を深く形成するには限界がある。そこで、分離絶縁膜5が基板から突出する部分の高さ(図10に示した高さh)を高くすることが考えられるが、SOI層3と分離絶縁膜5との段差部分にゲート電極12のパターニングの際にポリシリコンの残骸が残ることを防止する必要があるため、それにも限界がある。

先に述べたように、分離絶縁膜5にPTIを採用した場合、その分離特性の劣化を防止するためにソースドレイン領域17形成の際に注入する不純物イオンが分離絶縁膜5を突き抜けないようにする必要がある。この突き抜けを抑制するために分離絶縁膜5を厚くすることが考えられるが、当該分離絶縁膜5の下のSOI層3は適度な厚さを確保する必要があるため、分離絶縁膜5を深く形成するには限界がある。そこで、分離絶縁膜5が基板から突出する部分の高さ(図10に示した高さh)を高くすることが考えられるが、SOI層3と分離絶縁膜5との段差部分にゲート電極12のパターニングの際にポリシリコンの残骸が残ることを防止する必要があるため、それにも限界がある。

このように、SOI層3の薄膜化が進むと、分離絶縁膜5を厚く形成することが難しくなる。その結果、ソースドレイン領域17形成のための不純物イオンの注入におけるエネルギーを極めて小さく設定する必要が生じ、そのマージンは小さくなる。よって不純物イオンの分離絶縁膜5の突き抜けを防止しつつ、ソースドレイン領域17を制度よく形成することが困難になる。本実施の形態では、この問題を解決するための技術を提案する。

先に示した実施の形態1では、ゲート電極12の側面のサイドウォール酸化膜14およびサイドウォール窒化膜15は、基板全面にサイドウォール酸化膜14となるシリコン酸化膜およびサイドウォール窒化膜15となるシリコン窒化膜を順次形成し、それらをエッチバックすることにより形成した。実施の形態1では当該エッチバックの際に、図10の如くソースドレイン領域17となるSOI層3の上面を露出させ、その状態でソースドレイン領域17形成のためイオン注入を行った。

それに対し実施の形態2では、上記エッチバック工程において、図20に示すように、サイドウォール酸化膜14となるシリコン酸化膜114が除去されないようにする。そして当該シリコン酸化膜114が、ゲート電極12、SOI層3および分離絶縁膜5の上面覆った状態のまま、当該シリコン酸化膜114を介してソースドレイン領域17形成のためのイオン注入を行う。つまりソースドレイン領域17形成のためのイオン注入の際には、分離絶縁膜5の上面にシリコン酸化膜114が残存する。

そのため、ソースドレイン領域17形成のためのイオン注入工程における分離絶縁膜5の厚さは、実質的にシリコン酸化膜114の厚さの分だけ厚くなる。そのため、注入した不純物イオンが分離絶縁膜5を突き抜けることが生じ難くなり、当該不純物イオン注入のエネルギーのマージンが大きくなる。従って、分離絶縁膜5が薄い場合においても、本発明に係る半導体装置の形成を容易にでき、またSOIデバイスにおけるSOI層の薄膜化にも寄与できる。

実施の形態1で図10を用いて説明したように、分離絶縁膜5のSOI層3から突出した部分の高さhを高くすると、ゲート電極12のパターニングの際にSOI層3と分離絶縁膜5との段差部分にポリシリコンの残骸が残る問題が生じる。それに対し本実施の形態では、その高さhを高くせずに、ゲート電極12のパターニング後に形成するシリコン酸化膜114を利用して実質的な分離絶縁膜5の厚さを増しているので、その問題は伴わない。

また本実施の形態においては、ソースドレイン領域17形成後に行うアニール(実施の形態1における図12の工程に対応)を、ソースドレイン領域17の上面がシリコン酸化膜114で覆われたまま状態で行うとよい。それにより、ソースドレイン領域17内の不純物の外方拡散が抑制され、ソースドレイン領域17の不純物濃度の低下を防止することができ、MOSトランジスタ10の電気的特性の向上に効果的である。

また、ソースドレイン領域17の外方拡散を抑制する必要が無い場合は、ソースドレイン領域17上面のシリコン酸化膜114を除去してからアニールを行ってもよい。

また、ゲート電極12およびソースドレイン領域17の上部にそれぞれシリサイド層12a,17aを形成する際には、ゲート電極12およびソースドレイン領域17上に金属を直接堆積する必要があるため、その際にはゲート電極12およびソースドレイン領域17上のシリコン酸化膜114はエッチングにより除去しておく必要がある。

なお、以上説明した工程を除いては、実施の形態1における製造方法と同様でよい。

<実施の形態3>

上記実施の形態2では、サイドウォール酸化膜14となるシリコン酸化膜114を利用することによって、ソースドレイン領域17形成のためのイオン注入工程における分離絶縁膜5の実質的な厚さを厚くしていた。

上記実施の形態2では、サイドウォール酸化膜14となるシリコン酸化膜114を利用することによって、ソースドレイン領域17形成のためのイオン注入工程における分離絶縁膜5の実質的な厚さを厚くしていた。

実施の形態3では、スペーサ酸化膜13、サイドウォール酸化膜14を実施の形態1と同じように形成する。即ち、スペーサ酸化膜13、サイドウォール酸化膜14の形成の際に、SOI層3における当該ソースドレイン領域17の形成部分は露出する。そしてその後、図21のように別途シリコン酸化膜60を全面に堆積し、当該シリコン酸化膜60を介してソースドレイン領域17形成のためのイオン注入を行う。つまりソースドレイン領域17形成のためのイオン注入の際には、分離絶縁膜5の上面にシリコン酸化膜60が設けられている。

即ち、ソースドレイン領域17形成のためのイオン注入工程における分離絶縁膜5の厚さは、実質的にシリコン酸化膜60の厚さの分だけ厚くなる。そのため、注入した不純物イオンが分離絶縁膜5を突き抜けることが生じ難くなり、当該不純物イオン注入のエネルギーのマージンが大きくなる。従って実施の形態2と同様に、本発明に係る半導体装置の形成を容易にでき、またSOIデバイスにおけるSOI層の薄膜化にも寄与できる。

本実施の形態でも、分離絶縁膜5のSOI層3から突出した部分の高さhを高くせずに、ゲート電極12のパターニング後に形成するシリコン酸化膜60を利用して実質的な分離絶縁膜5の厚さを増やしている。従って、ゲート電極12のパターニングの際にSOI層3と分離絶縁膜5との段差部分にポリシリコンの残骸が残ってしまう問題は伴わない。

また本実施の形態においては、ソースドレイン領域17形成後に行うアニール(実施の形態1における図12の工程に対応)を、ソースドレイン領域17の上面がシリコン酸化膜60で覆われたまま状態で行うとよい。それにより、ソースドレイン領域17内の不純物の外方拡散が抑制され、ソースドレイン領域17の不純物濃度の低下を防止することができ、MOSトランジスタ10の電気的特性の向上に効果的である。

なお、ソースドレイン領域17の外方拡散を抑制する必要が無い場合は、ソースドレイン領域17上面のシリコン酸化膜60を除去してからアニールを行ってもよい。

なお、ゲート電極12およびソースドレイン領域17の上部にそれぞれシリサイド層12a,17aを形成する際には、ゲート電極12およびソースドレイン領域17上に金属を直接堆積する必要があるため、その際には、ゲート電極12およびソースドレイン領域17上のシリコン酸化膜60はエッチングにより除去しておく必要がある。

なお、以上説明した工程を除いては、実施の形態1における製造方法と同様でよい。

1 支持基板、2 BOX層、3 SOI層、4 シリコン酸化膜、5 分離絶縁膜、6 ゲート絶縁膜、10 MOSトランジスタ、11 ゲート絶縁膜、12 ゲート電極、12a,17a,30a シリサイド層、13 スペーサ酸化膜、14 サイドウォール酸化膜、15 サイドウォール窒化膜、16 エクステンション領域、17 ソースドレイン領域、17a シリサイド層、18 ボディ領域、30 ボディ電位固定用セル30。

Claims (11)

- 絶縁体層上に形成された半導体層と、

前記半導体層に形成され、当該半導体層における活性領域を規定する分離絶縁膜と、

前記活性領域に形成されたソースドレイン領域を有するトランジスタと、

前記トランジスタの前記ソースドレイン領域上部に形成されたシリサイド層と

を備える半導体装置であって、

前記分離絶縁膜は、前記絶縁体層に達していない部分を有しており、

前記ソースドレイン領域は、互いに質量数が異なる第1および第2不純物イオンにより形成されている

ことを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記第1不純物イオンは、前記第2不純物イオンよりも質量数が小さく、

前記シリサイド層と前記ソースドレイン領域との界面において、前記第1不純物イオンの濃度は前記第2不純物イオンの濃度以上である

ことを特徴とする半導体装置。 - 請求項1または請求項2記載の半導体装置であって、

前記ソースドレイン領域の底は、前記絶縁体層にまで達している

ことを特徴とする半導体装置。 - 請求項1から請求項3のいずれか記載の半導体装置であって、

前記半導体層は、100nm以下の厚さである

ことを特徴とする半導体装置。 - 請求項1から請求項4のいずれか記載の半導体装置であって、

前記第1不純物イオンは、Pイオンであり、

前記第2不純物イオンは、Asイオンである

ことを特徴とする半導体装置。 - 請求項1から請求項4のいずれか記載の半導体装置であって、

前記第1不純物イオンは、Bイオンであり、

前記第2不純物イオンは、InイオンあるいはBF2イオンである

ことを特徴とする半導体装置。 - (a)絶縁体層上に形成された半導体層に、当該半導体層における活性領域を規定する分離絶縁膜を形成する工程と、

(b)前記活性領域に、トランジスタのゲート電極を形成する工程と、

(c)前記活性領域に、比較的質量数の小さい第1不純物イオンおよび比較的質量数の大きい第2不純物イオンを、質量数の小さい順に注入することによって、前記トランジスタのソースドレイン領域を形成する工程と、

(d)熱処理によって、前記ソースドレイン領域の前記第1および第2不純物イオンを拡散させる工程と、

(e)前記ソースドレイン領域上部にシリサイド層を形成する工程と

を備える半導体装置の製造方法であって、

前記工程(a)において、前記分離絶縁膜は、少なくともその一部が前記絶縁体層にまで達しないように形成され、

前記工程(c)における前記第1および第2不純物イオンの注入条件は、前記工程(d)および(e)後における前記シリサイド層と前記ソースドレイン領域との界面において、前記第1不純物イオンの濃度が前記第2不純物イオンの濃度以上になるよう設定される

ことを特徴とする半導体装置の製造方法。 - 請求項7記載の半導体装置の製造方法であって、

前記工程(b)よりも後、且つ、前記工程(c)よりも前に、

(e)前記分離絶縁膜上を含む前記半導体層上に酸化膜を形成する工程をさらに備え、

前記工程(b)における前記第1および第2不純物イオンの注入は、前記酸化膜を介して行われる

ことを特徴とする半導体装置の製造方法。 - 請求項8記載の半導体装置の製造方法であって、

前記工程(d)の前記熱処理は、前記酸化膜を残存させた状態で行われる

ことを特徴とする半導体装置の製造方法。 - 請求項7から請求項9のいずれか記載の半導体装置の製造方法であって、

前記第1不純物イオンは、Pイオンであり、

前記第2不純物イオンは、Asイオンである

ことを特徴とする半導体装置の製造方法。 - 請求項7から請求項9のいずれか記載の半導体装置の製造方法であって、

前記第1不純物イオンは、Bイオンであり、

前記第2不純物イオンは、InイオンあるいはBF2イオンである

ことを特徴とする半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005184295A JP2007005575A (ja) | 2005-06-24 | 2005-06-24 | 半導体装置およびその製造方法 |

| US11/425,072 US20060289904A1 (en) | 2005-06-24 | 2006-06-19 | Semiconductor device and method of manufacturing the same |

| US12/253,510 US20090047757A1 (en) | 2005-06-24 | 2008-10-17 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005184295A JP2007005575A (ja) | 2005-06-24 | 2005-06-24 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007005575A true JP2007005575A (ja) | 2007-01-11 |

| JP2007005575A5 JP2007005575A5 (ja) | 2008-07-31 |

Family

ID=37566309

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005184295A Withdrawn JP2007005575A (ja) | 2005-06-24 | 2005-06-24 | 半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20060289904A1 (ja) |

| JP (1) | JP2007005575A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008226904A (ja) * | 2007-03-08 | 2008-09-25 | Elpida Memory Inc | 半導体記憶装置及びその製造方法 |

| JP2009158710A (ja) * | 2007-12-26 | 2009-07-16 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2010258471A (ja) * | 2008-06-18 | 2010-11-11 | Internatl Business Mach Corp <Ibm> | 寄生容量が低減されたsoiボディ・コンタクト型fetのための方法 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7935596B2 (en) * | 2008-12-22 | 2011-05-03 | Spansion Llc | HTO offset and BL trench process for memory device to improve device performance |

| CN103779212B (zh) * | 2012-10-18 | 2016-11-16 | 中国科学院微电子研究所 | 半导体结构及其制造方法 |

| US9768254B2 (en) | 2015-07-30 | 2017-09-19 | International Business Machines Corporation | Leakage-free implantation-free ETSOI transistors |

| CN110164978B (zh) * | 2018-02-14 | 2022-06-21 | 联华电子股份有限公司 | 半导体装置以及其制作方法 |

| CN112289852B (zh) * | 2020-12-15 | 2021-05-11 | 北京芯可鉴科技有限公司 | 降低埋氧层泄漏电流的soi器件结构及其制作方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4969715B2 (ja) * | 2000-06-06 | 2012-07-04 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2002141420A (ja) * | 2000-10-31 | 2002-05-17 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP2004241755A (ja) * | 2003-01-15 | 2004-08-26 | Renesas Technology Corp | 半導体装置 |

-

2005

- 2005-06-24 JP JP2005184295A patent/JP2007005575A/ja not_active Withdrawn

-

2006

- 2006-06-19 US US11/425,072 patent/US20060289904A1/en not_active Abandoned

-

2008

- 2008-10-17 US US12/253,510 patent/US20090047757A1/en not_active Abandoned

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008226904A (ja) * | 2007-03-08 | 2008-09-25 | Elpida Memory Inc | 半導体記憶装置及びその製造方法 |

| JP2009158710A (ja) * | 2007-12-26 | 2009-07-16 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2010258471A (ja) * | 2008-06-18 | 2010-11-11 | Internatl Business Mach Corp <Ibm> | 寄生容量が低減されたsoiボディ・コンタクト型fetのための方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090047757A1 (en) | 2009-02-19 |

| US20060289904A1 (en) | 2006-12-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20220029018A1 (en) | Method for manufacturing semiconductor device with recess, epitaxial growth and diffusion | |

| JP3691963B2 (ja) | 半導体装置及びその製造方法 | |

| US20020142529A1 (en) | Semiconductor device comprising buried channel region and method for manufacturing the same | |

| US6437404B1 (en) | Semiconductor-on-insulator transistor with recessed source and drain | |

| KR20010030293A (ko) | 반도체 장치 및 그 제조 방법 | |

| US6825528B2 (en) | Semiconductor device, method of manufacture thereof, and information processing device | |

| US8329539B2 (en) | Semiconductor device having recessed gate electrode and method of fabricating the same | |

| US20070200185A1 (en) | Semiconductor device and method for fabricating the same | |

| JP2007005575A (ja) | 半導体装置およびその製造方法 | |

| JP2013074189A (ja) | 半導体装置及びその製造方法 | |

| JP5627165B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2001156290A (ja) | 半導体装置 | |

| US20130026565A1 (en) | Low rdson resistance ldmos | |

| US20060163675A1 (en) | Semiconductor device and method of manufacturing the same | |

| US7851853B2 (en) | Semiconductor device comprising high-withstand voltage MOSFET and its manufacturing method | |

| US20090162980A1 (en) | Method of manufacturing semiconductor device | |

| US20090152648A1 (en) | Semiconductor Device and Method of Fabricating the Same | |

| JPH09135029A (ja) | Mis型半導体装置及びその製造方法 | |

| JP2007305889A (ja) | 半導体装置およびその製造方法 | |

| US20180342537A1 (en) | Method of manufacturing semiconductor device | |

| KR100591172B1 (ko) | 모스 트랜지스터의 제조 방법 | |

| JP2012230993A (ja) | 半導体基板、半導体装置及びその製造方法 | |

| KR20080029266A (ko) | 반도체 소자의 제조방법 | |

| US20070200151A1 (en) | Semiconductor device and method of fabricating the same | |

| JP3123598B2 (ja) | Lsi及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080617 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080617 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080617 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20091111 |