CN1324674C - 用于键合并转移一种材料以形成半导体器件的方法 - Google Patents

用于键合并转移一种材料以形成半导体器件的方法 Download PDFInfo

- Publication number

- CN1324674C CN1324674C CNB028272463A CN02827246A CN1324674C CN 1324674 C CN1324674 C CN 1324674C CN B028272463 A CNB028272463 A CN B028272463A CN 02827246 A CN02827246 A CN 02827246A CN 1324674 C CN1324674 C CN 1324674C

- Authority

- CN

- China

- Prior art keywords

- substrate

- donor

- semiconductor substrate

- bonding

- transfer layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/2003—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy characterised by the substrate

- H01L21/2007—Bonding of semiconductor wafers to insulating substrates or to semiconducting substrates using an intermediate insulating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

Abstract

本发明公开了一种制造半导体器件的方法。一被进行构图、从而带有一施主台面(18)的施主衬底(12)被键合到一接纳衬底(20)上。在一实施方式中,施主衬底的基块部分被去除掉,但留下一转移层(26),其被键合到接纳衬底上。转移层是从施主台面上转移下来的一层材料。可对接纳衬底的一部分进行加工而形成用于接纳施主台面的凹腔(27、28、或32)。作为备选方案,转移层可被制在接纳衬底上制出的假体构件(46)上,此情况下,施主衬底上可带有台面或不带有台面。在一优选实施方式中,转移层被用于在半导体器件中形成光电探测器等的光学器件。采用本发明,不论接纳衬底的表面是否为平面,都能实现键合。

Description

技术领域

本发明总体上涉及半导体器件的制造,更具体而言,本发明涉及一种采用晶片键合法来制造半导体器件的工艺。

背景技术

晶片接合法是一种公知的工艺,其用于在最终制得的同一器件中形成两种截然不同的单晶半导体材料。这两种材料可具有相同的成分,或者也可以是相异的材料。举例来讲,可将两个硅晶片键合到一起,或者可以将锗晶片或镓晶片键合到一硅晶片上。在多数情况下,键合着的两晶片由一介电层隔开,该介电层不仅作为电绝缘层,还作为构成键合物的接合层。

对于要在两个半导体晶片上都制出器件的场合,希望其中一晶片应足够地薄,以便于器件的制造、以及形成该器件的连线。但是,如从一足够薄的晶片开始执行工艺,则将其键合到受体晶片的操作将难于实现,原因在于薄晶片的结构强度不足。使键合层厚度足够薄的一种方法是在键合之后对其中一晶片的背面进行深刻蚀。但对于希望所制得层体的厚度非常薄的情况,这种方法可能是不理想的,原因在于必须要刻蚀掉大量的晶片材料,且不易控制晶片剩余层厚度的均匀性。现有技术中已发展出一种备选的工艺,其能将半导体薄层材料从施主晶片有效地转移到受体晶片上。利用通过执行氢离子注入而在半导体晶片上形成一弱化区,从而在施主晶片上界定出薄层。施主晶片和受体晶片被键合到一起,随后再采用退火加工或裂解工艺来将位于弱化区上的薄层与施主晶片的其余部分分离开。

发明内容

上述的晶片键合工艺尤其适用于这样的场合:两待键合晶片的平面度非常高—例如对于在一硅晶片上形成硅绝缘体(SOI)的情况。但是,如果将现有技术中这种晶片键合技术应用到受体晶片为非平面的场合中则就会出现问题,例如在受体晶片上已制出或部分制出有源器件和连线的情况。因而,人们希望能有一种改进后的晶片键合工艺,以便于适用于非平面晶片的情况。

此外,还希望这种改进的工艺能只将位于选定区域内的其中一种半导体材料键合并转移到另一种半导体材料上。尽管现有技术中已经尝试着实现选择性的键合(例如通过在硅晶片上与希望进行键合的位置相对应的区域处选择性地执行氢离子注入),但这些努力同样也面临着与非平面受体晶片相键合的问题。

根据本发明的一个方面,一种衬底的键合方法,包括:

在施主衬底中注入一种元素而形成注入区;

对施主衬底进行构图而形成基块部分和施主台面,其中,施主台面包括所述注入区的至少一部分;

利用施主台面和接纳衬底包括的接纳凹腔将施主衬底与接纳衬底键合到一起;以及

去除施主衬底的基块部分,但留下施主衬底的转移层,其在接纳凹腔内被键合到接纳衬底上,

其中所述转移层包括所述施主台面。

根据本发明的另一个方面,一种形成半导体器件的方法,包括:

将第一半导体衬底键合到第二半导体衬底上,其中,第二半导体衬底包括:

第一区域;

第二区域;以及

被制在第一区域内的假体构件,该假体构件使得第一区域的顶面至少与第二区域的顶面上的最高部分等高;

去除掉第一半导体衬底的一部分,从而形成被键合到第二半导体衬底的第一区域上的转移层;以及

对转移层进行构图,以便于在假体构件上形成布有图案的转移层部分,并从第二半导体衬底的第二区域上去除掉一部分所述转移层。

根据本发明的再一个方面,一种衬底的键合方法,包括:

设置第一半导体衬底,其中,对第一半导体衬底进行构图而形成台面和基块部分;

设置第二半导体衬底,其中,第二半导体衬底的形貌是非平面的,且第二半导体衬底包括接纳凹腔;

将第一半导体衬底与第二半导体衬底键合起来,其中,所述键合还包括将台面键合到接纳凹腔中的操作;以及

去除掉第一半导体衬底的基块部分,同时至少留下被键合到第一半导体衬底上的一部分台面,其中所述至少一部分台面是转移层。

附图说明

附图例示性地表示了本发明,但这些附图并非限定性的,在附图中,相同的数字标号指代类似的元件,在附图中:

图1到图4是一些局部剖视图,表示了根据本发明一实施方式的、形成半导体器件的加工步骤,在该实施方式中,一种半导体材料被选择性地转移、键合到一介电层上,该介电层被制在一半导体衬底上;

图5中的局部剖视图表示了本发明的一种备选实施方式,在该实施方式中,一种半导体材料被选择性地转移到一半导体材料上,并直接键合到其上;

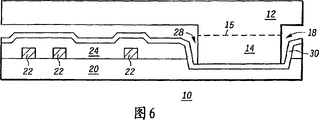

图6中的局部剖视图表示了本发明的一种备选实施方式,在该实施方式中,一种半导体材料被选择性地转移、键合到一介电层上,该介电层沿着制在半导体衬底上的一沟槽布置;

图7中的局部剖视图表示了本发明的一种备选实施方式,在该实施方式中,一种半导体材料被选择性地转移、键合到一介电层上,该介电层形成在一已被制有凹陷的半导体衬底上;以及

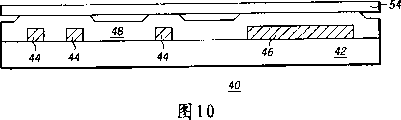

图8到图11中的局部剖视图表示了根据本发明另一实施方式制出的半导体器件,在半导体器件中,在与另一半导体层进行键合的区域处,半导体接纳衬底上增设了一个假体构件(dummy feature)。

为了简化描述、并使描述清晰,附图表示了本发明结构的一般形式,同时,为了避免对本发明的理解造成不必要的干扰,略去了对公知特征和技术的描述和详细讨论。此外,附图中的元件没有必要按照比例进行绘制。举例来讲,图中某些元件的尺寸相对于其它元件被放大了,有利于对本发明实施方式的理解。另外,不同附图中相同的附图标号指代相同的元件。

另外,如果必要的话,说明书和权利要求书中使用了“第一、第二”等词语,这些词语用于区别类似的元件,但并非是为了描述顺序或时间次序。还可以理解:在合适的环境下,这些词语的使用是可互换的,从而,文中所描述的本发明实施方式例如能按照不同于文中所表示或描述次序的顺序进行。

此外,如果需要的话,说明书和权利要求书中为了进行描述而使用了诸如“前、后、顶部、底部、上、下”等的词语,但这些词语并非限定的是永久不变的相对位置关系。可以理解:在合适的环境下,这些词语的使用是可互换的,从而,文中所描述的本发明实施方式例如能按照不同于文中所表示或描述的定向的方位进行。

具体实施方式

总体上讲,本发明既针对于键合到非平面接纳衬底的问题、也针对于只在接纳衬底的选定部位形成键合区域的问题。在一实施方式中,一施主衬底被制成包括一突起部分(下文称之为施主台面),以使得只有该突起部分被转移到接纳衬底上。因而,接纳衬底缺乏全局性的平面度并不会对键合过程造成不利影响。另外,通过在接纳衬底上设置对应的凹陷,可使键合后的最终结构具有更高的平面度。在另一实施方式中,接纳衬底上设置有一个假体构件,其能有效地抬高接纳衬底上要键合另一半导体材料的区域。通过使接纳衬底上要键合另一半导体材料的区域高于接纳衬底上的其余结构、或至少与其余结构等高,可确保在这一区域获得足够强的键合作用。

图1到图4以局部剖面图的形式表示了根据本发明一实施方式的、形成一半导体器件10的制造过程。在图1中,提供了一施主衬底12。施主衬底12的基块优选地是由半导体单晶材料组成的,这些材料例如是硅、锗、砷化镓、磷化铟等。在一优选实施方式、以及整个申请中所描述的本发明应用场合中,施主衬底都是由锗组成的。从图1还可看出,施主衬底12具有一注入区14,该注入区例如是通过将氢离子注入到施主衬底12的表面中而形成的。形成注入区14的目的是为了形成一转移层,这一薄层施主衬底可被转移到另一衬底上。也可选用其它的方法来形成转移层。例如,可在施主衬底的表面上制出一具有应变的晶格层,可在该应变晶格层上生产出一转移层。

可将注入区14的深度或厚度选择为等于要被转移到接纳衬底上的半导体材料的预期厚度。注入能量被选定为使得注入元素的投影范围或峰值浓度(如图1中的虚线15所示)等于所需的深度。通常,该深度范围在到0.1μm到2μm之间,注入剂量在1×1016到1×1017原子/立方厘米之间。在一优选实施方式中,被转移的材料被用作光电检测器件,此情况下,优选地将氢元素注入到锗晶片中,注入深度为1μm到2μm。

在形成转移层之后(不论是通过注入或其它工艺形成),对施主衬底12进行构图,以使得转移层只出现在选定的区域。如图1所示,这一工作是这样完成的:通过淀积并构图一光致抗蚀层而形成一刻蚀掩模16,其保护着位于选定区域的转移层。然后,如图2所示,以刻蚀掩模16作为刻蚀掩模对施主衬底执行刻蚀而形成一施主台面18。优选地是,施主衬底12被刻蚀成除施主台面18之外(即不包括)的注入区14都被去除,从而只有施主台面18中的材料能被从施主衬底12转移到接纳衬底上。除施主台面之外的区域被称为衬底的基块部分。常规的化学刻蚀剂和工艺可被用来执行该刻蚀加工,具体的化学药剂和工艺取决于施主衬底12上的特定材料。在一优选实施方式中,施主衬底12包括氢离子注入后的锗,一种适于形成施主台面18的刻蚀剂是含氯或氟等离子化学刻蚀剂。作为备选方案,可采用诸如含过氧化氢(H2O2)的水溶液等的湿式化学刻蚀剂来形成施主台面18。尽管在图中只表示出了一个施主台面18,但本领域工程人员将能认识到可形成任意数目个这样的台面。

在一备选实施方式中,在对衬底执行注入或其它处理、以形成转移层之前,可对施主衬底12进行构图,以便于形成一个或多个施主台面。在该备选实施方式中,氢离子的注入发生在台面形成之后,且台面的高度和注入状况被调整为只允许台面区域内的材料能被转移到接纳衬底上,从下文的介绍能更清楚地领会这些内容。

在形成或另外提供了已构图后的施主衬底12之后,如图3所示那样将构图后的施主衬底键合到接纳衬底20上。优选地是,接纳衬底的基块是由半导体单晶材料组成的,这些材料例如是硅、锗、砷化镓、磷化铟等。在一优选实施方式,接纳衬底20是由硅构成的。接纳衬底20可包括有源或/或无源的器件,这些器件或者是制在衬底基块材料内、或者是制在基块上。对于理解本发明而言,这些器件的具体情况并不重要。因此,在图中只表示出了选定的几种代表性元件。举例来讲,如图3所示,接纳衬底20包括多个导电构件22,这些导电构件具有一叠置的第一介电层24。按照常规的实践形式,导电构件可由多晶硅或金属制成。同样,可利用公知的技术制出介电层24,在一优选实施方式中,介电层包括二氧化硅(SiO2)材料。

从图3可见,如许多情况中那样,接纳衬底20的表面为非平面。因此,现有技术中用于将另一半导体衬底键合到其上的技术会存在前述的问题。根据本发明,通过将构图后的施主半导体衬底键合到接纳衬底上就可克服这些问题。更具体来讲,施主衬底12被相对于接纳衬底20定位成这样:使得施主台面18与接纳衬底20上即将接纳被转移层的部分相对准。如图所示,施主台面被排布成不会覆盖接纳衬底20上的任何有源电路,但是,这并非是本发明所有应用场合的要求条件。

在施主台面18被充分地对准之后,接纳衬底20和施主衬底12在接触区域处键合到一起,其中的接触区域也即是施主台面与接纳衬底20的上表面相接触的区域。可利用公知的晶片键合技术来实现键合,但通常要采用一压力/温度处理来形成强度足够高的接合键。施主衬底20或接纳衬底12中存在的材料可能会限制采用多高的键合温度和随后的处理。另外,本发明并不对特定的键合技术作出限制。

应当指出的是:尽管在图3中施主衬底20的左侧看起来并未支撑在器件10上,但通常并不是这样的情况。优选地是,施主衬底12和接纳衬底20为晶片的形式,每一晶片上都具有多个设置了器件的位置。因此,施主衬底12很有可能受到接纳衬底上至少一个相邻的器件位置的支撑,甚至可能在别处受到器件10上位置的支撑。如果支撑不足,则另外设置一些台面来提供其它的结构支撑作用。

一旦施主衬底12被键合到接纳衬底20上之后,就执行一分离步骤或转移步骤。在该步骤中,如图4所示,施主衬底12的基块部分被去除。换言之,在除被键合到接纳衬底12上的施主台面18的注入区14,其余的施主衬底12都被去掉。结果就形成了一个转移层26。可利用公知的技术来将转移层与施主衬底12的其余部分分离开。举例来讲,可采用热加工技术,在这种技术中,在氢注入的峰值浓度处(图中用虚线15表示)形成了氢气泡。气泡的出现有利于转移层在施主台面18中此位置处的分离。作为备选方案,可采用机械方法来促使施主台面内相同部位处的分离,例如可采用超声振动、流体喷射等方法来进行裂解。

在转移层26与施主衬底12的其余部分分离开之后,可在转移层26上形成器件,并为其制造连线。在一优选实施方式中,通过移植N型和P型的导电指,并在二者之间形成非掺杂区,就可利用转移层26形成了一光电探测器。然后再形成连线,以便于导电指与制在接纳衬底20中的电路连接起来。

在本发明参照图1-4所描述的实施方式中,施主台面18被键合到接纳衬底20的介电层24上,而没有为接纳施主台面而制出任何特定的容纳结构。在一备选实施方式中,对接纳衬底20执行处理而为施主台面形成一容纳凹腔,从而导致最终制得的结构具有较高的平面度。在某些应用中,转移层26的预期厚度很大,以至于使最终键合/转移后的结构的平面度不足以执行随后的加工。为了能应对这样的厚转移层,接纳衬底中的凹陷可被制成具有合适的深度,以达到足够高的最终平面度。例如,在图5中,对介电层24进行构图而形成一开口27,其暴露出接纳衬底20的基块半导体材料的表面。作为备选方案,如图6所示,可在接纳衬底20的基块材料中形成一凹腔或沟槽28。或者可如图7所示那样对介电层24执行刻蚀而形成一个凹陷32,该凹陷并不会裸露出接纳衬底20的下层结构。在图5-7的任一实施方式中,可按照公知的刻蚀技术制出接纳凹腔(不论是开口27、沟槽28或凹陷32),具体的刻蚀技术将取决于需要被去除的材料。

如图5中实施方式所示,施主台面18被键合到接纳衬底20的基块上(即这是一个半导体对半导体的接合键),而不是被键合到介电材料上。在希望获得异质结构器件(例如锗在硅上的结构、砷化铟镓在砷化镓上的结构等)的场合中,这样的设计是有利的。为了实现半导体对半导体的键合,应当注意避免或减小在裸露的半导体表面上形成本体氧化物层,该氧化物层会降低键合强度或影响异质结器件的工作。

在上述各种备选形式的任一种中,在将施主台面键合到接纳衬底20上之前,都可在其上淀积一可选性质的介电层30。介电层30可被用来在两衬底材料(如图6所示)之间形成电绝缘、或增强两衬底之间的键合作用。适于作为介电层30的材料包括SiO2、氟化的SiO2、苯并环丁烯(BCB)、MSSQ(methysilsequioxane)、以及其它用于键合“胶接层”的材料。如果采用介电层30的话,可用常规的工艺来对其进行淀积。

下面将参照图8-11对一种备选的方法进行介绍,该方法用于解决与在非平面接纳衬底上执行键合相关的问题,这些附图也表示了一种根据本发明的、用于形成一半导体器件40的加工方法。如图8所示,接纳衬底42包括导电构件44以及一第一介电层48。这些元件分别类似于前一实施方式中的接纳衬底20、导电构件22、以及第一介电层24。此外,接纳衬底42包括一假体构件46,其被制在要从施主衬底50转移来一个层体的位置处。图9中表示出了施主衬底50,其与前述的施主衬底12一样,优选地是单晶半导体材料,并包括一注入区52,也具有注入元素(优选为氢)的峰值浓度区,其在图中由虚线53表示。

设置假体构件46是为了抬高接纳衬底42上要与施主衬底50相键合的区域。通过将接纳衬底上将要进行键合的区域设置成高于其它结构、或至少与其它结构等高,就可保证在该区域具有充分的键合作用。例如,如图9所示,导电构件44使得接纳衬底的上表面成为非平面。设置了一个假体构件46来形成一升高的表面,在该表面上进行键合。优选地是,假体构件是与导电构件或其它形貌构件同时制出的,并用同种材料制成,从而可避免另外增加加工步骤。假体构件的制造不要求任何特定的材料(例如,其可用除导电材料之外的介电材料制成)。假体构件的尺寸和形状应当被选定为与施主衬底50上要被键合和转移的部分具有相同的尺寸、或大于这一部分。尽管在图中只表示出了一个假体构件,但为了实现相同或相似的效果可采用多个假体构件。

根据本发明,如图9所示,具有假体构件46的接纳衬底42被键合到施主衬底50上。可按照上述的方法将施主衬底50键合到接纳衬底42上,且优选地是,只在两衬底相互接触的区域处(包括假体构件46上的区域)产生键合。

如图10所示,施主衬底50的基块部分被去掉,只留下一覆盖着接纳衬底42整个表面的转移层54。优选地是,该去除过程是采用上文参照去除施主衬底12基块部分所描述的几种技术中的某一种技术完成的。作为备选方案,也可采用背面刻蚀技术。然后,如图11所示,用平版印刷法对转移层54进行构图和刻蚀处理,从而在假体构件46上留下一构图的转移层56。可对构图后的转移层进行加工而形成一器件,该器件例如是光电探测器等的光学器件,其与制在接纳衬底42上的电路保持电连接。

因而,很显然:本申请提供了一种改进的衬底键合方法,该方法可应用在非平面接纳衬底上,另外,其还实现了选择性的键合。利用制在施主衬底上的施主台面,可选择性地将半导体材料转移到接纳衬底上。接纳衬底无须具有很高的平面度,其可被改变为具有一台面接纳凹陷,以便于进一步提高键合后最终结构的平面度。在被转移层体的厚度方面,本发明所提出的制造方法具有高度的控制能力。另外,本发明尤其利于不相似的半导体材料要被键合到一起的场合,原因在于可同步地进行加工,而不是顺次地将某种半导体材料的器件键合到另一半导体材料上。将施主台面半导体材料转移到接纳衬底上一个或多个选定区域、并在台面转移之后形成一平面的设计有利于随后的集成电路加工步骤,后续的步骤既针对施主衬底的某些部分,也针对接纳衬底的某些部分。例如,可在整个半导体器件的施主台面部分和接纳衬底部分上制出金属化层或层间介电层。

上文针对具体的实施方式对本发明的效果、其它优点、以及解决问题的方案进行了描述。但是,这些效果、优点、解决问题的方案、以及任何其它因素都不应理解为某些或全部权利要求中必要的、所需的或重要的特征或因素,其中的其它因素可带来任何效果、优点、或显见或变得显见的方案。在本文的语境中,词语“包括”、“包含”或这些词语的其它变型被用来表达非排它性的开放式含有,例如,包括所列出元素的工艺、方法、物品或装置不仅包括这些元素,而且还可能包括其它未被列出的元素,或这些方法、工艺、物品或装置固有的元素。

在上文的描述中,参照具体的实施方式对本发明进行了描述。但是,本领域普通技术人员能领会:在不悖离本发明范围的前提下,可作出多种形式的改动和变型,其中,本发明的范围由后附的权利要求书限定。举例来讲,普通技术人员可以意识到可将所述任一实施方式中的一个或几个方面与另一实施方式进行结合(例如施主台面可与假体构件组合使用)。此外,本领域技术人员将意识到:施主衬底在与受体晶片键合之前,可在其中制有器件或部分的器件。另外,在将施主衬底键合到接纳衬底上之前,可在接纳衬底中制有器件或部分的器件。另外,在将施主衬底键合到接纳衬底上之后,可执行本领域公知的各个步骤来完成集成电路的制造。因此,本文的描述和附图只被看作是示例性的,而非限定性的,且本发明的范围涵盖所有的改型形式。

Claims (3)

1.一种衬底的键合方法,包括:

在施主衬底中注入一种元素而形成注入区;

对施主衬底进行构图而形成基块部分和施主台面,其中,施主台面包括所述注入区的至少一部分;

利用施主台面和接纳衬底包括的接纳凹腔将施主衬底与接纳衬底键合到一起;以及

去除施主衬底的基块部分,但留下施主衬底的转移层,其在接纳凹腔内被键合到接纳衬底上,

其中所述转移层包括所述施主台面。

2.一种形成半导体器件的方法,包括:

将第一半导体衬底键合到第二半导体衬底上,其中,第二半导体衬底包括:

第一区域;

第二区域;以及

被制在第一区域内的假体构件,该假体构件使得第一区域的顶面至少与第二区域的顶面上的最高部分等高;

去除掉第一半导体衬底的一部分,从而形成被键合到第二半导体衬底的第一区域上的转移层;以及

对转移层进行构图,以便于在假体构件上形成布有图案的转移层部分,并从第二半导体衬底的第二区域上去除掉一部分所述转移层。

3.一种衬底的键合方法,包括:

设置第一半导体衬底,其中,对第一半导体衬底进行构图而形成台面和基块部分;

设置第二半导体衬底,其中,第二半导体衬底的形貌是非平面的,且第二半导体衬底包括接纳凹腔;

将第一半导体衬底与第二半导体衬底键合起来,其中,所述键合还包括将台面键合到接纳凹腔中的操作;以及

去除掉第一半导体衬底的基块部分,同时至少留下被键合到第一半导体衬底上的一部分台面,其中所述至少一部分台面是转移层。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/022,711 | 2001-12-17 | ||

| US10/022,711 US6616854B2 (en) | 2001-12-17 | 2001-12-17 | Method of bonding and transferring a material to form a semiconductor device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1615543A CN1615543A (zh) | 2005-05-11 |

| CN1324674C true CN1324674C (zh) | 2007-07-04 |

Family

ID=21811041

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028272463A Expired - Fee Related CN1324674C (zh) | 2001-12-17 | 2002-12-05 | 用于键合并转移一种材料以形成半导体器件的方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US6616854B2 (zh) |

| EP (1) | EP1500132A2 (zh) |

| JP (1) | JP4554930B2 (zh) |

| KR (1) | KR20040079916A (zh) |

| CN (1) | CN1324674C (zh) |

| AU (1) | AU2002353020A1 (zh) |

| TW (1) | TWI255525B (zh) |

| WO (1) | WO2003052817A2 (zh) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7078320B2 (en) * | 2004-08-10 | 2006-07-18 | International Business Machines Corporation | Partial wafer bonding and dicing |

| US7288458B2 (en) * | 2005-12-14 | 2007-10-30 | Freescale Semiconductor, Inc. | SOI active layer with different surface orientation |

| KR100755368B1 (ko) * | 2006-01-10 | 2007-09-04 | 삼성전자주식회사 | 3차원 구조를 갖는 반도체 소자의 제조 방법들 및 그에의해 제조된 반도체 소자들 |

| US7682930B2 (en) * | 2006-06-09 | 2010-03-23 | Aptina Imaging Corporation | Method of forming elevated photosensor and resulting structure |

| US7432174B1 (en) * | 2007-03-30 | 2008-10-07 | Advanced Micro Devices, Inc. | Methods for fabricating semiconductor substrates with silicon regions having differential crystallographic orientations |

| EP1993126B1 (en) * | 2007-05-18 | 2011-09-21 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing methods of semiconductor substrate |

| US8201325B2 (en) | 2007-11-22 | 2012-06-19 | International Business Machines Corporation | Method for producing an integrated device |

| US7842583B2 (en) * | 2007-12-27 | 2010-11-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor substrate and method for manufacturing semiconductor device |

| US7927975B2 (en) | 2009-02-04 | 2011-04-19 | Micron Technology, Inc. | Semiconductor material manufacture |

| GB0914251D0 (en) * | 2009-08-14 | 2009-09-30 | Nat Univ Ireland Cork | A hybrid substrate |

| CN102822970B (zh) * | 2010-03-31 | 2015-06-17 | Soitec公司 | 键合半导体结构及其形成方法 |

| FR2965974B1 (fr) * | 2010-10-12 | 2013-11-29 | Soitec Silicon On Insulator | Procédé de collage moléculaire de substrats en silicium et en verre |

| US8778737B2 (en) | 2011-10-31 | 2014-07-15 | International Business Machines Corporation | Flattened substrate surface for substrate bonding |

| US9190379B2 (en) | 2012-09-27 | 2015-11-17 | Apple Inc. | Perimeter trench sensor array package |

| US9209142B1 (en) | 2014-09-05 | 2015-12-08 | Skorpios Technologies, Inc. | Semiconductor bonding with compliant resin and utilizing hydrogen implantation for transfer-wafer removal |

| WO2017052646A1 (en) * | 2015-09-25 | 2017-03-30 | Intel Corporation | Island transfer for optical, piezo and rf applications |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6093623A (en) * | 1998-08-04 | 2000-07-25 | Micron Technology, Inc. | Methods for making silicon-on-insulator structures |

| CN1272684A (zh) * | 1999-02-02 | 2000-11-08 | 佳能株式会社 | 衬底及其制造方法 |

| US6191007B1 (en) * | 1997-04-28 | 2001-02-20 | Denso Corporation | Method for manufacturing a semiconductor substrate |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4966646A (en) | 1986-09-24 | 1990-10-30 | Board Of Trustees Of Leland Stanford University | Method of making an integrated, microminiature electric-to-fluidic valve |

| US5389569A (en) * | 1992-03-03 | 1995-02-14 | Motorola, Inc. | Vertical and lateral isolation for a semiconductor device |

| JP3114570B2 (ja) * | 1995-05-26 | 2000-12-04 | オムロン株式会社 | 静電容量型圧力センサ |

| JPH09127352A (ja) * | 1995-10-30 | 1997-05-16 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP3257624B2 (ja) * | 1996-11-15 | 2002-02-18 | キヤノン株式会社 | 半導体部材の製造方法 |

| JPH1140823A (ja) * | 1997-05-22 | 1999-02-12 | Fujitsu Ltd | 光検出器モジュール |

| JPH1145862A (ja) * | 1997-07-24 | 1999-02-16 | Denso Corp | 半導体基板の製造方法 |

| US6271101B1 (en) * | 1998-07-29 | 2001-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Process for production of SOI substrate and process for production of semiconductor device |

| JP2001007362A (ja) * | 1999-06-17 | 2001-01-12 | Canon Inc | 半導体基材および太陽電池の製造方法 |

| JP2001102523A (ja) * | 1999-09-28 | 2001-04-13 | Sony Corp | 薄膜デバイスおよびその製造方法 |

| US6400009B1 (en) * | 1999-10-15 | 2002-06-04 | Lucent Technologies Inc. | Hermatic firewall for MEMS packaging in flip-chip bonded geometry |

-

2001

- 2001-12-17 US US10/022,711 patent/US6616854B2/en not_active Expired - Fee Related

-

2002

- 2002-12-05 JP JP2003553615A patent/JP4554930B2/ja not_active Expired - Fee Related

- 2002-12-05 CN CNB028272463A patent/CN1324674C/zh not_active Expired - Fee Related

- 2002-12-05 AU AU2002353020A patent/AU2002353020A1/en not_active Abandoned

- 2002-12-05 WO PCT/US2002/038564 patent/WO2003052817A2/en active Application Filing

- 2002-12-05 KR KR10-2004-7010056A patent/KR20040079916A/ko not_active Application Discontinuation

- 2002-12-05 EP EP02789986A patent/EP1500132A2/en not_active Withdrawn

- 2002-12-16 TW TW091136258A patent/TWI255525B/zh not_active IP Right Cessation

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6191007B1 (en) * | 1997-04-28 | 2001-02-20 | Denso Corporation | Method for manufacturing a semiconductor substrate |

| US6093623A (en) * | 1998-08-04 | 2000-07-25 | Micron Technology, Inc. | Methods for making silicon-on-insulator structures |

| CN1272684A (zh) * | 1999-02-02 | 2000-11-08 | 佳能株式会社 | 衬底及其制造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4554930B2 (ja) | 2010-09-29 |

| TWI255525B (en) | 2006-05-21 |

| WO2003052817B1 (en) | 2003-09-25 |

| JP2005513781A (ja) | 2005-05-12 |

| WO2003052817A2 (en) | 2003-06-26 |

| AU2002353020A1 (en) | 2003-06-30 |

| WO2003052817A3 (en) | 2003-08-21 |

| EP1500132A2 (en) | 2005-01-26 |

| AU2002353020A8 (en) | 2003-06-30 |

| KR20040079916A (ko) | 2004-09-16 |

| US20030114001A1 (en) | 2003-06-19 |

| US6616854B2 (en) | 2003-09-09 |

| CN1615543A (zh) | 2005-05-11 |

| TW200302548A (en) | 2003-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1324674C (zh) | 用于键合并转移一种材料以形成半导体器件的方法 | |

| CN1155073C (zh) | 平面密集构图的绝缘体基硅结构及其制造方法 | |

| CN1836323A (zh) | 混合晶向衬底上的高性能cmos soi器件 | |

| CN1838417A (zh) | 半导体结构及其形成方法 | |

| KR970030640A (ko) | 반도체 장치의 소자 분리막 형성방법 | |

| KR100366748B1 (ko) | 스텐실 마스크 및 스텐실 마스크의 형성 방법 | |

| KR100511900B1 (ko) | 에스오아이 기판의 제조방법 | |

| KR20010060988A (ko) | 반도체 장치의 분리구조 제조방법 | |

| JP3216488B2 (ja) | 半導体装置の製造方法 | |

| KR20210056831A (ko) | Soi 기판 제조 방법 | |

| KR100289658B1 (ko) | 반도체 소자 분리방법 | |

| KR100318262B1 (ko) | 반도체 소자의 얼라인먼트 키 형성방법 | |

| KR20020002640A (ko) | 반도체소자의 소자분리막 형성방법 | |

| KR20210111488A (ko) | 멀티 soi 기판 제조 방법 및 멀티 soi 기판 | |

| KR19990032753A (ko) | 반도체 소자 분리 방법 | |

| US20030022458A1 (en) | Method for forming a shallow trench isolation in a semiconductor structure | |

| KR950029849A (ko) | 소자분리막 형성 방법 | |

| KR950012680A (ko) | 반도체소자의 소자분리막 제조방법 | |

| KR20070090089A (ko) | 반도체 장치 및 그 제조 방법 | |

| KR950021349A (ko) | 준자기정렬 트렌치 소자격리방법 | |

| KR19980055926A (ko) | 반도체 소자의 제조방법 | |

| KR19980014005A (ko) | 반도체 소자의 격리방법 | |

| KR20040001326A (ko) | 반도체소자의 소자분리막 제조방법 | |

| JPS6386562A (ja) | 半導体装置 | |

| KR20080051684A (ko) | 반도체 장치의 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C56 | Change in the name or address of the patentee |

Owner name: FISICAL SEMICONDUCTOR INC. Free format text: FORMER NAME: FREEDOM SEMICONDUCTOR CORP. |

|

| CP01 | Change in the name or title of a patent holder |

Address after: Texas in the United States Patentee after: FREESCALE SEMICONDUCTOR, Inc. Address before: Texas in the United States Patentee before: FreeScale Semiconductor |

|

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20070704 Termination date: 20141205 |

|

| EXPY | Termination of patent right or utility model |