CN103378045A - 引线框架、半导体封装件及它们的制造方法 - Google Patents

引线框架、半导体封装件及它们的制造方法 Download PDFInfo

- Publication number

- CN103378045A CN103378045A CN201310133137XA CN201310133137A CN103378045A CN 103378045 A CN103378045 A CN 103378045A CN 201310133137X A CN201310133137X A CN 201310133137XA CN 201310133137 A CN201310133137 A CN 201310133137A CN 103378045 A CN103378045 A CN 103378045A

- Authority

- CN

- China

- Prior art keywords

- terminal

- semiconductor package

- lead frame

- hole

- cap

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 152

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 41

- 239000011347 resin Substances 0.000 claims abstract description 72

- 229920005989 resin Polymers 0.000 claims abstract description 72

- 238000009434 installation Methods 0.000 claims description 30

- 238000000034 method Methods 0.000 claims description 21

- 239000000758 substrate Substances 0.000 abstract description 17

- 230000000149 penetrating effect Effects 0.000 abstract description 3

- 238000007747 plating Methods 0.000 abstract description 2

- 238000007789 sealing Methods 0.000 abstract 1

- 239000002184 metal Substances 0.000 description 16

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000000463 material Substances 0.000 description 15

- 239000010931 gold Substances 0.000 description 13

- 238000000465 moulding Methods 0.000 description 13

- 229910000679 solder Inorganic materials 0.000 description 9

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000005520 cutting process Methods 0.000 description 8

- 239000003822 epoxy resin Substances 0.000 description 8

- 239000000945 filler Substances 0.000 description 8

- 229920000647 polyepoxide Polymers 0.000 description 8

- 229920001721 polyimide Polymers 0.000 description 6

- 239000010949 copper Substances 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000003475 lamination Methods 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- 239000009719 polyimide resin Substances 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 238000007788 roughening Methods 0.000 description 3

- 229910000881 Cu alloy Inorganic materials 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 238000004026 adhesive bonding Methods 0.000 description 2

- 239000007767 bonding agent Substances 0.000 description 2

- 238000004925 denaturation Methods 0.000 description 2

- 230000036425 denaturation Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 241000218202 Coptis Species 0.000 description 1

- 235000002991 Coptis groenlandica Nutrition 0.000 description 1

- 230000006835 compression Effects 0.000 description 1

- 238000007906 compression Methods 0.000 description 1

- 238000000748 compression moulding Methods 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000005499 meniscus Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000004080 punching Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07

- H01L21/4814—Conductive parts

- H01L21/4821—Flat leads, e.g. lead frames with or without insulating supports

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/16—Fillings or auxiliary members in containers or encapsulations, e.g. centering rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49579—Lead-frames or other flat leads characterised by the materials of the lead frames or layers thereon

- H01L23/49582—Metallic layers on lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49579—Lead-frames or other flat leads characterised by the materials of the lead frames or layers thereon

- H01L23/49586—Insulating layers on lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/561—Batch processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45147—Copper (Cu) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L24/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49121—Beam lead frame or beam lead device

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Lead Frames For Integrated Circuits (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Abstract

提供一种能够提高实装至基板时的连接可靠性的引线框架、具有该引线框架的半导体封装件、及它们的制造方法。本半导体封装件具有:引线框架,具有安装半导体芯片的芯片安装部、及作为外部连接端子的端子部;半导体芯片,安装于所述芯片安装部,并与所述端子部电气连接;贯穿槽,沿厚度方向从作为所述半导体芯片侧的面的一个面至另一个面贯穿所述端子部;盖部,对所述端子部的所述一个面侧的所述贯穿槽的端部进行堵塞;及树脂部,对所述半导体芯片进行封装,使所述端子部的所述另一个面及所述贯穿槽的内侧面露出。其中,所述端子部的所述另一个面及所述贯穿槽的所述内侧面被镀膜覆盖。

Description

技术领域

本发明涉及一种引线框架、具有该引线框架的半导体封装件及它们的制造方法。

背景技术

现有技术中,在例如SON(Small-Outline No Lead)或QFN(Quad FlatNo Lead)等无引线半导体封装件中,用于与基板等连接的外部连接端子从例如半导体封装件的底面、及由个片化(也称“划片”或“切割”处理)时的切割而呈现出的侧面露出。因为个片化之前通常要形成镀膜,所以从半导体封装件露出的外部连接端子的底面形成了镀膜,但是,从半导体封装件露出的外部连接端子的侧面却没有形成镀膜。

为此,在使用焊料将半导体封装件实装至基板等时,外部连接端子的侧面对焊料的湿润性和连接性基本上没有贡献,主要是外部连接端子的底面对焊料的湿润性和连接性作出了贡献。因此,因为半导体封装件与基板间所形成的焊料量较少,所以半导体封装件和基板间的热膨张系数的差导致产生应力,进而导致半导体封装件和基板间的连接可靠性下降。

作为提高连接可靠性的对策,例如,提出了一种在外部连接端子上形成贯穿孔,并且为了在进行树脂封装时不让树脂流入贯穿孔,而在贯穿孔内填充焊料材料、金、或银等导电材料的技术。在该技术中,个片化之后,使贯穿孔内填充的导电材料作为外部连接端子的一部分从半导体封装件的侧面露出,据此,对连接可靠性的提高进行了尝试。

现有技术文献

专利文献

专利文献1:美国发明专利申请公布第2011/0108965号说明书

发明内容

发明要解决的课题

但是,在贯穿孔内填充金或银的情况下,因为与形成普通的镀膜相比,较多地使用了高价材料,所以存在着半导体封装件的制造成本上升的问题。因此,一般来说,都是将廉价的焊料材料填充至贯穿孔内,但是,焊料材料容易发生氧化,并且在包括树脂封装步骤的半导体芯片实装步骤中表面也容易发生氧化,这样,就不能充分地确保将半导体封装件实装至基板时的连接可靠性。

本发明是鉴于上述问题而提出的,其课题在于提供一种可提高实装至基板时的连接可靠性的引线框架、半导体封装件及它们的制造方法。

用于解决课题的手段

本半导体封装件包括:引线框架,具有安装半导体芯片的芯片安装部、及作为外部连接端子的端子部;半导体芯片,安装在所述芯片安装部上,并与所述端子部电气连接;贯穿槽,沿宽度方向从作为所述半导体芯片侧的面的一个面至另一个面贯穿所述端子部;盖部,对所述端子部的所述一个面侧的所述贯穿槽的端部进行堵塞;以及树脂部,对所述半导体芯片进行封装,使所述端子部的所述另一个面及所述贯穿槽的内侧面露出。其中,所述端子部的所述另一个面及所述贯穿槽的所述内侧面被镀膜覆盖。

本引线框架包含被进行个片化的多个区域。各区域具有:芯片安装部,用于安装半导体芯片;端子部,作为外部连接端子;支持部,对所述芯片安装部和所述端子部进行支持;贯穿孔,沿厚度方向从作为安装所述半导体芯片侧的面的一个面至另一个面贯穿所述端子部;以及盖部,对所述端子部的所述一个面侧的所述贯穿孔的端部进行堵塞。其中,所述贯穿孔被形成为,跨越对所述各区域进行个片化时的切割线。

发明的效果

根据所公开的技术,能够提供一种可提高实装至基板时的连接可靠性的引线框架、半导体封装件及它们的制造方法。

附图说明

图1A、图1B是对第1实施方式的半导体封装件进行例示的图。

图2是对端子部上所形成的新月形部进行说明的图。

图3A、图3B是对第1实施方式的半导体封装件的制造步骤进行例示的图(其1)。

图4A、图4B是对第1实施方式的半导体封装件的制造步骤进行例示的图(其2)。

图5A、图5B是对第1实施方式的半导体封装件的制造步骤进行例示的图(其3)。

图6A、图6B是对第2实施方式的半导体封装件进行例示的图。

图7A、图7B是对第2实施方式的半导体封装件的制造步骤进行例示的图(其1)。

图8A、图8B是对第2实施方式的半导体封装件的制造步骤进行例示的图(其2)。

图9A、图9B是对第2实施方式的半导体封装件的制造步骤进行例示的图(其3)。

图10A、图10B是对第3实施方式的半导体封装件进行例示的图。

图11A、图11B是对第3实施方式的半导体封装件的制造步骤进行例示的图。

图12A、图12B是对第4实施方式的半导体封装件进行例示的图。

图13A、图13B是对第4实施方式的半导体封装件的制造步骤进行例示的图。

图14A、图14B是对有关切割线设定的变化的例子进行说明的图(其1)。

图15A、图15B是对有关切割线设定的变化的例子进行说明的图(其2)。

图16A、图16B是对有关切割线设定的变化的例子进行说明的图(其3)。

图17A、图17B是对有关切割线设定的变化的其它例子进行说明的图。

图18是对变形例3的半导体封装件进行例示的截面图。

图19是对变形例3的半导体封装件的制造步骤进行例示的图。

符号说明

10、10A、10B、10C、10D半导体封装件

20、200引线框架

21芯片安装部

21a、22a下面

22端子部

22x贯穿槽

30、30A、30B镀膜

40、40B、40C、400、400B、400C盖部

50接合部

60半导体芯片

70金属线

80树脂部

80a侧面

80x沟部

100配线基板

110安装垫(Pad)

150新月形部(Meniscus Part)

210、220、230区域

220x、220y、220z贯穿孔

具体实施方式

下面参照附图对本发明的实施方式进行说明。这里需要说明的是,各图中,相同的构成部分被标注了相同的符号,并且还存在着省略了重复说明的情况。

<第1实施方式>

[第1实施方式的半导体封装件的结构]

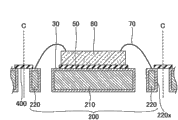

首先,对第1实施方式的半导体封装件的结构进行说明。图1A、图1B是对第1实施方式的半导体封装件进行例示的图,其中,图1A是平面图,图1B是沿图1A的A-A线所截得的截面图。参照图1A、图1B,半导体封装件10大致具有引线框架20、镀膜30、盖部40、接合部50、半导体芯片60、金属线70(键合线)、及树脂部80。这里需要说明的是,为了便于说明,在图1A中,以点状模样示出了盖部40。另外,在图1A中,镀膜30的图示被省略了,树脂部80被示为透明。

引线框架20例如是通过对薄金属板实施压力加工或蚀刻加工等所形成的导电性基材,并具有用于安装半导体芯片的芯片安装部21(晶片垫)、及作为外部连接端子的端子部22(引线)。作为引线框架20的材料,例如可使用铜(Cu)、铜合金、或42合金(Fe和Ni的合金)等。引线框架20的厚度例如可为100~250μm左右。

半导体芯片60介由接合部50在面朝上(Face Up)的状态下被安装在引线框架20的芯片安装部21上。端子部22与芯片安装部21电气独立(电气分离),并且在芯片安装部21的周围以预定的间距被设置了多个(这里需要说明的是,本文中,多个是指2个以上)。但是,端子部22并非一定要设置在芯片安装部21的周围,例如,也可以设置在芯片安装部21的两侧。端子部22的宽度例如可为0.2mm左右。端子部22的间距例如可为0.4mm左右。各端子部22介由金线或铜线等金属线70与半导体芯片60的上面侧所形成的各电极端子(图中未示)电气连接。

在芯片安装部21及端子部22的表面上形成有镀膜30。作为镀膜30,例如可列举出Au膜、Ag膜、Ni/Au膜(将Ni膜和Au膜依次层积了的金属膜)、或Ni/Pd/Au膜(将Ni膜、Pd膜及Au膜依次层积了的金属膜)等。镀膜30的厚度例如可为0.1~数μm左右。

各端子部22的半导体封装件10的外周缘部侧(以下称“各端子部22的外侧面侧”)形成有贯穿槽22x,贯穿槽22x沿厚度方向从一个面(上面)至作为其反对面的另一个面(下面22a)贯穿各端子部22。贯穿槽22x是在与各端子部22的下面22a平行的方向上的截面形状(以下简称为“截面形状”)为近似半圆形的沟。贯穿槽22x的直径例如可为0.1mm左右。但是,贯穿槽22x的截面形状并不限定于近似圆形,也可为近似半椭圆形、近似矩形、或近似多边形等。

各端子部22的上面(半导体芯片60侧的面)的、半导体封装件10的外周缘部侧设置有盖部40,用于对贯穿槽22x的上端部进行堵塞。这里需要说明的是,尽管各贯穿槽22x的内侧面形成了镀膜30,但是各贯穿槽22x的内侧面之外的各端子部22的外侧面却没有形成镀膜30,所以露出了用于构成引线框架20的金属材料。

盖部40是绝缘性板状部件,例如可使用在各端子部22的上面侧形成了黏接层的树脂膜等。作为盖部40,可使用预先将树脂材料成型为具有预定形状的绝缘性板状部件,并且可通过黏接剂将其贴附在各端子部22的上面侧。在半导体封装件10的制造步骤中,盖部40被设置为,在通过树脂部80对半导体芯片60等进行封装时,不让树脂流入最终成为贯穿槽22x的贯穿孔220x内。

作为用于盖部40的树脂,例如可使用热硬化性树脂。具体而言,作为用于盖部40的树脂,例如可列举出环氧树脂、变性环氧树脂、聚酰亚胺(PI)树脂、变性聚酰亚胺树脂等。盖部40的厚度例如可为75~100μm左右。这里需要说明的是,在图1A、图1B的例子中,多个端子部22上分别设置了贯穿槽22x,并且针对每个贯穿槽22x一个一个地设置了盖部40。

引线框架20、盖部40、接合部50、半导体芯片60及金属线70被树脂部80封装。但是,覆盖芯片安装部21的下面21a的镀膜30、覆盖各端子部22的下面22a的镀膜30、覆盖各贯穿槽22x的内侧面的镀膜30、各贯穿槽22x的内侧面之外的各端子部22的外侧面、盖部40的下面的各贯穿槽22x内所露出的区域、及盖部40的半导体封装件10的外周缘部侧的侧面则从树脂部80中露出。覆盖芯片安装部21的下面21a的镀膜30的下面、覆盖各端子部22的下面22a的镀膜30的下面、及树脂部80的下面为大致同面。作为树脂部80,例如可采用使环氧树脂含有了填充物(Filler)的所谓的模制树脂等。

表面被镀膜30所覆盖的各端子部22的下面22a、及表面被镀膜30所覆盖的各贯穿槽22x的内侧面在将半导体封装件10连接至配线基板等时,成为与焊料或导电性糊膏(Paste)等导电材料连接的部分。换言之,表面被镀膜30所覆盖的各端子部22的下面22a、及表面被镀膜30所覆盖的各贯穿槽22x的内侧面形成了新月形部。例如,如图2所示,在将半导体封装件10连接至配线基板100的安装垫110时,由焊料或导电性糊膏等导电材料形成了新月形150。

[第1实施方式的半导体封装件的制造方法]

下面对第1实施方式的半导体封装件的制造方法进行说明。图3A、图3B、图4A、图4B、图5A、图5B是对第1实施方式的半导体封装件的制造步骤进行例示的图。

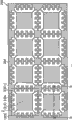

首先,在图3A、图3B(图3A是平面图,图3B是沿图3A的B-B线所截得的截面图)所示的步骤中,形成具有预定形状的引线框架200。之后,在具有预定形状的引线框架200的表面上形成镀膜30。这里需要说明的是,在图3A中,为了便于说明,以点状模样示出了镀膜30。另外,还以括号的形式示出了被镀膜30所覆盖的区域210、220、及230。

引线框架200例如可通过对薄金属板实施压力加工或蚀刻加工等方式所形成。作为引线框架200的材料,例如可使用铜(Cu)、铜合金、或42合金(Fe和Ni的合金)等。引线框架200的厚度例如可为100~250μm左右。

镀膜30例如可通过电解电镀法等形成于引线框架200的表面。作为镀膜30,例如可列举出Au膜、Ag膜、Ni/Au膜(将Ni膜和Au膜依次层积了的金属膜)、或Ni/Pd/Au膜(将Ni膜、Pd膜及Au膜依次层积了的金属膜)等。这里需要说明的是,根据需要,在形成镀膜30之前,还可以对引线框架200的表面实施粗化处理。通过对引线框架200的表面实施粗化处理,可以提高引线框架200的表面和镀膜30间的密着性。

引线框架200具有由虚线所示的切割线所围成的多个区域C(以下称“单个封装区域C”)。引线框架200最终沿虚线所示的切割线被切割,并且,去除虚线所示的切割线内的一部分(例如,用于连接作为各端子部22的各区域的架桥部等),然后按每个单个封装区域C进行个片化,以形成引线框架20。

各单个封装区域C具有最终成为芯片安装部21的区域210、最终成为多个端子部22的多个区域220、及对区域210和220进行支持(连接)的区域230(支持部)。各区域220上形成了沿厚度方向贯穿各区域220的贯穿孔220x。贯穿孔220x的一部分(大约一半)最终成为贯穿槽22x。因为是在将引线框架200加工成预定形状之后再形成镀膜30的,所以各贯穿孔220x的内侧面被镀膜30所覆盖。

这里需要说明的是,在毗邻的单个封装区域C内,区域220之间相连,连接了的区域220上形成有1个贯穿孔220x。贯穿孔220x的一部分(大约一半)最终成为毗邻的一个单个封装区域C的贯穿槽22x,贯穿孔220x的剩余部分(剩余的大约一半)最终成为毗邻的另一个单个封装区域C的贯穿槽22x。贯穿孔220x的截面形状可为近似圆形、近似椭圆形、近似矩形、或近似多边形等。贯穿孔220x为近似圆形时的直径例如可为0.1mm左右。

接下来,在图4A、图4B(图4A是平面图,图4B是沿图4A的B-B线所截得的截面图)所示的步骤中形成盖部400,以对各贯穿孔220x的上端部(在后述步骤中安装半导体芯片60的一侧)进行堵塞。

盖部400是通过被切割最终成为盖部40的绝缘性板状部件,例如可通过在引线框架200的整个上面贴附了形成有黏接层的树脂膜之后,再将不要的部分进行去除的方式而形成。另外,也可以将形成有黏接层的树脂膜预先加工成预定的形状,并且将其贴附在各贯穿孔220x的上面侧,以形成盖部400。或者,还可以采用预先将树脂材料成型为具有预定形状的绝缘性板状部件以取代树脂膜,并且使用黏接剂将其贴附在各贯穿孔220x的上面侧,以形成盖部400。

作为用于盖部400的树脂,优选为可承受在包含后述的图5B所示的步骤中的树脂部80的引线框架200上安装半导体芯片60时的温度,并且可达成引线框架200和树脂部80间的良好密着性的树脂。作为这样的树脂,例如可列举出环氧树脂、变性环氧树脂、聚酰亚胺树脂、及变性聚酰亚胺树脂等。盖部400的厚度例如可为75~100μm左右。盖部400的宽度例如可为贯穿孔220x的最大外形尺寸再加上100μm左右。

接下来,在图5A所示的步骤中,在作为各单个封装区域C的芯片安装部21的区域210上介由接合部50安装半导体芯片60。接合部50例如可通过在各区域210上贴附芯片黏接膜(Die Attach Film)而形成。之后,将半导体芯片60的上面侧所形成的各电极端子(图中未示)介由金属线70与各区域220电气连接。金属线70例如可通过引线键合法(Wire Bonding)与半导体芯片60的各电极端子(图中未示)及各区域220连接。

接下来,在图5B所示的步骤中,在引线框架200上形成树脂部80,以覆盖盖部400、接合部50、半导体芯片60、以及金属线70。作为树脂部80,例如可采用使环氧树脂含有填充物的所谓的模制树脂等。树脂部80例如可通过传递模(Transfer Mold)法或压模(Compression Mold)法等形成。这里需要说明的是,在形成树脂部80之前,如果事先对盖部400的表面实施粗化处理,则有助于提高盖部400和树脂部80间的密着性。

接下来,在图5B所示的步骤之后,去除用于支持(连接)区域210和220的区域230,在各单个封装区域C上形成由芯片安装部21及多个端子部22构成的引线框架20。区域230例如可通过以区域230之外的部分(由芯片安装部21及多个端子部22构成的部分)为掩模(Mask)进行蚀刻的方式而被去除。或者,也可以使用刳刨机(Router)、模具冲压(Punch)、或激光等,以机械方式去除区域230。

之后,沿虚线所示的切割线进行切割,按每个单个封装区域C进行个片化,据此,形成了多个半导体封装件10(参照图1A、图1B)。沿虚线所示的切割线的切割例如可通过切割刀(Dicing Saw)等进行。据此,各端子部22上形成了基于贯穿孔220x的、截面形状为近似半圆形的贯穿槽22x。这里需要说明的是,尽管各贯穿槽22x的内侧面上形成了镀膜30,但是,因为各贯穿槽22x的内侧面之外的各端子部22的外侧面为切割面,所以,其上并没有形成镀膜30,露出了用于构成引线框架20的金属材料。

上面对作为1个产品发货时的半导体封装件10的制造步骤进行了说明,然而,也可以将图4A、图4B所示的结构体(设置了盖部400的引线框架200)作为1个产品进行发货。在这种情况下,获得了作为产品的图4A、图4B所示的结构体的厂家等可执行图5A、图5B之后的步骤,以形成半导体封装件10。

这样,在第1实施方式中,形成了沿厚度方向贯穿引线框架20的各端子部22,并且内侧面被镀膜30所覆盖的贯穿槽22x。据此,在将半导体封装件10实装至基板等时,不仅可对覆盖各端子部22的下面22a的镀膜30,而且还可对覆盖贯穿槽22x的内侧面的镀膜30进行焊料接合。因此,因为可在新月形部上确保具有充足的焊料量,所以可提高半导体封装件10和基板等之间的连接可靠性。

这里需要说明的是,例如尽管也可以采用设置不贯穿端子部22的沟,然后形成覆盖该沟的内侧面的镀膜30的方法,但是,因为可确保形成在新月形部上的焊料量减少了,所以存在着不能充分地获得连接可靠性的问题。如第1实施方式所述,通过设置沿厚度方向贯穿端子部22的贯穿槽22x,并且形成覆盖贯穿槽22x的内侧面的镀膜30,就可以解决上述问题。

另外,即使在镀膜30中包含了金(Au)等高价材料,然而,因为镀膜30是以覆盖贯穿槽22x的内侧面等的方式被形成为极薄,并不是用于填充贯穿槽22x,所以也不会对半导体封装件10的制造成本产生较大的影响。

另外,因为在贯穿槽22x的内侧面等上并没有形成焊料等的容易发生氧化的金属,所以在将半导体封装件10实装至基板等时,可获得良好的焊料接合性。换言之,可确保形成良好的新月形部,并可提高连接可靠性。

另外,因为最终成为贯穿槽22x的贯穿孔220x的上端部被盖部400所覆盖,在使用树脂对半导体芯片60进行封装时,树脂不能流入贯穿孔220x内,所以可使覆盖贯穿孔220x的镀膜30的表面维持良好的状态。换言之,可使覆盖通过切割贯穿孔220x而形成的贯穿槽22x的内侧面的镀膜30的表面维持良好的状态。因此,在将半导体封装件10实装至基板等时,可获得良好的焊料接合性。换言之,可确保形成良好的新月形部,并可提高连接可靠性。

另外,因为在贯穿槽22x的内侧面上确保形成了良好的新月形部,所以通过目视或使用检查设备等,可容易地对焊料的接合状态进行确认。

<第2实施方式>

第2实施方式中示出了具有与第1实施方式不同的结构的半导体封装件的例子。这里需要说明的是,在第2实施方式中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。

[第2实施方式的半导体封装件的结构]

首先,对第2实施方式的半导体封装件的结构进行说明。图6A、图6B是对第2实施方式的半导体封装件进行例示的图,其中,图6A是平面图,图6B是沿图6A的A-A线所截得的截面图。这里需要说明的是,为了便于说明,在图6A中,以点状模样示出了盖部40。另外,在图6A中,镀膜30的图示被省略了,树脂部80被示为透明。

参照图6A、图6B,半导体封装件10A在镀膜30是由镀膜30A及30B所构成的这点上与半导体封装件10(参照图1A、图1B)不同。在引线框架20的上面,设置了盖部40的区域附近之外的区域内形成了镀膜30A。换言之,盖部40被设置在引线框架20的上面的、没有形成镀膜30A的区域上。但是,盖部40的一部分也可形成在镀膜30A上。

另外,在引线框架20的下面(芯片安装部21的下面21a及端子部22的下面22a)及各贯穿槽22x的内侧面上形成了镀膜30B。在引线框架20中,芯片安装部21的侧面及贯穿槽22x的内侧面之外的各端子部22的侧面上并没有形成镀膜30。这里需要说明的是,镀膜30A和镀膜30B也可被形成为一部分互相重叠。引线框架20的下面(芯片安装部21的下面21a及端子部22的下面22a)和树脂部80的下面为大致同面。

[第2实施方式的半导体封装件的制造方法]

下面对第2实施方式的半导体封装件的制造方法进行说明。图7A、图7B、图8A、图8B、图9A、图9B是对第2实施方式的半导体封装件的制造步骤进行例示的图。

首先,在图7A、图7B(图7A是平面图,图7B是沿图7A的B-B线所截得的截面图)所示的步骤中,与第1实施方式的图3A、图3B所示步骤同样地形成具有预定形状的引线框架200,之后,在引线框架200的上面的预定区域D之外的区域上形成镀膜30A。这里需要说明的是,引线框架200的上面之外的部分事先被掩盖(Masking),不形成镀膜30A。

这里,预定区域D是指图8A、图8B所示步骤中设置了盖部400的区域附近的区域。这里需要说明的是,在图7A中,为了便于说明,以点状模样示出了镀膜30A,并且以与镀膜30A不同的点状模样示出了预定区域D。另外,还以括号的形式示出了被镀膜30A所覆盖的区域210、220、及230。

接下来,在图8A、图8B(图8A是平面图,图8B是沿图8A的B-B线所截得的截面图)所示的步骤中,与第1实施方式的图4A、图4B所示步骤同样地形成盖部400,以对各贯穿孔220x的上端部(在后述步骤中安装半导体芯片60的一侧)进行堵塞。但是,盖部400是形成在图7A、图7B所示步骤中没有形成镀膜30A的预定区域D上。

接下来,在图9A所示的步骤中,与第1实施方式的图5A所示步骤同样地,在作为各单个封装区域C的芯片安装部21的区域210上介由接合部50安装半导体芯片60。之后,与第1实施方式的图5B所示步骤同样地,在引线框架200上形成树脂部80,以对盖部400、接合部50、半导体芯片60、及金属线70进行覆盖。在此阶段,各贯穿孔220x的内侧面及引线框架200的下面并没有形成镀膜30A。另外,引线框架200的下面和树脂部80的下面为大致同面。

接下来,在图9B所示的步骤中,与第1实施方式的图3A、图3B所示步骤同样地,在各贯穿孔220x的内侧面及引线框架200的下面上形成镀膜30B。这里需要说明的是,在此步骤中,因为盖部400的一部分触及了镀液,所以,作为盖部400的材料,需要使用可耐镀液腐蚀的材料。但是,作为盖部400,如果使用了上述的环氧树脂或聚酰亚胺树脂等,则没问题。

接下来,在图9B所示的步骤之后,与第1实施方式同样地,对用于支持区域210和220的区域230进行去除,在各单个封装区域C上形成由芯片安装部21及多个端子部22构成的引线框架20。之后,沿虚线所示的切割线进行切割,按每个单个封装区域C进行个片化,这样,就形成了多个半导体封装件10A(参照图6A、图6B)。据此,与第1实施方式同样地,在各端子部22上形成了基于贯穿孔220x的贯穿槽22x。

这样,在设置了用于堵塞各贯穿孔的上端部的盖部之后,也可以在各贯穿孔的内侧面和各端子部的下面形成镀膜。这里需要说明的是,与第1实施方式同样地,也可以将图8A、图8B所示的结构体作为1个产品进行发货。

<第3实施方式>

第3实施方式中示出了具有与第1实施方式不同的结构的半导体封装件的其它例子。这里需要说明的是,在第3实施方式中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。

[第3实施方式的半导体封装件的结构]

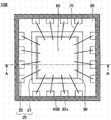

首先,对第3实施方式的半导体封装件的结构进行说明。图10A、图10B是对第3实施方式的半导体封装件进行例示的图,其中,图10A是平面图,图10B是沿图10A的A-A线所截得的截面图。这里需要说明的是,为了便于说明,在图10A中,以点状模样示出了盖部40B。另外,在图10A中,镀膜30的图示被省略了,树脂部80被示为透明。

参照图10A、图10B,半导体封装件10B在盖部40被盖部40B置换了这点上与半导体封装件10(参照图1A、图1B)不同。盖部40B被设置为框状,以在各端子部22的上面(半导体芯片60侧)的、半导体封装件10的外周缘部侧对贯穿槽22x的上端部进行堵塞。

这里需要说明的是,在本实施方式中,各贯穿槽22x的内侧面上形成了镀膜30,各贯穿槽22x的内侧面之外的各端子部22的外侧面上没有形成镀膜30,露出了用于构成引线框架20金属材料,这点与半导体封装件10同样。另外,盖部40B的材料和厚度等也可与盖部40同样。

这里需要说明的是,在图10A、图10B的例子中,以围绕芯片安装部21的方式所配置的多个端子部22上分别设置了贯穿槽22x,针对所有的贯穿槽22x,设置1个平面形状为框状的盖部40B,但是,并不限定与此。针对毗邻的至少2个贯穿槽22x,可设置1个盖部。例如,在平面视图中,可沿半导体封装件10的各边设置细长条状的4个盖部。

[第3实施方式的半导体封装件的制造方法]

下面对第3实施方式的半导体封装件的制造方法进行说明。图11A、图11B是对第3实施方式的半导体封装件的制造步骤进行例示的图。

制造半导体封装件10B时,可执行图11A、图11B所示的步骤以取代第1实施方式的图4A、图4B所示的步骤。即,可在引线框架200的整个上面贴附了形成有黏接层的树脂膜之后,通过去除不要的部分以形成盖部400B。另外,也可以预先将形成有黏接层的树脂膜加工成预定的形状,并且将其贴附在各贯穿孔220x的上面侧,以形成盖部400B。或者,还可以采用预先将树脂材料成型为具有预定形状的绝缘性板状部件以取代树脂膜,并且将其贴附在各贯穿孔220x的上面侧,以形成盖部400B。这里需要说明的是,盖部400B是通过被切割而最终成为盖部40B的部件。

这样,针对毗邻的至少2个的贯穿槽,可设置1个盖部。例如,针对所有的贯穿槽,可设置1个平面形状为框状的盖部。这里需要说明的是,与第1实施方式同样地,可将图11A、图11B所示结构体作为1个产品进行发货。

<第4实施方式>

第4实施方式中示出了具有与第1实施方式不同的结构的半导体封装件的另外的其它例子。这里需要说明的是,在第4实施方式中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。

[第4实施方式的半导体封装件的结构]

首先,对第4实施方式的半导体封装件的结构进行说明。图12A、图12B是对第4实施方式的半导体封装件进行例示的图,其中,图12A是平面图,图12B是沿图12A的A-A线所截得的截面图。这里需要说明的是,为了便于说明,在图12A中,以点状模样示出了盖部40C及接合部50。另外,在图12A中,镀膜30的图示被省略了,树脂部80被示为透明。

参照图12A、图12B,半导体封装件10C在盖部40被盖部40C置换了这点上与半导体封装件10(参照图1A、图1B)不同。与第1实施方式的盖部40同样地,针对每个贯穿槽22x一个一个地设置盖部40C,以在各端子部22的上面(半导体芯片60侧)的、半导体封装件10C的外周缘部侧对贯穿槽22x的上端部进行堵塞。

这里需要说明的是,在本实施方式中,各贯穿槽22x的内侧面上形成了镀膜30,各贯穿槽22x的内侧面之外的各端子部22的外侧面上没有形成镀膜30,露出了用于构成引线框架20的金属材料,这点与半导体封装件10同样。但是,盖部40C通过与接合部50相同的材料被形成为具有与接合部50相同的厚度。

[第4实施方式的半导体封装件的制造方法]

下面对第4实施方式的半导体封装件的制造方法进行说明。图13A、图13B是对第4实施方式的半导体封装件的制造步骤进行例示的图。

制造半导体封装件10C时,可执行图13A、图13B所示的步骤以取代第1实施方式的图4A、图4B所示的步骤。即,可在引线框架200的整个上面贴附了形成有黏接层的树脂膜之后,通过去除不要的部分以在单个封装区域C上形成盖部400C及接合部50。换言之,由相同的树脂膜(例如,芯片黏接膜)形成盖部400C及接合部50。另外,也可以通过预先将形成有黏接层的树脂膜加工成与盖部400C及接合部50相对应的预定的形状,并且将其分别贴附在各贯穿孔220x的上面侧及区域210的上面侧,以形成盖部400C及接合部50。这里需要说明的是,盖部400C是通过被切割而最终成为盖部40C的部件。

这样,可使用相同的材料,并且在相同的步骤中形成盖部和接合部。这里需要说明的是,与第1实施方式同样地,可将图13A、图13B所示的结构体作为1个产品进行发货。

<变形例1>

变形例1中示出了有关切割线设定的变化的例子。这里需要说明的是,在变形例1中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。另外,尽管变形例1是基于第1实施方式而进行说明的,但是,变形例1也可应用于其它实施方式。

在第1实施方式中,引线框架200沿虚线所示的切割线被进行了切割和个片化。如图14A、图14B所示,在变形例1中,图3A、图3B等中C所示的部分(切割线)被设定为宽于第1实施方式(图14A、图14B的切割线E)。具体而言,切割线E的宽度W1被设定为,比用于连接作为各端子部22的各区域的架桥部的宽度W2还宽。这里需要说明的是,因为在毗邻的单个封装区域内确实地形成了贯穿槽22x,所以切割线E最好设定在穿过贯穿孔220x的中心的位置。

在变形例1的半导体封装件的制造步骤中,对图3A、图3B、图4A、图4B、图5A、图5B而言,其与第1实施方式的半导体封装件的制造步骤同样。但是,在图5B所示的步骤之后,在对引线框架200进行个片化时,是沿图14A、图14B所示的切割线E进行切割的。具体而言,使用宽度比切割线E的宽度W1还宽的切割刀(刀刃的厚度(刃厚)较厚),沿切割线E进行切割,以对引线框架200进行个片化。据此,因为在对引线框架200进行个片化的同时,还去除了用于连接作为各端子部22的各区域的架桥部,进而实现了各端子部22的独立化,所以可大幅度地提高半导体封装件的制造步骤的效率。

这里需要说明的是,如果贯穿孔220x的直径小于切割刀的刃厚,则个片化后不会形成贯穿槽22x。所以,贯穿孔220x的直径被设计为大于切割刀的刃厚。另外,如果不将贯穿孔220x的平面形状设计为圆形,而是设计成如图15A、图15B所示的贯穿孔220y那样的、以切割线E的宽度方向为长径的椭圆形,则更有助于确实地形成贯穿槽22x。另外,也可以将贯穿孔220y的平面形状设计为椭圆形之外的纵长形状(例如,以切割线E的宽度方向为长边的长方形等)。

或者,如图16A、图16B所示,在作为端子部22的各区域内设置2个贯穿孔220z,也有助于确实地形成贯穿槽22x。这里需要说明的是,只要能确实地形成贯穿槽22x,贯穿孔220z的平面形状可为圆形、椭圆形或其它形状。另外,在作为端子部22的各区域内,在平面视图上,各贯穿孔220z可设置为互相邻接、互相重复、或互相离开。另外,在作为端子部22的各区域内,也可设置3个以上的贯穿孔220z。

<变形例2>

变形例2中示出了有关切割线设定的变化的其它例子。这里需要说明的是,在变形例2中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。另外,尽管变形例2是基于第1实施方式而进行说明的,变形例2也可应用于其它实施方式。

在第1实施方式中,引线框架200沿虚线所示的切割线被进行了切割和个片化。如图17A、图17B所示,在变形例2中,图3A、图3B等中的C所示的部分(切割线)被切割线F1及F2所置换。切割线F1被设定在用于连接作为各端子部22的各区域的架桥部的外侧,切割线F2被设定在用于连接作为各端子部22的各区域的架桥部的内侧。这里需要说明的是,由切割线F2所围成的区域是单个封装区域。

在变形例2的半导体封装件的制造步骤中,对图3A、图3B、图4A、图4B、图5A、图5B而言,其与第1实施方式的半导体封装件的制造步骤同样。但是,在图5B所示的步骤之后,在对引线框架200进行个片化时,是使用切割刀沿图17A、图17B所示的切割线F1及F2进行切割,以对引线框架200进行个片化的。据此,因为在对引线框架200进行个片化的同时,还去除了用于连接作为各端子部22的各区域的架桥部,进而实现了各端子部22的独立化,所以可大幅度地提高半导体封装件的制造步骤的效率。

这里需要说明的是,如果贯穿孔220x的直径小于切割线F1和切割线F2间的距离(间隔),则个片化后不会形成贯穿槽22x。所以,贯穿孔220x的直径被设计为大于切割线F1和切割线F2间的距离(间隔)。另外,如果形成了如图15A、图15B和图16A、图16B所示形态的贯穿孔,则会更好,这点与变形例1同样。

另外,在引线框架200的外周,也可以不设置2条切割线F1及F2,而是设置1条切割线,以避开用于支持区域220的区域230。例如,在引线框架200的外周,可仅有图17A、图17B的切割线F2的位置处所设置的1条切割线。在这种情况下,引线框架200的外周的贯穿孔220x可形成在例如图17A、图17B的切割线F2的位置处所设置的1条切割线穿过其中心那样的位置处。

另外,沿切割线F1及F2进行切割的切割刀并不是如变形例1所述的刃厚较厚的刀,可使用与第1实施方式同样的刃厚较薄的刀。

<变形例3>

变形例3中示出了树脂部80的形状的变化的例子。这里需要说明的是,在变形例3中,对与已经说明了的实施方式相同的构成部件的说明进行了省略。另外,尽管变形例3是基于第1实施方式而进行说明的,但是变形例3也可应用于其它实施方式。

在第1实施方式中,引线框架200沿虚线所示的切割线被进行了切割和个片化。之后,树脂部80又被形成在了图5B等中的C所示的切割线上。换言之,在对引线框架200进行个片化时,需要对切割线上的树脂部80进行切割。在变形例3中,树脂部80并不是形成在C所示的切割线上。下面参照图18及图19对其进行说明。

图18是对变形例3的半导体封装件进行例示的截面图。参照图18,在半导体封装件10D中,树脂部80的侧面80a为倾斜面,配置在C所示的切割线附近的引线框架20和盖部40从树脂部80中露出。但是,树脂部80的侧面80a并不一定要为倾斜面,例如,可为与盖部40的上面大致垂直的面。

图19是对变形例3的半导体封装件的制造步骤进行例示的图。在制造半导体封装件10D时,首先执行与第1实施方式的图3A、图3B、图4A、图4B、图5A同样的步骤。之后,如图19所示,在引线框架200上形成树脂部80,以覆盖盖部400、接合部50、半导体芯片60、及金属线70。但是,在树脂部80上形成了使C所示的切割线露出的沟部80x。沟部80x例如可通过在传递模法或压模法等中所使用的金型中设置与沟部80x相对应的突起部的方式而形成。

在图19所示的步骤之后,对引线框架200进行个片化,此时,因为C所示的切割线已经在沟部80x内露出来了,所以并不需要对树脂部80进行切割。树脂部80例如采用使环氧树脂含有了填充物的所谓的模制树脂等,然而,在填充物的含有率较高的情况下,如果对树脂部80进行切割,则填充物有可能导致切割刀破损。在变形例3中,因为并不对树脂部80进行切割,所以可排除填充物导致切割刀破损的可能性。

这里需要说明的是,也可以不使C所示的切割线从树脂部80露出,而使覆盖C所示的切割线的树脂部80的厚度薄于覆盖其它部分的树脂部80的厚度。在这种情况下,即使切割刀对树脂部80进行了切割,然而,因为切割部分的树脂部80被事先设计为较薄,所以也可降低填充物导致切割刀破损的可能性。

另外,在变形例3中,因为C所示的切割线在沟部80x内露出来了,所以,在图19所示的步骤中,也可以使用基于压力加工的冲压法对C所示的切割线进行切割。在覆盖C所示的切割线的树脂部80的厚度薄于覆盖其它部分的树脂部80的厚度的情况下,同样地也可以使用基于压力加工的冲压法对C所示的切割线进行切割。

另外,也可以将变形例3与变形例1或2进行组合。

以上对本发明的较佳实施方式及变形例进行了说明,但是,本发明并不限定于上述的实施方式及变形例,只要不脱离权利要求的范围,可以对上述实施方式及变形例进行各种各样的变形、变更或置换。

例如,也可以采用倒装芯片(Flip Chip)实装技术将半导体芯片实装至引线框架。

Claims (10)

1.一种半导体封装件,具有:

引线框架,具有安装半导体芯片的芯片安装部、及作为外部连接端子的端子部;

半导体芯片,安装于所述芯片安装部,并与所述端子部电气连接;

贯穿槽,沿厚度方向从作为所述半导体芯片侧的面的一个面至另一个面贯穿所述端子部;

盖部,对所述端子部的所述一个面侧的所述贯穿槽的端部进行堵塞;及

树脂部,对所述半导体芯片进行封装,使所述端子部的所述另一个面及所述贯穿槽的内侧面露出,

其中,所述端子部的所述另一个面及所述贯穿槽的所述内侧面被镀膜覆盖。

2.根据权利要求1所述的半导体封装件,其中,

具有多个所述端子部,

在多个所述端子部上设置所述贯穿槽,

针对多个所述贯穿槽的每一个,分别设置一个所述盖部。

3.根据权利要求1所述的半导体封装件,其中,

具有多个所述端子部,

在多个所述端子部上设置所述贯穿槽,

针对毗邻的至少2个所述贯穿槽,设置1个所述盖部。

4.一种引线框架,具有被进行切片的多个区域,其中,

所述多个区域的每一个具有:

安装半导体芯片的芯片安装部;

作为外部连接端子的端子部;

对所述芯片安装部和所述端子部进行支撑的支持部;

沿厚度方向从作为安装所述半导体芯片的一侧的面的一个面至另一个面贯穿所述端子部的贯穿孔;及

对所述端子部的所述一个面侧的所述贯穿孔的端部进行堵塞的盖部,

其中,所述贯穿孔被形成为跨越对所述区域进行切片时使用的切割线。

5.根据权利要求4所述的半导体封装件,其中,

所述端子部的所述另一个面及所述贯穿孔的内侧面被镀膜覆盖。

6.根据权利要求4或5所述的半导体封装件,其中,

具有多个所述端子部,

在多个所述端子部上设置所述贯穿孔,

针对多个所述贯穿孔的每一个,分别设置一个所述盖部。

7.根据权利要求4或5所述的半导体封装件,其中,

具有多个所述端子部,

在多个所述端子部上设置所述贯穿孔,

针对毗邻的至少2个所述贯穿孔,设置1个所述盖部。

8.一种半导体封装件的制造方法,具有:

在权利要求4至7的任1项所述的引线框架的所述芯片安装部上安装所述半导体芯片的步骤;

对所述半导体芯片和所述端子部进行电气连接的步骤;

使用树脂对所述半导体芯片进行封装,使所述端子部的被所述镀膜覆盖的所述另一面及所述贯穿孔的所述内侧面露出的步骤;及

沿厚度方向对包含所述贯穿孔的区域进行切割,以在所述端子部上形成内侧面被镀膜覆盖的贯穿槽的步骤。

9.一种引线框架的制造方法,具有:

对金属板进行加工,形成安装半导体芯片的芯片安装部、及作为外部连接端子的端子部的步骤,所述端子部具有沿厚度方向从作为安装所述半导体芯片的一侧的面的一个面贯穿至另一个面的贯穿孔;及

在所述端子部的所述一个面侧设置堵塞所述贯穿孔的端部的盖部的步骤。

10.根据权利要求9所述的引线框架的制造方法,还具有:

在所述端子部的所述另一个面及所述贯穿孔的内侧面形成镀膜的步骤。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012-097053 | 2012-04-20 | ||

| JP2012097053A JP2013225595A (ja) | 2012-04-20 | 2012-04-20 | リードフレーム及び半導体パッケージ並びにそれらの製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN103378045A true CN103378045A (zh) | 2013-10-30 |

Family

ID=49379343

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201310133137XA Pending CN103378045A (zh) | 2012-04-20 | 2013-04-17 | 引线框架、半导体封装件及它们的制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8853841B2 (zh) |

| JP (1) | JP2013225595A (zh) |

| KR (1) | KR20130118781A (zh) |

| CN (1) | CN103378045A (zh) |

| TW (1) | TW201405723A (zh) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107768513A (zh) * | 2016-08-22 | 2018-03-06 | 罗姆股份有限公司 | 半导体器件和半导体器件的安装结构 |

| CN110622304A (zh) * | 2017-06-02 | 2019-12-27 | 株式会社三井高科技 | 引线框架、引线框架的制造方法和半导体装置的制造方法 |

| CN112652583A (zh) * | 2019-10-10 | 2021-04-13 | 珠海格力电器股份有限公司 | 一种封装器件及其生产方法 |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014188632A1 (ja) * | 2013-05-23 | 2014-11-27 | パナソニック株式会社 | 放熱構造を有する半導体装置および半導体装置の積層体 |

| JP6269417B2 (ja) * | 2014-09-26 | 2018-01-31 | 三菱電機株式会社 | 半導体装置 |

| US20160172275A1 (en) * | 2014-12-10 | 2016-06-16 | Stmicroelectronics S.R.L. | Package for a surface-mount semiconductor device and manufacturing method thereof |

| JP6840466B2 (ja) * | 2016-03-08 | 2021-03-10 | 株式会社アムコー・テクノロジー・ジャパン | 半導体パッケージ及び半導体パッケージの製造方法 |

| JP6603169B2 (ja) * | 2016-04-22 | 2019-11-06 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法および半導体装置 |

| JP6800745B2 (ja) * | 2016-12-28 | 2020-12-16 | 株式会社ディスコ | 半導体パッケージの製造方法 |

| JP7037368B2 (ja) * | 2018-01-09 | 2022-03-16 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

| EP3736857A1 (en) * | 2019-05-07 | 2020-11-11 | Nexperia B.V. | Through hole side wettable flank |

| CN111106089B (zh) * | 2019-11-29 | 2021-08-17 | 青岛歌尔微电子研究院有限公司 | 高密度管脚qfn的封装结构与方法 |

| CN111987002A (zh) * | 2020-09-04 | 2020-11-24 | 长电科技(滁州)有限公司 | 一种封装体成型方法 |

| IT202100005759A1 (it) | 2021-03-11 | 2022-09-11 | St Microelectronics Srl | Procedimento per fabbricare dispositivi a semiconduttore e dispositivo a semiconduttore corrispondente |

| KR102514564B1 (ko) * | 2021-06-28 | 2023-03-29 | 해성디에스 주식회사 | 홈이 형성된 리드를 포함하는 리드 프레임 |

| JP7614985B2 (ja) * | 2021-09-08 | 2025-01-16 | Towa株式会社 | 半導体装置の製造方法およびリードフレーム |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002270627A (ja) * | 2001-03-13 | 2002-09-20 | New Japan Radio Co Ltd | 半導体装置の製造方法 |

| JP2004019465A (ja) * | 2002-06-12 | 2004-01-22 | Fuji Heavy Ind Ltd | エンジンの圧縮圧力診断装置 |

| CN1534776A (zh) * | 2003-04-02 | 2004-10-06 | 雅马哈株式会社 | 半导体封装及其引线框架 |

| US20110108965A1 (en) * | 2009-11-12 | 2011-05-12 | Hess Kevin J | Semiconductor device package |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2004082019A1 (ja) * | 2003-03-11 | 2004-09-23 | The Furukawa Electric Co. Ltd. | プリント配線基板、その製造方法、リードフレームパッケージおよび光モジュール |

| JP3915794B2 (ja) * | 2003-04-02 | 2007-05-16 | ヤマハ株式会社 | 半導体パッケージ、その製造方法、および、これに使用するリードフレーム |

| JP2006019465A (ja) * | 2004-07-01 | 2006-01-19 | Mitsui Chemicals Inc | 半導体パッケージおよびその製造方法 |

| JP5546363B2 (ja) * | 2010-06-11 | 2014-07-09 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

-

2012

- 2012-04-20 JP JP2012097053A patent/JP2013225595A/ja active Pending

-

2013

- 2013-04-03 US US13/855,840 patent/US8853841B2/en active Active

- 2013-04-10 TW TW102112628A patent/TW201405723A/zh unknown

- 2013-04-16 KR KR1020130041515A patent/KR20130118781A/ko not_active Application Discontinuation

- 2013-04-17 CN CN201310133137XA patent/CN103378045A/zh active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002270627A (ja) * | 2001-03-13 | 2002-09-20 | New Japan Radio Co Ltd | 半導体装置の製造方法 |

| JP2004019465A (ja) * | 2002-06-12 | 2004-01-22 | Fuji Heavy Ind Ltd | エンジンの圧縮圧力診断装置 |

| CN1534776A (zh) * | 2003-04-02 | 2004-10-06 | 雅马哈株式会社 | 半导体封装及其引线框架 |

| US20110108965A1 (en) * | 2009-11-12 | 2011-05-12 | Hess Kevin J | Semiconductor device package |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN107768513A (zh) * | 2016-08-22 | 2018-03-06 | 罗姆股份有限公司 | 半导体器件和半导体器件的安装结构 |

| CN110622304A (zh) * | 2017-06-02 | 2019-12-27 | 株式会社三井高科技 | 引线框架、引线框架的制造方法和半导体装置的制造方法 |

| CN110622304B (zh) * | 2017-06-02 | 2023-07-14 | 株式会社三井高科技 | 引线框架、引线框架的制造方法和半导体装置的制造方法 |

| CN112652583A (zh) * | 2019-10-10 | 2021-04-13 | 珠海格力电器股份有限公司 | 一种封装器件及其生产方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8853841B2 (en) | 2014-10-07 |

| KR20130118781A (ko) | 2013-10-30 |

| TW201405723A (zh) | 2014-02-01 |

| JP2013225595A (ja) | 2013-10-31 |

| US20130277817A1 (en) | 2013-10-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103378045A (zh) | 引线框架、半导体封装件及它们的制造方法 | |

| JP5634033B2 (ja) | 樹脂封止型半導体装置とその製造方法 | |

| US6674154B2 (en) | Lead frame with multiple rows of external terminals | |

| US6710430B2 (en) | Resin-encapsulated semiconductor device and method for manufacturing the same | |

| KR102054385B1 (ko) | 수지 봉지형 반도체 장치 및 그 제조 방법 | |

| US9779966B2 (en) | Lead frame and semiconductor device | |

| US8115288B2 (en) | Lead frame for semiconductor device | |

| JP2002076228A (ja) | 樹脂封止型半導体装置 | |

| KR102402841B1 (ko) | 리드 프레임, 반도체 장치, 및 리드 프레임의 제조 방법 | |

| KR20050016130A (ko) | 반도체 장치 및 그 제조 방법 | |

| KR20060121823A (ko) | 가역 리드리스 패키지, 및 이를 제조 및 사용하기 위한방법 | |

| KR20150105923A (ko) | 반도체 장치 및 그 제조 방법 | |

| TWI775747B (zh) | 半導體裝置之製造方法及半導體裝置 | |

| US12119263B2 (en) | Methods and apparatus for an improved integrated circuit package | |

| US20200321228A1 (en) | Method of manufacturing a lead frame, method of manufacturing an electronic apparatus, and electronic apparatus | |

| JP6143726B2 (ja) | 樹脂封止型半導体装置とその製造方法、リードフレーム | |

| WO2007018473A1 (en) | Leadframe and semiconductor package | |

| JP2017038051A (ja) | 半導体パッケージ及びその製造方法 | |

| JP5285289B2 (ja) | 回路装置およびその製造方法 | |

| JP4994883B2 (ja) | 樹脂封止型半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Application publication date: 20131030 |

|

| WD01 | Invention patent application deemed withdrawn after publication |