CN100483972C - 用于帧同步的导频序列及帧同步方法和装置 - Google Patents

用于帧同步的导频序列及帧同步方法和装置 Download PDFInfo

- Publication number

- CN100483972C CN100483972C CNB2004100491090A CN200410049109A CN100483972C CN 100483972 C CN100483972 C CN 100483972C CN B2004100491090 A CNB2004100491090 A CN B2004100491090A CN 200410049109 A CN200410049109 A CN 200410049109A CN 100483972 C CN100483972 C CN 100483972C

- Authority

- CN

- China

- Prior art keywords

- pilot

- frame

- code

- sequence

- correlation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0202—Channel estimation

- H04L25/0224—Channel estimation using sounding signals

- H04L25/0226—Channel estimation using sounding signals sounding signals per se

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/7073—Synchronisation aspects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/7073—Synchronisation aspects

- H04B1/7075—Synchronisation aspects with code phase acquisition

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/0202—Channel estimation

- H04L25/0224—Channel estimation using sounding signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L5/00—Arrangements affording multiple use of the transmission path

- H04L5/003—Arrangements for allocating sub-channels of the transmission path

- H04L5/0048—Allocation of pilot signals, i.e. of signals known to the receiver

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W56/00—Synchronisation arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/7073—Synchronisation aspects

- H04B1/7075—Synchronisation aspects with code phase acquisition

- H04B1/70755—Setting of lock conditions, e.g. threshold

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/709—Correlator structure

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/709—Correlator structure

- H04B1/7095—Sliding correlator type

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/69—Spread spectrum techniques

- H04B1/707—Spread spectrum techniques using direct sequence modulation

- H04B1/7097—Interference-related aspects

- H04B1/711—Interference-related aspects the interference being multi-path interference

- H04B1/7115—Constructive combining of multi-path signals, i.e. RAKE receivers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B2201/00—Indexing scheme relating to details of transmission systems not covered by a single group of H04B3/00 - H04B13/00

- H04B2201/69—Orthogonal indexing scheme relating to spread spectrum techniques in general

- H04B2201/707—Orthogonal indexing scheme relating to spread spectrum techniques in general relating to direct sequence modulation

- H04B2201/70701—Orthogonal indexing scheme relating to spread spectrum techniques in general relating to direct sequence modulation featuring pilot assisted reception

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B7/00—Radio transmission systems, i.e. using radiation field

- H04B7/24—Radio transmission systems, i.e. using radiation field for communication between two or more posts

- H04B7/26—Radio transmission systems, i.e. using radiation field for communication between two or more posts at least one of which is mobile

- H04B7/2662—Arrangements for Wireless System Synchronisation

- H04B7/2668—Arrangements for Wireless Code-Division Multiple Access [CDMA] System Synchronisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J13/00—Code division multiplex systems

- H04J13/16—Code allocation

- H04J13/18—Allocation of orthogonal codes

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Power Engineering (AREA)

- Mobile Radio Communication Systems (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Time-Division Multiplex Systems (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Abstract

一种使用最佳导频码型的帧同步方法,包括如下步骤:接收具有根据任意一种码片速率的用于无线电帧的时隙长度(2l+1)的代码序列;对应于无线电帧时隙长度对所接收的代码序列进行排列,并根据该代码序列的接收位置进行自相关,同时,对应于无线电帧时隙长度对代码序列进行排列,并根据代码序列的接收位置进行互相关;以及观察相关的结果,以检测帧同步。

Description

本申请要求于1999年5月28日提交的美国临时申请No.60/136,763的利益,本申请也是于1999年8月13日提交的申请No.的后续申请,其所公开的全文在此引用作为参考。

技术领域

本发明涉及通信系统,具体涉及优选为宽带码分多址(W-CDMA)通信系统的无线通信系统。

背景技术

为便于多个系统通信而使用的几种技术之一是码分多址(CDMA)调制技术。图1简略地图示一个系统10,该系统在用户设备(UE)12a、12b和基站(BTS)14a、14b之间的通信中使用CDMA调制技术,每一用户设备包括一蜂窝电话。基站控制器(BSC)16一般包括用于向BTS 14a、14b提供系统控制的接口和处理电路。BSC 16控制从公用交换电话网(PSTN)到适当BTS的电话呼叫的路由选择以传送给合适的用户设备。BSC 16还控制从用户设备经至少一个BTS到PSTN的呼叫的路由选择。因为用户设备之间一般不直接进行通信,BSC 16可以经合适的BTS在用户设备之间控制呼叫。BSC 16可以通过各种装置,包括专用电话线、光纤链路,或者通过微波通信链路连接到BTS 14a和14b。

箭头13a-13d定义BTS14a和用户设备12a、12b之间可能的通信链路。箭头15a-15d定义BTS 14b和用户设备12a、12b之间可能的通信链路。在反向信道或上行链路上(即从UE到BTS),由BTS 14a和/或BTS 14b接收UE信号,经解调和组合之后,将信号发送给交汇点,一般是BSC 16。在前向信道或下行链路上(即从BTS到UE),由UE 12a和/或UE 12b接收BTS信号。上述系统在美国专利US5,101,501、5,103,390、5,109,390和5,416,797中描述,其所公开的全文在此引用作为参考。

无线电信道本质上是一种通常的敌意介质。很难预知其性能。传统上,用一种统计方法使用实际的传播测量数据模拟无线电信道。通常,根据发射机和接收机之间视线(LOS)情况的存在与否,无线电环境下的信号衰落可以分成大量值路径损耗分量、对数正态分布的中量值慢变化分量和Rician或Rayleigh(瑞利)分布的小量值快变化分量。

图2表示这三种不同的传播现象。可以发现发射机和接收机之间传输路径中的急剧变化,从直接视线变化到由于建筑物、山地或树木导致的严重遮断路径。由于反射、绕建筑物的衍射和折射产生的接收功率随距离下降的现象被称作路径损耗。

如图所示,发射信号由发射机和接收机之间的多种障碍物反射,由此产生一条多径信道。因为时延不同的多个多径之间的干扰,接收信号经受频率选择性多径衰落。例如,当使用2GHz的载频频带和装有一用户设备的汽车以100公里/小时的速度行驶时,衰落的最高多普勒频率是185Hz。虽然相干检测可以用于提高链路容量,在这种快衰落的情况下,一般很难实现用于相关检测的信道估计。由于衰落信道,很难获得用于数据调制信号相干检测的相位基准。因此,最好有一个独立的导频信道。

用于相干检测的信道估计一般从公用导频信道获得。然而,与通过窄波束发射的业务信道信号相比,用全方向性天线发射的公用导频信道经历一条不同的无线电信道。已经注意到,当使用自适应天线时公共控制信道经常在下行链路中出问题。可以通过用户专用导频码元防止此问题,该码元用作信道估计的参考信号。专用导频码元可以被时分或码分复用。

图3表示用于改进信道估计方法所用时分复用导频码元的发射机和接收机的方框图,该发射机和接收机在慢衰落至快衰落的环境下能令人满意地工作。已知导频码元被定期与发射数据序列复用。导频码元和跟随导频码元的数据码元组成一个时隙,如图3所示。

而且,在DS-CDMA发射机中,用一个扩频码调制信息信号,在接收机中,用一个相同的扩频码进行相关。因此,指定用户和干扰用户之间的低互相关性对于抑制多址干扰是很重要。可靠的初始化同步需要优良的自相关性,这是因为自相关函数的大旁瓣可能导致错误的码同步判定。而且,优良的自相关性对于可靠地分离多径分量是重要的。

因为扩频码的自相关函数应当尽可能地类似白噪声的自相关函数,DS码序列也称作伪随机(PN)序列。以这种方式联系自相关和互相关函数不可能同时获得优良的自相关值和互相关值。通过注意具有优良的自相关性也是序列优良随机性的表示,这可以被直观的解释。随机码与确定码相比具有较差的互相关性。

这种移动通信系统已经经历不同的发展阶段,并且各个国家使用不同的标准。八十年代的第一代移动系统为语音业务使用模拟传输。美国的高级移动电话业务(AMPS)、英国的全接入通信系统(TACS)、斯堪的纳维亚的北欧移动电话(NMT)和日本的日本电报电话(NTT)等属于第一代。

在八十年代后期产生使用数字传输的第二代系统。与第一代系统相比,它们提供更高的频谱效率、更好的数据业务和更先进的漫游。欧洲的全球移动通信系统(GSM)、日本的个人数字蜂窝系统(PDC)和美国的IS-95属于第二代。

最近,第三代移动无线电网络已经在热烈地讨论和研究之中,并将在2000年左右形成。在国际电信联盟(ITU)中,第三代网络被称作国际移动电信-2000(IMT-2000),在欧洲,被称作通用移动电信系统(UMTS)。IMT-2000将提供多种业务,包括多媒体和高比特率分组数据。

宽带CDMA已经作为第三代网络的主流空中接口的解决方案出现。目前,宽带CDMA系统由欧洲的欧洲电信标准协会(ESTI)、日本的无线电工业和商业协会(ARIB)、美国的TIA工程委员会TR45和TR46以及T1委员会T1P1和韩国的电信技术协会TTA I和TTA II(分别更名为全球CDMA I和II)进行标准化。可以在Artech House出版社1998年出版的T.Ojanpera等人编著的《第三代移动通信的宽带CDMA》中发现上述各种系统的说明和背景,其全文在此引用作为参考。

最近,日本的ARIB、欧洲的ESTI、美国的T1和韩国的TTA已经根据现有全球移动通信系统(GSM)的核心网络和无线电接入技术制定出第三代移动通信系统,以提供包括多媒体的各种业务,例如音频、视频和数据。他们已经达成协议合作研究以提出发展下一代移动通信系统的技术规范,并将合作研究计划命名为第三代合作计划(3GPP)。

3GPP被划分成三部分的技术研究。第一部分是基于3GPP规范的系统结构和业务性能。第二部分是通用陆地无线电接入网(UTRAN)的研究,该网是应用基于频分双工(FDD)模式的宽带CDMA技术和基于时分双工(TDD)模式的TD-CDMA技术的无线电接入网(RAN)。第三部分是从第二代GSM发展成核心网络的研究,此第二代GSM已经具有第三代网络的性能,例如移动管理和全球漫游。

在3GPP的技术研究中,UTRAN研究定义并指定传输和物理信道。该技术规范,TS S1.11 v1.1.0在1999年3月颁布,其全文在此引用作为参考。此物理信道包括在上行链路和下行链路中使用的专用物理信道(DPCH)。每条DPCH一般提供有三层,例如,超帧、无线电帧和时隙。如3GPP无线电接入网(RAN)标准中所指定的,超帧具有720毫秒周期的最大帧单元。鉴于系统帧数目,一个超帧由七十二个无线电帧组成。每一无线电帧周期为10毫秒,并且一无线电帧包括六十个时隙,根据DPCH每一时隙包括装有相应信息比特的字段。

图4表示基于3GPP RAN标准的一条上行链路DPCH的帧结构。此上行链路DPCH提供有两种信道,例如,一条专用物理数据信道(DPDCH)和一条专用物理控制信道(DPCCH)。上行链路DPDCH适于传送专用数据,而上行链路DPCCH适于传送控制信息。

用于传送控制信息的上行链路DPCCH包括各种字段,例如Npilot比特的导频字段21、NTPC比特的发射功率控制(TPC)字段22、NFBP比特的反馈信息(FBI)字段23和NTFCI比特的可选传送组合标志(TFCI)字段24。导频字段21包括用于支持相干检测所用信道估计的导频比特Npilot。TFCI字段4支持由系统同时提供的多种业务。在上行链路DPCCH中没有TFCI字段4表示相关业务是固定速率业务。参数k确定每一上行链路DPDCH/DPCCH时隙的比特数。它与物理信道扩频因子SF的关系为SF=256/2k。因此扩频因子SF可以从256降到4。

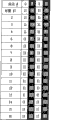

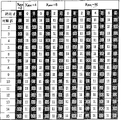

图5是一张表,表示上行链路DPCCH的各种信息,其中信道比特和码元速率是扩频之前的数据。(在该技术规范时,没有确定图4中不同上行链路DPCCH字段(Npilot、NTPc、NFBI和NTFCI)的实际比特数。)

图6是一张表,表示上行链路DPCCH的导频比特码型,更具体地说,是用于每一时隙的6比特和8比特导频比特码型。在图6中,非阴影序列用于信道估计,而阴影序列可以用作帧同步字或序列。除了帧同步字之外的导频比特例如信道估计字的值为1。

例如,在每一时隙包括六个导频比特Npilot=6的情况下,由时隙#1至时隙#16在比特#1、比特#2、比特#4和比特#5上组成的序列用作帧同步字。在每一时隙包括八个导频比特的情况下(Npilot=8),在比特#1、比特#3、比特#5和比特#7上的序列用作帧同步字。在每一序列时隙的导频比特数是6或8的情况下,总共四个比特用作帧同步字。结果,因为一个无线电帧提供有16个时隙,用作帧同步字的导频比特数是每帧64比特。

图7表示一个扩频/扰频装置,用于基于3GPP RAN标准的上行链路DPCH。图7的装置用于执行四相移相键控(QPSK)操作,其中上行链路DPDCH和DPCCH分别被映射成I和Q信道分支。

扩频是通过各自的信道分支将所有码元转换成多个码片的操作。根据两个不同的正交可变扩频因子(OVSF)或信道化编码CD和CC分别在码片速率上扩频I和Q信道分支。OVSF表示在每一信道分支上每码元的码片数。两个信道分支的扩频被加和,然后用一个特定复数扰频码Cscramb复数扰频。复数扰频结果被划分成实部和虚部,然后放在相应载波上之后发射。

图8表示基于3GPP RAN标准的下行链路DPCH的帧结构。上行链路DPCH中的导频比特(或码元)数是6或8,因为上行链路DPCH在16Kbs的固定速率上启动。然而,因为下行链路DPCH在可变速率上启动,它具有图9所示的导频码元码型。

参见图8,类似于上行链路DPCH,下行链路DPCH提供有两种信道,例如,专用物理数据信道(DPDCH)和专用物理控制信道(DPCCH)。在下行链路DPCH上,下行链路DPDCH适合于传送专用数据,而下行链路DPCCH适合于传送控制信息。用于传送控制信息的下行链路DPCCH包括各种字段,例如导频字段27、TPC字段26和TFCI字段25。导频字段27包括用于支持相干检测所用信道估计的导频码元。

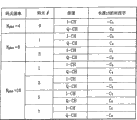

图9是一张表,表示下行链路DPCCH中所包含的导频码元码型,其根据下行链路DPCCH的不同码元速率被分类。例如,在码元速率是16、32、64或128Kbps的情况下,每一时隙包括用于I信道分支的四个导频码元和用于Q信道分支的四个导频码元,总共八个导频码元。

在图9中,非阴影序列用于信道估计,而阴影序列可以用作帧同步字。除了帧同步字之外的其余导频码元(例如信道估计)的值为11。例如,在码元速率是16、32、64或128Kbps的情况下,由从时隙#1到时隙#16,在码元#1和码元#3上的导频码元组成的序列被用作帧同步字。因此,因为每一时隙用作帧同步字的导频码元数是4,在每一无线电帧中使用64个导频码元。

图10表示一个扩频/扰频装置,用于基于3GPP RAN标准的下行链路DPCH。图10的装置用于下行链路DPCH和公共控制物理信道(CCPCH)的扩频和扰频。以下述方式针对两条信道的一对码元执行QPSK操作,即对它们进行串并转换,然后分别映射成I和Q信道分支。

基于两个相同的信道化编码Cch在码片速率上分别扩频I和Q信道分支。两个信道分支的扩频被加和,然后用一个特定复数扰频码Cscramb进行复数扰频。复数扰频结果被分离成实部和虚部,然后分别放在相应载波上之后被发射。显然,在一个蜂窝内同一扰频码用于所有物理信道,而不同的信道化编码用于不同的物理信道。数据和各种控制信息通过上述扩频和扰频后的上行链路和下行链路DPCH被传送给接收机。

TS S1.11 v1.1.0规范还规定了主公共控制物理信道(PCCPCH),它是用于承载广播信道(BCH)的固定速率的下行链路物理信道,和次级公共控制物理信道(SCCPCH),用于在恒定速率上承载前向接入信道(FACH)和寻呼信道(PCH)。图11A和11B表示PCCPCH和SCCPCH的帧结构,每一信道具有一个导频字段。TS S1.11 v1.1.0规范为PCCPCH和SCCPCH推荐了导频码型。而且,TS S1.11 v1.1.0规范推荐了DPCH信道的导频码型和用于PCCPCH和SCCPCH的分集天线导频码型,其中DPCH信道的导频码型用于使用开环天线分集的分集天线,该开环天线分集根据基于时空块编码的发射分集(STTD)。这些码型可以在TS S1.11 v1.1.0规范中发现,省略详细说明。

为了帧同步,必须根据导频码型序列执行自相关函数。在导频序列的设计中,发现对于降低有关同步的误报警的概率,具有最小相位差系数的序列的自相关是很重要的。当没有检测到峰值时检测到一个峰值,可确定一个误报警。

最佳地,对于在指定导频比特上具有一个序列的帧,自相关的结果在一个相关周期的零和中间时移上应当具有相同的最大值,但其极性相反,并且在除零和中间时移之外的时移上其余旁瓣的值为零。然而,在上行链路和下行链路上,TS S1.11 v1.1.0中所推荐的各种导频码型并不符合此要求。

在Young Joon Song等人的标题为“用于数字蜂窝电话的具有双阈值的同步序列设计”的论文(1998年8月18-20日)(本发明人是合著者)中,该论文描述了一种用于GSM编码的相关器电路,其中除了零和中间移位上具有第一峰值和第二峰值之外,异相系数都为零,其中第一和第二峰值极性相反,但峰值相等。而且,该论文描述了最低异相系数+4和-4。然而,此论文并未提供如何使用这种序列和自相关获得上述最佳结果,并且,此论文并未提供足够的公开即该序列实现或可以实现最低自相关旁瓣。

如上所述,用作帧同步字或序列的导频码型并未获得最佳结果。而且,背景导频码型不能快速和正确地执行帧同步。并且,上述导频码型和帧同步序列并不提供最佳互相关和自相关。另外,TS规范和该论文都未提供将导频码型用于逐时隙双检帧同步方案的解决方案,也未公开将帧同步序列用于信道估计。

发明内容

本发明的一个目的是至少解决相关技术中存在的问题和缺点。

本发明的目的之一是提供得到最佳自相关结果的帧同步字。

本发明进一步的目的是消除或防止旁瓣。

本发明进一步的目的是提供零和中间时移上的最大值。

本发明的另一个目的是为至少一个快速和准确帧同步提供同步字。

本发明的另一个目的是提供一种逐时隙双检帧同步方案。

本发明的又一个目的是提供一种可以用于信道估计的帧同步字。

本发明的又一个目的是同时提供优良的互相关性和自相关性。

本发明的一个目的是提供用于当在下一代移动通信系统的上行链路或下行链路物理信道中采用3.8Mcps的码片速率时,用于利用其时隙长度具有最小旁瓣值的最佳导频码型来进行帧同步的数学基础。

本发明的另一个目的是提供一种无需任何修改而利用具有用于无线电帧的时隙长度的最佳导频码型来进行相关处理,使得能够准确进行帧同步的帧同步方法。

本发明的再一个目的是提供一种用于当第三代移动通信系统的上行链路和下行链路中采用3.8Mcps的码片速率时,通过利用具有每无线电帧时隙长度的最佳导频码型来进行相关处理,而根据各自的时隙来精确地确认帧同步的方法。

本发明还有一个目的是提供一种用于利用3GPP无线电接入网标准中所建议的上行链路和下行链路导频码型来实现帧同步的帧同步装置和方法。

通过一种使用最佳导频码元同步帧的方法,可以全部或部分地实现本发明,包括步骤:(1)在通信链路上通过相应物理信道接收帧中每一时隙的导频码元;(2)使每一导频码元的接收位置与相应导频序列相关;(3)组合并加和多个相关结果,并从相关中提取最终结果,其中相关结果的旁瓣被抵销;和(4)使用最终结果同步该帧。

导频码元被组合成每一导频序列,以便最终结果除了相关周期的特定位置之外具有零值旁瓣。特定位置是相关周期(x)的起始点(x=0)和x/整数点。导频码元是以(a,/a)格式的导频码元组合。导频序列在除了相关周期中的起始点和起始点一半之外的位置上提供最小相关合成。在用于检测相关的信道估计中使用除了相关中所用的导频码元之外的导频码元。发送帧中每一时隙的导频码元,和通信链路上各专用信道中专用物理控制信道的导频字段中所包含的导频码元。根据专用物理控制信道的导频字段中所包括的比特值,在相关中使用上行通信链路上各不相同的导频序列。根据专用物理控制信道的码元速率,在相关中使用下行通信链路上各不相同的导频序列。

通过一种使用最佳导频码元同步帧的方法,也可以全部或部分地实现本发明,包括步骤:(1)在通信链路上通过相应物理信道接收帧中每一时隙的导频码元;(2)使每一导频码元的接收位置与相应导频序列相关;(3)组合并求和多个相关结果,并从相关中提取最终结果,其中相关结果的旁瓣具有最小值,并且相关结果在相关周期的起始点和中间点上具有极性不同的最大值;和(4)使用该最终结果同步该帧。

通过一种在基站和移动站之间的通信信道上消除旁瓣的方法,可以全部和部分地实现本发明,包括步骤:生成通信信道中的控制信号和数据信号,控制信号具有L比特的第一序列和L比特的第二序列;根据第一序列生成第一组指定值,第一序列与第一组预定值之间具有第一指定关系;根据第二序列生成第二组指定值,第二序列与第二组指定值之间具有第二指定关系;和组合第一和第二组指定值。

通过一种建立通信信道的方法,可以全部或部分地实现本发明,该方法包括步骤:生成多个帧;为每一帧生成L个时隙,每一时隙具有N比特的导频信号,并且每一时隙中的一个相应比特形成一个导频比特L序列字,所以有N个字,其中从1至L时隙两个相邻字之间比特值相同的两个导频比特数减去从1至L时隙两个相邻字之间比特值不同的两个导频比特数为零或接近于零的一个指定值。

通过一种建立一条具有帧同步或信道估计中至少之一的通信信道的方法,可以全部或部分地实现本发明,该方法包括步骤:生成多个帧;为每一帧生成L个时隙,每一时隙具有N比特的导频信号,并且每一时隙中的一个相应比特形成一个导频比特L序列字,所以有N个字,其中该字具有下述特征的至少之一:帧同步所用的两个相邻序列之间的互相关在零时移上为零,或者帧同步所用的字和帧估计所用的字之间的互相关在所有时移上为零。

通过一种为帧同步降低旁瓣的方法,可以全部或部分地实现本发明,包括步骤:生成多个帧同步字,每个帧同步字具有多个比特;在每对帧同步字上执行自相关函数以生成一对指定值组;并组合该对指定值组以便在零和中间时移上获得幅值相等和极性相反的两个峰值。

通过在具有L个时隙的帧中生成一个指定码型的导频信号的一种方法,可以全部或部分地实现本发明,包括步骤:为每一时隙生成N个导频比特;并根据上述步骤形成N个字,其中指定数目的字被用于帧同步字,并且每一帧同步字具有第一指定数目b0的值为“0”的比特,和第二指定数目b1的值为“1”的比特,以便b1-b0等于零或接近于零的数。

通过包括多个层的用户设备和基站之间的一种通信链路,可以全部或部分地实现本发明,其中一层是物理层,用于建立用户设备和基站之间的通信,并且物理层具有数据和控制信息中的至少之一,一个控制信息是发射L个时隙的N比特的导频字段,所以形成N个L比特的字,其中用于帧同步的两个相邻字之间的互相关在零时移上为零,或者用于帧同步的字和用于信道估计的字之间的互相关在所用时移上为零。

通过用于用户设备和基站至少之一的一种相关器电路,可以全部或部分地实现本发明,包括:多个锁存器电路,每一锁存器电路锁存由来自多个时隙的导频比特形成的字;多个相关器,每一相关器连接到一个相应的锁存器电路,并使该字与一组指定值相关;和一个组合器,组合来自每一相关器的值以便在零和中间时移上形成幅值相等和极性相反的最大峰值。

通过一种通信设备可以全部或部分地实现本发明,包括:用于发送数据和控制信息至少之一的装置;用于接收数据和控制信息至少之一的装置,其中接收装置包括:多个锁存器电路,每一锁存器电路锁存由来自多个时隙的导频比特形成的字;多个相关器,每一相关器连接到一相应的锁存器电路,并使该字与一组指定值相关;多个缓冲器,每一缓冲器连接到一相应的相关器以存储该组指定值;和一个组合器,用于组合来自每一缓冲器的一组值,以便在零和中间时移上形成幅值相等和极性相反的最大峰值。

为了实现本发明的目的,其提供了一种使用最佳导频码型的帧同步方法,其包括如下步骤:接收具有根据任意一种码片速率的用于无线电帧的时隙长度(21+1)的代码序列;对应于无线电帧时隙长度对所接收的代码序列进行排列,并根据该代码序列的接收位置进行自相关,同时,对应于无线电帧时隙长度对代码序列进行排列,并根据该代码序列的接收位置进行互相关;以及观察相关的结果,以检测出帧同步。

根据本发明的一种优选实施例,该种帧同步方法另外包括如下步骤:在完成相关步骤之后,对上述相关结果的至少一个进行组合,并对其进行加和以在检测到该帧同步的延迟时间点之外的延迟时间点上获得互相关值。

进行相关的步骤包括如下子步骤:根据接收位置对所接收代码序列中的第一代码序列和第二代码序列进行第一互相关,并同时,对第二代码序列和被移动预定位长的第一代码序列进行第二互相关。此处,第一互相关的结果与第二互相关的结果具有相同的特性,并且第二代码序列是通过循环移位和倒置第一代码序列而得到的。

检测帧同步的步骤是以如下一种方式来执行的:对应于无线电帧时隙长度对所接收的代码序列进行排列,并单独地观察根据该代码序列接收位置的自相关结果,以检测出帧同步。另外,检测帧同步的步骤可以按照如下的方式进行,即对应于无线电帧时隙长度对所接收的代码序列进行排列,并单独地观察根据该代码序列接收位置的互相关结果,以检测出帧同步。

从自相关结果可以看出,在延迟时间点“0”处具有对应于无线电帧时隙长度的最大相关值,而在延迟时间点“0”之外的其它延迟时间点处则具有最小相关值。根据接收位置对所接收代码序列中的第一代码序列和第二代码序列进行互相关所得的结果,具有与通过先将第一代码序列循环移位1位长度后再将其与第二代码序列进行互相关所得结果相同的特性。

与在将第一代码序列循环移位(1+1)位长的时间点的自相关值相比,来自上述两个相关步骤的结果的极性不同,但幅值相同。来自这两个相关步骤结果的总和,与在将第一代码序列循环移位(1+1)位长的时间点的自相关值相比,其大小是该自相关值的两倍而极性不同。

对其时隙长度为(21+1)的代码序列进行排列,以使相邻代码序列之间的互相关结果在延迟时间点“0”处成为最小值。对其时隙长度为(21+1)的代码序列进行排列,以使每个代码序列的自相关结果在延迟时间点“0”之外的其它延迟时间点处变成最小值。

为了实现上述和其它优点,并根据本文中所实施及广义说明的本发明的目的,其所提供的通过利用基于各单独时隙的相关结果来确认帧同步的方法,包括如下步骤:通过一条通信链路中的各条物理信道,接收其每无线电帧时隙长度根据可选码片速率而定的多个导频序列;对所接收的上述多个导频序列进行排列,以使其与该无线电帧单元的时隙长度相对应,并根据该导频序列的接收位置进行每时隙的相关处理;将计算所得的各个相关结果进行加和,并对所得加和值和预先所确定的一个相关阈值进行比较;以及从比较的结果中确认该无线电帧的同步。

优选地,所接收到的多个导频序列代表了基于其相应接收位置的每个时隙的每个延迟时间点上的相同的相关结果,即,所接收到多个导频序列在延迟时间点“0”处,即τ=0时具有最大的相关值,而所接收的多个导频序列在除了该延迟时间点“0”之外的其它时间点处则具有最小的相关值。该最大和最小相关值彼此具有不同的极性。

根据本发明的一个方面,其提供了一种使用最佳导频码型的帧同步方法,包括如下步骤:在检测上行链路和下行链路信道的帧同步过程中,逐时隙地将所解调和输入的列序列存储到帧单元中;利用从列序列之间关系中所得到的码型特征,根据与每个序列有关的码型特征对所存储的列序列进行变换;逐时隙地加和变换所得的列序列;对加和所得的结果与先前所指定的代码列进行相关处理。

优选地,上述变换步骤包括下述步骤:对单独一个列序列分别进行移位、反转(reversing)和倒置(inverting)操作,以由此产生剩余的列序列。

根据本发明的另一个方面,其提供了一种使用最佳导频码型的帧同步装置,其包括:存储器映射/寻址模块,用于根据所定义的码型特征对逐时隙地输入/解调的列序列进行变换;加法器,用于将来自该存储器映射/寻址模块的变换输出加和在一起;以及相关器,用于对加和结果与先前所指定的代码列进行相关处理。

根据本发明的一种传送用于接收侧的用于帧同步和信道估计中的至少一个的导频码型的方法,所述方法包括:提供包括15时隙的无线电帧,每个时隙包括多个导频比特;将第一代码序列和第二代码序列插入所述无线电帧中,其中,所述第一代码序列是“100011110101100”,所述第一代码序列的每个比特位于每个时隙的相同的导频比特位置,并且其中所述第二代码序列是“101001101110000”,所述第二代码序列的每个比特位于每个时隙的另一个相同的导频比特位置;以及在专用物理控制信道上将所述无线电帧传送到所述接收侧。

根据本发明的一种传送用于接收侧的用于帧同步和信道估计中的至少一个的导频码型的方法,所述方法包括:提供包括15时隙的无线电帧,每个时隙包括多个导频比特;将第一代码序列和第二代码序列插入所述无线电帧中,其中,所述第一代码序列是“110001001101011”,所述第一代码序列的每个比特位于每个时隙的相同的导频比特位置,并且其中所述第二代码序列是“001010000111011”,所述第二代码序列的每个比特位于每个时隙的另一个相同的导频比特位置;以及在专用物理控制信道上将所述无线电帧传送到所述接收侧。

本发明其它的优点、目的和特征中的一部分将在下述说明书中说明,另一部分通过后续审查或通过实施本发明来领会,对于本领域的普通技术人员来说将是显然的。如新附权利要求书所具体指出的,可以实现和获得本发明的目的和优点。

附图说明

将参照下述附图详细说明本发明,在附图中同一参考号表示同一单元:

图1简略地图示一个系统,该系统在用户和基站之间的通信中使用CDMA调制技术;

图2表示这三种不同的传播现象;

图3表示用于时分复用导频码元的发射机和接收机的方框图;

图4表示基于3GPP RAN标准的上行链路DPCH的帧结构;

图5是一张表,表示上行链路DPCCH的各种信息;

图6是一张表,表示上行链路DPCCH的导频比特码型;

图7表示一个基于3GPP RAN标准用于上行链路DPCH的扩频/扰频装置;

图8表示基于3GPP RAN标准的下行链路DPCH的帧结构;

图9是一张表,表示下行链路DPCCH中所包含的导频码元码型;

图10表示基于3GPP RAN标准用于下行链路DPCH的一个扩频/扰频装置;

图11A和11B分别表示PCCPCH和SCCPCH的帧结构;

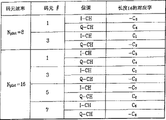

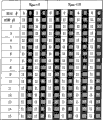

图12A是一张表,表示根据本发明优选实施例的帧同步字C1至Ci-th;

图12B是一张表,表示导频比特序列的自相关函数;

图13A表示两个自相关函数的加和;

图13B表示四个自相关函数的加和;

图14A和14B是表格,表示根据本发明优选实施例用于上行链路DPCCH的导频码型;

图14C是一张表,表示图12A中8个同步字C1-C8和图14A和14B阴影导频比特码型之间的映射关系;

图14D表示根据本发明优选实施例的相关电路,用于基于上行链路DPCCH导频比特的帧同步;

图14E是一张表,表示图14D的点A1-A4上的相关结果和点B上相关结果之和;

图14F是一张表,表示根据本发明优选实施例基于帧同步字的上行链路导频码型的相关结果的各种加和结果;

图14G表示根据一种可选实施例的一个相关器电路,用于基于上行链路DPCCH导频比特序列的帧同步;

图14H表示基站或用户设备的接收机电路,用于恢复在导频字段中包括帧同步字的接收扩频信号;

图14I表示使用此技术规范的导频码型的相关电路结果;

图14J表示图14I结果之和的时移图;

图15A表示用于下行链路DPCH的导频码元码型;

图15B表示图12A的8个帧同步字和图15A阴影导频码元码型之间的映射关系;

图15C表示根据优选实施例的一个相关器电路,用于下行链路DPCCH的帧同步;

图16A表示PCCPCH的导频码元码型;

图16B表示图12A的同步字C1-C8和图16A阴影导频码元码型之间的映射关系;

图16C表示SCCHPCH的导频码元码型;

图16D表示图12A的同步字C1-C8和图16C阴影导频码元码型之间的映射关系;

图17A-17C表示优选实施例的帧同步字和用于DPCH和PCCPCH的当前导频码型(在TS S1.11 v1.1.0规范中所描述的)的自相关函数的加和;

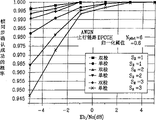

图18A表示在附加高斯白噪声(AWGN)上在上行链路DPCCH和下行链路DPCH上获得的参数PD、PFA和PS;

图18B表示在AWGN信道上在下行链路DPCCH上检测的概率PD;

图18C表示在AWGN信道上在下行链路DPCCH上误报警的概率PFA;

图18D表示在AWGN信道上在下行链路DPCCH上帧同步确认成功检测的概率PS;

图19A表示下行链路DPCH的导频码元码型,用于使用基于时空块编码的发射分集(STTD)的分集天线;

图19B表示图12A的8个字C1-C8和图19Ad的阴影导频码元码型之间的映射关系;

图19C表示用于PCCPCH的分集天线导频码元码型;

图19D表示图12A的字C1-C8和图19C阴影导频码元码型之间的映射关系;

图19E表示当在SCCPCH上使用STTD编码时用于分集天线的导频码元码型;

图19F表示图12A的字C1-C8和图19E阴影导频码元码型之间的映射关系;

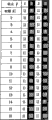

图20A是一张表,表示根据本发明另一优选实施例的帧同步字C1-C16(i=16)和自相关函数;

图20B是一张表,表示在PCSP中分类的每一帧同步字的导频比特的自相关函数;

图20C表示上行链路DPCCH的导频比特码型;

图20D表示图20A的可选帧同步字C1-C16和图20C的阴影帧同步字之间的映射关系;

图20E和20F表示下行链路DPCH的导频码元码型;

图20G表示图20A的可选帧同步字C1-C16和图20E和20F的阴影帧同步字之间的映射关系;

图20H表示下行链路PCCPCH的导频码元码型;

图20I表示图20A的可选帧同步字C1-C16和图20H的阴影帧同步字之间的映射关系;

图21表示用于新的帧同步字C1-Ci-th的一种优选实施例;

图22A表示两个自相关函数的加和;

图22B表示同一类中两个帧同步字之间的两个互相关函数的加和;

图22C表示四个自相关函数的加和;

图22D表示两类的四个帧同步字之间的四个互相关函数的加和;

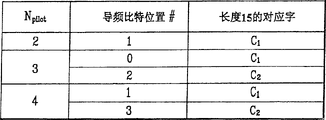

图23A表示Npilot=2、3和4的上行链路DPCCH上的导频比特码型;

图23C表示与图23相比根据一种可选实施例的Npilot=2、3和4的上行链路DPCCH上的导频比特码型;

图23E和23F表示Npilot=5、6、7和8的上行链路DPCCH上的导频比特码型;

图23B和23D分别表示图21的帧同步字和图23A和23D的阴影帧同步字之间的映射关系;

图23G表示图21的帧同步字和图23E和23F的阴影帧同步字之间的映射关系;

图23H表示随机接入信道的结构;

图23I表示随机接入消息控制字段;

图23J表示RACH的导频比特码型;

图24A表示当Npilot=2、4、8和16时下行链路DPCH上的导频码元码型;

图24B表示图21的帧同步字C1-C8和图24A的阴影导频码元码型之间的映射关系;

图24C表示下行链路DPCH的导频码元码型,用于使用STTD的分集天线;

图24D表示图21的帧同步字C1-C8和图24C的阴影导频码元码型之间的映射关系;

图25A表示Npilot=8和16的用于下行链路SCCPCH的导频码元码型;

图25B表示图21的帧同步字C1-C8和图25A的阴影导频码元码型之间的映射关系;

图25C表示Npilot=8和16的下行链路SCCPCH的导频码元码型,用于使用STTD的分集天线;

图25D表示图21的帧同步字C1-C8和图25C的阴影导频码元码型之间的映射关系;

图26A表示用于估计上行链路DPCCH上在AWGN上导频比特码型性能的参数;

图26B表示在Npilot=6的上行链路DPCCH上在AWGN信道上帧同步确认成功的概率PS;

图26C表示在Npilot=6的上行链路DPCCH上在AWGN信道上误报警的概率PFA;

图27是用于15时隙和16时隙的实施例之间的比较图。

图28A是根据3GPP RAN标准的STTD发射机的方框图;

图28B表示基于图28A的STTD发射机的STTD编码;

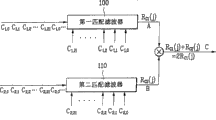

图29A和29B分别显示一种装置和相关结果,用于表示使用根据本发明第一实施例的最佳导频码型的帧同步方法;

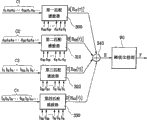

图30A和30B分别显示一种装置和相关结果,用于表示使用根据本发明另一个实施例的最佳导频码型的帧同步方法;

图31显示一种装置,用于表示使用根据本发明另一个实施例的最佳导频码型的帧同步方法;

图32A和32B分别显示一种装置和相关结果,用于表示使用根据本发明另一个实施例的最佳导频码型的帧同步方法;

图33A和33B分别显示一种装置和相关结果,用于表示当码元率在下行链路物理信道中是8Ksps(Npilot=4)时,根据本发明一个实施例的帧同步方法;

图34显示一种装置,用于表示当码元率在下行链路物理信道中

是8Ksps(Npilot=4)时,根据本发明另一个实施例的帧同步方法;

图35A和35B分别显示一种装置和相关结果,用于表示当码元

率在下行链路物理信道中是8Ksps(Npilot=4)时,根据本发明另一个实施例的帧同步方法;

图36A和36B分别显示一种装置和相关结果,用于表示当码元率在下行链路物理信道中是8Ksps(Npilot=4)时,根据本发明另一个实施例的帧同步方法;

图37显示相关结果,用于表示当码元率在下行链路物理信道中是8Ksps(Npilot=4)时,根据本发明另一个实施例的帧同步方法;

图38显示一种一般装置的结构,用于表示使用根据本发明优选实施例的最佳导频码型的帧同步方法;

图39A和39B分别表示装置和相关结果的另一个实施例,其使用一种通过使用每个时隙的相关结果来确认帧同步的方法;

图40A和40B分别表示装置和相关结果的另一个实施例,其使用一种通过使用每个时隙的相关结果来确认帧同步的方法;

图41A和41B表示本发明另一个实施例中的装置和相关结果,其使用一种每个时隙的帧同步确认方法;

图42A和42B表示使用根据本发明优选实施例的导频码型的相关结果的实施例;

图43A和43B表示使用根据本发明优选实施例的导频码型的相关结果的另一个实施例;

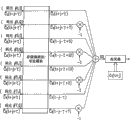

图44表示根据本发明优选实施例用于上行链路信道的相关处理装置;和

图45表示根据本发明优选实施例用于下行链路信道的相关处理装置;

图46表示图45的相关处理装置的相关结果。

具体实施方式

根据本发明优选实施例的新帧同步字使自相关函数的最小相位差值在零和中间移位上具有幅值相等和极性相反的两个峰值。此帧同步字适合于帧同步确认,因为通过简单地加和这些字的自相关函数,可以在零和中间移位上获得幅值相等和极性相反的两个最大相关值。这一性质可以用于双检同步定时并减少同步搜索时间。

根据从网络通知的主CCPCH同步定时、帧偏移组和时隙偏移组,用户设备建立下行链路码片同步和帧同步。可以使用帧同步字确认帧同步。根据帧偏移组和时隙偏移组,网络建立上行链路信道码片同步和帧同步。也可以使用帧同步字确认帧同步。

当在上行链路信道或下行链路信道上使用长扰频码时,使用帧同步字的帧同步确认中的故障总是意味着失去帧和码片同步,因为长扰频码的相位每帧重复一次。在上行链路DPCCH上短扰频码的情况下,帧同步确认中的故障未必总是指失去码片同步,因为短扰频码的长度是256,并且它对应于SF=256的上行链路DPCCH的一个码元周期。因此,导频码型的帧同步字能检测同步状态,并且此信息可以用于层2的RRC连接建立和释放过程。

图12A是一张表,表示根据本发明优选实施例的帧同步字C1至Ci-th,其中每个字包括L个导频比特序列(L>1),这些导频比较来自L个时隙中每一时隙的Npilot比特的指定比特位置(Npilot>0)。在下文描述的第一优选实施例中,同步字数i等于8,时隙数L=16,每一时隙中导频比特数Npilot在4至16之间,但本发明也可以应用于不同的i、L和Npilot。

根据同步字的自相关函数,可以将优选实施例的同步字C1-C8划分成4类(E-H,称作优选相关序列对(PCSP)),如下:

E={C1,C5}

F={C2,C6}

G={C3,C7}

H={C4,C8}

图12B是一张表,表示划分成E、F、G和H类的每一帧同步字的1至16导频比特序列在一个相关周期从时移0到15中的自相关函数。如图12A和12B所示,每类包括两个序列,同类序列具有相同的自相关函数。根据图12B,同步字的自相关函数的最低相位差值在零和中间移位上具有幅值相等和极性相反的两个峰值。而且,自相关函数的结果R1和R2彼此互补。自相关函数之间的关系用下列等式(1)-(4)表示:

RE(τ)=RF(τ)=RG(τ)=RH(τ),τ为偶数 (1)

RE(τ)=-RF(τ),τ为奇数 (2)

RG(τ)=-RH(τ),τ为奇数 (3)

Ri(τ)+Ri(τ+8)=0,i∈{E,F,G,H},对于所有的τ (4)

根据等式(1)、(2)和(3),获得下式:

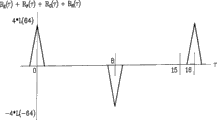

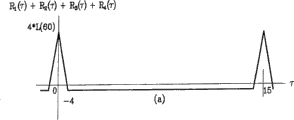

RE(τ)+RF(τ)=RG(τ)+RH(τ),对于所有的τ (5)

两个自相关函数RE(τ)和RF(T)或RG(T)和RH(T)的加和变成在零和中间移位上具有幅值相等和极性相反的两个峰值的函数,并且在除零和中间移位之外的所有值为零,如图13A所示,其中峰值等于2*L或-2*L。在优选实施例中,图13A的峰值是32和-32,因为L=16。诸如(RE(τ)+RG(T))、(RE(T)+RH(T))、(RF(T)+RG(τ))和(RF(τ)+RH(τ))的其它组合并不具有图13A所示的相同值。通过使用帧同步字所导出的性质,获得下述性质:

其中Ri(τ)是序列Ci的自相关函数,1≤i≤8。

在图13B中表示四个自相关函数的加和,除了最大值加倍成4*L或-4*L之外与图13B相同(对于优选实施例此最大值为64和-64),因为通过等式(5)和(6)RE(τ)+RF(τ)+RG(τ)+RH(τ)=2RE(τ)+RF(τ)。此性质允许帧同步定时的双检,并减少同步搜索时间。

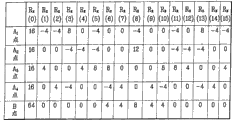

上行链路DPCCH的第一实施例

图14A和14B是表格,表示根据本发明优选实施例用于上行链路DPCCH且Npilot=5,6,7和8的导频码型。图14A和14B的阴影码型用于帧同步(也可以用于信道估计),除帧同步字之外的导频比特(例如信道估计)的值为1。图14C是一张表,表示图12A的8个同步字C1-C8与图14A和14B的阴影导频比特码型之间的映射关系,其中帧同步字C1、C2、C3和C4分别是组{E,F,G和H}的元素。分别使等式(6)中的α=1和2获得图13A和13B的结果,它允许在Npilot=5、6、7和8的上行链路DPCCH上帧同步定时的双检,并减少同步时间。

例如,当Npilot=6时,在自相关处理中将比特#1(C1)、比特#2(C2)、比特#4(C3)和比特#5(C4)上的帧同步字用于帧同步。对于Npilot=8,在自相关处理中将比特#1(C1)、比特#3(C2)、比特#5(C3)和比特#7(C4)上的帧同步字用于帧同步。对于在每一时隙中Npilot=5、6、7和8,总共使用四个帧同步字。结果,因为一个无线电帧具有十六个时隙,在优选实施例中每一帧用于帧同步的导频比特数仅是64。显然,用于帧同步的字数可以根据Npilot的改变而变化。例如,由于该优选实施例的新颖特征,当Npilot=1时,C1-C8中的一个帧同步字可以同时用于帧同步和信道估计。

通过实施新的导频码型,参考图4,每字段比特数的值在下面的表1和表2中显示。表1中给出的信道比特和码元率是即将扩频之前的速率。

表1:DPDCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>data</sub> |

| 16 | 16 | 256 | 160 | 10 | 10 |

| 32 | 32 | 128 | 320 | 20 | 20 |

| 64 | 64 | 64 | 640 | 40 | 40 |

| 128 | 128 | 32 | 1280 | 80 | 80 |

| 256 | 256 | 16 | 2560 | 160 | 160 |

| 512 | 512 | 8 | 5120 | 320 | 320 |

| 1024 | 1024 | 4 | 10240 | 640 | 640 |

有两种类型的上行链路专用物理信道(Uplink Dedicated PhysicalChannels):那些包含TFCI的(例如用于几个同时业务)和那些不包含TFCI的(例如用于固定速率业务)。这些类型由表2中的重复行反映。表2中给出的信道比特和码元率是即将扩频之前的速率。

表2:DPCCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>pilot</sub> | N<sub>TPC</sub> | N<sub>TFCI</sub> | N<sub>FBI</sub> |

| 16 | 16 | 256 | 160 | 10 | 6 | 2 | 2 | 0 |

| 16 | 16 | 256 | 160 | 10 | 8 | 2 | 0 | 0 |

| 16 | 16 | 256 | 160 | 10 | 5 | 2 | 2 | 1 |

| 16 | 16 | 256 | 160 | 10 | 7 | 2 | 0 | 1 |

| 16 | 16 | 256 | 160 | 10 | 6 | 2 | 0 | 2 |

| 16 | 16 | 256 | 160 | 10 | 5 | 1 | 2 | 2 |

图14D表示根据本发明优选实施例的一种相关电路,当使用帧同步字C1-C4时,根据上行链路DPCCH的导频比特进行帧同步。帧同步字C1-C4分别锁存在锁存电路31-34中。相关器41-44分别执行帧同步字C1-C4的相关函数R(x),其中x=0至(L-1),以生成相关结果A1-A4并存储在缓冲器51至53中。

图14E是一张表,表示点A1-A4上的相关结果和点B上的相关结果之和。如图所示,此结果在零和中间时移R(0)和R(8)上具有极性相反的最大值。而且,在点B上加和之后,除了零和中间之外的时移上的其余旁瓣值为零。旁瓣被消除或最小化,B点上的结果对应于图13B的最佳结果。

图14F是一张表,表示根据本发明的优选实施例根据帧同步字C1-C4的上行链路导频码型点A1-A4相关结果的各种加和结果。点(A1+A2)、(A3+A4)、(A1+A4)和(A2+A3)的自相关结果的各个加和呈现与图13A所示最佳结果相同的特征。

图14G表示根据一种可选实施例的相关器电路,根据上行链路DPCCH的导频比特序列进行帧同步。其单元与图14D的相关器电路相同。(C1和C2)、(C2和C3)、(C3和C4)和(C4和C1)的帧同步字被相关并求和以提供D点上的结果。图14G的D点上的求和结果类似于图14D的相关器电路,除了极性相反的最大值分别是2*L(32)和-2*L(32),而不是4*L(64)和-4*L(64)之外,与图14F的结果和图13A的最佳结果相对应。

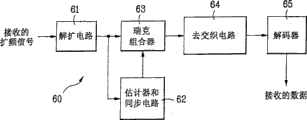

图14H表示基站或用户设备的接收机电路60,用于恢复在导频字段中包括帧同步字的所接收的扩频信号。在由解扩电路61解扩所接收的扩频信号之后,信道估计器和帧同步器62根据导频字段执行信道估计和帧同步。瑞克组合器63使用信道估计器和帧同步器的结果,在瑞克组合之后,由去交织器64以发射机侧的相反顺序去交织数据。此后,数据在解码器65解码得以恢复。

根据先前在TS S1.11 v1.1.0规范中所推荐的帧同步字和用于例如Npilot=6的帧同步字的比较,可以明显看出本发明的优点。应用等式(1)-(6)的相同原理和图14D的相关器电路,可获得图14I的结果用于技术规范中所指的导频码型。当B点上的求和结果被映射在时移图上时,旁瓣的问题是很明显的,如图14J所示。换句话说,在零和中间时移上没有极性相反的最大峰值,并且在除零和中间之外的时移上出现旁瓣。

如背景技术所述,很难同时获得优良的互相关和自相关,其中互相关涉及不同时移上的不同字,自相关涉及时移形式的相同序列。本发明的优良互相关和自相关性基于帧同步字的独特性质。

参见图12、14A和14B,可以很容易看出根据优选实施例的帧同步字的独特性质。如图12的帧同步字C1-C8中所示,每个字的1和0的个数基本相等。换句话说,值为1的帧同步字的导频比特数(b1)减去值为0的帧同步字的导频比特数(b0)等于零或接近于零。在优选实施例中,当有偶数个时隙时,在一个帧同步字中有相同数目的值为1和0的导频比特以便b1-b0为零。显然,当在一个帧同步字中有奇数个导频比特时,b1-b0的结果是±1,例如接近于零。

通过考察一对相邻帧同步字(Npilot=5、6和7的图14A和14B的阴影码型),或一对相邻帧同步字和信道估计字(Npilot=5、6、7和8的图14A和14B的阴影和非阴影码型),可以看出帧同步字的第二个性质。通常,在一对相邻字之间(即,在两个相邻帧同步字之间,或相邻的帧同步字和信道估计字之间)数值相同的比特(0,0和1,1)数目(b3)减去相邻字之间(即,在两个相邻帧同步字之间,或相邻的帧同步字和信道估计字之间)数值不同的比特(1,0或0,1)数目(b4)等于零或接近于零的指定值。

在优选实施例中,两个相邻字之间值相同的导频比特数(b3)等于在两个相邻字之间值不同的导频比特数(b4),即b3-b4=0。在优选实施例中,当Npilot=5时,在比特#0上的C1和比特#1上的C2的两个同步字之间,从时隙#1至时隙#16有相同数目的值相同的导频比特(0,0和1,1)和值不同的导频比特(1,0和0,1),如图14A所示。同样,在比特#1上的同步字C2和比特#2上的信道估计字之间,从时隙#1至时隙#16有相同数目的值相同的导频比特(0,0和1,1)和值不同的导频比特(1,0和0,1)。同样适用于比特#2和比特#3上的两个相邻字之间,和比特#3和比特#4上的两个相邻字之间。上述也适用于Npilot=6、7和8的相邻比特。显然,当使用奇数个时隙时,b3-b4的结果是±1,例如接近于零。

由于此特征,用于帧同步的两个相邻字之间的互相关在零时移上为零(正交)。而且,在用于帧同步的字和用于信道估计的序列之间的互相关在所有时移上为零(正交)。换句话说,在Npilot个L比特的字中,有偶数个用于帧同步的字,但所有的字执行信道估计,其中在用于帧同步的相邻字之间,有基本上为零的互相关。而且,用于帧同步的字与不用于帧同步的字即用于信道估计的字在所有时移上具有基本上为零的互相关。

而且,通过一个自相关函数每Npilot个字对应于一个指定数,以便当组合与用于帧同步的字相对应的来自一组自相关结果的一对时,在零和中间时移上获得峰值相等和极性相反的两个峰值,同时在除了零和中间之外的时移上基本上消除旁瓣。根据本发明的自相关可以被一般定义为一个字和它的时移复制(包括零时移上的复制)之间的相关,其中相关是两个字之间值相同的比特数减去在相同的两个字之间值不同的比特数。而且,如图12B所示,R1和R2彼此互补。

下行链路DPCH的第一实施例

图15A表示Npilot=4、8和16的用于下行链路DPCH的导频码元码型,其中两个导频比特形成一个码元,其中右边的比特用于I信道分支,左边的比特用于Q信道分支。在优选实施例中,Npilot=4可以用于8ksps(千码元每秒);Npilot=8可以用于16、32、64和128 ksps;Npilot=16可以用于256、512和1024 ksps。图15A的阴影码元可以用于帧同步,除了用于帧同步字之外即用于信道估计(信道估计字)的导频码元的值为11。通过为下行链路DPCH对于Npilot=4使等式(6)中的α=1,对于Npilot=8使α=2,对于Npilot=16使α=4,获得图15A的结果。

图15B表示图12A的8个帧同步字和图15A的阴影导频码元码型之间的映射关系。例如,在Npilot=4的优选实施例中,码元#1包括两个帧同步字C1(用于I信道分支I-CH,即从时隙#1到时隙#16左边的比特序列)和C2(用于Q信道分支Q-CH,即从时隙#1到时隙#16右边的比特序列),对于Npilot=8和Npilot=16,在图15B中,对于相应码元,字与信道之间的对应是显然的。与上行链路DPCCH相似,通过使用根据等式(6)的导频码元码型的自相关性,可以实现帧同步定时的逐一时隙双检,并减少帧同步的搜索时间。

因为下行链路DPCH的帧同步字是基于图12A的帧同步字,为上行链路DPCCH所述的特征适用于下行链路DPCH。例如,相邻字之间(即帧同步码元的I信道分支的同步字和Q信道分支的同步字之间,或者相邻的Q信道分支的信道估计字和I信道分支的帧同步字之间,或者相邻的Q信道分支的帧同步字和I信道分支的信道估计字之间)值相同(0,0和1,1)的比特数(b3)减去相邻字之间(即帧同步码元的I信道分支的同步字和Q信道分支的同步字之间,或者相邻的Q信道分支的信道估计字和I信道分支的帧同步字之间,或者相邻的Q信道分支的帧同步字和I信道分支的信道估计字之间)值不同(1,0和0,1)的比特数(b4)等于零或一个接近于零的指定值。

例如,对于Npilot=8,在码元#0和#1之间,比特值为1,1和0,0的一对相邻比特,即来自码元#0的Q信道分支的一个比特和来自码元#1的I信道分支的一个比特的数目与比特值为1,0和0,1的相邻比特的数目相同。换句话说,b3-b4=0。显然,如果时隙数L是一个奇数,b3-b4的结果是±1,例如接近于零的指定值。

通过实施新的导频码元,参考图8,下面的表3显示了各种字段的每时隙比特数目。基本上有两种类型的下行链路专用物理信道(Downlink Dedicated Physical Channel):那些包含TFCI的(例如用于几个同时业务)和那些不包含TFCI的(例如用于固定速率业务)。这些类型由表3中的重复行反映。表3中给出的信道比特和码元率是即将扩频之前的速率。如果没有TFCI,那么TFCI字段被空出(*)。

表3:DPDCH和DPCCH字段

图15C表示根据本发明优选实施例用于Npilot=8的下行链路DPCCH的帧同步的相关电路。其操作和组成与图14D的用于上行链路DPCCH的相关电路相同,除了接收I信道分支和Q信道分支同步字之外。点A1-A4和点B的结果与图14E相同。同样,旁瓣被消除或最小化,此结果对应于图13B的最佳结果。因为用于帧同步的导频码元(或导频比特)数是每时隙两个码元(或每时隙四个比特),共有32个导频码元(或64个导频比特)要在每一无线电帧中用于帧同步。

在下行链路DPCCH中对于Npilot=4,可以使用图14G的相关器电路,在这种情况下,I和Q信道帧同步字被输入相关器电路。求和结果将与图14F相同,该结果对应于图13A的最佳结果。在这种情况下,用于帧同步的导频码元(或导频比特)数是每时隙一个码元(或每时隙两个比特),共16个码元(或32个导频比特)在每一无线电帧中用于帧同步。

在下行链路DPCCH中按Npilot=16,可以扩展图15C的相关器电路以适应导频码元#5和码元#7的I和Q信道分支的附加帧同步字。求和结果类似于图13B的最佳结果,但极性相反的最大峰值将是128(8*L)和-128(8*L)。而且,用于帧同步的导频码元(或导频比特)数是每时隙四个码元(或每时隙八个比特),在每一无线电帧中为帧同步使用64个导频码元(或128个导频比特)。

下行链路PCCPCH和SCCPCH的第一实施例

图16A表示PCCPCH的导频码元码型。阴影码元可用于帧同步,不用于帧同步的导频码元的值是11。图16B表示图12A的同步字C1-C8与图16A的阴影导频码元码型之间的映射关系。通过在公式(6)中取α=1或2,可以获得同步定时的双检帧以及并使同步搜索时间的减少。

图16C表示SCCPCH的导频码元码型。阴影码元可用于帧同步,不用于帧同步的导频码元的值是11。图16D表示图12A的同步字C1-C8与图16C的阴影导频码元码型之间的映射关系。

如上所示,PCCPCH和SCCPCH的帧同步字是基于帧同步字C1-C8,并且对于上行链路DPCCH和下行链路DPCH的公开是适用的。因此,由于本领域技术人员基于上行链路DPCCH和下行链路DPCH很容易理解本发明,此处略去对包括互相关、自相关、操作和执行的各种特性的详细说明。

如上所述,非阴影码元是不用于帧同步的导频码元,其包括值为11的码元,而阴影码元则用于帧同步。导频码型的帧同步字用于帧同步确认,并且需要对用于各个帧同步字的自相关值的加和。帧同步字的自相关值的加和的性质非常重要。

通过实施新的导频码元,参考图11B,表4中给出了每字段比特数目的值。表4中给出的信道比特和码元率是即将扩频之前的速率。

表4:次级CCPCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>data</sub> | N<sub>pilot</sub> | N<sub>TFCI</sub> |

| 32 | 16 | 256 | 320 | 20 | 12 | 8 | 0 |

| 32 | 16 | 256 | 320 | 20 | 10 | 8 | 2 |

| 64 | 32 | 128 | 640 | 40 | 32 | 8 | 0 |

| 64 | 32 | 128 | 640 | 40 | 30 | 8 | 2 |

| 128 | 64 | 64 | 1280 | 80 | 72 | 8 | 0 |

| 128 | 64 | 64 | 1280 | 80 | 64 | 8 | 8 |

| 256 | 128 | 32 | 2560 | 160 | 152 | 8 | 0 |

| 256 | 128 | 32 | 2560 | 160 | 144 | 8 | 8 |

| 512 | 256 | 16 | 5120 | 320 | 304 | 16 | 0 |

| 512 | 256 | 16 | 5120 | 320 | 296 | 16 | 8 |

| 1024 | 512 | 8 | 10240 | 640 | 624 | 16 | 0 |

| 1024 | 512 | 8 | 10240 | 640 | 616 | 16 | 8 |

| 2048 | 1024 | 4 | 20480 | 1280 | 1264 | 16 | 0 |

| 2048 | 1024 | 4 | 20480 | 1280 | 1256 | 16 | 8 |

图17A(Npilot=4),图17B(Npilot=8)和图17C(Npilot=16)中表示用于DPCH和PCCPCH的优选实施例和当前导频码型(其在TSS1.11v1.1.0规范中描述)的帧同步字的自相关函数的加和。如图所示,当前导频码型具有非零相差自相关函数,其峰值在零时移处(zeroshift)。而优选实施例的帧同步字具有零相差自相关函数,其在零和中间时移(延迟)有两个幅值相等极性相反的峰值。

与规定的帧同步字的相关是用于帧同步的最佳方法。由于导频码型的帧同步字被用于帧同步确认,下面的事件和参数被用来评估使用优选实施例和当前导频码型的帧同步字的帧同步确认的性能:

H1事件:当所接收的阴影列帧同步字和其对应接收机存储的帧同步字之间的编码相位偏移是零时,相关器输出超过预定阈值。

H2事件:当所接收的阴影列帧同步字和其对应接收机存储的帧同步字之间的编码相位偏移不是零时,相关器输出超过预定阈值。

H3事件:对于一帧的一个H1事件并且没有H2事件。

H4事件:当所接收的阴影列帧同步字与其对应接收机存储的帧同步字之间的编码相位偏移分别是0或8时,相关器输出超过预定阈值或小于-1×(预定阈值)。

H5事件:当所接收的阴影列帧同步字与其对应接收机存储的帧同步字之间的编码相位偏移不是0和8时,相关器输出超过预定阈值或小于-1×(预定阈值)。

H6:对于一帧的一个H4事件并且没有H5事件。

PD:检测的概率。

PFA:误报警的概率。

PS:用于一帧的帧同步确认成功的概率。

根据以上定义,在当前导频码型被用于帧同步确认时,检测和误报警的概率可以表示为:

PD=Prob(H1) (7)

PFA=Prob(H2) (8)

用于一帧的帧同步确认成功的概率变为PS=Prob(H3),其可表示为:

PS=PD(1-PFA)15 (9)

而在应用优选实施例的帧同步字的情况下,如前所述,双检帧同步需要双阈值,检测和误报警的概率可表示为:

PD=Prob(H4) (10)

PFA=Prob(H5) (11)

类似地,在应用优选实施例的帧同步字的情况下,用于一帧的帧同步确认成功的概率变为PS=Prob(H6),其可表示为:

PS=PD(1-PFA)14 (12)

根据公式(9)和(12),由于PS与PD和(1-PFA)14或(1-PFA)15成比例,帧同步确认的概率在很大程度上受误报警的概率影响。例如,假设PFA=10-1,则(1-PFA)14=0.2288并且(1-PFA)15=0.2059。现在使PFA=10-3,则(1-PFA)14=0.9861并且(1-PFA)15=0.9851。通过选择阈值使得PFA远小于(1-PD),可以充分地评估帧同步的性能。

图18A的参数被用于获得上行链路DPCCH和下行链路DPCH上在附加高斯白噪声(AWGN)上的PD,PFA和PS。图18B表示在下行链路DPCCH上在AWGN信道上的检测概率PD,图18C表示在Npilot=4的下行链路DPCCH上在AWGN信道上的误报警概率PFA,图18D表示优选实施例的导频码型和当前导频码型之间的在Npilot=4的下行链路DPCCH上在AWGN上的帧同步确认成功的概率PS,其中PD,PFA和PS被表示为Eb/No比率的函数(Eb=每比特能量,No=噪声功率谱密度)。

优选实施例的导频码型的PD和PS大于当前导频码型的对应值。此外,根据优选实施例的导频码型的PFA也小于当前导频码型的值。理论公式(9)和(12)与图18D的模拟结果相同。因此,优选实施例的导频码型和当前导频码型的帧同步性能之间有显著差异。例如,从图18D可看出,采用优选实施例的导频码型,在PS=0.93处有3dB的增益。

优选实施例的帧同步字尤其适用于帧同步确认。通过加和阴影帧同步字的自相关函数,得到在零和中间时移处的幅值相等极性相反的双最大值。可以使用这种性质来一个时隙接一个时隙地双检帧同步定时和减少同步搜索时间。在AWGN上使用导频码型的帧同步确认的性能表示出优选实施例的导频码型和当前导频码型的帧同步性能之间的显著差异。

用于STTD分集的下行链路DPCH,PCCPCH和SCCPH的第一实施例

图19A表示用于使用基于发送分集的时空块编码(STTD)的分集天线的下行链路DPCH的新导频码元码型。对于下行链路DPCH上的分集导频码元码型,将STTD应用于Npilot=8的阴影导频码元#1和#3,和Npilot=16的阴影导频码元#1,#3,#5和#7。Npilot=8的非阴影导频码元#0和#2,和Npilot=16的非阴影导频码元#0,#2,#4和#6被编码为与图15A的导频码元正交。但是,由于STTD编码需要两个码元,所以具有Npilot=4的下行链路DPCH的分集导频码型被STTD编码。图19B表示图12A的8个字C1-C8与图19A的阴影导频码元码型之间的映射关系。

图19C表示用于PCCPCH的新分集天线导频码元码型。图19C的导频码元被编码为与图16A的导频码元正交。图19D表示图12A的字C1-C8与图19C的阴影导频码元码型之间的映射关系。

图19E表示当在SCCPCH上使用STTD编码时用于分集天线的新导频码元码型。对于SCCPCH上的分集导频码元码型,STTD被应用于图19E中Npilot=8的阴影导频码元#1和#3,和Npilot=16的阴影导频码元#1,#3,#5和#7。而Npilot=8非阴影导频码元#0和#2,和Npilot=16的非阴影导频码元#0,#2,#4,#6则被编码为与图16C中的导频码元正交。图19F表示图12A的字C1-C8与图19E的阴影导频码元码型之间的映射关系。

由于以上说明是基于字C1-C8的,所以对于前面关于上行链路DPCCH和下行链路DPCH的讨论,PCCPCH和SCCPH是很适用的。本领域技术人员根据前面的公开可以很容易理解使用分集天线的下行链路的特性,在此省略其详细说明。

用于上行链路DPCCH和下行链路DPCH和PCCPCH的可替代实施例

图20A是表示根据本发明另一个优选实施例的帧同步字C1-C16(i=16)和自相关函数的表。帧同步字C1-C16可以被分类为第一实施例的PCSP,表示如下:

E={C1,C3,C9,C11}

F={C2,C4,C10,C12}

G={C5,C7,C13,C15}

H={C6,C8,C14,C16}

该可替代帧同步字C1-C16的分类同样可应用于公式(1)-(6),并且具有与第一实施例相同的性质和特性。图20B是表示分类为PCSP的各个帧同步字的导频比特的自相关函数的表。在该特定情况下,每个类包含4个序列,同一类的序列具有相同的自相关函数。

图20C表示具有Npilot=6和8的上行链路DPCCH的导频比特码型,图20D表示图20A的可替代帧同步字C1-C16与图20C的阴影帧同步字之间的映射关系。图20E和20F表示具有8,16,32,64,128,256,512,1024,2048和4096ksps的下行链路DPCH的导频码元码型,图20G表示图20A的可替代帧同步字C1-C16与图20E和20F的阴影帧同步字之间的映射关系。图20H表示下行链路PCCPCH的导频码元码型,图20I表示图20A的可替代帧同步字C1-C16与图20H的阴影帧同步字之间的映射关系。

由于以上说明是基于与第一实施例的字C1-C8具有相同特征的可替代字C1-C16进行的,对于前面关于上行链路DPCCH和下行链路DPCH的讨论,第一实施例的PCCPCH和SCCPH是很容易适用的。本领域的技术人员根据前面的公开可以容易地理解该实施例的特征,在此省略对其的详细说明。

该优选实施例的帧同步字尤其适用于帧同步确认。通过加和阴影帧同步字的自相关函数,得到在零和中间时移的幅值相等和极性相反的双最大值。该性质可以用于一个时隙接一个时隙地双检帧同步定时和减少同步搜索时间。而且,本发明使接收机的自相关器电路有更简单的结构,从而降低接收机的复杂性。由于本发明的各种优点,第一优选实施例已被3GPP接受(1999年6月分发,如TS 25.211 v2.0.1中所示),其整个内容被包含在此作为参考。

用于L=15的优选实施例

根据本发明优选实施例的上述导频码型具有包括帧同步确认在内的各种优点。在以上优选实施例中,上行链路或下行链路的物理信道具有4.096Mcps的码片速率,这是由于将基于16时隙长度的导频码型用于帧同步的结果。换句话说,码片速率是基于2n的时隙长度。但是,如果码片速率从4.096Mcps改变为3.84Mcps,由于一个无线电帧是基于15时隙的时隙长度,所以需要可替代的导频码型。因此,由于OHG和谐,需要可替代的导频码型用于15时隙(L=15)。

图21表示用于新帧同步字C1-Ci-th的优选实施例,其具有最低相差系数的自相关函数,以及在中间时移处(其中i=8)具有负峰值的互相关函数的最低幅值。这些帧同步字用于设计优选实施例的上行链路DPCCH,下行链路DPCH和SCCPCH的常规导频码型和分集天线导频码型。通过使用该两个相关函数,能够在零和中间时移处双检帧同步。当在AWGN环境中完成了单检和双检帧同步确认的性能评估时,图21的字C1-C8适合于帧同步确认。

帧同步字C1-C8具有下面的二值自相关函数:

其中Ri(T)是帧同步字Ci的自相关函数。与L=16相似,图21的字可以被分为4类,如下所示:

E={C1,C2}

F={C3,C4}

G={C5,C6}

H={C7,C8}

在同一类中的两个字是PCSP。用于优选对{C1,C2},{C3,C4},{C5,C6}或{C7,C8}的互相关频谱是:

其中Ri,j(τ)是E,F,G,H,和i,j=1,2,3,...,8的优选对的两个字之间的互相关函数。通过组合这种自相关函数和互相关函数,可得到下面的公式(16)和(17):

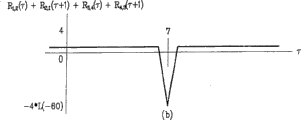

根据公式(16)和(17),当α=2时,图22A表示两个自相关函数的加和,图22B表示在同一类内的两个帧同步字之间的两个互相关函数的加和。类似地,根据公式(16)和(17),当α=4时,图22C表示四个自相关函数,图22D表示两个类E和F的四个帧同步字之间的四个互相关函数的加和。

由于根据该优选实施例的帧同步字C1-C8的自相关函数具有最低的相差系数,通过在图22C的自相关函数输出的(a)处应用正阈值,单检帧同步确认是可行的。此外,通过在图22D的互相关函数输出的(b)处设置负阈值,还可以获得双检帧同步确认。

图23A表示具有Npilot=2,3和4的上行链路DPCCH上的导频比特码型,图23C表示与图23A比较的根据可替代实施例的具有Npilot=2,3和4的上行链路DPCCH的导频比特码型。此外,图23E和23F表示具有Npilot=5,6,7和8的上行链路DPCCH上的导频比特码型。图23A,23C,23E和23F的阴影部分用于帧同步字,除了帧同步字之外的导频比特的值是1。图23B和23D分别表示图21的帧同步字与图23A和23D的阴影帧同步字之间的映射关系。此外,图23G表示图21的帧同步字与图23E和23F的阴影帧同步字之间的映射关系。

上述对于当L=16时的上行链路DPCCH的各种说明可以容易地适用于当L=15时的该优选实施例,包括相关器电路(有一些改动)和一般特性。例如,如图21的帧同步字C1-C8中所示,每个字基本上具有相同数量的1和0。在该优选实施例中,b1-b0的结果是+1或-1,例如接近零。此外,当时隙数是15即奇数时,b3-b4的结果是等于+1或-1,例如接近零。此外,由于两个帧同步字被用于Npilot=2,3和4并且在一个无线电帧中有15个时隙,用于同步的导频比特的数目是每帧30。对于Npilot=5,6,7和8,由于四个帧同步字被用于一个无线电帧中的15个时隙,用于同步的导频比特的数目是每帧60。而且,两个或四个自相关函数和在两个或四个帧同步字之间的互相关函数的加和结果对应于图22A-22D。

通过实施新的导频码型,参考图4,在下面表5和表6中显示了每字段比特数目的值。表5中给出的信道比特和码元率是即将扩频之前的速率。

表5:DPDCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>data</sub> |

| 15 | 15 | 256 | 150 | 10 | 10 |

| 30 | 30 | 128 | 300 | 20 | 20 |

| 60 | 60 | 64 | 600 | 40 | 40 |

| 120 | 120 | 32 | 1200 | 80 | 80 |

| 240 | 240 | 16 | 2400 | 160 | 160 |

| 480 | 480 | 8 | 4800 | 320 | 320 |

| 960 | 960 | 4 | 9600 | 640 | 640 |

有两种类型的上行链路专用物理信道:那些包括TFCI的(例如用于几个同时业务)和那些不包含TFCI的(例如用于固定速率业务)。这些类型由表6中的重复行反映。表6中给出的信道比特和码元率是即将扩频之前的速率。

表6:DPCCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>pilot</sub> | N<sub>TPC</sub> | N<sub>TFCI</sub> | N<sub>FBI</sub> |

| 15 | 15 | 256 | 150 | 10 | 6 | 2 | 2 | 0 |

| 15 | 15 | 256 | 150 | 10 | 8 | 2 | 0 | 0 |

| 15 | 15 | 256 | 150 | 10 | 5 | 2 | 2 | 1 |

| 15 | 15 | 256 | 150 | 10 | 7 | 2 | 0 | 1 |

| 15 | 15 | 256 | 150 | 10 | 6 | 2 | 0 | 2 |

| 15 | 15 | 256 | 150 | 10 | 5 | 1 | 2 | 2 |

随机接入信道(RACH)是用于载带来自UE的控制信息的上行链路传输信道。RACH还可以载带短用户分组。RACH总是从整个蜂窝单元接收的。图23H表示随机接入信道的结构。该10ms消息被分成15时隙,每个时隙长度Tslot=2560码片。每个时隙具有两部分,其中数据部分载带Layer2信息,控制部分载带Layerl控制信息。数据和控制部分被并行发送。

数据部分包括10*2k比特,其中k=0,1,2,3。这分别对应于用于消息数据部分的扩频因子256,128,64和32。控制部分具有8个已知导频比特以支持相干检测的信道估计,以及2比特的速率信息。这对应于用于消息控制部分的扩频因子256。

通过实施新的导频码型,参考图23H,表7中显示了每字段比特数目的值。

表7:随机接入消息数据字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>data</sub> |

| 15 | 15 | 256 | 150 | 10 | 10 |

| 30 | 30 | 128 | 300 | 20 | 20 |

| 60 | 60 | 64 | 600 | 40 | 40 |

| 120 | 120 | 32 | 1200 | 80 | 80 |

图23I表示随机接入消息控制字段,每个时隙总是有8个导频码元用于信道估计。由于根据优选实施例的帧同步字的独特特性,帧同步字C1-C8可以在RACH的导频比特码型中用于信道估计。图23J表示RACH的导频比特码型,以及与图23G中所示用于Npilot=8的映射关系相同的映射关系。由于帧同步字C1-C8的还可以被独自用于信道估计的新特性,很容易复用该导频码型,因此允许不同上行链路信道之间的公共性。

图24A表示当Npilot=2,4,8和16时下行链路DPCH上的导频码元码型。图24A的阴影部分可用于帧同步码元,每个码元具有一个用于I信道分支的帧同步字和另一个用于Q信道分支的帧同步字,除了帧同步字之外的导频码元的值是11。图24B表示图21的帧同步字C1-C8与图24A的阴影导频码元码型之间的映射关系。

图24C表示用于使用STTD的分集天线的下行链路DPCH的导频码元码型。对于下行链路DPCH上的分集导频码元码型,STTD被应用于Npilot=8的阴影导频码元#1和#3,和Npilot=16的码元#1,#3,#5和#7。Npilot=8的非阴影导频码元#0和#2,和Npilot=16的码元#0,#2,#4和#6被编码为与图24A的导频码元正交。但是,由于STTD编码需要两个码元,因此对具有Npilot=4的下行链路DPCH的分集导频码型进行STTD编码。由于STTD编码的导频码元码型与普通导频码元码型正交,STTD编码的导频码型还可以用于反馈模式分集的天线校验。图24D表示图21的帧同步字C1-C8与图24C的阴影导频码元码型之间的映射关系。

通过实施新的导频码型,参考图8,下面的表8中显示了各种字段的每时隙比特数目。基本上有两种类型的下行链路专用物理信道:那些包含TFCI的(例如用于几个同时业务)和那些不包含TFCI的(例如用于固定速率业务)。这些类型由表8的重复行反映。表8中给出的信道比特和码元率是即将扩频之前的速率。如果没有TFCI,那么TFCI字段被空出(*)。

表8:DPDCH和DPCCH字段

图25A表示用于Npilot=8和16的下行链路SCCPCH的导频码元码型,图25B表示图21的帧同步字C1-C8与图25A的阴影导频码元码型之间的映射关系。此外,图25C表示用于使用STTD的分集天线的Npilot=8和16的下行链路SCCPCH的导频码元码型,图25D表示图21的帧同步字C1-C8与图25C的阴影导频码元码型之间的映射关系。

通过实施新的导频码型,参考图11B,表9中给出了每字段比特数目。表9中给出的信道比特和码元率是即将扩频之前的速率。在次级公用控制物理信道(Secondary Common Control Physical Channel)中,有可能具有基于无线电帧单元的突发传输。在进行突发传输时,应将导频码元加到突发串的标题。码元的数目和要附加的导频码元的码元码型将采用时隙#15的码型。

表9:具有导频比特的次级CCPCH字段

| 信道比特速率(kbps) | 信道码元速率(ksps) | SF | 比特/帧 | 比特/时隙 | N<sub>data</sub> | N<sub>pilot</sub> | N<sub>TFCI</sub> |

| 30 | 15 | 256 | 300 | 20 | 12 | 8 | 0 |

| 30 | 15 | 256 | 300 | 20 | 10 | 8 | 2 |

| 60 | 30 | 128 | 600 | 40 | 32 | 8 | 0 |

| 60 | 30 | 128 | 600 | 40 | 30 | 8 | 2 |

| 120 | 60 | 64 | 1200 | 80 | 72 | 8 | 0 |

| 120 | 60 | 64 | 1200 | 80 | 64 | 8 | 8 |

| 240 | 120 | 32 | 2400 | 160 | 152 | 8 | 0 |

| 240 | 120 | 32 | 2400 | 160 | 144 | 8 | 8 |

| 480 | 240 | 16 | 4800 | 320 | 304 | 16 | 0 |

| 480 | 240 | 16 | 4800 | 320 | 296 | 16 | 8 |

| 960 | 480 | 8 | 9600 | 640 | 624 | 16 | 0 |

| 960 | 480 | 8 | 9600 | 640 | 616 | 16 | 8 |

| 1920 | 960 | 4 | 19200 | 1280 | 1264 | 16 | 0 |

| 1920 | 960 | 4 | 19200 | 1280 | 1256 | 16 | 8 |

可以理解,上述当L=16时对于下行链路DPCH的各种说明很容易应用于当L=15时的该优选实施例,包括相关器电路(有一些改动)和一般特性。而且,两个或四个自相关函数和在两个或四个帧同步字之间的互相关函数的加和结果对应于图22A-22D。

为了评估根据优选实施例的用于每帧15时隙的帧同步字的性能,首先定义以下的事件和参数:

H1事件:自相关器输出在零时隙偏移处超过预定阈值。

H2事件:自相关器输出在零时隙偏移处超过预定阈值,或者互相关器输出在7时隙偏移处小于-1×(预定阈值)。

H3事件:自相关器输出在除了零的时隙偏移处超过预定阈值。

H4事件:互相关器输出在除了7的时隙偏移处小于-1×(预定阈值)。

PS:帧同步确认成功的概率。

PFA:误报警的概率。

如果使用帧同步字的相关器的输出超过预定阈值,则确认帧同步。当连续SR帧同步被确认时,可确定帧同步确认的成功。否则,确定出帧同步确认的失败。因此,帧同步确认成功的概率以下式定义:

误报警的概率可以表示为:

PFA=Prob(H3) (19)

=Prob(H4)

图26A的参数被用于评估在AWGN上在上行链路DPCCH上的导频比特码型的性能。图26B表示在AWGN信道上具有Npilot=6的上行链路DPCCH上的帧同步确认成功的概率PS。此外,图26C表示在AWGN信道上具有Npilot=6的上行链路DPCCH上的误报警的概率PFA。PS和PFA被表示为Eb/No的比率的函数(Eb=每比特能量,No=噪声功率谱密度)。

在上行链路DPCCH上SR=3的单检和双检帧同步确认的PS在-5dB分别小于0.945和0.99。此外,与单检方法相比,通过双检方法可以获得大约4dB增益。根据图26C,对于在-5dB归一化阈值=0.6情况下的误报警概率小于2.5×10-4。由于当使用双检帧同步确认方法时在Eb/No=0dB处检测到具有零误报警的完全帧同步确认成功,可以将该导频码型用于帧同步确认。

图27是用于15时隙和16时隙的实施例之间的比较图。除了用于L=16实施例的各种优点之外,根据该优选实施例的用于L=15的导频比特/码元码型还具有附加的优点。通过使用帧同步字的这种性质/特性,可以获得双检帧同步方案。与单检方法相比,采用双检帧同步确认方法可以有约4dB的显著增益。但是,在15时隙的情况下,由于使用了用于正峰值检测的自相关器和用于负峰值检测的互相关器,相关器电路的复杂程度被加倍。

由于15时隙的帧同步字的自相关函数具有最低的异相系数,也可以采用单检帧同步确认方法;而在16时隙的情况下,由于+4或-4的异相系数而存在一些问题。由于当使用双检帧同步确认方法时在上行链路上Eb/No=0dB处检测到具有零误报警的完全帧同步确认成功,15时隙的导频码型非常适用于帧同步确认。由于优选实施例的各种优点,15时隙的导频比特/码元码型也已经被3GPP接受。

下行链路的STTD编码

3GPP RAN在关于下行链路物理信道发送分集的TS s1.11 v1.1.0中对不同下行链路物理信道中的开环发送分集和闭环发送分集的应用有所描述。开环发送分集使用基于空间或时间块编码的STTD编码。如上所述,本发明建议考虑新的使用STTD编码的下行链路导频码型。STTD编码在基站任选使用,并且最好是在用户设备被要求使用。

图28A针对开环发送分集说明了根据3GPP RAN标准的STTD发射机60的方框图。以非分集模式提供给STTD发射机的数据通过用于信道编码的信道编码器61,用于速率匹配的速率匹配器62,和用于交织的交织器63,并由此到第一复用器64。复用器64复用最终交织的数据、TFCI字段、和TPC字段。STTD编码器65把将要通过第一发射天线67和第二发射天线68分别发射的数据码型提供给第二复用器66。换句话说,第二复用器66具有与码元S1和S2正交产生的码元-S2 *和S1 *一起通过QPSK提供至此的码元S1和S2。

图28B说明了根据3GPP RAN标准的STTD发射机60的STTD编码。例如,假设提供给STTD编码器65的QPSK码元在第一码元周期0T是"S1=11",在第二码元周期T2T是"S2=10"。在STTD编码器65产生的与QPSK码元正交的码元在第一码元周期0T是"00",在第二码元周期T2T是"10"。

根据STTD编码产生的码元具有下面的特征。在第一码元周期0T中产生的码元"00"是从在第二码元周期T2T中提供给STTD编码器65的QPSK码元S2转换的码元,在第二码元周期T2T中产生的码元"10"是从在第一码元周期0 T中提供给STTD编码器65的QPSK码元S1转换的码元。

在相应的码元周期中通过根据STTD编码移位、互补和转换处理来产生码元"-S2 *和S1 *"。最后,由于码元"-S2 *和S1 *=00,10"与提供给STTD编码器65的QPSK码元SI和S2=11,10具有相关值“0”,它们彼此正交。

图19A的STTD编码的导频码元码型与图15A的导频码元码型正交,下面参考图28B说明通过将STTD编码原理应用于图15A的导频码元码型产生图19的导频码元码型的方法。

最好以两个码元为单元作为束单元执行STTD编码。换句话说,如果假设两个码元是"S1=A+jB"和"S2=C+jD",利用约束成一个单元的S1和S2执行STTD编码。在这种情况下,"A"和"C"是I信道分支的导频比特,"B"和"C"是Q信道分支的导频比特。"S1S2"的STTD编码产生"-S2 * S1 *"(其中*表示共轭复数)。在编码结束,STTD编码的两个码元将是"-S2 *=-C+jD"和"S1 *=A-jB"。

具体地说,当码元速率是图15A的8ksps(Npilot=4)时,把相应的码元#0和码元#1的"S1=1+j,S2=C1+jC2"STTD编码成码元#0的"-S2 *=-C1+jC2"和码元#1的"S1 *=1-j0"。当码元速率是图15A中的16、32、64或128ksps(Npilot=8)时,把在码元#1和码元#3的"S1=C1+jC2,S2=C3+jC4"STTD编码成图19A的码元#1的"-S2 *=-C3+jC4"和码元#3的"S1 *=C1-jC2"。使图19A中非阴影码元#0和码元#2与图15A中非阴影码元#0和码元#2正交。换句话说,使图15A中的"11","11"成为图19A中的"11","00"。当码元速率是256、512、1024ksps(Npilot=16)时,有四个阴影导频码元。因此,由两个阴影码元,例如图19A的阴影码元#1和码元#3的"S1=C1+jC2,S2=C3+jC4对导频码元进行STTD编码,将其STTD编码成图19A的码元#1的"-S2 *=-C3+jC4"和码元#3的"S1 *=C1-jC2",把图15A的第三和第四阴影码元#5和码元#7的"S1=C5+jC6,S2=C7+jC8"STTD编码成图19A的码元#5的"-S2 *=-C7+jC8"和码元#7的"S1 *=C5-jC6"。图19A的非阴影码元#0、码元#2、码元#4、和码元#6与图15A的非阴影码元#0、码元#2、码元#4、和码元#6正交。就是说,使图15A的"11"、"11"、"11"、"11"成为图19A的"11"、"00"、"11"、"00"。

通过把STTD编码应用于图15A中的导频码元码型产生的图19A的码元具有下面的特征。在图15A中,当码元速率是8ksps(Npilot=4)、16、32、64、或128ksps(Npilot=8)、或256、512、或1024ksps(Npilot=16)时,把阴影列序列分类从最低码元编号开始的四个PCSP′E′、′F′、′G′或′H′,根据优选实施例,列序列以与该分类对应的顺序包括字C1、C2、C3、和C4以及C5、C6、C7、和C8,以便如上所述将每个PCSP表示为E={C1,C5}、F={C2,C6}、G={C3,C7}、和H={C4,C8}。由于图19A的导频码元码型在STTD编码后是图15A中的导频码元码型,当码元速率是256、512、或1024ksps((Npilot=16)时,在将阴影列序列分类从最低码元编号开始的′E′、′F′、′G′或′H′时,按"-C3、C4、C1、和-C2"以及"-C7、C8、C5、-C6"排列列序列。因此,E={-C3,-C7}、F={C4,C8}、G={C1,C5}、和H={-C2,-C6}。比较图15B和19B。

按照非阴影导频码元码型,当每个时隙具有4个导频比特时,把"10"分配给码元#1的所有时隙。当每个时隙具有8个导频比特时,把"11"分配给码元#0的所有时隙,和把"00"分配给码元#2的所有时隙。当每个时隙具有16个导频比特时,把"11"分配给码元#0的所有时隙,把"00"分配给码元#2的所有时隙,把"11"分配给码元#4的所有时隙,和把"00"分配给码元#6的所有时隙。因此,图19A的非阴影码元,即具有"10(Npilot=4比特)","11(Npilot=8比特和Npilot=16比特)",或"00(Npilot=8比特和Npilot=16比特)"的列序列与阴影列序列的互相关对于所有时移"τ"具有"0"值。另外,当一个时隙具有4、8、或16个导频比特时,本发明排列该导频码元码型,以使每个码元编号中I信道分支的字与Q信道分支的字的互相关在时移"τ=0"是"0"。

上述STTD编码很容易应用于16个时隙的下行链路PCCPCH(比较图16A和19C)和下行链路次级CCPCH(比较图16C和19E)。另外,STTD编码很容易应用于15个时隙的下行链路DPCH(比较图24A和24C)和下行链路SCCPCH(比较图25A和25C)。

奇数编号时隙的第一实施例

本发明导致了具有最小旁瓣系数的15个时隙长度的导频码型,并且在码片速率是3.84Mcps而不是4.09Mcps(16个时隙长度)时对上行链路或下行链路的物理信道的帧同步是最佳的。可以根据下面在1=7时包括L=15的21+1(1=1、2、3、4、...)的时隙长度交替说明导频码型的该相关特征。

首先,当把具有最小旁瓣值的序列长度定义为21+1并且具有21+1长度的序列为C1时,C1的自相关值由下面表示:

RC1(j)=(21+1)-4z (4z=0、4、8、16、...) (20)

序列C1的最大自相关值是21+1,并且该自相关值与通过从最大相关值减小4的倍数获得的值相对应。在此,如果1是奇数,例如,1=7,可将1表示为1=2i+1(i=0、1、2、3、...)。因此,可将(20)表示如下

RC1(j)=2(2i+1)+1-4z

=4i+3-4z

=4(i-z+1)-1 (21)

从公式(21)看出,当i-z+1=1(其中z∈1,i∈0)时,序列C1具有最小相关值"-1"。例如,当z=1且i=0,或z=2且i=1时RC1(j)=-1。由于序列C1在"0"的时间点或时移具有最大相关值,因此不考虑z=0的情况。由于除时间点"0"外,最小相关值对应于在旁瓣的相关值,将最小相关值称为最小旁瓣值。如果1是偶数编号,可将1表示为1=2i(i=1、2、3、...)。因此,可将公式(20)表示如下

RC1(j)=2(2i)+1-4z

=4(i-z)+1 (22)

从公式(22)看出,当i-z=0(其中z∈1,i∈1)时,序列C1具有最小相关值"1"。例如,当z=1且i=1,或z=2且i=2时RC1(j)=1。由于序列C1在"0"的时间点具有最大相关值,所以不考虑z=0的情况。从公式(20),(21)和(22)获得由下面的公式(23)和(24)表示的序列C1的自相关特征。

(23)

(24)

可根据代码序列C1通过下面定义具有21+1长度的另一个代码序列C2

C2=-T1+1C1 (25)

其中T表示左循环移位,"-"表示取1的补码的二进制码的倒置。换句话说,通过把代码序列C1的向左循环移位1+1并把循环移位的结果倒置获得C2。C1和C2具有下面的特征:

RC1,C2(j)=RC2,C1(j+1)

=-RC1(j+1+1)

=-RC2(j+1+1) (26)

根据公式(20)至(26)获得下面的结果。

RC1(j)+RC2(j)=2RC1(j) (27)

RC1,.C2(j)+RC2,C1(j+1)=-2RC1(j+1+1) (28)

如果代码序列C1和C2表示公式(23)的自相关特征,当把这些代码序列应用到公式(27)时获得如图29B所示的自相关结果,当把它们应用到公式(28)时获得如图30B所示的自相关结果。结果是,可通过把具有最小旁瓣值和21+1长度的代码序列C1和C2代入公式(27)和(28)来确认帧同步。

图29A和29B分别示出一个装置的结构和相关结果,用于说明使用按照本发明第一实施例的最佳导频码型根据如下面的定义的代码序列C1和C2的帧同步方法。

C1=(C1,0,C1,1,C1,2,...,C1,1,...,C1,21)

C2=(C2,0,C2,1,C2,2,...,C2,1,...,C2,21)

参见图29A,第一匹配滤波器100接收代码序列C1以便进行自相关,从而输出公式(23)或(24)的相关结果。由于序列C1和C2的长度在图29A的结构中不是偶数,第一匹配滤波器100输出公式(23)的自相关结果。第二匹配滤波器110接收代码序列C2并输出公式(25)的自相关结果。将第一和第二匹配滤波器100和110的输出相加以产生图29B所示结果。把该总和与规定的相关阈值(VT)比较,把该总和超过相关阈值的时间(0或21+1)看作是检测到帧同步的时间点。

图30A和30B分别示出一个装置和相关结果,用于说明根据本发明另一个实施例使用最佳导频码型的帧同步方法。图30A的匹配滤波器120和130对输入的代码序列进行互相关。

第三匹配滤波器120接收代码序列C2并利用指定给第三匹配滤波器的代码序列C1的权执行互相关。因此,从第三匹配滤波器120输出公式(26)的结果-RC2(j+1+1)。第四匹配滤波器130接收代码序列C1并利用指定给第四匹配滤波器的代码序列C2的权执行互相关,从而输出公式(26)的结果-RC2(j+1+1)。在此,指定给第四滤波器130的权与通过把代码序列C2向左循环移位1获得的值相对应。

把第三和第四匹配滤波器120和130的输出相加,产生图30B的结果。把该总和与规定的相关阈值(-VT)比较,把该总和小于相关阈值的时间(1)看作是检测到帧同步的时间点。

图31示出根据本发明另一个实施例使用最佳导频码型的帧同步方法的装置。图31的装置是图29A和30B的装置的组合。因此,图31的匹配滤波器100、110、120和130的操作和输出与图29A和30A中的那些相同。由于最大相关结果在′0′和/或"21+1",和"1"的时间点(τ)以彼此相反的极性出现,图31的装置在帧同步检测期间允许双检,而与图29A和30A的装置不同。例如,当1=7和L=15时,该相关结果对应于图22A和22B。

图32A和32B分别示出根据本发明另一个实施例使用最佳导频码型的帧同步方法的装置和相关结果。该装置把根据图31的第一和第二匹配滤波器100和110的自相关结果的总和与根据图31的第三和第四匹配滤波器120和130的互相关结果的总和相加,并使用该加和结果检测帧同步。图32B示出用于检测最终帧同步的最终结果。该结果与图13A中说明的L=16的偶数编号时隙长度相似。因此,与图14D和14G的装置相似(其中的装置也可用于L=15),图29、30A和32A的装置很容易应用于L=16。

在图33A的装置结构中,把最终的加和结果与规定的相关阈值(±VT)进行比较,把该结果比阈值高或低时的时间看作是检测到帧同步的时间点。换句话说,实现了帧同步检测期间的双检。

上面的图21说明了在上行链路或下行链路的物理信道中使用3.84Mcps(L=15个时隙)而不是4.09Mcps的码片速率的情况下用于物理信道中帧同步检测的导频码型。

当把图21的具有15个时隙长度的导频码型的自相关特征应用于公式(23)时,获得下面的公式(29)

RC1(τ)=RC2(τ)=RC3(τ)=RC4(τ)=(15τ=0,-1τ=0) (29)

由于该图的每个代码序列的长度是15,根据15=21+1,1变成7。最大相关值等于′15′。RC1(τ)、RC2(τ)、RC3(τ)、和RC4(τ)对应于代码序列C1、C2、C3和C4的自相关结果。当把代码序列的这些自相关结果组合和相加时,得到下面的公式(30)和(31),公式(30)和(31)分别对应于图22A、22B和22C、22D。

RC1(τ)+RC2(τ)=RC3(τ)+RC4(τ)=(30τ=0,-2τ≠0) (30)

RC1(τ)+RC2(τ)+RC3(τ)+RC4(τ)=(60τ=0,-4τ≠0) (31)

本发明按时隙对具有上述自相关特征的15个时隙长度的代码序列进行自相关或互相关,把相关结果相加,把加和值用于帧同步检测。因此,对于上行链路,可很容易将图29A、30A、31和32的装置应用于L=15,和其它奇数编号的时隙。另外,通过改进本发明也可应用于L=16。

根据上面的公式,产生图23A、23C、23E和23F用于上行链路的导频码型,图23J用于RACH的导频码型,和图24A、24C,25A和25C用于下行链路的导频码型。

把上面作为示例的代码序列C1、C2、C3、C4、C5、C6、C7和C8中的每一个按时隙指定给物理信道的每个比特#或码元#,具有下面的特征。第一,当在相邻比特编号或码元编号的代码序列的互相关结果中延迟时间点是"0"时出现最小相关值。第二,在除在代码序列C1、C2、C3、C4、C5、C6、C7和C8的自相关结果中延迟时间点是′0′外,在旁瓣出现最小相关值。通过循环移位和使C1倒置获得代码序列C2,通过循环移位和使C3倒置获得代码序列C4。其目的是便于在帧同步检测期间使用C1和C2,或C3和C4的互相关结果双检。通过分别循环移位代码序列C1、C2、C3、C4得到代码序列C5、C6、C7和C8。

下面说明在下行链路DPCH中码元速率为8Ksps(Npilot=4)的情况下使用具有15个时隙长度的导频码型检测帧同步的方法。为方便起见基于Npilot=4来说明,但该装置很容易应用于下行链路DPCH、具有STTD的下行链路DPCH、下行链路SCCPCH和具有STTD的下行链路SCCPCH的其它码元速率/导频比特。图33A和33B示出了一种装置和相关结果,作为根据本发明第一实施例的帧同步方法。第一匹配滤波器200接收码元#1的I信道分支的代码序列C1以进行自相关。该输出对应于公式(29)的结果。第二匹配滤波器210接收码元#1的Q信道分支的代码序列C2以进行自相关,并输出与第一匹配滤波器200的输出相同的相关结果。把第一和第二匹配滤波器200和210的输出相加。

同时,第三匹配滤波器220接收码元#1的Q信道分支的代码序列C2以便利用指定给第三匹配滤波器的代码序列C1的权进行互相关。因此,第三匹配滤波器220输出互相关结果,该互相关结果给出在延迟或时移是7的时间点具有负极性的最大相关值′-15′,并给出在除延迟是′7′时之外的延迟时间点的最小相关值′1′。

第四匹配滤波器230接受码元#1的I信道分支的代码序列C1以便利用指定给第四匹配滤波器的代码序列C2的权进行互相关,并输出与第三匹配滤波器220的结果相同的结果。指定给第三匹配滤波器220的权是"C1,14、...、C1,2、C1,1、C1,0",指定给第四匹配滤波器230的权是通过把代码序列C2向左循环移位1得到的"C2,13、...、C2,1、C2,0、C2,14"。把第三和第四匹配滤波器220和230的输出相加,产生图36B的结果。

把根据第一和第二匹配滤波器200和210的自相关结果之和加到根据第三和第四匹配滤波器220和230的互相关结果之和,以便用于帧同步。图33B示出用于最终帧同步检测的结果。在图33A的装置中,把该最终结果与规定的相关阈值(±VT)比较,并把该结果比阈值高或低的时间点看作是检测到帧同步的时间点。换句话说,在帧同步检测期间实现双检。

图34示出在下行链路DPCH中码元速率是8Ksps(Npilot=4)时,使用根据本发明另一个实施例的帧同步方法的装置。在图34的装置结构中,把根据第一和第二匹配滤波器200和210的自相关结果之和与规定的相关阈值(VT)比较,并把该总和比阈值高的时间点看作是检测到帧同步的时间点。此外,把根据第三和第四匹配滤波器220和230的互相关结果之和与规定的相关阈值(-VT)比较,并把该总和比阈值低的时间点看作是检测到帧同步的时间点。

与图33A的装置相同,图34的装置允许在帧同步检测期间双检。图33和34之间区别在于由图34的装置进行的与相关阈值的比较是分开进行。

图35A和35B分别示出在下行链路DPCH中码元速率是8Ksps(Npilot=4)时,使用根据本发明另一个实施例的帧同步方法的装置和相关结果。参见图35A,第一匹配滤波器200接收码元#1的I信道分支的代码序列C1以便进行自相关。其输出对应于上述公式(29)。第二匹配滤波器210接收码元#1的Q信道分支的代码序列C2以便进行自相关,并输出与第一匹配滤波器200的输出相同的相关结果。把第一和第二匹配滤波器200和210的输出相加,产生图35B所示的结果。

图36A和36B分别示出在下行链路DPCH中码元速率是8Ksps(Npilot=4)时,使用根据本发明另一个实施例的帧同步方法的装置和相关结果。第三匹配滤波器220接收码元#1的Q信道分支的代码序列C2以便利用指定给第三匹配滤波器220的代码序列C1的权进行互相关。因此,其输出互相关结果,该互相关结果给出在延迟是′7′的时间点具有负极性的最大相关值′-15′,并给出在除延迟是′7′时之外的延迟时间点的最小相关值′1′。第四匹配滤波器230接收码元#1的I信道分支的代码序列C1以便利用指定给第四匹配滤波器230的代码序列C2的权进行互相关,并输出与第三匹配滤波器220的结果相同的结果。

在此,指定给第三匹配滤波器220的权是"C1,14、...、C1,2、C1,1、C1,0",指定给第四匹配滤波器230的权是通过把代码序列C2向左循环移位1得到的"C2,13、...、C2,1、C2,0、C2,14"。把第三和第四匹配滤波器220和230的输出相加,产生图36B的结果。把总和与规定的相关阈值(-VT)比较,并把该结果比阈值低的时间点看作是检测到帧同步的时间点。

本发明还可允许使用图33A的装置结构在帧同步检测期间双检。在第一种情况下,第一匹配滤波器200的输出(A)和第三匹配滤波器220的输出(D)用于在匹配滤波器200、210、220和230的输入没有任何改变情况下的帧同步检测。在第二种情况下,第一匹配滤波器200的输出(A)和第四匹配滤波器230的输出(E)用于帧同步检测。在第三种情况下,第二匹配滤波器210的输出(B)和第三匹配滤波器220的输出(D)用于检测帧同步。在第四种情况下,第二匹配滤波器210的输出(B)和第四匹配滤波器230的输出(E)用于帧同步检测。图37中示出上面四种情况中使用的相关结果。

图38示出使用根据本发明用于上行链路和下行链路的最佳导频码型的帧同步方法的一般装置。参见图38,相关器100′、110′、120′和130′对输入的代码序列进行相关处理并输出对应的结果。上述匹配滤波器是相关器的一个实例。

根据使用本发明的最佳导频码型的帧同步方法,当在下一代移动通信系统的上行链路或下行链路物理信道中使用基于奇数长度时隙的3.8Mcps的码片速率时,可应用带有21+1的长度具有最小旁瓣值的最佳导频码型,而对帧同步检测没有任何改变。正如可以理解的,可把上面说明的装置应用于其它码片速率和基于偶数编号的时隙,例如L=16的码片速率。通过充分地相关处理具有21+1长度的导频码型可进行准确的帧同步检测。此外,可在帧同步检测中使用双检,导致快速帧同步。这样减少了同步搜索时间。

1.奇数编号时隙的第二实施例

在下面的优选实施例中描述了通过使用基于相应时隙的相关结果确认帧同步的方法。在上行链路或下行链路的物理信道中,在使用3.84Mcps而不是4.096Mcps的码片速率作为16个时隙的长度的情况下,使用最佳导频码型确认帧同步。

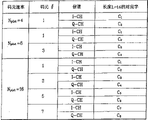

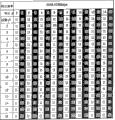

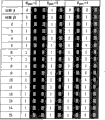

可根据下面表10中所示的相关处理表示图21中所示的15个时隙长度的导频码型。

表10

| 列序列(15时隙长度) |

| C<sub>1</sub>=(a1,a3,a5,....,a29)=(100011110101100) |

| C<sub>2</sub>=(a2,a4,a6,....,a30)=(101001101110000) |

| C<sub>3</sub>=(b1,b3,b5,....,b29)=(110001001101011) |

| C<sub>4</sub>=(b2,b4,b6,....,b30)=(001010000111011) |

| C<sub>5</sub>=(c1,c3,c5,....,c29)=(111010110010001) |

| C<sub>6</sub>=(c2,c4,c6,....,c30)=(110111000010100) |

| C<sub>7</sub>=(d1,d3,d5,....,d29)=(100110101111000) |

| C<sub>8</sub>=(d2,d4,d6,....,d30)=(000011101100101) |

如上所述,表10所示的15个时隙长度的导频码型的重要特征之一是自相关特征。15个时隙长度的导频码型具有下面公式(30)的自相关特征。

RC1(τ)=RC2(τ)=RC3(τ)=RC4(τ)=(15,τ=0

-1,τ≠0) (30)

其中RC1(τ)表示列序列C1的自相关结果,RC2(τ)表示列序列C2的自相关结果,RC3(τ)给出了列序列C3的自相关结果,RC4(τ)提供了列序列C4的自相关结果。

在组合和相加这些相应列序列的相关结果时,将这些结果表示如下:

RC1(τ)+RC2(τ)+RC3(τ)+RC4(τ)=(30,τ=0-2,τ≠0) (31)

RC1(τ)+RC2(τ)+RC3(τ)+RC4(τ)=(60,τ=0-4,τ≠0) (32)

本发明中使用的导频码型的自相关结果在下面全部四种情况中具有相同值:

(1)循环移位一个序列时;

(2)准时转换一个序列,并在此后循环移位时;

(3)把一个序列转换成补码,并在此后循环移位时;和

(4)准时转换一个序列,此后转换成补码,然后循环移位时。

在本发明的一个优选实施例中,由每个时隙相关处理15个时隙长度的列序列或字,并把相关结果相加。此后,把相加的结果与相关阈值VT比较,通过检验比较结果确认帧同步。

下面的表11给出了15个时隙长度的每个延迟时间点或时移的相关结果。

表11

| τ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| R(τ) | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

如表11所示,在利用15个时隙长度的导频码型进行相关处理的过程中,可在′τ=0′的时间点获得最大相关值15,在旁瓣获得相关值-1。此刻,使用相关阈值VT以便提高帧同步检测的效率。换句话说,认为仅当15个时隙长度的序列的自相关结果大于相关阈值时是获得帧同步的检测时间点。

根据表10,可分别根据表12和13为上行链路DPCH构成图23E和23F的导频码型。该构成也很容易应用于上面针对L=15描述的所有上行链路、RACH和下行链路导频码型。

表12

表13

图39A和39B分别描绘了根据本发明另一个实施例使用利用了每个时隙的相关结果的帧同步确认方法的装置和相关结果。

表14描述了在使用表10所示的15个时隙长度的序列的过程中,在图39A所示的匹配滤波器100的输出A表示的自相关结果[RC(τ)],和阈值比较器90的输出B。

表14

| τ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 时隙# | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| A点 | 15 | 1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| B点 | H | L | L | L | L | L | L | L | L | L | L | L | L | L | L |

如图39B所示,在利用15个时隙长度的导频码型进行相关处理的情况下,在′τ=0′的时间点可获得最大相关值′15′,和在旁瓣获得最小相关值-1。把相关阈值VT设定成比最大相关值′15′小的值,并根据每个延迟时间点τ,认为在来自匹配滤波器100的相关结果[RC(τ)]大于相关阈值时是帧同步检测时间点。

如果在该情况下出现了超过′VT+1′的噪声,在帧同步中出现了错误检测。从相关阈值与旁瓣相关值之间的关系决定帧同步中这种错误检测的概率。

在表13中,在图39A的装置中表示阈值比较器90根据延迟变量τ的输出。在阈值比较器90中将预定阈值VT与匹配滤波器100的输出比较的过程中,把超过阈值VT的输出表示为′H′,和把阈值VT以下的输出表示为′L′

在图39A所示的装置中,通过根据各个时隙针对序列C1、C2、C3和C4中的任何一个在相关结果中检验阈值比较器90的输出可确认帧同步。

图40A和40B说明在本发明的另一个实施例中按每个时隙使用帧同步确认方法的装置和相关结果。表15提供了在使用表10的15个时隙长度的序列的过程中,图40A的匹配滤波器200和210的输出A和B的相关值[RC1(τ)]和[RC2(τ)]。

表15说明了通过用加法器220把第一匹配滤波器200的输出A[RC1(τ)]和第二匹配滤波器210的输出B[RC2(τ)]相加获得的在输出C的相关值,并说明了作为把输出C的相关值[RC1(τ)]+[RC2(τ)]与预定相关阈值比较的结果获得的在阈值比较器90的输出D。

表15

| τ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 时隙# | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| A点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| B点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| C点 | 30 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 | -2 |

| D点 | H | L | L | L | L | L | L | L | L | L | L | L | L | L | L |

如图40B所示,在利用15个时隙长度的导频码型进行相关处理,然后把两个相关结果相加的情况下,可在′τ=0′的时间点获得最大相关值′30′,在旁瓣获得最小相关值-2。此刻,相关阈值VT是小于最大相关值′30′的值,并认为来自匹配滤波器200和210的,基于每个延迟时间点的相关结果的加和值[RC1(T)]+[RC2(τ)]大于相关阈值时的时间点是帧同步检测时间点。

如果在该情况下出现了超过′VT+2′的噪声,在帧同步中出现了错误检测。从相关阈值与旁瓣相关值之间的关系决定帧同步中这种错误检测的概率。

在表15中,在图40A所示的装置中表示阈值比较器90根据延迟变量τ的输出D。在把匹配滤波器200和210的输出相加并在阈值比较器40B中将预定阈值VT与该加和值[RC1(T)]+[RC2(τ)]比较的过程中,把超过阈值VT的加和值表示为′H′,和把阈值VT以下的加和值表示为′L′

在图40A的装置中,通过每个时隙地针对序列,即针对C1、C2、C3和C4组合多于一个相关结果,和从组合结果检验阈值比较器90的输出可确认帧同步。

图41A和41B说明了在本发明的另一个实施例中按每个时隙使用帧同步确认方法的装置和相关结果。

表16提供了在使用表10所示的15个时隙长度的序列的过程中,图40A所示的匹配滤波器300、310、320、和330的输出A、B、C和D的相关值[RC1(τ)]、[RC2(τ)]、[RC3(τ)]和[RC4(τ)]。

表16还说明了作为相应匹配滤波器300、310、320、和330所有输出的加和结果的加法器340的输出E′[RC1(τ)]+[RC2(τ)]+[RC3(τ)]+[RC4(τ)]′,并且还表示了作为把该相加的相关结果与预定的相关阈值比较的结果获得的阈值比较器90的输出

表16

| τ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 时隙# | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| A点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| B点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| C点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| D点 | 15 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 | -1 |

| E点 | 60 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 | -4 |

| F点 | H | L | L | L | L | L | L | L | L | L | L | L | L | L | L |

如图41B所示,在利用15个时隙长度的导频码型进行相关处理,然后把其所有相关结果相加的情况下,可在′τ=0′的时间点获得最大相关值′60′,在旁瓣获得最小相关值-4。此刻,把相关阈值VT确定成小于最大相关值′60′的值,并认为来自相应匹配滤波器300、310、320、330的,基于每个延迟时间点τ的相关结果的加和值大于相关阈值时是帧同步检测时间点。

如果在该情况下出现了超过′VT+4′的噪声,在帧同步中出现了错误检测。从相关阈值与旁瓣相关值之间的关系决定帧同步中这种错误检测的概率。

在表16中,在图40A所示的装置结构中表示了阈值比较器90根据延迟变量的输出。在把匹配滤波器300、310、320、和330的输出相加,并在阈值比较器90中将预定相关阈值VT与该加和值比较的过程中,把超过阈值VT的加和值表示为′H′,和把阈值VT以下的加和值表示为′L′。

在图41A的装置中,通过每个时隙地针对序列,即针对C1、C2、C3和C4把所有自相关结果相加,和从该加和结果检验阈值比较器90的输出可确认帧同步。

如上所述,在图39A、40A和41A所示的设备结构中,匹配滤波器100、200、210、300、310、320、和330针对15个时隙长度的输入序列使用相同长度的系数。

用于上行链路和下行链路的帧同步装置的可替代实施例

当每帧使用15个时隙时,其使用图21所示的帧同步字来进行帧同步检测。为了使用图21所示的帧同步字来进行帧同步检测,优选地采用如下的配置特征。

每个代码序列C1,C2,C3,C4,C5,C6,C7,C8中比特值“0”或“1”的数目比其中比特值“1”或“0”的数目大1,以允许(1)在当全具有比特值“1”的导频序列被插入上行链路和下行链路的阴影序列之间时,能够使在所有延迟时间点上导频序列之间的相关值为最小值,以及(2)当全具有比特值“0”的代码序列被插入导频序列C1,C2,C3,C4,C5,C6,C7,C8之间时,能够使在所有延迟时间点或时移上,各导频序列之间具有最小的相关值。

另外,每个导频序列C1,C2,C3,C4,C5,C6,C7,C8被设计成在延迟时间点“0”处彼此相邻的导频序列之间(例如,C1和C2,C2和C3)具有最小的相关值。而导频序列C5,C6,C7,C8则是通过将导频序列C1,C2,C3,C4移位而形成的。换句话说,导频序列C5,C6,C7,C8是通过将在延迟时间点“0”处彼此相邻的两个导频序列之间具有最小相关值的导频序列C1,C2,C3,C4移位来形成的。

导频序列C1,C2,C3,C4,C5,C6,C7,C8每一个均被设计成在除了延迟时间点“0”之外的任何其它延迟时间点处均具有最小的相关值。

导频序列C1与C2之间的相关值在某个中间延迟时间点上具有极性为负的最大值,而导频序列C2与C1之间的相关值则在除了该中间延迟时间点之外的其它任何延迟时间点处均具有最小值。导频序列C3与C4之间的相关值在某个中间延迟时间点上具有极性为负的最大值,而导频序列C4与C3之间的相关值则在除了该中间延迟时间点之外的其它任何延迟时间点处均具有最小值。

导频序列C5与C6之间的相关值在某个中间延迟时间点上具有极性为负的最大值,而导频序列C6与C5之间的相关值则在除了该中间延迟时间点之外的其它任何延迟时间点处均具有最小值。导频序列C7与C8之间的相关值在某个中间延迟时间点上具有最大值,而导频序列C8与C7之间的相关值则在除了该中间延迟时间点之外的其它任何延迟时间点处均具有最小值。

具体地说,导频序列C1被移位和倒置,以产生导频序列C2。而将导频序列C3移位和倒置,以产生导频序列C4。类似地,导频序列C5被移位和倒置,以产生导频序列C6。而将导频序列C7移位和倒置,以产生导频序列C8。

图21所示的帧同步字是根据上述配置特征设计的,以用于上行链路和下行链路信道的帧同步检测,具体地说,即用于对帧同步检测的双检。

正如可以从上述配置特征看出的,这些帧同步字的每个导频序列均表现出如下的一种自相关特性

其中i=1,2,3,...8,而RCi(τ)则表示从C1到C8各个导频序列的自相关函数。如上所述,这些帧同步字被分成了PCSP的E,F,G和H。

同一类中所包含的导频序列对{Ci,Cj},例如{C1,C2},{C3,C4},{C5,C6},和{C7,C8}均具有如下的互相关特征:

其中i=1&j=2,i=3&j=4,i=5&j=6,i=7&j=8。

其中j=2&i=1,j=4&i=3,j=6&i=5,j=8&i=7。

在公式(34)中,RCi,Cj(τ)表示每一类中各对代码序列之间的互相关函数。而在公式(35)中,RCj,Ci(τ+1)则是代码序列Ci与移动1个位长后所得代码序列Cj之间的互相关函数。

将自相关特性公式(33)与互相关特性公式(34)和(35)联立,可得:

其中α=1,2,3,...,8。

其中α=2,4,6,8

图42A和42B所示为根据本发明一种优选实施例利用某种导频码型所得相关结果的一个实施例的曲线图,而图43A和43B所示为根据本发明的一种优选实施例利用某种导频码型所得相关结果的另一实施例的曲线图。

图42A到43B所示的相关结果是从公式(36)和(37)中推出的,其中图42A和42B所示为公式(36)和(37)中当α=2时的相关结果,而图43A和43B所示为公式(36)和(37)中当α=4时的相关结果。

更详细地说,图42A所示为公式(36)中当α=2时自相关函数的加和结果,而图42B所示为公式(37)中当α=2时互相关函数的加和结果。图43A所示为公式(36)中当α=4时自相关函数的加和结果,而图43B所示为公式(37)中当α=4时互相关函数的加和结果。

通过观察图42A到43B中的各种相关的结果,可以在进行帧同步检测时将执行单检,而通过同时观察图42A到43B中的自相关和互相关结果,则可以在进行帧同步检测时进行双检。基于上述说明,如上所述,将产生用于上行链路和下行链路的L=15的导频码型和导频码元。

从单独一个导频序列中可以产生如图21所示的,优选地,8个帧同步字。各帧同步字之间的关系由如下公式(38)给定。具体地说,将给定导频序列C1与其它导频序列之间的关系。

C1(t+j+τ)=-C2(t+j+τ+7)

=C3(t-j-τ+5)

=-C4(t-j-τ+12)

=C5(t+j+τ+10)

=-C6(t+j+τ+2)

=C7(t-j-τ)

=-C8(t-j-τ+7) (38)

在公式(38)中,通过对其它代码序列进行倒置、循环移位或反转将可以产生导频序列C1。

而根据公式(38),当公式(36)中α=8时,自相关函数的加和结果由如下的公式(40)给定。然而,在计算该加和结果之前,应该利用公式(39)求出上述8个导频序列的总和(S):

S(t+j+τ)=C1(t+j+τ)-C2(t+j+τ+7)+C3(t-j-τ+5)

-C4(t-j-τ+12)+C5(t+j+τ+10)-C6(t+j+τ+2)

+C7(t-j-τ)-C8(t-j-τ+7)=8C1(t+j+τ) (39)

当α=8时,利用公式(39),可以将公式(36)表示为公式(40):

假设导频序列C1,C2,C3,C4,C5,C6,C7,C8由如下的公式(41)所定义,则公式(42)按索引进行处理的关系(index processed relation)将由公式(38)给定。

C1=(C1,0,C1,1,...,C1,14)

C2=(C2,0,C2,1,...,C2,14)

C3=(C3,0,C3,1,...,C3,14)

C4=(C4,0,C4,1,...,C4,14)

C5=(C5,0,C5,1,...,C5,14)

C6=(C6,0,C6,1,...,C6,14)

C7=(C7,0,C7,1,...,C7,14)

C8=(C8,0,C8,1,...,C8,14) (41)

C1,(j+τ)(mod15)=—C2,(j+r+7)(mod15)

=C3.(-j-τ+5)(mod15)

=—C4,(-j-τ+12)(mod15)

=C5.(j+τ+10)(mod15)

=—C6,(j+τ+2)(mod15)

=C7,(-j-τ)(mod15)

=—C8,(-j-τ+7)(mod15) (42)

利用上述原理,可以实现一种根据本发明的用于帧同步的相关处理装置。在本发明的该种相关处理装置中,上述8个帧同步字被存储在一个存储器中,此时,如果每个导频序列的索引(i,j)所代表的是存储器的地址,则该存储器中所存储的帧同步字之间的关系将取决于公式(42)。

图44所示为根据本发明一种优选实施例的用于上行链路信道的相关处理装置,其中在进行帧同步检测时,将对每个时隙进行单检。

作为一个实例,在图44所示的相关装置中,导频比特Npilot的数目为6,而所输入用于帧同步检测的导频序列的数目为4。换句话说,即α=4,因此将用到图21所示的导频序列C1,C2,C3,C4。

因此,公式(40)将被转换为如下的公式(43):

由于在本发明中所用的是如公式(43)中所表示的帧同步字特征,所以图44所示的相关处理装置将采用单独一个相关器用于帧同步检测。

接收上行链路专用物理控制信道的一个帧单元中的信号,同时按照时隙号的顺序依次输入图23E的导频码型中比特#1,比特#2,比特#4和比特#5的解调列序列。

4个列序列被输入到存储器映射/寻址模块中,其中将各列序列存储到上述帧单元中,并利用公式(42)所表示的帧同步字之间的互相关对其进行移位及反转。在此情况下,存储在该帧单元中的列序列将由如下的公式(44)给定。此时,每个列序列的索引(i,j)所表示的是存储器地址。

在利用存储器映射/寻址模块将公式(44)中的每一个列序列移位及反转后,将其输出。同时将存储器映射/寻址模块的输出加和在一起,以将如公式(45)所示的结果值“S1”提供给相关器。

该相关器对先前所存储的导频序列C1与公式(45)所表示的结果值“S1”进行相关,以由此来检测帧同步。此时,相关的结果如图43A所示,通过观察该相关结果,可以实现帧同步检测过程中的单检。

图45所示为根据本发明的一种优选实施例的用于下行链路的相关处理装置的示意图,其中在进行帧同步检测时将对每个时隙执行单检。

在此实例中,如图45所示,码元速率为256,512,1024Ksps(Npilot=16),而所输入用于帧同步检测的代码序列的数目为8。换句话说,即α=8,因此将用到图21所示的代码序列C1到C8。而对于列序列,则将用到由第一、第三、第五和第七导频码元(码元#1,码元#3,码元#5,码元#7)的每条I或Q信道的分支位流(branch stream)所映射的列序列。

因此,可以直接使用公式(40)而不需进行任何变换,同时也将使用公式(40)中所示的帧同步字的特征。其结果是,图45所示的相关处理装置采用单独一个相关器用于帧同步检测。

参照图45,其接收下行链路专用物理控制信道的一个帧单元中的信号,同时将按照时隙号的顺序依次输入图24A所示导频码型中的码元#1,码元#3,码元#5和码元#7的解调列序列。

8个列序列被输入到存储器映射/寻址模块中,其中将各列序列存储到上述帧单元中,并利用公式(42)的帧同步字之间的互相关将其移位及反转。在此情况下,存储在该帧单元中的列序列将由如下的公式(46)给定。此时,每个列序列的索引(i,j)所表示的是存储器地址。

利用存储器映射/寻址模块对上述公式(46)中的每一个列序列进行移位及反转,随后再将其输出。来自存储器映射/寻址模块的输出被加和在一起,以将如公式(47)所示的结果值“S2”提供给相关器。

该相关器对先前所存储的导频序列C1与由公式(47)所表示的结果值“S2”进行相关,以由此来检测帧同步。此时,相关的结果如图46所示,通过观察该相关结果,可以实现帧同步检测过程中的单检。

在利用每个时隙的相关结果来确认帧同步的方法中,是通过利用在15时隙长度的序列中适当加和各相关处理结果来确认帧同步的,由此将可以减小由于噪声而出现帧同步错误检测的可能性。

此外,当移动通信系统的上行链路和下行链路中所用的码片速率为3.84Mcps时,按原样使用15时隙长度的导频序列来进行相关处理,并从其相关结果的加和值中来确认帧同步。因此,其将可以使用结构十分简单的装置来确认帧同步。

根据本发明的用于上行链路和下行链路信道的相关处理装置,将各个代码序列加在一起,同时对于每个代码序列均具有不同的特定时间延迟及上行/下行排序(ordering)。一旦对代码序列进行加和,则每个序列将具有多种类型的信道特征,以由此获得时间分集效果。

如果所存储的代码序列的大小小于两帧,则在进行相关处理时,有可能会破坏各代码序列的序列连续性。然而,序列的不连续性将可以提供时间分集效果。

当所加和的代码序列的数目等于2或3或更大,且其中将按照相同方向(上行或下行方向)顺序的代码序列组合在一起时,存储器的大小可以减小。与此相反,在其中将按照不同方向顺序的代码序列组合在一起的情况中,则可以通过序列的不连续性来获得时间分集。

如果将彼此时间延迟相差很小的代码序列组合在一起,则可以减小存储器的大小。与此相反,如果将彼此时间延迟相差很大的代码序列组合在一起,则可以获得时间分集。

如上所述,根据本发明的使用最佳导频码型的帧同步装置和方法,不论所用代码序列的数目为多少,均可以在上行链路或下行链路中只使用单独一个相关器,由此使得接收方一侧用于帧同步的硬件变得十分简单。

并且,得到简化的硬件结构同时也不需要任何复杂的软件来支持,由此使其能够以十分简单的方式来检测帧同步。

上述实施例仅是示例性的而并不应理解为对本发明的限制。此处所讲述的方法可以容易地应用到其它类型的装置。本发明的讲述是用于说明性目的,并不限制权利要求的范围。本领域技术人员可以作出多种替换、修改和变型。在权利要求中,装置+功能的表述是为了涵盖执行所述功能的所述结构,及其各种等同结构和方法。

Claims (4)

1.一种传送用于接收侧的用于帧同步和信道估计中的至少一个的导频码型的方法,所述方法包括:

提供包括15时隙的无线电帧,每个时隙包括多个导频比特;

将第一代码序列和第二代码序列插入所述无线电帧中,其中,所述第一代码序列是“100011110101100”,所述第一代码序列的每个比特位于每个时隙的相同的导频比特位置,并且其中所述第二代码序列是“101001101110000”,所述第二代码序列的每个比特位于每个时隙的另一个相同的导频比特位置;以及

在专用物理控制信道上将所述无线电帧传送到所述接收侧。

2.根据权利要求1所述的方法,其中,每个时隙进一步包括多个TFCI比特,该TFCI比特表示传输格式组合指示符TFCI。

3.一种传送用于接收侧的用于帧同步和信道估计中的至少一个的导频码型的方法,所述方法包括:

提供包括15时隙的无线电帧,每个时隙包括多个导频比特;

将第一代码序列和第二代码序列插入所述无线电帧中,其中,所述第一代码序列是“110001001101011”,所述第一代码序列的每个比特位于每个时隙的相同的导频比特位置,并且其中所述第二代码序列是“001010000111011”,所述第二代码序列的每个比特位于每个时隙的另一个相同的导频比特位置;以及

在专用物理控制信道上将所述无线电帧传送到所述接收侧。

4.根据权利要求3所述的方法,其中,每个时隙进一步包括多个TFCI比特,该TFCI比特表示传输格式组合指示符TFCI。

Applications Claiming Priority (26)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR8630/1999 | 1999-03-15 | ||

| KR1019990008630A KR100294711B1 (ko) | 1999-03-15 | 1999-03-15 | 최적의 파일럿 심볼을 이용한 프레임 동기 방법 |

| KR1019990012856A KR100323767B1 (ko) | 1999-04-12 | 1999-04-12 | 프레임 동기 유지 방법 |

| KR12856/1999 | 1999-04-12 | ||

| KR12857/1999 | 1999-04-12 | ||

| KR1019990012857A KR100320421B1 (ko) | 1999-04-12 | 1999-04-12 | 최적의 파일럿 심볼을 이용한 프레임 동기 확인 방법 |

| KR15722/1999 | 1999-04-30 | ||

| KR1019990015722A KR100317256B1 (ko) | 1999-04-30 | 1999-04-30 | 최적의 파일럿 심볼을 이용한 프레임 동기 방법 |

| KR1019990019506A KR20000075107A (ko) | 1999-05-28 | 1999-05-28 | 최적의 프레임 동기화 부호를 이용한 셀 탐색 방법 |

| KR19506/1999 | 1999-05-28 | ||

| KR1019990019505A KR100331870B1 (ko) | 1999-05-28 | 1999-05-28 | 파일럿 패턴 할당 및 배치 방법 |

| KR19505/1999 | 1999-05-28 | ||

| KR1019990019610A KR100304938B1 (ko) | 1999-05-29 | 1999-05-29 | 최적의 파일럿 패턴을 이용한 프레임 동기 방법 |

| KR19610/1999 | 1999-05-29 | ||

| KR23140/1999 | 1999-06-19 | ||

| KR23141/1999 | 1999-06-19 | ||

| KR1019990023141A KR100331871B1 (ko) | 1999-06-19 | 1999-06-19 | 슬롯별 상관 결과를 이용한 프레임 동기 확인 방법 |

| KR1019990023140A KR100308151B1 (ko) | 1999-06-19 | 1999-06-19 | 샘플링된 상관 결과를 이용한 프레임 동기 확인 방법 |

| KR1019990023568A KR100331872B1 (ko) | 1999-06-22 | 1999-06-22 | 프레임 동기를 위한 파일럿 시퀀스 생성 방법 |

| KR23568/1999 | 1999-06-22 | ||

| KR1019990023937A KR100606673B1 (ko) | 1999-06-24 | 1999-06-24 | 파일럿 패턴을 이용한 프레임 동기 방법 |

| KR23937/1999 | 1999-06-24 | ||

| KR1019990026689A KR100331874B1 (ko) | 1999-07-02 | 1999-07-02 | 공통 파일럿 채널의 파일럿 패턴을 이용한 프레임 동기 방법 |

| KR26689/1999 | 1999-07-02 | ||

| KR1019990034212A KR100339337B1 (ko) | 1999-08-18 | 1999-08-18 | 최적의 파일럿 패턴을 이용한 프레임 동기 장치 및 방법 |

| KR34212/1999 | 1999-08-18 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB001031066A Division CN1161903C (zh) | 1999-03-15 | 2000-03-15 | 用于帧同步的通信网络、方法和装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1658534A CN1658534A (zh) | 2005-08-24 |

| CN100483972C true CN100483972C (zh) | 2009-04-29 |

Family

ID=27584380

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00103104A Expired - Lifetime CN1124708C (zh) | 1999-03-15 | 2000-03-15 | 消除旁瓣的方法和帧结构 |

| CNB001031066A Expired - Fee Related CN1161903C (zh) | 1999-03-15 | 2000-03-15 | 用于帧同步的通信网络、方法和装置 |

| CNB2004100491090A Expired - Lifetime CN100483972C (zh) | 1999-03-15 | 2000-03-15 | 用于帧同步的导频序列及帧同步方法和装置 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00103104A Expired - Lifetime CN1124708C (zh) | 1999-03-15 | 2000-03-15 | 消除旁瓣的方法和帧结构 |

| CNB001031066A Expired - Fee Related CN1161903C (zh) | 1999-03-15 | 2000-03-15 | 用于帧同步的通信网络、方法和装置 |

Country Status (11)

| Country | Link |

|---|---|

| US (1) | US7616681B2 (zh) |

| EP (5) | EP2099143B1 (zh) |

| JP (1) | JP4318963B2 (zh) |

| KR (1) | KR100294711B1 (zh) |

| CN (3) | CN1124708C (zh) |

| AT (2) | ATE473562T1 (zh) |

| BR (1) | BRPI0001674B1 (zh) |

| DE (2) | DE10012286B4 (zh) |

| ES (3) | ES2502015T3 (zh) |

| GB (1) | GB2350760B (zh) |

| HK (1) | HK1077134A1 (zh) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100685960B1 (ko) * | 2000-02-03 | 2007-02-23 | 엘지전자 주식회사 | 파일럿 패턴을 이용한 프레임 동기 확인 및 동기 실패검출 방법 |

| CN1318866C (zh) * | 2001-10-16 | 2007-05-30 | 日东电工株式会社 | 偏振片的制造方法及液晶显示装置 |

| CN1613220A (zh) * | 2002-03-22 | 2005-05-04 | 连宇通信有限公司 | 一种生成具有零相关窗的非匹配扩频序列编码方法 |

| KR100479864B1 (ko) * | 2002-11-26 | 2005-03-31 | 학교법인 중앙대학교 | 이동 통신 시스템에서의 하향링크 신호의 구성 방법과동기화 방법 및 그 장치 그리고 이를 이용한 셀 탐색 방법 |

| FR2859025B1 (fr) * | 2003-08-22 | 2006-04-21 | Cit Alcatel | Procede de validation de la detection d'un pic de correlation par un recepteur de systeme de positionnement par satellite |

| EP1542488A1 (en) * | 2003-12-12 | 2005-06-15 | Telefonaktiebolaget LM Ericsson (publ) | Method and apparatus for allocating a pilot signal adapted to the channel characteristics |

| GB0420847D0 (en) | 2004-09-20 | 2004-10-20 | Koninkl Philips Electronics Nv | A radio communication system, a radio station, and a method of transmitting data |

| CN100399726C (zh) * | 2004-12-20 | 2008-07-02 | 大唐移动通信设备有限公司 | 一种用于搜索广播中同步位置的方法 |

| CN101351017B (zh) * | 2005-01-10 | 2011-03-02 | 中兴通讯股份有限公司 | 一种无线综合接入网插入定位时隙的方法 |

| AU2006246322B2 (en) * | 2005-05-13 | 2010-04-22 | Dspace Pty Ltd | Method and system for communicating information in a digital signal |

| EP3029846A3 (en) | 2005-05-13 | 2016-08-17 | Dspace Pty Ltd | Method and system for communicating information in a digital signal |

| JP4632863B2 (ja) * | 2005-05-20 | 2011-02-16 | 京セラ株式会社 | 無線通信システム及び無線通信方法 |

| CN102571138B (zh) * | 2005-12-20 | 2015-02-11 | Lg电子株式会社 | 产生码序列的方法及使用其来发送信号的方法 |

| US8830983B2 (en) | 2005-12-20 | 2014-09-09 | Lg Electronics Inc. | Method of generating code sequence and method of transmitting signal using the same |

| US8259852B2 (en) * | 2006-07-19 | 2012-09-04 | Broadcom Corporation | Method and system for satellite communication |

| EP2074707B1 (en) | 2006-09-26 | 2018-08-08 | LG Electronics Inc. | A method for transmitting information using sequence. |

| CN101316115B (zh) * | 2007-05-31 | 2015-02-18 | 电信科学技术研究院 | 导频序列信号的检测方法、设备及系统 |

| CN101359931B (zh) * | 2007-07-30 | 2012-11-21 | 鼎桥通信技术有限公司 | 一种信道导频序列的传输方法 |

| US9246541B2 (en) | 2008-02-01 | 2016-01-26 | Qualcomm Incorporated | UTRAN enhancements for the support of inter-cell interference cancellation |

| CN101674101B (zh) * | 2008-09-08 | 2013-06-05 | 中兴通讯股份有限公司 | 一种宽带码分多址系统的多径合并数据存储方法和装置 |

| US20100240382A1 (en) * | 2009-03-19 | 2010-09-23 | Qualcomm Incorporated | Systems, apparatus and methods for interference management in wireless networks |

| KR101696464B1 (ko) * | 2009-08-28 | 2017-01-16 | 엘지전자 주식회사 | 무선 통신 시스템에서 파일럿 전송 방법 및 장치 |

| CN104796370B (zh) * | 2015-03-20 | 2018-03-30 | 中国电子科技集团公司第三研究所 | 一种水声通信的信号同步方法、系统及水声通信系统 |

| WO2016165080A1 (zh) * | 2015-04-15 | 2016-10-20 | 华为技术有限公司 | 参考信号发送与接收方法及装置 |

| CN106559209B (zh) * | 2015-09-21 | 2020-07-17 | 中兴通讯股份有限公司 | 一种帧同步的方法及装置 |

| ES2785905T3 (es) | 2016-03-31 | 2020-10-08 | Fraunhofer Ges Forschung | Preámbulo optimizado y procedimiento para detección robusta de paquetes de interferencia para aplicaciones de telemetría |

| CN109995689B (zh) * | 2017-12-29 | 2021-08-06 | 普天信息技术有限公司 | 估计pucch频偏的方法、装置、电子设备和存储介质 |

Family Cites Families (75)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3461451A (en) * | 1967-09-22 | 1969-08-12 | Itt | Code generator to produce permutations of code mates |

| CA923603A (en) | 1970-09-23 | 1973-03-27 | Canadian Marconi Company | Circuit for avoiding false lock |

| US4901307A (en) * | 1986-10-17 | 1990-02-13 | Qualcomm, Inc. | Spread spectrum multiple access communication system using satellite or terrestrial repeaters |

| JPH0251289A (ja) * | 1988-08-15 | 1990-02-21 | Sekisui Plastics Co Ltd | レーザー光線による複合圧電素子材料の製作方法 |

| JPH0332241A (ja) * | 1989-06-29 | 1991-02-12 | Mitsubishi Electric Corp | スペクトラム拡散通信方式 |

| US5022047A (en) | 1989-08-07 | 1991-06-04 | Omnipoint Data Corporation | Spread spectrum correlator |

| WO1992016064A1 (en) | 1989-08-07 | 1992-09-17 | Omnipoint Corporation | Asymmetric spread spectrum correlator |

| US5101501A (en) * | 1989-11-07 | 1992-03-31 | Qualcomm Incorporated | Method and system for providing a soft handoff in communications in a cdma cellular telephone system |

| US5109390A (en) * | 1989-11-07 | 1992-04-28 | Qualcomm Incorporated | Diversity receiver in a cdma cellular telephone system |

| US5103459B1 (en) * | 1990-06-25 | 1999-07-06 | Qualcomm Inc | System and method for generating signal waveforms in a cdma cellular telephone system |

| JP3038866B2 (ja) * | 1990-10-03 | 2000-05-08 | 日本電気株式会社 | データ伝送方式 |

| DE4203301C1 (zh) | 1992-01-31 | 1993-01-14 | Siemens Ag, 8000 Muenchen, De | |

| CA2112221A1 (en) | 1992-04-24 | 1993-11-11 | Haruhiro Shiino | Receiver for a digital communication system |

| JP2755067B2 (ja) | 1992-09-25 | 1998-05-20 | 日本電気株式会社 | フレーム同期回路 |

| US5581580A (en) | 1993-05-20 | 1996-12-03 | Telefonaktiebolaget Lm Ericsson | Low complexity model based channel estimation algorithm for fading channels |

| DE4318368C1 (de) | 1993-05-28 | 1994-07-14 | Siemens Ag | Verfahren zum Gewinnen eines einen Ausfall der Synchronisation zwischen einer Pseudozufallssignalfolge eines Senders und einer Referenz-Pseudozufallssignalfolge eines Empfängers anzeigenden Signals |

| JP3106037B2 (ja) | 1993-06-30 | 2000-11-06 | 株式会社東芝 | 加熱調理器及び調理皿用取手 |

| JP3222001B2 (ja) | 1993-12-14 | 2001-10-22 | ユニデン株式会社 | チャンネル切替制御方法およびそれを用いたコードレス電話機 |

| JP3097443B2 (ja) | 1994-02-28 | 2000-10-10 | ケイディディ株式会社 | ユニークワード検出方法 |

| FI96154C (fi) * | 1994-05-30 | 1996-05-10 | Nokia Telecommunications Oy | Menetelmä tilaajapäätelaitteiden synkronisoimiseksi, tukiasema sekä tilaajapäätelaite |

| US5495516A (en) | 1994-06-09 | 1996-02-27 | General Datacomm, Inc. | Diagnostic channel wakeup sequence for network managed fractional T1 or E1 digital service units |

| JP2749263B2 (ja) | 1994-07-07 | 1998-05-13 | 三洋電機株式会社 | フレーム同期再生回路 |

| US5627863A (en) | 1994-07-15 | 1997-05-06 | Amati Communications Corporation | Frame synchronization in multicarrier transmission systems |

| US5680414A (en) | 1994-09-09 | 1997-10-21 | Omnipoint Corporation | Synchronization apparatus and method for spread spectrum receiver |

| JP2605648B2 (ja) | 1994-12-22 | 1997-04-30 | 日本電気株式会社 | Ss受信機における逆拡散符号位相検出装置 |

| DE69634845T2 (de) | 1995-01-05 | 2006-05-18 | Ntt Docomo Inc. | Vorrichtung und verfahren zur kohärenten verfolgung eines signals zur verwendung in einem cdma empfänger |

| DE69636424T8 (de) | 1995-06-13 | 2007-12-06 | Ntt Docomo, Inc. | Direktsequenz-Kodemultiplexvielfachzugriffsempfänger und Verfahren zur Synchronisierung dafür |

| FI110645B (fi) | 1995-06-30 | 2003-02-28 | Nokia Corp | Vastaanottomenetelmä ja tukiasemavastaanotin |

| JP2914232B2 (ja) | 1995-08-09 | 1999-06-28 | 日本電気株式会社 | スペクトル拡散通信システム |

| JP2924730B2 (ja) | 1995-09-13 | 1999-07-26 | 日本電気株式会社 | 信号受信方法 |

| GB2309864A (en) | 1996-01-30 | 1997-08-06 | Sony Corp | An equalizer and modulator using a training sequence and multiple correlation with a stored copy of the sequence |

| DE19614543C1 (de) | 1996-04-12 | 1997-08-28 | Philips Patentverwaltung | Entzerrer mit erweiterter Kanalschätzung für einen Empfänger in einem digitalen Übertragungssystem |

| US6005903A (en) | 1996-07-08 | 1999-12-21 | Mendelovicz; Ephraim | Digital correlator |

| US5737326A (en) | 1996-07-12 | 1998-04-07 | Lucent Technologies Inc. | Multi-code code division multiple access receiver |

| JP2751959B2 (ja) | 1996-07-15 | 1998-05-18 | 日本電気株式会社 | Cdma受信装置の受信タイミング検出回路 |

| KR0183002B1 (ko) | 1996-07-16 | 1999-05-15 | 서정욱 | 코드분할다중접속 통신방식에서의 파일럿신호를 이용한 동시획득 및 추적장치와 그 방법 |

| JP3681230B2 (ja) | 1996-07-30 | 2005-08-10 | 松下電器産業株式会社 | スペクトル拡散通信装置 |

| US6404732B1 (en) | 1996-07-30 | 2002-06-11 | Agere Systems Guardian Corp. | Digital modulation system using modified orthogonal codes to reduce autocorrelation |

| SE510890C2 (sv) | 1996-08-02 | 1999-07-05 | Ericsson Telefon Ab L M | Förfarande och anordning för bredbandstransmission |

| US6067292A (en) | 1996-08-20 | 2000-05-23 | Lucent Technologies Inc | Pilot interference cancellation for a coherent wireless code division multiple access receiver |

| US5889768A (en) | 1996-08-30 | 1999-03-30 | Motorola, Inc. | Method of and apparatus for pilot channel acquisition |

| JP3795984B2 (ja) | 1996-12-20 | 2006-07-12 | 富士通株式会社 | 無線受信機 |

| JP3242860B2 (ja) | 1997-04-08 | 2001-12-25 | シャープ株式会社 | スペクトル直接拡散通信システムにおける相関同期回路 |

| JP3204925B2 (ja) * | 1997-06-18 | 2001-09-04 | 株式会社エヌ・ティ・ティ・ドコモ | Cdma通信システムにおける信号受信装置 |

| US5991330A (en) * | 1997-06-27 | 1999-11-23 | Telefonaktiebolaget L M Ericsson (Pub1) | Mobile Station synchronization within a spread spectrum communication systems |

| US5930366A (en) | 1997-08-29 | 1999-07-27 | Telefonaktiebolaget L M Ericsson | Synchronization to a base station and code acquisition within a spread spectrum communication system |

| DE19744428C1 (de) * | 1997-10-08 | 1999-02-25 | Texas Instruments Deutschland | Verfahren zum Übertragen eines digitalen Datensignals von einem Sender zu einem Empfänger |

| JP3441636B2 (ja) | 1997-11-21 | 2003-09-02 | 株式会社エヌ・ティ・ティ・ドコモ | チャネル推定値を求める装置および方法、受信装置ならびに伝送システム |

| JP3308481B2 (ja) | 1998-01-09 | 2002-07-29 | 沖電気工業株式会社 | 相関値算出装置 |

| JP3967452B2 (ja) | 1998-03-13 | 2007-08-29 | 株式会社東芝 | スペクトラム拡散無線伝送受信装置 |

| JP3411214B2 (ja) | 1998-05-22 | 2003-05-26 | 三菱電機株式会社 | ディジタル無線通信系の受信処理方法および受信機 |

| US6504830B1 (en) | 1998-06-15 | 2003-01-07 | Telefonaktiebolaget Lm Ericsson Publ | Method, apparatus, and system for fast base synchronization and sector identification |

| KR20000009140A (ko) * | 1998-07-21 | 2000-02-15 | 윤종용 | 확산대역 통신시스템의 초기 포착 및 프레임동기 장치 및 방법 |

| US6078607A (en) | 1998-08-10 | 2000-06-20 | Omnipont Corporation | Synchronization codes for use in communication |

| US6526091B1 (en) | 1998-08-17 | 2003-02-25 | Telefonaktiebolaget Lm Ericsson | Communication methods and apparatus based on orthogonal hadamard-based sequences having selected correlation properties |

| US6363104B1 (en) | 1998-10-02 | 2002-03-26 | Ericsson Inc. | Method and apparatus for interference cancellation in a rake receiver |

| US6356605B1 (en) | 1998-10-07 | 2002-03-12 | Texas Instruments Incorporated | Frame synchronization in space time block coded transmit antenna diversity for WCDMA |

| US6424642B1 (en) | 1998-12-31 | 2002-07-23 | Texas Instruments Incorporated | Estimation of doppler frequency through autocorrelation of pilot symbols |

| US6507602B1 (en) | 1999-01-07 | 2003-01-14 | Ericsson, Inc. | Smoothing receiver channel estimates using spectral estimation |

| US6487252B1 (en) | 1999-01-29 | 2002-11-26 | Motorola, Inc. | Wireless communication system and method for synchronization |

| GB9904398D0 (en) | 1999-02-25 | 1999-04-21 | Fluorescience Ltd | High throughput assay |

| US6567482B1 (en) | 1999-03-05 | 2003-05-20 | Telefonaktiebolaget Lm Ericsson (Publ) | Method and apparatus for efficient synchronization in spread spectrum communications |

| US6804264B1 (en) | 1999-03-15 | 2004-10-12 | Lg Information & Communications, Ltd. | Pilot signals for synchronization and/or channel estimation |

| US6721299B1 (en) | 1999-03-15 | 2004-04-13 | Lg Information & Communications, Ltd. | Pilot signals for synchronization and/or channel estimation |

| US6987746B1 (en) | 1999-03-15 | 2006-01-17 | Lg Information & Communications, Ltd. | Pilot signals for synchronization and/or channel estimation |