CN100414405C - 具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 - Google Patents

具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 Download PDFInfo

- Publication number

- CN100414405C CN100414405C CNB02122790XA CN02122790A CN100414405C CN 100414405 C CN100414405 C CN 100414405C CN B02122790X A CNB02122790X A CN B02122790XA CN 02122790 A CN02122790 A CN 02122790A CN 100414405 C CN100414405 C CN 100414405C

- Authority

- CN

- China

- Prior art keywords

- gate

- line

- data

- tft

- film transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title description 17

- 230000000007 visual effect Effects 0.000 title 1

- 239000010409 thin film Substances 0.000 claims abstract description 72

- 239000000758 substrate Substances 0.000 claims abstract description 55

- 238000011179 visual inspection Methods 0.000 claims description 39

- 238000007689 inspection Methods 0.000 claims description 26

- 230000005540 biological transmission Effects 0.000 claims description 18

- 229910000679 solder Inorganic materials 0.000 description 45

- 239000004065 semiconductor Substances 0.000 description 43

- 238000010586 diagram Methods 0.000 description 31

- 239000012212 insulator Substances 0.000 description 28

- 239000002184 metal Substances 0.000 description 26

- 229910052751 metal Inorganic materials 0.000 description 26

- 238000005530 etching Methods 0.000 description 24

- 239000010408 film Substances 0.000 description 24

- 238000002161 passivation Methods 0.000 description 18

- 238000000151 deposition Methods 0.000 description 16

- 230000008021 deposition Effects 0.000 description 16

- 229910021417 amorphous silicon Inorganic materials 0.000 description 14

- 238000001312 dry etching Methods 0.000 description 10

- 230000008859 change Effects 0.000 description 9

- 230000008878 coupling Effects 0.000 description 9

- 238000010168 coupling process Methods 0.000 description 9

- 238000005859 coupling reaction Methods 0.000 description 9

- 239000007789 gas Substances 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 7

- 238000001259 photo etching Methods 0.000 description 7

- 238000005520 cutting process Methods 0.000 description 6

- 229910003460 diamond Inorganic materials 0.000 description 6

- 239000010432 diamond Substances 0.000 description 6

- 238000009413 insulation Methods 0.000 description 6

- 239000004973 liquid crystal related substance Substances 0.000 description 6

- 238000001039 wet etching Methods 0.000 description 6

- 229910004205 SiNX Inorganic materials 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 230000014509 gene expression Effects 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- MZAGXDHQGXUDDX-JSRXJHBZSA-N (e,2z)-4-ethyl-2-hydroxyimino-5-nitrohex-3-enamide Chemical compound [O-][N+](=O)C(C)C(/CC)=C/C(=N/O)/C(N)=O MZAGXDHQGXUDDX-JSRXJHBZSA-N 0.000 description 4

- 238000003466 welding Methods 0.000 description 4

- HCUOEKSZWPGJIM-YBRHCDHNSA-N (e,2e)-2-hydroxyimino-6-methoxy-4-methyl-5-nitrohex-3-enamide Chemical compound COCC([N+]([O-])=O)\C(C)=C\C(=N/O)\C(N)=O HCUOEKSZWPGJIM-YBRHCDHNSA-N 0.000 description 3

- 101001109689 Homo sapiens Nuclear receptor subfamily 4 group A member 3 Proteins 0.000 description 3

- 101000598778 Homo sapiens Protein OSCP1 Proteins 0.000 description 3

- 101000912503 Homo sapiens Tyrosine-protein kinase Fgr Proteins 0.000 description 3

- 101001067395 Mus musculus Phospholipid scramblase 1 Proteins 0.000 description 3

- 102100037226 Nuclear receptor coactivator 2 Human genes 0.000 description 3

- 102100022673 Nuclear receptor subfamily 4 group A member 3 Human genes 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 229910001316 Ag alloy Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000006073 displacement reaction Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 230000003760 hair shine Effects 0.000 description 2

- 230000001939 inductive effect Effects 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 229910000667 (NH4)2Ce(NO3)6 Inorganic materials 0.000 description 1

- RRIGVQQUVAETIG-UHFFFAOYSA-N 1,2,3,4,6,7,8,9-octahydro-[1,2,4,5]tetrazino[1,2-a][1,2,4,5]tetrazine Chemical compound C1NNCN2CNNCN21 RRIGVQQUVAETIG-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- 101000974356 Homo sapiens Nuclear receptor coactivator 3 Proteins 0.000 description 1

- 102100022883 Nuclear receptor coactivator 3 Human genes 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000008676 import Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000012797 qualification Methods 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136254—Checking; Testing

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Nonlinear Science (AREA)

- Manufacturing & Machinery (AREA)

- Optics & Photonics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Mathematical Physics (AREA)

- Ceramic Engineering (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

本发明公开了一种薄膜晶体管面板,其中多条栅极线和与栅极线相交以限定显示区域的多条数据线形成在包括显示区域和围绕区域的绝缘衬底上。在围绕区域上,形成了连接到栅极线上的栅极驱动电路和夹置在栅极驱动电路和栅极线之间并具有多个第一到第三或非门的用于VI的逻辑电路。用于VI的逻辑电路的第一或非门的第一输入端子连接到栅极驱动电路的输出端子上,且其第二输入端子连接到第一控制端子CON1上,其输出端子连接到第二或第三或非门的第一输入端子上。第二或非门的第二输入端子连接到第二控制端子CON2上。而其输出端子连接到奇数栅极线上,或非门的第二输入端子连接到第三控制端子CON3上,而其输出端子连接到偶数栅极线上。

Description

技术领域

本发明涉及一种薄膜晶体管阵列面板,尤其是涉及一种视觉检查(visualinspection)装置和在其中集成了栅极驱动电路的薄膜晶体管阵列面板中进行视觉检查的方法.

背景技术

薄膜晶体管阵列面板用作液晶显示器(LCD)或有机电致发光(EL)显示器等等中独立驱动每个像素的电路板,在薄膜晶体管面板中,形成了用于传输扫描信号的扫描信号线或栅极线、和用于传输图像信号的图像信号线或数据线.其中也形成了连接到栅极线和数据线的薄膜晶体管、连接到薄膜晶体管上的像素电极、用于覆盖和绝缘栅极线的栅极绝缘层以及用于覆盖并用于绝缘薄膜晶体管和数据线的钝化层.薄膜晶体管包括与作为栅极线一部分的栅极电极、源极电极和作为数据线一部分的漏极电极一起形成通道的半导体层,栅极绝缘层、和钝化层.薄膜晶体管为开关元件,其根据通过栅极线传输的扫描信号将通过数据线传输的图像信号传送到像素电极上.

LCD是利用这种薄膜晶体管面板的显示装置的代表,尤其是如反射型或半透射型LCD的中小型LCD大部分采用COG(玻璃上芯片)型.在这种情况下,视觉检查(visual inspection)(VI)和总体测试(gross test)(GT)在COGIC安装步骤之前进行,以便节省昂贵的COG IC、偏振器和补偿薄膜,并提高产量.由于测试需要昂贵的设备,此外需要很长的处理时间,因此难于将GT应用到实际过程中.另外,目前可用的VI是在形成用于检查的导线之后进行的,该导线连接到COG端子之间的栅极线和数据线上,或连接到相对侧上,以进行VI,然后,与面板一起进行金刚石切割,或进行激光切割来分开用于检查的导线。在这种情况下,在这种切割过程中,产生污染物颗粒,或者导线通过其切割侧被腐蚀,从而使可靠性下降.

同时,TFT面板可以通过如下的方法制造,即,驱动集成电路或是局部地或是作为一个整体地直接形成在薄膜晶体管上.作为这种示例,存在多晶硅薄膜晶体管面板(多晶硅TFT面板)和无定形驱动集成电路面板(a-si IC面板).在TFT面板上作为一个整体地直接形成驱动IC的方法中,GT可以通过TFT自身来进行.然而,在TFT面板上直接形成仅一部分驱动IC的方法需要昂贵的设备来执行GT.

此外,由于形成在TFT工件上的驱动IC在激光切割时作用为障碍物,在检查后难于采用激光切割,并且由于TFT面板和滤光片形成为相同的尺寸,所以难于获得用于激光切割的空间.

发明内容

本发明通过解决这些问题提高了液晶显示器的可靠性.

本发明提供了一种用于在具有驱动集成电路的薄膜晶体管中进行视觉检查的装置.

本发明也提供了一种用于在具有驱动集成电路的薄膜晶体管中进行视觉检查的方法.

在一个方面中,本发明提供了一种薄膜晶体管面板,其包括用于VI的逻辑电路,该电路连接在栅极驱动电路和栅极线之间,以施加栅极检查信号.

详细地说,薄膜晶体管面板包括具有显示区域和围绕区域的绝缘衬底;形成在绝缘衬底上的第一信号线;形成在绝缘衬底上并与第一信号线绝缘且交叉以限定显示区域的第二信号线;形成在绝缘衬底的围绕区域上并连接到Voff电压施加端子上的多条驱动信号线;形成在绝缘衬底的围绕区域上的多条检查信号线;用于检查的第一薄膜晶体管,其具有连接到第一信号线上的漏极电极、连接到任一条检查信号线上的源极电极、以及连接到任一条驱动信号线上的栅极电极;以及用于检查的第二薄膜晶体管,其具有连接到第二信号线上的漏极电极、连接到任一条检查信号线上的源极电极、以及连接到任一条驱动信号线上的栅极电极.

连接到用于检查的第二薄膜晶体管上的检查信号线包括第一检查信号线和第二检查信号线.用于检查的第二薄膜晶体管可以交替地连接到第一检查信号线或第二检查信号线上.连接到用于检查的第一薄膜晶体管上的第一检查信号线包括第三和第四检查信号线.用于检查的第一薄膜晶体管可以交替地连接到第三检查信号线和第四检查信号线上.

另外,连接到用于检查的第二薄膜晶体管上的检查信号线包括第一、第二和第三检查信号线.用于检查的第二薄膜晶体管可以依次连接到第一、第二和第三检查信号线上.连接到用于检查的第一薄膜晶体管上的检查信号线包括第四和第五检查信号线.用于检查的第一薄膜晶体管交替地连接到第四和第五检查信号线上.

连接到用于检查的第二薄膜晶体管上的驱动信号线包括第一、第二和第三驱动信号线.用于检查的第二薄膜晶体管可以依次连接到第一、第二和第三驱动信号线上。

具有用于检查的薄膜晶体管的薄膜晶体管面板的详细结构如下.

薄膜晶体管面板包括具有显示区域和围绕区域的绝缘衬底;形成在绝缘衬底上的栅极线;形成在绝缘衬底的围绕区域上的数据驱动信号线;形成在绝缘衬底的围绕区域上的数据检查信号线;形成在栅极线、数据驱动信号线和数据检查信号线上的栅极绝缘层;形成在栅极绝缘层上的半导体图案,其至少一部分与数据驱动信号线重叠;形成在第一半导体图案上并在其间暴露出与数据驱动信号线相对应的一部分第一半导体图案的第一和第二欧姆接触层;形成在栅极绝缘层上并与栅极线相交以限定显示区域的数据线,其至少一部分形成在第二欧姆接触层上;形成在栅极绝缘层上的用于检查的第一电极,其至少一部分形成在第一欧姆接触层上;形成在数据线和用于检查的第一电极上的钝化层;以及形成在钝化层上并与数据检查信号线和用于检查的第一电极相连的第一连接部分.

薄膜晶体管面板还包括形成在绝缘衬底的围绕区域上的栅极驱动信号线;形成在绝缘衬底围绕区域上的栅极检查信号线;形成在栅极绝缘层上的第二半导体图案,其至少一部分与栅极驱动信号线重叠;形成在第二半导体图案上并在其间暴露出与栅极驱动信号线相对应的一部分第二半导体图案的第三和第四欧姆接触层;形成在栅极绝缘层上的用于检查的第二电极,其至少一部分形成在第三欧姆接触层上;形成在栅极绝缘层上的用于检查的第三电极,其至少一部分形成在第四欧姆接触层上;形成在钝化层上并连接栅极线和用于检查的第三电极的第二连接部分;以及形成在钝化层上并连接栅极检查信号线和用于检查的第二电极的第三连接部分.第一到第四欧姆接触层分别形成在数据线和用于检查的第一到第三电极的整个表面上.

薄膜晶体管面板还可以包括:形成在围绕区域上的传输门电路,其输出端子连接到数据线上;以及连接到传输门电路的输入端子上的短路条.或还包括形成在绝缘衬底的围绕区域上并具有连接到数据线上的输出的传输门电路;形成在绝缘衬底的围绕区域上并连接到Voff电压施加端子上的驱动信号线;形成在绝缘衬底的围绕区域上的检查信号线;以及用于检查的薄膜晶体管,其具有连接到数据线上的漏极电极、连接到检查信号线上的源极电极、以及连接到驱动信号线上的栅极电极.另外,连接到用于检查的薄膜晶体管上的检查信号线包括第一和第二检查信号线,并且优选的是用于检查的薄膜晶体管依次连接到第一检查信号和第二检查信号上。

同时,薄膜晶体管面板还包括连接到奇数数据线上的第一短路条和连接到偶数数据线上的第二短路条.

即使来形成这种逻辑电路,在如下的液晶显示器中,视觉检查通过将Von电压施加到栅极驱动电路的第一和第二时钟信号端子、开关电源端子、扫描起始端子和驱动信号端子上,并通过将公共电压施加到公共电压端子上来进行,该液晶显示器包括:具有显示区域和围绕区域的第一绝缘衬底;形成在第一绝缘衬底上的多条栅极线;形成在第一绝缘衬底上并与栅极线相交以限定显示区域的多条数据线;形成在第一绝缘衬底上并连接到栅极线和数据线上的像素薄膜晶体管;形成在显示区域上并连接到像素薄膜晶体管上的像素电极;形成在薄膜晶体管的围绕区域上并连接到栅极线上且具有第一和第二时钟信号端子、开关电源端子和扫描起始端子的栅极驱动电路;形成在第一绝缘衬底的围绕区域和驱动信号端子上的驱动信号线;第一绝缘衬底的围绕区域和检查信号端子上的检查信号线;用于检查的薄膜晶体管,其具有连接到数据线上的漏极电极、连接到检查信号线上的源极电极、以及连接到驱动信号线上的栅极电极;形成在第一绝缘区域的围绕区域上的公共电压端子;相对第一绝缘衬底设置的第二绝缘衬底;形成在第二绝缘衬底上并连接到公共电压端子上的公共电极;以及注入到第一和第二绝缘衬底之间的液晶材料.

另外,在如下的液晶显示器中,可以通过将Von电压施加到栅极驱动电路的第一和第二时钟信号端子、开关电源端子、扫描起始端子和驱动信号端子上,且通过将检查信号施加到短路条并将公共电压施加到公共电压端子上来进行视觉检查,该液晶显示器包括:由显示区域和围绕区域构成的第一绝缘衬底;形成在第一绝缘衬底上的多条栅极线;形成在第一绝缘衬底上并与栅极线相交以限定显示区域的多条数据线;形成在第一绝缘衬底上并连接到栅极线和数据线上的像素薄膜晶体管;形成在显示区域上并连接到像素薄膜晶体管上的像素电极;形成在薄膜晶体管的围绕区域上并连接到栅极线且具有第一和第二时钟信号端子、开关电源端子和扫描起始端子的栅极驱动电路;形成在第一绝缘衬底的围绕区域上并连接到数据线上的短路条;形成在第一绝缘区域的围绕区域上的公共电压端子;相对于第一绝缘衬底设置的第二绝缘衬底;形成在第二绝缘衬底上并连接到公共电压端子上的公共电极;以及注入第一和第二绝缘衬底之间的液晶材料.

附图说明

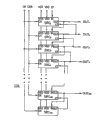

图1是根据本发明第一和第二实施例的薄膜晶体管的电路图;

图2A和2B是根据本发明第一实施例的薄膜晶体管的布线图,分别是图1所示的A和B的布线图;

图3A和3B分别是沿图2A的线IIIa-IIIa′和图2B的线IIIb-IIIb′截取的横截面图;

图4A和4B到图9A和9B是显示制造根据本发明第一实施例的薄膜晶体管的每个步骤的横截面图,“A”表示对应于图3A的一部分,而“B”表示对应于图3B的一部分;

图10A和10B是根据本发明第二实施例的薄膜晶体管的布线图,分别是图1所示的A和B;

图11A和11B分别是沿着图10A的线XIa-XIa′和图10B的XIb-XIb′截取的横截面图;

图12是根据本发明第三实施例的薄膜晶体管的布线图;

图13是根据本发明第四实施例的薄膜晶体管的电路图;

图14是根据本发明第五实施例的薄膜晶体管的电路图;

图15是根据本发明第六实施例的薄膜晶体管的电路图;

图16是栅极驱动电路的移位寄存器的框图;

图17是一级移位寄存器的详细电路图;

图18是图17的相应部分的时钟图;

图19是图15的用于VI的逻辑电路的详细电路图;

图20是根据本发明第七实施例的薄膜晶体管的电路图;

图21是根据本发明第八实施例的薄膜晶体管的电路图;

图22是根据本发明第九实施例的薄膜晶体管的电路图;以及

图23是根据本发明第十实施例的薄膜晶体管的电路图.

具体实施方式

将参照附图描述薄膜晶体管(TFT).

图1是根据本发明第一和第二实施例的电路图.

多条栅极线2横向延伸,而被绝缘以在纵向上与栅极线2相交的多条数据线3形成在绝缘衬底100上.连接到栅极驱动IC上的多个栅极焊点20连接到栅极线2的第一端,而连接到数据驱动IC上的多个数据焊点30连接到数据线3的第二端上.栅极线2和数据线3彼此相交以限定像素区域,一组像素区域形成显示区域.不同于显示区域的一部分限定为围绕区域.用于检查的栅极TFT B连接到与栅极线2相对的第三端上,而用于检查的数据TFT A连接到与数据线3的第二端相对的第四端上.栅极TFT B也连接到栅极检查信号线22和栅极驱动信号线24上,而数据TFT A也连接到数据检查信号线21和栅极驱动信号线25上.栅极线2、栅极检查信号线22和栅极驱动信号线24分别与栅极TFT B的漏极电极、源极电极和栅极电极相连.另外,数据线3、数据检查信号线21和驱动信号线25分别与数据TFT A的漏极电极、源极电极和栅极电极相连.第一焊点到第四焊点39、41、32和40连接到栅极检查信号线22、栅极驱动信号线24、数据检查信号线21和数据驱动信号线25的相应端上.栅极驱动信号线24通过第二焊点41连接到栅极Voff端子52上,而数据驱动信号线25连接到数据Voff端子51上.即,栅极TFT B的所有栅极电极连接到栅极Voff端子52上,且数据TFT A的所有栅极电极连接到数据Voff端子51上.Voff端子51和52通过在后续工序中经由FPC(柔性电路板)连接到Voff电压源上而作为Voff电压保持恒定.从而,TFT A和B一直处于关状态,这与断开状态相同.于是,不需要进行金刚石切割或激光切割来将用于检查的导线与数据线和栅极线分开.数据检查信号线21和数据驱动信号线25分别连接到第三和第四焊点32和40上,以相同的方式,栅极检查信号线22和栅极驱动信号线24分别连接到第一和第二焊点39和41上.另外,数据检查信号线21和数据驱动信号线25可以从要被弯曲的衬底100的边缘部分抽出.这是为了同时切割数据检查信号线21和数据驱动信号线25并沿着切割线(C)抛光边缘的目的.

包括公共电极、黑矩阵(black matrix)和滤色片的衬底200面对衬底100.

将参照附图详细描述TFT面板的这种衬底.

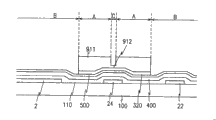

图2A和2B为根据本发明第一实施例的TFT的布线图,其分别是TFTA和TFT B的布线图,而图3A和3B是沿着图2A的线IIIa-IIIa′和图2B的线IIIb-IIIb′截取的横截面图.

首先,参照图2A和3A描述用于检查的数据TFT A.

数据检查信号线21和数据驱动信号线25横向延伸地形成在绝缘衬底100上,而其上形成栅极绝缘层110.第一半导体图案401在栅极绝缘层110上沿着纵向延伸.第一半导体图案401与数据驱动信号线25相交,但不到达数据检查信号线21.在第一半导体图案401上,形成欧姆接触层501和502.欧姆接触层501和502在他们之间暴露出与数据驱动信号线25相对应的一部分第一半导体图案401.用于数据的数据线3和源极电极301形成在欧姆接触层501和502的整个表面上.钝化层120形成在数据线3和源极电极301上,并具有用于暴露出数据检查信号线21的第一接触孔121和用于暴露出源极电极301的第二接触孔122.用于将数据检查信号线21与源极电极301连接的第一连接部分101形成在钝化层120上.

以下,将参照图2B和3B描述栅极TFT B.

栅极检查信号线22和栅极驱动信号线24纵向延伸地形成在绝缘衬底100上,而栅极线2横向延伸.栅极绝缘层110形成在其上.第二半导体图案402在栅极绝缘层110上在横向上延伸.第二半导体图案402与栅极驱动信号线24相交,但不到达栅极检查信号线22.在第二半导体图案402上,形成欧姆接触层503和504.欧姆接触层503和504在他们之间暴露出与栅极驱动信号线24相对应的一部分第二半导体图案402.用于栅极的漏极电极302和用于栅极的源极电极303形成在欧姆接触层503和504的整个表面上.钝化层120形成在漏极电极302和源极电极303上,并具有用于暴露出栅极线2的第三接触孔123、用于暴露出漏极电极302的第四接触孔124、用于暴露出源极电极303的第五接触孔125以及用于暴露出栅极检查信号线22的第六接触孔126.用于将栅极线2与漏极电极302连接的第二连接部分102和用于将源极电极303和栅极检查信号线22连接的第三连接部分103形成在钝化层120上.

图4A和4B到图9A和9B为显示制造根据本发明第一实施例的薄膜晶体管的每个步骤的横截面图,“A”表示对应于图3A的部分,而“B”表示对应于图3B的部分.

首先,如图4A和图4B所示,在绝缘层100上,沉积栅极金属层并光刻以形成栅极线2、栅极检查信号线22、栅极驱动信号线24、数据检查信号线21和数据驱动信号线25,他们可以形成为双层.例如,沉积具有所需的物理化学特性的Cr或Mo合金层,以形成第一层,然后,沉积具有较小电阻的Al或Ag合金,以在第一层上形成第二层.

接着,如图5A和5B所示,通过化学气相沉积将由SiNx制成的栅极绝缘层110、半导体层400和欧姆接触层500依次沉积为厚、厚和厚,然后,沉积数据金属层300,接着,在其上涂敷1~2μm厚的感光膜.数据金属层可以形成为双层.例如,沉积具有所需物理化学特性的Cr或Mo合金层,以形成第一层,然后,沉积具有较小电阻的Al或Ag合金,以在第一层上形成第二层.金属层可以通过例如溅射方法沉积.此外,栅极绝缘层110由SiNx制成,半导体层400由无定形硅制成,而欧姆接触层由以高浓度掺杂诸如P的N型杂质的无定形硅制成.

接着,通过将光线经掩膜照射到感光膜900中并显影而形成感光膜图案911和912.除去感光膜900,以留下第一部分912和第二部分911,第一部分912被形成得比第二部分911薄.第一部分912位于显示区域的源极电极(未示出)和漏极电极(未示出)之间、数据线3和源极电极301之间、以及漏极电极302和源极电极303之间,而第二部分911位于将形成包括显示区域的源极和漏极电极、数据线3和源极电极301、漏极电极302和源极电极303的数据层图案3、301、302和303的部分上.在这种情况下,留在通道部分C内的第一部分912的厚度与留在数据层图案部分A中的第二部分911的厚度的比随后面描述的蚀刻条件而变化.例如,第一部分912的厚度小于第二部分911的一半,例如,小于

如上所述,有用于根据位置不同而改变感光膜的厚度的多种方法,且狭缝型或网格型图案形成在掩膜上,或通过利用半透明薄膜在其上形成半透明区域,以调节区域A内的光透射量.

在这方面中,优选的是,在狭缝中放置的图案的线宽度或图案的间隔,即,狭缝的宽度小于在利用半透明薄膜情况下用于曝光的分辨率,且在制造掩膜时,可以用具有不同透射率或不同厚度的薄膜来调节透射率.

当光线通过这种掩膜照射到感光膜上时,在直接暴露于光线中的部分内的聚合分子完全分解,而在狭缝图案或半透明薄膜所形成的部分内的聚合分子由于光照射量降低而未完全分解,且光遮蔽膜遮挡部分中的聚合物分子很难分解.接着,当感光膜显影时,只有聚合分子未分解的部分得以留下,而光稍微照射的部分比光完全未照射的部分薄.为了获得这种效果,应该适当地调节曝光时间.

利用由能够重熔(reflow)的材料制成的感光膜形成这种薄感光膜.即,它用普通的掩膜曝光,该掩膜具有完全透射光线的部分和完全不透射光线的部分,然后,显影并重熔以使得一部分感光膜流动到未剩余感光膜的部分,于是,形成薄的感光膜.

接着,感光膜900及其下层薄膜,即,数据金属层300、欧姆接触层500和半导体层400被蚀刻.数据金属层300及其下层薄膜同样保留在数据层图案部分A中,只有半导体层400留在通道部分C中,且在其他部分B内三个层300、500和400都被去除以暴露出栅极绝缘层110.

首先,如图6A和6B所示,暴露在其他部分B中的数据金属层300被去除以暴露出其欧姆接触层500.在这个步骤中使用干法蚀刻和湿法蚀刻.蚀刻在数据金属层300被蚀刻并且感光膜图案911和912几乎不蚀刻的条件下进行.然而,在干法蚀刻中不容易找到只有数据金属层300被蚀刻而感光膜图案911和912不被蚀刻的条件,因此,干法蚀刻可以在感光膜图案911和912也被蚀刻的条件下进行.在这种情况下,所需的是第一部分912的厚度比在湿法蚀刻中获得的厚度厚,以便不暴露出下面的数据金属层300.

以这种方式,如图6A和6B所示,在通道部分C和数据层图案部分A中的数据金属层300,即,仅显示区域的数据线3和源极电极301、漏极电极302和源极电极303得以留下,而其他部分B中的数据金属层被去除以暴露出其欧姆接触层500.剩余的数据金属层310和320与数据层图案3、301、302和303具有相同的形式,除了源极电极和漏极电极以外,数据线3和源极电极301、以及漏极电极302和源极电极303未分离.同时,当使用干法蚀刻时,感光图案911和912蚀刻到一定程度的厚度.

接着,如图7A和图7B所示,在其他部分B中暴露的欧姆接触层500及其下部半导体层400与第一部分一起由干法蚀刻同时去除.欧姆接触层500和半导体层400的蚀刻应该在感光膜图案911和912、欧姆接触层500以及半导体层400(半导体层和中间层几乎不具有蚀刻选择性)被同时蚀刻且栅极绝缘层110不被蚀刻的条件下进行.尤其是,优选地感光膜图案911和912与半导体图案400的蚀刻比率几乎相同.例如,当利用SF6和HCl或SF6和O2的混合气体时,该两层可以蚀刻几乎相同的厚度.当感光膜图案911和912以及半导体图案400的蚀刻比率相同时,第一部分912的厚度与半导体层400和欧姆接触层500的厚度总和相同或小于后者.

以这种方式,如图7A和图7B所示,通道部分C中的第一部分912被去除以暴露出剩余的数据金属层310和320,而在其他部分B中的欧姆接触层500和半导体层400被去除以暴露出其下部栅极绝缘层110.同时,数据层图案部分A中的第二部分911也被蚀刻,并由此变得更薄.此外,在这个步骤中完成半导体图案401和402.附图标记510和520分别表示剩余的数据金属层310和320的下部欧姆接触层图案.

然后,留在通道部分C中的数据金属层310和320表面内的感光膜残余通过灰化工艺去除.

接着,如图8A和8B所示,在通道部分C中的数据金属层310和320及其下部欧姆接触层图案510和520被蚀刻去除.他们的蚀刻可以只利用干法蚀刻实现,剩余的数据金属层310和320可以由湿法蚀刻来蚀刻,且欧姆接触层图案510和520可以由干法蚀刻来蚀刻.在前者情况下,优选的是,剩余的数据金属层310和320及其下部欧姆接触层510和520在其蚀刻选择比大的条件下进行蚀刻,这是因为,如果蚀刻选择比不大,则不容易发现蚀刻的终止点,由此不容易调节留在通道部分C内的半导体图案401和402的厚度.在一个接一个地进行于法蚀刻和湿法蚀刻的后一情况下,剩余数据金属层310和320的侧部由湿法蚀刻来蚀刻,然而,欧姆接触层图案510和520几乎不能通过干法蚀刻来蚀刻,由此形成台阶形状.作为用于蚀刻剩余的数据金属层310和320以及下欧姆接触层图案510和520的蚀刻气体的示例,存在上述的CF4和HCl混合气体或CF4和O2的混合气体.如果使用CF4和O2的混合气体,可以留下具有均匀厚度的半导体图案401和402.在这个方面,如图16B所示,部分半导体图案401和402被去除,并从而其厚度变得更薄,并且此处,感光膜图案的第二部分911也被蚀刻到一定程度的厚度.此蚀刻在栅极绝缘层110未被蚀刻的条件下进行,且优选的是感光膜图案较厚,使得第二部分911被蚀刻而不暴露出下部的数据层图案3、301、302和303。

以这种方式,显示区域的源极电极和漏极电极、数据线3和源极电极301、源极电极303和漏极电极302彼此隔离,且数据层图案3、301、302和303及其下部的欧姆接触层图案501、502、503和504同时完成.

最后,留在数据层图案部分A内的感光膜的第二部分911被去除,然而,第二部分911可以在通道部分C内的数据金属层310和320被蚀刻之后,并在其下部的欧姆接触层图案510和520被去除之前去除.

如上所述,湿法蚀刻和干法蚀刻可以一个接一个地使用,或可以仅使用干法蚀刻.后者由于使用一种蚀刻而在工艺上相对简单,但是蚀刻条件不容易找到.相反,前者相对后者复杂,但是蚀刻条件相对容易找到.

接着,钝化层120通过沉积诸如SiNx、SiOx等的无机绝缘层,或通过涂敷有机绝缘层,或通过由化学气相沉积来生长a-Si:C:O薄膜或a-Si:O:F薄膜来形成.在此,a-Si:C:O薄膜或a-Si:O:F薄膜为无机绝缘层,并具有非常低的介电常数,该介电常数在2到4的范围内.在a-Si:C:O薄膜的情形下,SiH(CH3)3、SiO2(CH3)4、(SiH)4O4(CH3)4、Si(C2H5O)4等用作碱性源(basicsource),且诸如N2O或O2的氧化剂和诸如Ar或He的混合气体被流动以沉积a-Si:C:O.另外,在a-Si:C:F的情况下,O2和SiH4、SiF4的混合气体被流动以将其沉积。在此,CF4可以作为辅助氟源而加入.

接着,如图9A和9B所示,钝化层120与栅极绝缘层110一同由光刻来蚀刻,以形成第一到第六接触孔,用于分别暴露出数据检查信号线21、源极电极301、栅极线2、漏极电极302和栅极检查信号线22.在这种情况下,还形成了用于暴露栅极焊点(未示出)、数据焊点(未示出)和漏极电极(未示出)的接触孔(未示出).

最后,如图3A和3B所示,具有到厚度的ITO或IZO被沉积并光刻,以形成第一到第三连接部分101、102和103.同样,在这个步骤中还形成显示区域的像素电极(未示出)、连接到栅极焊点的辅助栅极焊点(未示出)和连接到数据焊点上的辅助数据焊点(未示出).

由于Cr蚀刻剂可以用作蚀刻剂,因此在用IZO形成第一到第三连接部分101、102和103、像素电极、辅助栅极焊点和辅助数据焊点的地方,防止了在形成这些元件的工序中通过接触孔暴露的数据线或栅极线金属被腐蚀.作为这种Cr蚀刻剂,存在HNO3/(NH4)2Ce(NO3)6/H2O等.另外,优选的是IZO在室温到200℃的温度下沉积,以便使接触部分的接触电阻减至最小,且用于形成IZO膜的靶包括In2O3和ZnO,且ZnO含量在15-20atm%范围内.

同时,优选的是氮被用作ITO或IZO沉积之前的预热中采用的气体,这是因为防止了金属氧化物膜形成在通过接触孔121、122、123、124、125和126暴露出金属膜的上侧上.

已经描述了应用利用四次光刻工艺制造TFT面板的方法时形成用于检查的TFT的工艺及其结构.将在下面描述利用五次光刻工艺制造TFT面板的方法及其结构.

首先将描述其结构.

图10A和10B是根据本发明第二实施例的薄膜晶体管的布线图,分别为图1所示的A和B,而图11A和B分别是沿图10A的线XIa-XIa′和图10B的线XIb-XIb′截取的横截面图.

首先,将参照图10A和图11A描述用于检查的数据TFT A.

数据检查信号线21和数据驱动信号线25横向延伸地形成在绝缘衬底100上,而栅极绝缘层110形成在数据检查信号线21和数据驱动信号线25上.在栅极绝缘层110上,第一半导体图案401在数据驱动信号线25的上侧上形成为岛形.欧姆接触层501和502形成在第一半导体图案401上,并在它们之间暴露出与数据驱动信号线25相对应的一部分第一半导体401.横向延伸的用于数据的数据线3和源极电极301形成在欧姆接触层501和502上.数据线3延伸到一个欧姆接触层501上,而源极电极301具有与其他欧姆接触层501相同的图案.钝化层120形成在数据线3和源极电极301上,并具有用于暴露出数据检查信号线21的第一接触孔121和用于暴露出源极电极301的第二接触孔122.用于将数据检查信号线21与源极电极301相连接的第一接触部分101形成在钝化层120上.

接着,将参照图10B和图11B描述用于检查的栅极TFT B.

栅极检查信号线22和栅极驱动信号线24纵向延伸地形成在绝缘衬底100上,而栅极线2在横向上形成.栅极绝缘层110形成在栅极线2、栅极检查信号线22和栅极驱动信号线24上.在栅极绝缘层110上,第二半导体图案402形成为栅极驱动信号线24上侧上的岛形状.欧姆接触层503和504形成在第二半导体图案402上,并在它们之间暴露出与栅极驱动信号线24相对应的一部分第二半导体图案402.用于栅极的漏极电极302和源极电极303形成在欧姆接触层503和504上.漏极电极302延伸到欧姆接触层503上,而源极电极303延伸到另一个欧姆接触层504上.钝化层120形成在漏极电极302和源极电极303上,并具有用于暴露出栅极线2的第三接触孔123、用于暴露出漏极电极302的第四接触孔124、用于暴露出源极电极303的第五接触孔125和用于暴露出栅极检查信号线22的第六接触孔.用于将栅极线2与漏极电极302连接的第二连接部分102和用于将源极电极303与栅极检查信号线22连接的第三连接部分103形成在钝化层120上.

然后,将描述制造具有如此结构的TFT的方法.

首先,在绝缘衬底上沉积并构图栅极金属层,以形成栅极线2、栅极检查信号线22、栅极驱动信号线24、数据检查信号线21和数据驱动信号线25.

接着,由SiNx制成的栅极绝缘层110、由无定形硅制成的半导体层和由掺杂的无定形硅制成的欧姆接触层这三个层依次沉积,然后,蚀刻半导体层和欧姆接触层以形成具有岛形状的半导体层401和402、以及具有与半导体层401和402相同形状的欧姆接触层图案.

接着,沉积并光刻数据金属层,以形成数据层图案,其包括与栅极线2相交的数据线、用于数据的源极电极301、用于栅极的漏极电极302和用于栅极的源极电极303。

然后,未被数据层图案阻挡的欧姆接触层得以蚀刻,以被分割成围绕栅极驱动信号线24和数据驱动信号线25的相对侧,从而暴露出欧姆接触层图案501、502、503和504中的半导体层图案401和402.可以进行氧气等离子体处理,以便使半导体图案401和402的暴露表面稳定.

接着,通过沉积诸如SiNx、SiOx等的无机绝缘层,或通过沉积有机绝缘层,或通过由化学气相沉积生长a-Si:C:O薄膜或a-Si:O:F薄膜来形成钝化层120.

然后,通过光刻,一起构图钝化层120与栅极绝缘层110,以形成第一到第六接触孔121、122、123、124、125和126.

最后,如图11A和11B所示,沉积和光刻ITO膜或IZO膜,以形成第一至第三连接部分101、102和103.

已经描述了其中每个用于检查的栅极TFT和用于检查的数据TFT施加有相同的扫描信号和图像信号以便被同时驱动的TFT面板.然而,不可能探测到相邻导线之间产生的短路.以下将描述具有能够检测相邻导线之间产生的短路的结构的TFT面板.

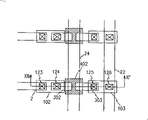

图12是根据本发明第三实施例的薄膜晶体管面板的电路图.

多条栅极线2在横向上延伸,而被绝缘以在纵向上与栅极线2相交的多条数据线3形成在绝缘衬底100上.连接到栅极驱动IC的多个栅极焊点20连接到栅极线2的第一端上,而连接到数据驱动IC上的多个数据焊点30连接到数据线3的第二端上.栅极线2和数据线3彼此相交,以限定一像素区域,且一组像素区域形成显示区域17.用于检查的第一和第二栅极薄膜晶体管(以下称为TFT)(B1、B2)连接到相对栅极线2的第一端的第三端上,而用于检查的第一和第二数据TFT(A1、A2)连接到与数据线3的第二端相对的第四端上.第一栅极TFT B1连接到第一栅极检查信号线22a和栅极驱动信号线24上,而第二栅极TFT B2连接到第二栅极信号线22b和栅极驱动检查信号线24上.另外,第一数据TFT A1连接到第一数据检查信号线21a和栅极驱动信号线25上,而第二数据TFT A2连接到第二数据检查信号线21b和数据驱动信号线25上.栅极线2连接到第一和第二栅极TFT B1和B2的漏极电极上,而栅极驱动信号线24连接到第一和第二栅极TFT B1和B2的源极电极上.第一检查信号线22a连接到第一栅极TFT B1的源极电极上,而第二栅极检查信号线连接到第二栅极TFT B2的源极电极上.另外,数据线3连接到第一和第二数据TFT A1和A2的漏极电极上,而数据驱动信号线25连接到第一和第二数据TFT A1和A2的栅极电极上.第一数据检查信号线21连接到第一数据TFT A1的源极电极上,而第二数据检查信号线21b连接到第二数据TFT A2的源极电极上.第一和第二数据检查信号线21a和21b、第一和第二栅极检查信号线22a和22b、栅极驱动信号线24和数据驱动信号线25连接到用于检查的第一到第六数据焊点32a、32b、39a、39b、41和40的相应一端上.在这种情况下,数据驱动信号线24通过第五焊点41连接到栅极Voff端子52上,而数据驱动信号线25连接到数据Voff端子51上,即,栅极TFT B1和B2的所有栅极电极连接到栅极Voff端子52上,而数据TFT A1和A2的所有栅极电极连接到数据Voff端子51上.Voff端子51和52通过在后面的步骤中经FPC连接到Voff电压源上而保持恒定为Voff电压。从而,TFT A和B一直处于与断开状态相同的关状态,于是,不需要进行金刚石切割或激光切割来将用于检查的导线与数据线和栅极线分开.

包括公共电极、黑矩阵和滤色片的衬底200面对衬底100.

同时,由于栅极线2依次连接到第一栅极TFT B1和第二栅极TFT B2上,且数据线3依次连接到第一数据TFT A1和第二数据TFT A2上,所以可以通过单独驱动TFT A1、A2、B1和B2依次驱动数据线3和栅极线2.于是,可以探测到栅极线2和数据线3中的短路.

图13是根据本发明第四实施例的TFT面板的电路图.

在根据本发明第四实施例的TFT面板中,用于检查的数据TFT依次连接到三条数据检查信号线21R、21G和21B上.栅极信号线22a和22b延伸,以至于栅极信号线22a和22b的焊点39a和39b形成在与数据检查信号线21R、21G和21B的焊点32R、32G和32B相邻的位置上.

由于数据TFT依次连接到三条数据检查信号线21R、21G和21B上,所以可以检查红、绿和蓝每种颜色.通过在与数据检查信号线21R、21G和21B的焊点32R、32G和32B相邻的位置上形成栅极信号线22a和22b的焊点39a和39b,便于与用于检查的驱动装置进行连接,并且,这可以应用于上述的第一到第三实施例和后面描述的第五实施例。

图14是根据本发明第五实施例的TFT面板的电路图.

如第四实施例中一样,在第五实施例中,各颜色的检查通过将用于检查的数据TFT连接到三条数据驱动信号线25R、25G和25B上而成为可能,然而,其连接状态与第四实施例中的不同.即,在第四实施例中用于检查的数据TFT的源极电极依次连接到三条数据检查信号线21R、21G和21B上,但是用于检查的数据TFT的栅极电极依次连接到三条数据驱动信号线25R、25G和25B上.另外,如第一实施例中的一样,用于检查的栅极TFT都连接到栅极检查信号线22和栅极驱动信号线24上.在这种结构中,可以探测数据线之间的短路.

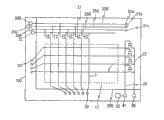

在以下的第六实施例中,形成了能够利用逻辑电路进行VI的用于液晶显示器的TFT面板.

图15是根据本发明第六实施例的薄膜晶体管的电路图.图16是栅极驱动电路的移位寄存器的框图,图17是一级移位寄存器中的详细电路图,图18是图17的相应部分的时钟图(timing diagram),图19是图15的用于VI的逻辑电路的详细电路图.

作为示例,以下将描述用于LCD的TFT面板.

参照图15,在TFT面板10上形成显示区域150,该区域包括多个像素、栅极驱动电路170、用于VI的逻辑电路180、作为数据驱动电路的一部分的包括多个晶体管ST2和ST3的传输门部分120TG、多个用于VI的信号线111、和多个信号焊点Von、Voff、VCK1、VCK2、VST、CON1、CON2、CON3、TG1、TG2和Vcom.这些元件在形成TFT和像素电极的过程中一同形成.

显示区域150包括在行的方向上延伸的m条数据线DL1~DLm,和在列的方向上延伸的n条栅极线GL1~GLn.

开关晶体管ST1形成在数据线和栅极线的交点上.开关晶体管ST1的漏极连接到数据线Dli上,而其栅极连接到栅极线Gli上.开关晶体管ST1的源极连接到透明像素电极PE上.液晶LC位于透明像素电极PE和滤色片(未示出)之间形成的透明公共电极中.

透射的光量通过根据施加到透明像素电极PE和透明公共电极CE上的电压来控制液晶的排列而予以调节,从而呈现出各像素的灰度.

将参照图16到18详细描述图15所示的栅极驱动电路170.

栅极驱动电路170包括移位寄存器.图16所示的移位寄存器174具有极联连接的多个级SRC1~SRC193.即,各级的相应的输出端子OUT连接到下一级的输入端子IN上。这些级包括具有与栅极线数量一致的级数量(在本实施例中为192)的级SRC1~SRC192和一个虚级(dummy stage)SRC193构成.每级具有一输入端子IN、一输出端子OUT、一控制端子CT、一时钟信号输入端子CK、一第一电源电压端子VSS和一第二电源电压端子VDD.在这种情况下,第一级SRC1的输入端子IN连接到VST焊点上,第一电源电压端子VSS连接到Voff焊点,而第二电源电压端子VDD连接到Von焊点.另外,级SRC1~SRC193的时钟信号输入端子CK连接到VCK1或VCK2.

图18所示的起始信号ST输入到第一级的输入端子上.在此,起始信号为与垂直同步信号同步的脉冲信号.

各级的输出信号OUT1~OUT192连接到相关的栅极线上.奇数级SRC1和SRC3设置有第一时钟信号CK,而偶数级SRC2和SRC4设置有第二时钟信号CKB.第一时钟信号CK和第二时钟信号CKB彼此反相.

每级(例如SRC1)的控制端子被提供给下一级(例如SRC2)的输出信号(例如OUT2)作为控制信号.即,输入到控制端子CT的控制信号由其本身的工作周期延迟。

因此,由于各级的输出信号以有功间隔(active interval)(高态(high state))依次产生,所以选出对应于各输出信号的有功间隔的水平线.

参照图17,将详细描述各级SRC1~SRC193的电路的示例性结构.

如图17所示,每级的移位寄存器174包括上拉装置181、下拉装置182、上拉驱动装置184、下拉驱动装置186、防浮置装置188和防导通装置190.

上拉装置181包括上拉NMOS晶体管NT1,其具有连接到时钟信号输入端子CK的漏极,连接到第一节点N1的栅极、以及连接到输出端子OUT的源极.

下拉装置182包括下拉NMOS晶体管NT2,其具有连接到输出端子OUT的漏极、连接到第二节点N2的栅极、以及连接到第一电源电压VSS的源极.

上拉驱动装置184包括电容器C和NMOS晶体管NT3~NT5.电容器连接在第一节点N1和输出端子OUT之间.晶体管NT3具有共同连接到输入端子IN上的漏极和栅极、以及连接到第一节点N1上的源极.晶体管NT4具有连接到第一节点N1上的漏极、连接到第二节点N2上的栅极和连接到第一电源电压VSS上的源极.晶体管NT5具有连接到第一节点N1上的漏极、连接到控制端子CT上的栅极、以及连接到第一电源电压VSS上的源极.

下拉驱动装置186包括两个NMOS晶体管NT6和NT7.晶体管NT6具有连接到第二电源电压VDD上的漏极、连接到控制端子CT上的栅极、以及连接到第二节点N2上的源极.晶体管NT7具有连接到第二节点N2上的漏极、连接到输入端子IN上的栅极、以及连接到第一电源电压VSS上的源极.

防浮置装置188包括NMOS晶体管NT8,其具有共同连接到第二电源电压VDD上的漏极和栅极、以及连接到第二节点N2上的源极.晶体管NT18被构造成尺寸相对小,例如为晶体管NT7的二十分之一.

防导通装置190包括NMOS晶体管NT9,其具有连接到第二节点N2上的漏极、连接到输出端子OUT上的栅极和连接到第一电源电压VSS上的源极.晶体管NT9的尺寸相对于晶体管NT7大约为1∶2.

如图18所示,当第一和第二时钟信号CK和CKB、以及扫描起始信号ST施加到移位寄存器170上时,第一级SRC1响应扫描起始信号ST的前边,而将第一时钟信号的高电平间隔延迟特定的时间(Tdr1),然后向输出端产生输出信号.

扫描起始信号ST的有功间隔相对于高电平间隔具有大约1/4周期的超前相(leading phase).起始信号ST的有功间隔被分成从脉冲的前边或上升边开始的启动时间(set time)Ts1和从脉冲的后边或下降边开始的保持时间Ts2.

于是,输出信号OUT1的前边具有大约2~4μs延迟的前边,即,自保持时间Ts2的起始点的上升边.也就是说,第一时钟信号CK的有功间隔或高电平间隔被延迟Tdr1,以在输出端子OUT中产生.

这种延迟特征的原因为上拉驱动装置184的电容器C在前边处从晶体管NT4的截止状态开始经由晶体管NT3充电,然后,在电容器C的充电电压被充到超过上拉晶体管NT1的栅极-源极的阈值电压后,上拉晶体管导通,且第一时钟信号CK的高电平间隔开始在输出端子产生.

当在输出端子的时钟信号的高电平间隔开始产生时,这个输出电压在电容器C中自举(bootstrap),以将上拉晶体管的栅极电压增大到超过导通电压VDD.于是,NMOS晶体管的上拉晶体管NT1保持在全导通状态.

另一方面,在下拉驱动装置186中,由于晶体管NT7在晶体管NT6的截止状态下截止,所以第二节点N2的电压降低到第一电源电压VSS。在这种情况下,防浮置装置188的晶体管NT8保持为导通状态,然而,由于导通的晶体管NT7比晶体管NT8约大二十倍,所以第二节点N2在第二电源电压VDD的状态下降低到第一电源电压VSS.由此,下拉晶体管NT2从导通状态变为截止状态.

当导通电压(VON=VDD)在输出端子OUT上产生时,防导通装置190的晶体管NT9导通,且用第一电源电压VSS驱动第二节点N2的效率增大约50%.因此,下拉晶体管的漏极-源极寄生电容器可以防止第二节点N2的电压在输出信号的上升-移位处增大.于是,可以防止在输出信号的上升-移位处导通下拉晶体管的误操作.

输出端子OUT的输出信号OUT1由第一时钟信号CK的工作周期产生.

当输出端子OUT的输出信号电压处于截止电压(VOFF=VSS)状态时,晶体管NT9截止,以通过晶体管NT8只将第二电源电压VDD提供到第二节点上,并由此第二节点N2的电压开始从第一电源电压VSS上升到第二电源电压VDD.当第二节点的电压开始上升时,晶体管NT4开始导通,由此,电容器的充电电压开始通过晶体管NT4放电,于是,上拉晶体管NT1也开始截止.

此后,由于提供至控制端子CT的下一级的输出信号增大到导通电压,所以这导致晶体管NT5和NT6导通.因此,第二节点N2的电压快速增大到由晶体管NT6和NT8所提供的第二电源电压VDD,而第一节点N1的电压通过晶体管NT4和NT5快速下降到第一电源电压VSS.

于是,上拉晶体管NT1截止,而下拉晶体管NT2导通,从而输出端子OUT从导通电压Von降低到第一电源电压的截止电压Voff.

即使提供给控制端子CT的下一级的输出信号处于低电平而截止晶体管NT6,但是第二节点N2通过晶体管保持为第二电源电压的偏置状态,且第一节点N1通过维持导通状态的晶体管NT4而保持为第一电源电压VSS的偏置状态.因此,即使晶体管NT2和NT4的阈值电压由于长期使用而增大,也能稳定工作,而不会由于第二节点N2的电压保持为第二电源电压VDD而出现截止晶体管NT2的误操作.

接着,将参照图19详细描述图15所示的用于VI的逻辑电路180.

逻辑电路180包括两排NOR(或非)门,在第一排中的或非门NOR1的第一输入端子相应地连接到各级SRC1~SRC192的输出端子上,而其第二输入端子全连接到CON1焊点上.第二排中的或非门NOR2和NOR3的第一输入端子相应地连接到或非门NOR1的输出端子上,其第二输入端子连接到CON2焊点或CON3焊点上.在本发明这个实施例中,奇数列中的或非门NOR2连接到CON2焊点上,而偶数列中的或非门NOR3连接到CON3焊点上.

在进行视觉检查(VI)时,没有信号从栅极驱动电路170的级SRC1~SRC2输入.因此,第一输入端子的信号总是处于关(0)状态.在这种情况下,当开(1)信号经由CON1焊点输入到第二输入端子上时,在NOR1的输出端子处产生关(0)信号.也就是说,关(0)信号输入到NOR2和NOR3的第一输入端子上.因此,取决于输入到其第二输入端子上的信号,只有奇数列或只有偶数列被导通(1),或者他们都导通(1).当关(0)信号通过CON2焊点输入到NOR2的第二输入端子上时,在奇数列的栅极线处产生开(1)信号,且当开(1)信号经由CON2焊点输入到其上时,在奇数列内的栅极线处产生关(0)信号.当关(0)信号经由CON3焊点输入到NOR3的第二输入端子上时,在偶数列的栅极线处产生开(1)信号,且当开(1)信号经由CON3焊点输入其上时,在偶数列内的栅极线处产生关(0)信号.

当之后驱动液晶显示器时,关(0)信号施加到所有CON1、CON2和CON3焊点.在这种方式中,由于施加到栅极线上的信号根据从栅极驱动电路170的各级SRCI~SRC192输出的信号决定,因此用于VI的逻辑电路180等同于不存在.

上述逻辑表示在表1中.

表1

| CON1 | CON2 | CON3 | |

| 奇数导线开 | 1 | 0 | 1 |

| 偶数导线开 | 1 | 1 | 0 |

| 所有导线开 | 1 | 0 | 0 |

| 所有导线关 | 1 | 1 | 1 |

| 在面板工作时 | 0 | 0 | 0 |

现在,将描述用于VI的数据线的引线.

如图15所示,作为驱动电路一部分的传输门部分120形成在TFT面板上,而传输门的输入端子全都连接到短路条111上.各TFT ST2和ST3的源极电极连接到短路条111上,作为传输门的输入端子,其漏极电极连接到各数据线DL1和DL2上,且其栅极电极连接到两个传输门端子TG1和TG2中的一个上.在图15中,奇数TFT ST2连接到TG1上,而偶数TFT ST3连接到TG2上.

当在这种结构中进行VI时,图像信号经由Vs端子输入到短路条111上.传输门部分120的TFT ST2和ST3可以根据输入到TG1和TG2端子上的信号而导通或截止,以将图像信号提供到奇数数据线或偶数数据线上,或者所有数据线上.

本发明第六实施例实现了能够利用用于VI的逻辑电路部分180区别地驱动奇数栅极线和偶数栅极线的2G和能够利用短路条111和传输门部分120区别地驱动奇数数据线和偶数数据线的2D.从而,可以探测到相邻数据线DL1~DLn以及相邻栅极线GL1~GLn之间的短路.

在图15中,A表示安装数据驱动集成电路(IC)的位置,而B表示激光照射以在完成VI后将短路条111与传输门部分120分开的线.

当VI在如上所述的构造下进行时,从各焊点输入的信号表示在表2中.

表2

| 序号 | 焊点名称 | 施加到焊点上的电压 |

| 1 | V<sub>on</sub> | V<sub>on</sub> |

| 2 | V<sub>off</sub> | V<sub>off</sub> |

| 3 | Vcom | Vcom |

| 4 | CON1 | V<sub>on</sub> |

| 5 | CON2 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 6 | CON3 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 7 | Vs | 图像信号 |

| 8 | TG1 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 9 | TG2 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

将描述本发明的第七实施例.

图20是根据本发明第七实施例的TFT的电路图.

本发明的第七实施例与第六实施例相同,除了没有传输门部分且短路条为两个以外.在第七实施例中,奇数数据线连接到第一短路条112上,而偶数数据线连接到第二短路条113上.第一短路条112和第二短路条114每一条均连接到Vs1和Vs2端子上以形成2D结构.本发明的第七实施例要在TFT面板上仅集成了栅极驱动电路的情况下实现2G、2D和VI结构.

当在如上所述构造下进行VI时,从各焊点输入的信号表示在表3中.

表3

| 序号 | 焊点名称 | 施加到焊点上的电压 |

| 1 | V<sub>on</sub> | V<sub>on</sub> |

| 2 | V<sub>off</sub> | V<sub>off</sub> |

| 3 | Vcom | Vcom |

| 4 | CON1 | V<sub>on</sub> |

| 5 | CON2 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 6 | CON3 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 7 | Vs1 | 图像信号1 |

| 8 | Vs2 | 图像信号2 |

图21是根据本发明第八实施例的TFT面板的电路图.

本发明的第八实施例与第六实施例相同,不同之处在于没有短路条,且取而代之的是形成了用于检查的第一和第二数据TFT A1和A2.

如图21所示,第一数据TFT A1连接到第一数据检查信号线21a和数据驱动信号线25上,而第二数据TFT A2连接到第二数据检查信号线21b和数据驱动信号线25上.另外,数据线DL1~DLn连接到第一和第二数据TFT A1和A2的漏极电极上,而数据驱动信号线25连接到第一和第二数据TFT A1和A2的栅极电极上.第一数据检查信号线21a连接到第一数据TFT A1的源极电极上,而第二数据检查信号线21b连接到第二数据TFT A2的源极电极上.用于检查的第一到第三焊点32a、32b和40连接到每条第一和第二检查数据线21a和21b以及数据驱动信号线25的一端上.在这种情况下,数据驱动信号线25连接到数据Voff端子51上.也就是说,数据TFT A1和A2的栅极电极都连接到数据Voff端子51上.Voff端子51通过经由后面模块化工艺中的FPC连接到Voff电压供给电路上而一直保持Voff电压.从而,数据TFT A1和A2处于相同的断开状态,这是由于在液晶显示器驱动时其一直保持在关状态.于是,不需要进行金刚石切割或激光切割来将用于检查的导线与数据线和栅极线分割开.

同时,由于数据线DL1~DLn依次连接到第一数据TFT A1和第二数据TFT A2上,所以可以通过单独驱动TFT A1和A2来依次驱动数据线DL1~DLn.于是,可以探测到相邻数据线DL1~DLn中的短路.

当在如上所述的这种结构中进行VI时,从各焊点输入的信号表示在表4中.

表4

| 序号 | 焊点名称 | 施加到焊点上的电压 |

| 1 | V<sub>on</sub> | V<sub>on</sub> |

| 2 | V<sub>off</sub> | V<sub>off</sub> |

| 3 | Vcom | Vcom |

| 4 | CON1 | V<sub>on</sub> |

| 5 | CON2 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 6 | CON3 | V<sub>on</sub>或V<sub>off</sub>(根据要被驱动的奇数栅极线或偶数栅极线而变化) |

| 7 | 40 | V<sub>on</sub> |

| 8 | 32a | 图像信号1 |

| 9 | 32b | 图像信号2 |

同时,省略传输门电路的结构在图21中也可以实现.

图22是根据本发明第九实施例的TFT面板的电路图.

根据本发明第九实施例的TFT面板与第八实施例的相同,除了省略逻辑电路以外.

可以通过施加如表5所示的电压到具有这种结构的TFT的各焊点上来进行1G和2D VI.也就是说,可以通过使所有的栅极线GL1~GLn处于开状态并通过依次导通或截止数据线DL1~DLn来进行VI.

表5

| 序号 | 焊点名称 | 施加到焊点上的电压 |

| 1 | V<sub>on</sub> | V<sub>on</sub> |

| 2 | V<sub>off</sub> | V<sub>on</sub> |

| 3 | Vcom | Vcom |

| 4 | VST | V<sub>on</sub> |

| 5 | VCK1 | V<sub>on</sub> |

| 6 | VCK2 | V<sub>on</sub> |

| 7 | 40 | V<sub>on</sub> |

| 8 | 32a | 图像信号1 |

| 9 | 32b | 图像信号2 |

同样,在根据本发明第九实施例的TFT面板中,与第八实施例类似,Voff端子51通过经由后面模块化工艺中的FPC连接到Voff电压供给电路上而一直保持Voff电压.从而,数据TFT A1和A2处于相同的断开状态,这是由于在液晶显示器驱动时起总是保持在关状态下.于是,不需要进行金刚石切割或激光切割来将用于检查的导线与数据线和栅极线分割开.

图23是根据本发明第十实施例的TFT面板的电路图.

根据本发明第十实施例的TFT面板与第七实施例的相同,除了省略了用于VI的逻辑电路部分以外.

可以通过将如表6所示的电压施加到具有这种结构的TFT的各焊点上来进行1G和2D VI.也就是说,可以通过使所有的栅极线GL1~GLn处于开状态,并通过依次导通或截止数据线DL1~DLn来进行VI.

本发明第十实施例需要进行激光切割或金刚石切割,以在进行VI后将短路条112和113与数据线分开。

上述实施例可直接应用于TFT面板上任何类型的驱动IC形成部分,如多晶硅TFT面板或无定形硅驱动IC面板.

表6

| 序号 | 焊点名称 | 施加到焊点上的电压 |

| 1 | V<sub>on</sub> | V<sub>on</sub> |

| 2 | V<sub>off</sub> | V<sub>on</sub> |

| 3 | Vcom | Vcom |

| 4 | VST | V<sub>on</sub> |

| 5 | VCK1 | V<sub>on</sub> |

| 6 | VCK2 | V<sub>on</sub> |

| 7 | Vs1 | 图像信号1 |

| 8 | Vs2 | 图像信号2 |

虽然本发明已参照示例性实施例加以说明,但其不限于上面公开的实施例.本发明的范围包括涵盖于所附权利要求书中的各种修改及其等价物.

如上所述,通过将用于检查的导线经由用于检查的TFT连接到数据线和栅极线上,并且在检查之后,通过将Voff电压施加到用于检查的TFT上,检查得以进行,该TFT保持为与切断相同的状态,而不需要单独的切割过程.因此,可以除去切割用于检查的导线的额外工序并解决由切割导致的导线腐蚀.

同时,根据本发明,可以在集成了栅极驱动IC的TFT面板中进行2G和2D或1G和2D的视觉检查.

Claims (6)

1. 一种薄膜晶体管面板,包括:

包括显示区域和围绕区域的绝缘衬底;

形成在绝缘衬底上的多条栅极线;

形成在绝缘衬底上并与栅极线相交以限定显示区域的多条数据线;

形成在围绕区域上并连接到栅极线上的栅极驱动电路;以及

插在栅极驱动电路和栅极线之间并具有多个第一到第三或非门的用于视觉检查的逻辑电路,

其中,用于视觉检查的逻辑电路的第一或非门的第一输入端子连接到栅极驱动电路的输出端子上,而其第二输入端子连接到第一控制端子上,且其输出端子连接到第二或第三或非门的第一输入端子上,而第二或非门的第二输入端子连接到第二控制端子上,且其输出端子连接到奇数栅极线上,而第三或非门的第二输入端子连接到第三控制端子上,且其输出端子连接到偶数栅极线上,其中由通过所述第一至第三控制端子施加的信号选择栅极线。

2. 如权利要求1所述的薄膜晶体管面板,还包括:

形成在围绕区域上的传输门电路,其输出端子连接到数据线上;以及

连接到传输门电路的输入端子上的短路条。

3. 如权利要求1所述的薄膜晶体管面板,还包括:

形成在绝缘衬底的围绕区域上并具有连接到数据线上的输出的传输门电路;

形成在绝缘衬底的围绕区域上并连接到Voff电压施加端子上的驱动信号线;

形成在绝缘衬底的围绕区域上的检查信号线;以及

用于检查的薄膜晶体管,其具有连接到数据线上的漏极电极、连接到检查信号线上的源极电极、以及连接到驱动信号线上的栅极电极,

其中Voff电压是用于检查的薄膜晶体管的截止电压。

4. 如权利要求3所述的薄膜晶体管面板,其中,连接到用于检查的薄膜晶体管上的检查信号线包括第一和第二检查信号线,且用于检查的薄膜晶体管交替地连接到第一检查信号线和第二检查信号线上。

5. 如权利要求1所述的薄膜晶体管面板,还包括:

连接到奇数数据线上的第一短路条;以及

连接到偶数数据线上的第二短路条。

6. 如权利要求1所述的薄膜晶体管面板,还包括:

形成在绝缘衬底的围绕区域上并连接到Voff电压施加端子上的驱动信号线;

形成在绝缘衬底的围绕区域上的检查信号线;以及

用于检查的薄膜晶体管,其具有连接到数据线上的漏极电极、连接到检查信号线上的源极电极、以及连接到驱动信号线上的栅极电极,

其中Voff电压是用于检查的薄膜晶体管的截止电压。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR62619/01 | 2001-10-11 | ||

| KR1020010062619A KR100816336B1 (ko) | 2001-10-11 | 2001-10-11 | 박막 트랜지스터 기판 및 그 제조 방법 |

| KR62619/2001 | 2001-10-11 | ||

| KR81049/01 | 2001-12-19 | ||

| KR81049/2001 | 2001-12-19 | ||

| KR1020010081049A KR100864487B1 (ko) | 2001-12-19 | 2001-12-19 | 비쥬얼 인스펙션 수단을 구비한 박막 트랜지스터 기판 및비쥬얼 인스펙션 방법 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2007101996289A Division CN101221958B (zh) | 2001-10-11 | 2002-06-13 | 具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1412735A CN1412735A (zh) | 2003-04-23 |

| CN100414405C true CN100414405C (zh) | 2008-08-27 |

Family

ID=26639384

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB02122790XA Expired - Lifetime CN100414405C (zh) | 2001-10-11 | 2002-06-13 | 具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6774398B2 (zh) |

| JP (2) | JP2003121867A (zh) |

| CN (1) | CN100414405C (zh) |

| TW (1) | TW543145B (zh) |

Families Citing this family (60)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4006304B2 (ja) * | 2002-09-10 | 2007-11-14 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| US7956976B1 (en) | 2002-09-10 | 2011-06-07 | Hitachi Displays, Ltd. | Liquid crystal display device |

| JP2004163493A (ja) * | 2002-11-11 | 2004-06-10 | Sanyo Electric Co Ltd | 表示装置 |

| KR100917009B1 (ko) * | 2003-02-10 | 2009-09-10 | 삼성전자주식회사 | 트랜지스터의 구동 방법과 쉬프트 레지스터의 구동 방법및 이를 수행하기 위한 쉬프트 레지스터 |

| KR100965176B1 (ko) * | 2003-04-07 | 2010-06-24 | 삼성전자주식회사 | 디지털 엑스레이 디텍터용 어레이 패널 및 이의 제조 방법 |

| KR100984345B1 (ko) * | 2003-05-30 | 2010-09-30 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치 |

| US7714820B2 (en) | 2003-06-27 | 2010-05-11 | Samsung Electronics Co., Ltd. | Contact structure of conductive films and thin film transistor array panel including the same |

| KR100951357B1 (ko) * | 2003-08-19 | 2010-04-08 | 삼성전자주식회사 | 액정 표시 장치 |

| KR100560787B1 (ko) * | 2003-11-05 | 2006-03-13 | 삼성에스디아이 주식회사 | 유기전계발광표시장치 |

| JP4546723B2 (ja) * | 2003-12-10 | 2010-09-15 | シャープ株式会社 | 表示装置用基板及びそれを用いた液晶表示装置 |

| KR100982122B1 (ko) * | 2003-12-30 | 2010-09-14 | 엘지디스플레이 주식회사 | 수평 전계 인가형 박막 트랜지스터 기판의 불량 화소암점화 방법 |

| US7391053B2 (en) * | 2004-05-28 | 2008-06-24 | Toshiba Matsushita Display Technology Co., Ltd. | Inspection substrate for display device |

| KR20050117303A (ko) * | 2004-06-10 | 2005-12-14 | 삼성전자주식회사 | 표시 장치 |

| KR101075599B1 (ko) * | 2004-06-23 | 2011-10-20 | 삼성전자주식회사 | 표시장치 |

| TWI382264B (zh) * | 2004-07-27 | 2013-01-11 | Samsung Display Co Ltd | 薄膜電晶體陣列面板及包括此面板之顯示器裝置 |

| JP4744824B2 (ja) * | 2004-08-06 | 2011-08-10 | 東芝モバイルディスプレイ株式会社 | 表示装置、表示装置の検査方法、及び、表示装置の検査装置 |

| JP2006078764A (ja) * | 2004-09-09 | 2006-03-23 | Toshiba Matsushita Display Technology Co Ltd | 表示装置 |

| JP4790292B2 (ja) | 2004-10-25 | 2011-10-12 | 三星電子株式会社 | アレイ基板及びこれを有する表示装置 |

| KR101100883B1 (ko) | 2004-11-08 | 2012-01-02 | 삼성전자주식회사 | 박막 트랜지스터 표시판 |

| KR101093229B1 (ko) | 2005-01-06 | 2011-12-13 | 삼성전자주식회사 | 어레이 기판 및 이를 갖는 표시장치 |

| US7714589B2 (en) * | 2005-11-15 | 2010-05-11 | Photon Dynamics, Inc. | Array test using the shorting bar and high frequency clock signal for the inspection of TFT-LCD with integrated driver IC |

| KR101209042B1 (ko) * | 2005-11-30 | 2012-12-06 | 삼성디스플레이 주식회사 | 표시 장치 및 그 검사 방법 |

| KR101115026B1 (ko) * | 2006-01-10 | 2012-03-06 | 삼성전자주식회사 | 게이트 드라이버와 이를 구비한 박막 트랜지스터 기판 및액정 표시 장치 |

| US8174478B2 (en) * | 2006-06-12 | 2012-05-08 | Samsung Electronics Co., Ltd. | Gate driving circuit and display apparatus having the same |

| KR101275248B1 (ko) * | 2006-06-12 | 2013-06-14 | 삼성디스플레이 주식회사 | 게이트 구동회로 및 이를 갖는 표시장치 |

| KR100996536B1 (ko) * | 2006-06-23 | 2010-11-24 | 엘지디스플레이 주식회사 | 액정표시장치의 광센서 회로 및 이를 이용한 백라이트제어장치 |

| JP2008026507A (ja) * | 2006-07-20 | 2008-02-07 | Sony Corp | 表示装置および表示装置の検査方法 |

| JP4860699B2 (ja) * | 2006-08-31 | 2012-01-25 | シャープ株式会社 | 表示パネルおよびそれを備えた表示装置 |

| KR101304416B1 (ko) | 2006-11-10 | 2013-09-05 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그의 제조 방법 |

| TWI453711B (zh) | 2007-03-21 | 2014-09-21 | Semiconductor Energy Lab | 顯示裝置 |

| KR100884463B1 (ko) * | 2007-07-31 | 2009-02-20 | 삼성모바일디스플레이주식회사 | 발광 표시 장치 및 그의 제조 방법 |

| JP5182993B2 (ja) * | 2008-03-31 | 2013-04-17 | 株式会社半導体エネルギー研究所 | 表示装置及びその作製方法 |

| TWI392944B (zh) * | 2009-05-19 | 2013-04-11 | Au Optronics Corp | 面板、液晶顯示器及面板的形成方法 |

| WO2011148424A1 (ja) * | 2010-05-27 | 2011-12-01 | パナソニック株式会社 | 表示装置用薄膜半導体装置、表示装置及び表示装置用薄膜半導体装置の製造方法 |

| US9128335B2 (en) * | 2011-05-18 | 2015-09-08 | Sharp Kabushiki Kaisha | Liquid crystal panel, liquid crystal display device |

| CN102306479A (zh) * | 2011-07-04 | 2012-01-04 | 深圳市华星光电技术有限公司 | 一种适用于psva与阵列的测试电路 |

| KR101813719B1 (ko) | 2011-07-19 | 2017-12-29 | 엘지디스플레이 주식회사 | 박막트랜지스터 어레이 기판의 제조 방법 |

| CN103163670B (zh) * | 2011-12-19 | 2016-03-02 | 上海中航光电子有限公司 | 一种液晶显示装置的检测开关 |

| KR102050438B1 (ko) * | 2012-11-29 | 2020-01-09 | 엘지디스플레이 주식회사 | 산화물 박막 트랜지스터의 제조 방법 |

| TWI498877B (zh) | 2013-04-26 | 2015-09-01 | Chunghwa Picture Tubes Ltd | 顯示面板 |

| CN103345080B (zh) * | 2013-07-10 | 2017-01-25 | 深圳市华星光电技术有限公司 | 一种快速测试切换装置及相应的tft‑lcd阵列基板 |

| CN103698911A (zh) * | 2013-12-09 | 2014-04-02 | 合肥京东方光电科技有限公司 | 一种阵列基板及显示装置 |

| US20150179666A1 (en) * | 2013-12-25 | 2015-06-25 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Wiring structure of array substrate |

| CN104280970B (zh) * | 2014-11-06 | 2017-12-22 | 上海天马微电子有限公司 | 阵列基板及液晶显示面板 |

| CN104375294B (zh) * | 2014-11-24 | 2017-03-15 | 深圳市华星光电技术有限公司 | 一种显示面板的检测电路及其检测方法 |

| US9601070B2 (en) | 2014-11-24 | 2017-03-21 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Method for performing detection on display panel |

| CN105404065A (zh) * | 2015-12-04 | 2016-03-16 | 深圳市华星光电技术有限公司 | 薄膜晶体管数组结构 |

| KR102436255B1 (ko) * | 2015-12-30 | 2022-08-26 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN105867033B (zh) * | 2016-06-13 | 2019-06-14 | 厦门天马微电子有限公司 | 阵列基板以及液晶显示面板 |

| KR102489594B1 (ko) * | 2016-07-29 | 2023-01-18 | 엘지디스플레이 주식회사 | 협 베젤을 갖는 표시장치 |

| CN110268461A (zh) * | 2017-02-09 | 2019-09-20 | L3技术公司 | 用于航空电子系统的容错液晶显示器 |

| CN108831360A (zh) | 2018-06-22 | 2018-11-16 | 京东方科技集团股份有限公司 | 栅极驱动信号检测电路、方法和显示装置 |

| CN109493770A (zh) * | 2018-11-15 | 2019-03-19 | 昆山龙腾光电有限公司 | 显示面板及其检测方法 |

| JP7217650B2 (ja) * | 2019-03-18 | 2023-02-03 | 株式会社ジャパンディスプレイ | 表示装置 |

| JP2020154251A (ja) * | 2019-03-22 | 2020-09-24 | 株式会社ジャパンディスプレイ | 表示装置及び検査方法 |

| CN110189723B (zh) * | 2019-06-27 | 2021-08-06 | 京东方科技集团股份有限公司 | 调节方法、调节装置、驱动方法、透明显示装置 |

| CN111983860B (zh) * | 2020-08-10 | 2022-07-29 | 深圳市华星光电半导体显示技术有限公司 | 显示面板和显示装置 |

| WO2022124161A1 (ja) * | 2020-12-08 | 2022-06-16 | 京セラ株式会社 | 表示装置および複合型表示装置 |

| TWI762218B (zh) * | 2021-02-25 | 2022-04-21 | 友達光電股份有限公司 | 驅動電路檢測系統 |

| CN114690493B (zh) * | 2022-03-18 | 2024-04-09 | 武汉华星光电技术有限公司 | 显示面板 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5563427A (en) * | 1993-02-10 | 1996-10-08 | Seiko Epson Corporation | Active matrix panel and manufacturing method including TFTs having variable impurity concentration levels |

| JP2653099B2 (ja) * | 1988-05-17 | 1997-09-10 | セイコーエプソン株式会社 | アクティブマトリクスパネル,投写型表示装置及びビューファインダー |

| US5982461A (en) * | 1990-04-27 | 1999-11-09 | Hayashi; Yutaka | Light valve device |

| US6067062A (en) * | 1990-09-05 | 2000-05-23 | Seiko Instruments Inc. | Light valve device |

| CN1314671A (zh) * | 2000-03-17 | 2001-09-26 | 三星电子株式会社 | 液晶显示板的驱动模块和具有该驱动模块的液晶显示装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH055866A (ja) * | 1991-06-28 | 1993-01-14 | Sharp Corp | アクテイブマトリクス基板の検査方法 |

| JP3203841B2 (ja) * | 1992-12-21 | 2001-08-27 | 松下電器産業株式会社 | 液晶表示デバイス |

| KR100223153B1 (ko) * | 1996-05-23 | 1999-10-15 | 구자홍 | 액티브 매트릭스 액정표시장치의 제조방법 및 액티브매트릭스액정표시장치 |

| CN1538228A (zh) * | 1997-07-23 | 2004-10-20 | ������������ʽ���� | 液晶装置及电子设备 |

| JP3667548B2 (ja) * | 1998-03-27 | 2005-07-06 | シャープ株式会社 | アクティブマトリクス型液晶表示パネル及びその検査方法 |

| JP4202571B2 (ja) * | 1999-12-21 | 2008-12-24 | 東芝松下ディスプレイテクノロジー株式会社 | 液晶表示装置およびその製造方法 |

| JP2001265248A (ja) * | 2000-03-14 | 2001-09-28 | Internatl Business Mach Corp <Ibm> | アクティブ・マトリックス表示装置、及び、その検査方法 |

-

2002

- 2002-02-08 TW TW091102456A patent/TW543145B/zh not_active IP Right Cessation

- 2002-05-30 JP JP2002157354A patent/JP2003121867A/ja active Pending

- 2002-06-03 US US10/161,236 patent/US6774398B2/en not_active Expired - Lifetime

- 2002-06-13 CN CNB02122790XA patent/CN100414405C/zh not_active Expired - Lifetime

-

2004

- 2004-05-11 US US10/843,270 patent/US7009202B2/en not_active Expired - Lifetime

-

2009

- 2009-08-26 JP JP2009195217A patent/JP4812862B2/ja not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2653099B2 (ja) * | 1988-05-17 | 1997-09-10 | セイコーエプソン株式会社 | アクティブマトリクスパネル,投写型表示装置及びビューファインダー |

| US5982461A (en) * | 1990-04-27 | 1999-11-09 | Hayashi; Yutaka | Light valve device |

| US6067062A (en) * | 1990-09-05 | 2000-05-23 | Seiko Instruments Inc. | Light valve device |

| US5563427A (en) * | 1993-02-10 | 1996-10-08 | Seiko Epson Corporation | Active matrix panel and manufacturing method including TFTs having variable impurity concentration levels |

| CN1314671A (zh) * | 2000-03-17 | 2001-09-26 | 三星电子株式会社 | 液晶显示板的驱动模块和具有该驱动模块的液晶显示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6774398B2 (en) | 2004-08-10 |

| TW543145B (en) | 2003-07-21 |

| JP2009276792A (ja) | 2009-11-26 |

| CN1412735A (zh) | 2003-04-23 |

| JP2003121867A (ja) | 2003-04-23 |

| US20040207018A1 (en) | 2004-10-21 |

| US7009202B2 (en) | 2006-03-07 |

| JP4812862B2 (ja) | 2011-11-09 |

| US20030075718A1 (en) | 2003-04-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100414405C (zh) | 具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 | |

| CN101221958B (zh) | 具有视觉检查装置的薄膜晶体管阵列面板及其检查方法 | |

| CN100478752C (zh) | 非晶硅薄膜晶体管液晶显示器及其制造方法 | |

| EP1383105B1 (en) | Liquid crystal display and driving method thereof | |

| US7777855B2 (en) | Thin film transistor substrate having gate shorting line and gate shorting bar connection and fabricating method thereof | |

| US8946719B2 (en) | TFT, shift register, scan signal line driving circuit, display device, and TFT trimming method | |

| US7626670B2 (en) | TFT array panel with improved connection to test lines and with the addition of auxiliary test lines commonly connected to each other through respective conductive layers which connect test lines to respective gate or data lines | |

| US7804097B2 (en) | Liquid crystal display device | |

| US6256076B1 (en) | Liquid crystal displays having switching elements and storage capacitors and a manufacturing method thereof | |

| US8183570B2 (en) | Thin film transistor array panel | |

| CN101655624B (zh) | 液晶显示器及其制造方法 | |

| KR101758783B1 (ko) | 게이트 구동부, 이를 포함하는 표시 기판 및 이 표시 기판의 제조 방법 | |

| TWI403812B (zh) | 薄膜電晶體陣列面板及包含該薄膜電晶體陣列面板之液晶顯示器 | |

| US10923061B2 (en) | Gate driving circuit with reduced power consumption and display device including the same | |

| US8373837B2 (en) | Liquid crystal display panel of line-on glass type to prevent signal interference between line-on glass signal lines and method of fabricating the same | |

| US20070171184A1 (en) | Thin film transistor array panel and liquid crystal display | |

| CN101221328B (zh) | 液晶显示装置及其制造方法 | |

| CN101201522A (zh) | 液晶显示设备及其制造方法 | |

| US20160180787A1 (en) | Gate driving circuit and display device having the same | |

| US7256861B2 (en) | Liquid crystal display device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: SAMSUNG MONITOR CO., LTD. Free format text: FORMER OWNER: SAMSUNG ELECTRONICS CO., LTD. Effective date: 20121029 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20121029 Address after: Gyeonggi Do, South Korea Patentee after: Samsung Display Co.,Ltd. Address before: Gyeonggi Do, South Korea Patentee before: Samsung Electronics Co.,Ltd. |

|

| CX01 | Expiry of patent term | ||

| CX01 | Expiry of patent term |

Granted publication date: 20080827 |