BR112018068970B1 - Dispositivo e método para fabricação de um substrato de pastilha embutida - Google Patents

Dispositivo e método para fabricação de um substrato de pastilha embutida Download PDFInfo

- Publication number

- BR112018068970B1 BR112018068970B1 BR112018068970-0A BR112018068970A BR112018068970B1 BR 112018068970 B1 BR112018068970 B1 BR 112018068970B1 BR 112018068970 A BR112018068970 A BR 112018068970A BR 112018068970 B1 BR112018068970 B1 BR 112018068970B1

- Authority

- BR

- Brazil

- Prior art keywords

- layer

- insert

- substrate

- hole

- conductive

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4857—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/486—Via connections through the substrate with or without pins

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49827—Via connections through the substrates, e.g. pins going through the substrate, coaxial cables

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5383—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5384—Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5389—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates the chips being integrally enclosed by the interconnect and support structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/20—Structure, shape, material or disposition of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L24/25—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of a plurality of high density interconnect connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04105—Bonding areas formed on an encapsulation of the semiconductor or solid-state body, e.g. bonding areas on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0618—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/06181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/23—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process

- H01L2224/25—Structure, shape, material or disposition of the high density interconnect connectors after the connecting process of a plurality of high density interconnect connectors

- H01L2224/251—Disposition

- H01L2224/2518—Disposition being disposed on at least two different sides of the body, e.g. dual array

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/291—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/2919—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/82009—Pre-treatment of the connector or the bonding area

- H01L2224/8203—Reshaping, e.g. forming vias

- H01L2224/82035—Reshaping, e.g. forming vias by heating means

- H01L2224/82039—Reshaping, e.g. forming vias by heating means using a laser

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

- H01L2224/82009—Pre-treatment of the connector or the bonding area

- H01L2224/8203—Reshaping, e.g. forming vias

- H01L2224/82047—Reshaping, e.g. forming vias by mechanical means, e.g. severing, pressing, stamping

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92244—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Abstract

Um dispositivo e método de fabricação são fornecidos. O dispositivo inclui um substrato tendo um primeiro lado e um segundo lado oposto, uma cavidade definida dentro do substrato a partir do primeiro lado, uma pastilha acoplada a um piso da cavidade e tendo uma almofada condutora em um lado da pastilha distal ao piso da cavidade. Uma camada laminada acoplada ao segundo lado do substrato pode ser incluída. Um furo pode ser perfurado, de uma só vez, através de camadas do dispositivo, através da pastilha e através da almofada condutora. O furo se estende através de e é definido dentro da camada laminada (se presente), do segundo lado do substrato, da pastilha e da almofada condutora. Um material condutor é fornecido dentro do furo e se estende entre e através da camada laminada (se fornecida), do segundo lado do substrato, da pastilha e da almofada condutora.

Description

[001] Este pedido reivindica prioridade e o benefício do Pedido Não Provisório n° 15/074.750 depositado no Escritório de Marcas e Patentes dos Estados Unidos em 18 de março de 2016, cujo conteúdo total é aqui embutido por referência, como se completamente estabelecido abaixo em sua totalidade e para todos os fins aplicáveis.

[002] Vários recursos referem-se geralmente a um substrato de pastilha embutida e, mais especificamente, a um substrato de pastilha embutida no qual uma pastilha é penetrada durante um processo de perfuração no lado posterior para expor um pad condutor de dentro da pastilha.

[003] A demanda por dispositivos eletrônicos utilizáveis e portáteis continua a crescer. Exemplos de dispositivos eletrônicos portáteis incluem telefones celulares móveis, dispositivo de formação de imagem (por exemplo, câmeras), dispositivos de música (por exemplo, reprodutores de MP3) e dispositivos que integram a funcionalidade de um ou mais dos dispositivos acima mencionados. Exemplos de dispositivos eletrônicos utilizáveis incluem óculos que podem integrar a funcionalidade de um dispositivo de formação de imagem, um visor de vídeo e um terminal de acesso à Internet. Um exemplo adicional de um dispositivo vestível inclui um dispositivo vestível de pulso que pode integrar a funcionalidade de dispositivos que monitoram/registram/transmitem parâmetros fisiológicos de um usuário (por exemplo, frequência cardíaca, nível de oxigênio no sangue, inquietação durante o sono) e/ou localização geográfica. Dispositivos utilizáveis de pulso podem adicionalmente ou alternativamente integrar a funcionalidade de dispositivos celulares móveis com visores coloridos. Muitos dispositivos eletrônicos utilizáveis e portáteis se integram com alguma forma de comunicação sem fio. Os usuários esperam novos recursos, memória adicional e desempenho aperfeiçoado com cada iteração de um dispositivo eletrônico. Além disso, os usuários esperam que seus dispositivos permaneçam do mesmo tamanho ou sejam reduzidos em tamanho, apesar da incorporação de novos recursos, memória adicional e desempenho aperfeiçoado.

[004] Para reduzir o tamanho, os dispositivos podem ser projetados com um aumento na densidade do transistor e/ou uma diminuição no tamanho da pastilha embutida no dispositivo. Pelo menos para fins de proteção e integração, a pastilha pode ser montada em pacotes. Para reduzir o tamanho do pacote, a ligação por fio da pastilha aos pacotes deu lugar à ligação flip-chip. As formas de pacote, tais como a pastilha de grade de esfera, também são usadas para reduzir o tamanho geral dos dispositivos.

[005] A integração vertical de pastilha/pacotes também ajudou a reduzir o tamanho geral dos dispositivos eletrônicos. Em projetos integrados verticalmente, as pastilhas/pacotes podem ser empilhadas um sobre o outro. Exemplos de pastilhas/pacotes empilhados verticalmente incluem a estrutura package on package (PoP). A estrutura PoP pode ser compreendida por uma pilha vertical de pacotes de pastilha de grade de esfera.

[006] Outra estrutura usada para integração vertical é conhecida como substrato de pastilha embutida ou substrato laminado embutido (aqui referido por consistência como substrato de pastilha embutida (EDS)). Um EDS pode empregar um substrato de múltiplas camadas. Para reduzir o tamanho vertical, em vez de montar a pastilha ativa e/ou componentes ativos/passivos para o topo do substrato de múltiplas camadas, a pastilha ativa e/ou os componentes ativos/passivos são montados dentro de uma cavidade no substrato de múltiplas camadas.

[007] O uso de EDS pode reduzir o tamanho vertical, mas as dificuldades permanecem na implementação. Por exemplo, em uma implementação de EDS, o acesso aos pads em um lado superior (por exemplo, primeiro lado) de uma pastilha de nós adjacentes a um lado posterior oposto (por exemplo, segundo lado) da pastilha pode envolver o uso de pastilhas que são dispendiosas de fabricar. É, portanto, desejável, por exemplo, reduzir os custos da pastilha usada nas implementações de EDS, mas manter o acesso aos pads no lado superior da pastilha a partir de nós adjacentes a um lado posterior da pastilha.

[008] Os aspectos aqui descritos proveem um dispositivo e métodos para fabricação do dispositivo, tal como um substrato de pastilha embutido.

[009] De acordo com um aspecto, um dispositivo pode incluir um substrato que tem um primeiro lado e um segundo lado oposto. O dispositivo pode adicionalmente incluir uma cavidade definida dentro do substrato a partir do primeiro lado e uma pastilha acoplada a um piso da cavidade. A pastilha pode ter um pad condutor em um lado da pastilha distal ao piso da cavidade. O dispositivo pode adicionalmente incluir um furo que se estende através e é definido dentro do segundo lado do substrato, da pastilha e do pad condutor. O dispositivo pode adicionalmente incluir um material condutor dentro do furo e que se estende entre e através do segundo lado do substrato e do pad condutor. O material condutor pode formar, ou ser descrito como, uma interconexão. Em termos mais específicos, o material condutor pode formar, ou ser descrito como, uma interconexão de pastilha penetrante de segmento único.

[0010] Em algumas implementações, o substrato é um substrato de núcleo que inclui uma camada condutora colocada entre (“sandwiched”) uma primeira camada dielétrica no primeiro lado do substrato e uma segunda camada dielétrica no segundo lado do substrato. Em alguns exemplos, quando o substrato é um tal substrato de núcleo, a cavidade é desprovida da primeira camada dielétrica e da camada condutora, e o piso da cavidade é definido pela segunda camada dielétrica exposta na cavidade.

[0011] Em um aspecto, o furo é contínuo através do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é concêntrico ao longo de um eixo linear que se estende através do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é um único furo linear ao longo de um comprimento do furo.

[0012] Em um aspecto, o material condutor é um segmento individual unitário. O material condutor inclui apenas uma camada.

[0013] De acordo com outro aspecto, um dispositivo pode incluir um substrato que tem um primeiro lado e um segundo lado oposto. O dispositivo pode adicionalmente incluir uma cavidade definida dentro do substrato a partir do primeiro lado e uma pastilha acoplada a um piso da cavidade. A pastilha pode ter um pad condutor em um lado da pastilha distal ao piso da cavidade. O dispositivo pode adicionalmente incluir uma camada laminada acoplada ao segundo lado do substrato. Em tal aspecto, o segundo lado do substrato é colocado entre a pastilha e a camada laminada. O dispositivo pode adicionalmente incluir um furo que se estende através e é definido dentro da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. O dispositivo pode adicionalmente incluir um material condutor dentro do furo e que se estende entre e através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. O material condutor pode formar ou ser descrito como uma interconexão. Em termos mais específicos, o material condutor pode formar, ou ser descrito como, uma interconexão de pastilha penetrante de segmento único.

[0014] Em algumas implementações, o substrato é um substrato de núcleo que inclui uma camada condutora colocada entre uma primeira camada dielétrica no primeiro lado do substrato e uma segunda camada dielétrica no segundo lado do substrato.

[0015] Em um aspecto, o furo é contínuo através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é concêntrico ao longo de um eixo linear que se estende através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é um único furo linear ao longo de um comprimento do furo.

[0016] Em um aspecto, o material condutor é um segmento individual unitário. O material condutor inclui apenas uma camada.

[0017] Em um aspecto, o dispositivo é incorporado a um dispositivo selecionado a partir de um grupo que inclui pelo menos um dispositivo móvel, uma unidade de sistema de comunicação pessoal (PCS) portátil, um assistente digital pessoal, um terminal de dados portátil, um dispositivo de sistema de posicionamento global (GPS) habilitado, um dispositivo de navegação, um set top box, um reprodutor de música, um reprodutor de vídeo, uma unidade de entretenimento, um terminal de localização fixa, um dispositivo de comunicação, um telefone celular, um telefone inteligente, um computador tablet, um computador, um dispositivo vestível, um dispositivo de Internet das coisas (IoT), um laptop, um servidor, um roteador e um dispositivo eletrônico implementado em um veículo automotivo.

[0018] De acordo com outro aspecto, o dispositivo pode incluir um substrato que tem um primeiro lado e um segundo lado oposto. O dispositivo pode adicionalmente incluir uma cavidade definida dentro do substrato a partir do primeiro lado e uma pastilha acoplada a um piso da cavidade. A pastilha pode ter um pad condutor em um lado da pastilha distal ao piso da cavidade. O dispositivo pode adicionalmente incluir meios para uma interconexão penetrar no substrato e na pastilha e acoplar o pad condutor a um nó oposto ao pad condutor no segundo lado do substrato. De acordo com um exemplo, os meios para a interconexão podem incluir um furo que se estende através e é definido dentro do segundo lado do substrato, da pastilha e do pad condutor, e pode adicionalmente incluir um material condutor dentro do furo e que se estende entre e através do segundo lado do substrato e o pad condutor. De acordo com outro exemplo, os meios para a interconexão podem ser contínuos através do segundo lado do substrato, da pastilha e do pad condutor. De acordo com ainda outro exemplo, os meios para a interconexão podem ser concêntricos ao longo de um eixo linear que se estende através do segundo lado do substrato, da pastilha e do pad condutor. Em outro exemplo, os meios para a interconexão incluem um único furo linear ao longo de um comprimento do furo. Em ainda outro exemplo, os meios para a interconexão incluem um material condutor formado como um segmento individual unitário que se acopla ao pad condutor de dentro do pad condutor.

[0019] Outro aspecto aqui descrito provê um método para fabricar um substrato de pastilha embutido. O método inclui prover um substrato que tem um primeiro lado e um segundo lado oposto. O método inclui ainda a formação de uma cavidade definida dentro do substrato a partir do primeiro lado. O método inclui ainda o acoplamento de uma pastilha a um piso da cavidade, a pastilha tendo um pad condutor em um lado da pastilha distal ao piso da cavidade. Em um aspecto, o método também inclui a perfuração de um furo que se estende e é definido dentro do segundo lado do substrato, da pastilha e do pad condutor. O método ainda inclui ainda chapear e/ou preencher o furo com um material condutor que se estende entre e através do segundo lado do substrato, da pastilha e do pad condutor, e que se acopla ao pad condutor a partir do furo.

[0020] Em algumas implementações, a pastilha é acoplada ao piso da cavidade antes de perfurar o furo. Em um aspecto, a perfuração do furo é realizada de uma só vez. Assim, o furo é perfurado através do segundo lado do substrato, da pastilha e do pad condutor em um processo. Em um aspecto, o furo é formado para ser concêntrico ao longo de um eixo linear que se estende através do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é formado para ser um único furo linear ao longo de um comprimento do furo.

[0021] Em um aspecto, o material condutor é formado como um segmento individual unitário. Em algumas implementações, o material condutor que se estende entre e através do segundo lado do substrato, da pastilha e do pad condutor é formado como apenas uma camada. Em outro aspecto, o método inclui adicionalmente acoplar uma camada laminada ao segundo lado do substrato, em que o furo é adicionalmente perfurado para se estender e ser definido dentro da camada laminada, e o material condutor estende-se ainda entre e através da camada laminada.

[0022] Outro aspecto aqui descrito provê outro método de fabricar um substrato de pastilha embutido. O método inclui prover um substrato que tem um primeiro lado e um segundo lado oposto. O método inclui ainda a formação de uma cavidade definida dentro do substrato a partir do primeiro lado. O método ainda inclui ainda, o acoplamento de uma pastilha a um piso da cavidade, a pastilha tendo um pad condutor em um lado da pastilha distal ao piso da cavidade. O método ainda inclui ainda o acoplamento de uma camada laminada ao segundo lado do substrato. Em um aspecto, o método também inclui a perfuração de um furo que se estende através e é definido dentro da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. O método ainda inclui ainda galvanizar e/ou preencher o furo com um material condutor que se estende entre e através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor, e que se acopla ao pad condutor dentro do furo.

[0023] Em algumas implementações, a pastilha é acoplada ao piso da cavidade e a camada laminada é acoplada ao segundo lado do substrato antes da perfuração do furo. Em um aspecto, a perfuração do furo é realizada de uma só vez. Em um aspecto, o furo é formado para ser concêntrico ao longo de um eixo linear que se estende através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor. Em um aspecto, o furo é formado para ser um único furo linear ao longo de um comprimento do furo.

[0024] Em um aspecto, o material condutor é formado como um segmento individual unitário. Em algumas implementações, o material condutor que se estende entre e através da camada laminada, do segundo lado do substrato, da pastilha e do pad condutor é formado apenas como uma camada. Em um exemplo, o material condutor forma uma interconexão entre uma superfície da camada laminada distal ao segundo lado do substrato e o pad condutor.

[0025] Diversas características, natureza e vantagens podem tornar-se evidentes a partir da descrição detalhada apresentada a seguir, quando tomadas em conjunto com os desenhos nos quais os caracteres de referência semelhantes identificam de forma correspondente ao longo do texto.

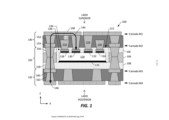

[0026] A figura 1 ilustra uma vista em corte transversal de um exemplo de um substrato de pastilha embutida (EDS) implementando um primeiro tipo de pastilha de acordo com uma abordagem.

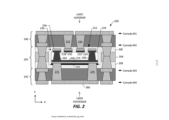

[0027] A figura 2 ilustra uma vista em corte transversal de um exemplo de um EDS implementando um segundo tipo de pastilha de acordo com outra abordagem.

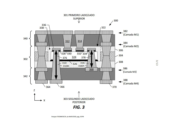

[0028] A figura 3 ilustra uma vista em corte de um EDS incluindo uma primeira interconexão de pastilha penetrante de segmento único e uma segunda interconexão de pastilha penetrante de segmento único de acordo com os aspectos aqui descritos.

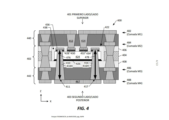

[0029] A figura 4 ilustra uma vista em corte transversal de outro EDS incluindo uma primeira interconexão de pastilha penetrante de segmento único e uma segunda interconexão de pastilha penetrante de segmento único de acordo com os aspectos aqui descritos.

[0030] A figura 5A ilustra uma vista de plano posterior de uma pastilha que pode ser instalada em uma EDS de acordo com os aspectos aqui descritos.

[0031] A figura 5B ilustra uma vista em corte da pastilha da figura 5A tomada ao longo da linha 5B-5B.

[0032] A figura 6A ilustra uma vista de plano posterior de um primeiro EDS tendo primeiros locais pré- designados para a formação de interconexões de inserção de pastilha de segmento único de acordo com os aspectos aqui descritos.

[0033] A figura 6B ilustra uma vista de plano posterior de um segundo EDS tendo primeiras localizações pré-designadas para a formação de interconexões de pastilha penetrante de segmento único de acordo com os aspectos aqui descritos.

[0034] A figura 7 (que inclui as figuras 7A- 7C) ilustra uma sequência exemplar de etapas para prover/fabricar um EDS que inclui interconexões de pastilha penetrante de segmento único de acordo com os aspectos aqui descritos.

[0035] A figura 8 ilustra um diagrama de fluxo de um método exemplar para a fabricação de um EDS, incluindo uma interconexão de pastilha penetrante de segmento único, de acordo com os aspectos aqui descritos.

[0036] A figura 9 ilustra outro diagrama de fluxo de um método exemplar para a fabricação de um EDS, incluindo uma interconexão de pastilha penetrante de segmento único, de acordo com os aspectos aqui descritos.

[0037] A figura 10 ilustra outro diagrama de fluxo de um método exemplar para a fabricação de um EDS, incluindo uma interconexão de pastilha penetrante de segmento único de acordo com os aspectos aqui descritos.

[0038] A figura 11 ilustra vários dispositivos eletrônicos que podem ser integrados com qualquer um dos EDS mencionados anteriormente que incluem uma interconexão de pastilha penetrante de segmento único.

[0039] Na descrição a seguir, detalhes específicos são providos para prover uma compreensão completa dos vários aspectos da descrição. Contudo, será entendido por um versado na técnica que os aspectos podem ser praticados sem os detalhes específicos aqui dados. Por exemplo, circuitos podem ser mostrados em diagramas de blocos para evitar obscurecer os aspectos em detalhes desnecessários. Em outros casos, circuitos, estruturas e técnicas bem conhecidos podem não ser mostrados em detalhes a fim de não obscurecer os aspectos da descrição.

[0040] Em algumas implementações, a altura de uma pastilha pode ser definida ao longo da direção Z da pastilha, que é mostrada nas figuras da presente descrição. Em algumas implementações, a direção Z da pastilha pode ser definida ao longo de um eixo entre um primeiro lado (por exemplo, um lado superior) e um segundo lado oposto (por exemplo, um lado posterior) da pastilha. Os termos lado superior (ou topo) e lado posterior (ou fundo) podem ser arbitrariamente atribuídos; no entanto, como um exemplo, uma superfície do lado superior de uma pastilha pode ser uma porção compreendendo uma maioria dos pads de entrada/saída, enquanto uma superfície do lado posterior da pastilha pode ser uma porção que está ligada, aderida ou de outro modo afixada a um substrato. Em algumas implementações, a porção do lado superior da pastilha pode ser um lado posterior da pastilha e a porção do lado posterior da pastilha pode ser um lado superior da pastilha. Uma porção do lado superior pode ser uma porção mais alta em relação a uma porção mais baixa do lado posterior. Uma porção do lado posterior pode ser uma porção mais baixa em relação a uma porção mais alta do lado superior. Exemplos adicionais de porções do lado superior e porções do lado posterior serão descritas adicionalmente abaixo. As direções X-Y da pastilha podem se referir à direção lateral e/ou à pegada da pastilha. Exemplos de direções X-Y são mostrados nas figuras da presente descrição e/ou descritas adicionalmente abaixo. Em muitas das figuras da presente descrição, a pastilha e as porções de um EDS podem ser mostradas por entre uma seção transversal X-Z ou plano X-Z. No entanto, em algumas implementações, a pastilha e as porções do EDS podem ser representadas por entre uma seção transversal Y-Z ou plano Y-Z.

[0041] Em algumas implementações, uma interconexão é um elemento ou componente de um dado, EDS, dispositivo ou pacote que permite ou facilita um acoplamento eletrônico e/ou térmico entre dois pontos, elementos e/ou componentes. Em algumas implementações, uma interconexão pode incluir um traço e/ou um furo chapeado e/ou preenchido (por exemplo, uma via). Em algumas implementações, uma interconexão pode ser formada por segmentos em cascata (camadas), tal como uma pluralidade de vias conectadas em série; tal interconexão pode ser referida aqui como uma interconexão segmentada. Interconexões segmentadas podem incluir junções entre segmentos (por exemplo, camadas), pelo menos porque segmentos separados podem ser formados durante operações separadas durante o processamento. Portanto, uma interconexão segmentada, tal como uma interconexão segmentada formada por uma pilha de vias em cascata, pode ter emendas, entre segmentos, ao longo do comprimento da interconexão segmentada, transversal ao comprimento da interconexão segmentada. Em contraste, em algumas implementações, uma interconexão pode ser formada por apenas um segmento (por exemplo, apenas uma camada); tal interconexão pode ser aqui referida como uma interconexão de segmento único (isto é, uma interconexão não segmentada). Interconexões de segmento único podem não ter emendas ao longo do comprimento da interconexão de segmento único, transversal ao comprimento da interconexão de segmento único. Em algumas implementações, uma interconexão pode ser fabricada com um material eletricamente condutor que pode ser configurado para prover um caminho eletrônico para um sinal (por exemplo, sinal de dados, sinal de aterramento, sinal de potência) de um primeiro nó para um segundo nó. Em algumas implementações, uma interconexão pode ser fabricada com um material termicamente condutor que pode ser configurado para prover um caminho térmico de um primeiro nó para um segundo nó. Uma interconexão pode ser eletricamente e/ou termicamente condutora. Uma interconexão pode fazer parte de um circuito. Uma lista não exclusiva de exemplos de materiais condutores inclui ouro, prata e cobre. O material condutor pode ser uma pasta condutora.

[0042] Como usado aqui, a perfuração (por exemplo, perfuração de um furo) pode ser implementada com processos que incluem, por exemplo, um processo de fotolitografia, um processo mecânico e/ou um processo de perfuração a laser.

[0043] Como usado aqui, um furo pode ser uma cavidade, abertura ou vazio em um objeto físico que é definido pela(s) parede(s) lateral(is) formada(s) no objeto físico.

[0044] Em um dispositivo multicamadas, costuma-se identificar a camada de metalização mais alta como uma primeira camada de metalização ou uma camada "Ml". Cada camada de metalização inferior é habitualmente incrementada em um. Os EDS exemplares aqui apresentados são ilustrados com quatro camadas de metalização (Ml, M2, M3, M4). No entanto, EDSs de acordo com os aspectos aqui descritos podem ser apresentados com qualquer número de camadas de metalização. Nada no presente destina-se a limitar o número de camadas de metalização de um EDS.

[0045] Algumas características pertencem a um substrato de pastilha embutida (EDS) que inclui um substrato com uma camada condutora colocada entre camadas dielétricas opostas, uma cavidade no substrato, uma pastilha montada no substrato dentro da cavidade e camadas pré-impregnadas laminadas nas camadas dielétricas nos lados opostos do substrato. Pelo menos uma interconexão de segmento único (por exemplo, um furo e/ou preenchido com um comprimento contínuo de um material condutor) se estende através de uma camada pré-impregnada em um lado posterior de EDS, uma camada dielétrica do substrato, e na pastilha. A interconexão de segmento único pode unir eletricamente e/ou termicamente um pad condutor em um primeiro lado (por exemplo, lado superior) da pastilha a um pad condutor em um segundo lado oposto (por exemplo, lado posterior) da camada pré-impregnada. A interconexão de segmento único, incluindo a porção dentro da pastilha, pode ser formada durante um processo de perfuração posterior de EDS, após a pastilha ser acoplada (por exemplo, montada) ao substrato dentro da cavidade. A formação da interconexão de segmento único (incluindo o lado dentro da pastilha) em uma localização pré-designado durante um processo de perfuração do lado posterior do EDS pode resultar na redução do custo da pastilha e na redução do custo de integração da pastilha na pastilha. EDS, em comparação, por exemplo, ao uso de uma pastilha com uma via através de substrato previamente formada (TSV) em um local correspondente à localização pré- designada na EDS. Além disso, a formação da interconexão de segmento único (incluindo o lado dentro da pastilha) em uma localização pré-designado durante o processo de perfuração do lado posterior de EDS permite que a interconexão de segmento único seja fabricada com um material condutor ao longo de todo o comprimento. Pode ser selecionado para minimizar a resistência de aterramento da dissipação térmica. Tipos de Pastilha de Substrato de Pastilha Embutida Exemplar

[0046] EDS geralmente usam um dos dois tipos de dados. Um primeiro tipo de pastilha tem pads de entrada/saída/aterramento/potência em uma superfície superior da pastilha. O uso do primeiro tipo de dado na EDS apresenta problemas para o roteamento. Todo o encaminhamento pode começar (ou terminar) na superfície do lado superior do dado. Roteamento para camadas do EDS abaixo do primeiro tipo de pastilha pode fazer uso de traços roteados de e sobre a pastilha. Traços de roteamento para cima e para cima da pastilha podem ser difíceis em espaços bidimensionais e tridimensionais. O tempo extra envolvido na solução de problemas de roteamento pode aumentar o custo do design geral. Traços adicionais podem diminuir a confiabilidade à medida que aumentam as chances de metalização aberta ou em curto. Além disso, o uso do primeiro tipo de pastilha na EDS pode afetar adversamente o desempenho, pois os requisitos térmicos e/ou elétricos do EDS podem não ser atendidos devido, pelo menos em parte, ao roteamento de traçados. Por exemplo, rotas longas de metalização podem dificultar a remoção de calor de um dado dentro de EDS. Adicionalmente, rotas longas de metalização aumentam a probabilidade de que a energia eletromagnética indesejada possa entrar na metalização e, assim, ter acesso aos circuitos internos da pastilha, interferindo na operação da pastilha.

[0047] Um segundo tipo de pastilha pode ter acesso a pelo menos alguns pads de entrada/saída/aterramento/potência em uma superfície do lado posterior da pastilha. O acesso aos pads da superfície do lado posterior é obtido pelo uso de vias através de substrato (TSVs) (também conhecidas como através de vias de silício) na pastilha. As TSVs podem interconectar um pad do lado superior a um pad do lado posterior. Uma TSV pode ser conceituada como uma conexão elétrica vertical entre dois nós elétricos na pastilha. No caso de uma pastilha tendo duas superfícies exteriores opostas, um primeiro não pode estar em uma primeira superfície (por exemplo, no lado superior) da pastilha enquanto o segundo não pode estar em uma segunda superfície (por exemplo, no lado posterior) da pastilha. Nesse caso, o TSV pode passar completamente através do dado.

[0048] As TSVs da pastilha são formadas durante a fabricação de pastilhas em uma fundição. Como usado aqui, o termo "fundição" refere-se a uma instalação de fabricação de semicondutores ou a um local que fabrica circuitos integrados de semicondutores. A fabricação de TSVs em um dado em uma fundição aumenta o custo do dado pelo menos devido a um aumento na contagem de máscaras e aumento em várias operações usadas para fabricar o dado com TSVs. A integração de TSVs em uma pastilha em uma fundição também pode envolver custos associados ao rendimento. Algumas das TSVs produzidas na fundição podem não ser fabricados adequadamente. Por exemplo, pode haver um circuito aberto dentro do TSV de modo que um primeiro nó em um primeiro lado da pastilha não seja conectado a um segundo nó em um segundo lado da pastilha. Devido a erros associados a TSVs fabricadas na fundição, o rendimento pode cair e o custo pode subir.

[0049] O uso do segundo tipo de pastilha (isto é, pastilhas com TSVs) em uma EDS resulta em um alto custo da pastilha devido à incorporação da TSV na pastilha (ou seja, pastilhas fabricadas com TSVs são mais caras do que pastilhas fabricadas sem TSVs). Um custo adicional está envolvido no fato de que pastilhas fabricadas com TSVs usam galvanização metálica nas porções superior e posterior da pastilha, para atuar como paradas de laser durante a integração EDS. Além disso, em conexão com TSVs formados de ouro, a condução térmica associada a TSVs de ouro não é tão boa quanto a condução térmica oferecida pelo cobre. Portanto, a resistência de aterramento de dissipação térmica em EDS usando pastilhas com TSVs não é tão baixa quanto desejado. Substrato de Pastilha Embutida (EDS) Exemplar

[0050] A figura 1 ilustra uma vista em corte transversal de um exemplo de um substrato de pastilha embutido (EDS) 100 que implementa um primeiro tipo de pastilha 124 (por exemplo, uma pastilha sem TSV) de acordo com uma abordagem. O EDS 100 pode incluir um substrato de núcleo 102 incluindo uma camada condutora central 104, uma camada dielétrica do lado superior 106, e uma camada dielétrica posterior 108.

[0051] Uma cavidade 122 para reter uma pastilha 124 pode ser formada na camada dielétrica 106 do lado superior e na camada condutora central 104. O lado inferior da cavidade 122 pode ser referida como o "piso" da cavidade 122. A pastilha 124 pode ser acoplada para o piso da cavidade 122 (por exemplo, acoplado à camada dielétrica posterior 108 dentro da cavidade 122). A cavidade 122 pode ser preenchida com um material de enchimento 138.

[0052] A pastilha 124 pode incluir uma pluralidade de pads condutores 128, 130, 132, 134 incluindo um primeiro pad condutor 128, um segundo pad condutor 130, um terceiro pad condutor 132 e uma quarto pad condutor 134 em uma superfície do lado superior da pastilha 124 A pastilha 124 da figura 1 não inclui TSVs (por exemplo, vias formadas dentro do corpo da pastilha em uma fundição durante a fabricação). Uma camada condutora protetora 136 pode ser provida em cada um dos vários pads condutores 128, 130, 132, 134.

[0053] Pode ser provida uma camada laminada do lado de cima 140 à camada dielétrica do lado de cima 106. Uma camada laminada do lado de trás 142 pode ser provida à camada dielétrica do lado de trás 108.

[0054] Na ilustração exemplar da figura 1, uma da pluralidade de pads condutores 128, 130, 132, 134 no lado superior da pastilha 124 pode ser ligada a um nó (por exemplo, um pad condutor ou traço) em uma camada do EDS 100 abaixo da pastilha 124. Um trajeto de encaminhamento exemplar 144 (para energia eléctrica e térmica) entre o segundo pad condutor 130 e um nó 146, em um lado posterior da camada laminada posterior 142, é ilustrado com uma seta de dois lados.

[0055] A perfuração do lado superior pode ser usada para alcançar o segundo pad condutor 130 da pastilha 124 no lado superior da pastilha 124. A perfuração no lado superior pode estender-se através da camada laminada do lado superior 140 e do material de enchimento 138 usado para preencher a cavidade 122. Uma perfuradora a laser pode ser usada para a perfuração do lado superior. Para fins de paragem a laser, a camada condutora protetora 136 protege o segundo pad condutor 130 da pastilha 124. O batente laser (por exemplo, camada condutora protetora 136) impede que a perfuradora a laser penetre através do segundo pad condutor 130 e na pastilha 124. A perfuração no lado posterior pode abrir um caminho a partir do nó 146 (por exemplo, um pad ou um traço) em direção à camada condutora central 104 do substrato de núcleo 102.

[0056] Para conseguir um caminho condutor entre o segundo pad condutor 130 e o nó 146 (por exemplo, um pad ou traço), a metalização pode ser encaminhada para cima e em torno da pastilha 124. A metalização pode ser encaminhada através da interconexão 112 (através da camada laminada no lado superior 140). A metalização pode então ser encaminhada lateralmente após a borda da pastilha 124, ao longo de uma porção de uma interconexão formada pelo traço condutor 148. A metalização pode então ser encaminhada para baixo passando a pastilha através de múltiplos segmentos verticais (por exemplo, segmentos substancialmente alinhados ao longo do eixo Z) de vias e pads. Por exemplo, a metalização pode ser encaminhada através de um primeiro segmento por via 152, um primeiro pad 154, um segundo segmento por via 156, um terceiro segmento por via 158, um segundo pad 160 e uma quarta segmento por via 162 antes de unir o nó 146 da camada laminada posterior 142. Quaisquer dois ou mais segmentos por via acoplados podem ser referidos aqui como uma "interconexão segmentada". O roteamento por circuitos de metalização acabado de descrever pode ser difícil de planejar e implementar. O roteamento por circuito pode adicionar custo à fabricação de EDS 100 e pode resultar no EDS 100 não atendendo aos requisitos elétricos e/ou térmicos.

[0057] A figura 2 ilustra uma vista em corte transversal de um exemplo de um EDS 200 implementando um segundo tipo de pastilha 224 (por exemplo, uma pastilha com TSVs) de acordo com outra abordagem. O EDS 200 pode incluir um substrato de núcleo 202, incluindo uma camada condutora central 204, uma camada dielétrica do lado superior 206, e uma camada dielétrica do lado posterior 208.

[0058] Uma cavidade 222 para reter uma fieira 224 pode ser formada na camada dielétrica do lado superior 206 e na camada condutora central 204. O lado inferior da cavidade 222 pode ser referida como o "piso" da cavidade 222. A fieira 224 pode ser acoplada para o piso da cavidade 222 (por exemplo, acoplado à camada dielétrica posterior 208 dentro da cavidade 222). A cavidade 222 pode ser preenchida com um material de enchimento 238.

[0059] A pastilha 224 pode incluir uma pluralidade de pads condutores 228, 230, 232, 234 incluindo um primeiro pad condutor 228, um segundo pad condutor 230, um terceiro pad condutor 232 e uma quarto pad condutor 234 em uma superfície do lado superior da pastilha 224 A pastilha 224 da figura 2 inclui um primeiro substrato através de via (TSV) 264 e um segundo TSV 266. O primeiro TSV 264 e o segundo TSV 266 podem ser vias formadas dentro do corpo da pastilha 224 em uma fundição durante a fabricação da pastilha. Uma camada condutora protetora do lado superior 236 pode ser provida em cada um dos vários pads condutores 228, 230, 232, 234.

[0060] Pode ser provida uma camada laminada do lado de cima 240 à camada dielétrica do lado superior 206. Uma camada laminada do lado de trás 242 pode ser provida à camada dielétrica do lado de trás 208.

[0061] Na ilustração exemplar da figura 2, a pastilha 224 é fabricada em uma fundição com o primeiro pad condutor 228 acoplada à primeira TSV 264 e a quarto pad condutor 234 acoplada à segunda TSV 266. O primeiro TSV 264 e o segundo TSV 266 são acoplados a um pad condutor do lado posterior 268. Isto é, a pastilha 224 inclui o primeiro TSV 264 e o segundo TSV 266 dentro do corpo da pastilha 224; o primeiro TSV 264 e o segundo TSV 266 foram formados dentro do corpo da pastilha 224 durante a fabricação da pastilha na fundição. Em tal configuração, o primeiro pad condutor 228, primeiro TSV 264, quarto pad condutor 234, segunda TSV 266, e pad condutor posterior 268 podem ser formadas de ouro.

[0062] Para fins de um batente laser em um lado superior da pastilha 224, uma camada condutora protetora do lado superior 236 protege a pluralidade de pads condutores 228, 230, 232, 234. Por exemplo, em um processo de perfuração do lado superior, o batente laser (por exemplo, camada condutora protetora do lado superior 236) impede que uma perfuradora a laser penetre através do segundo pad condutor 230 e dentro da pastilha 224.

[0063] Para fins de paragem a laser do lado posterior da pastilha 224, uma camada condutora protetora posterior 270 protege o pad condutor do lado posterior 268. A adição da camada condutora protetora do lado posterior 270 à pastilha 224 adiciona custos à pastilha 224. A camada condutora de proteção do lado posterior 270 atua como um batente laser para furos formados por perfuração a laser a partir do lado posterior de EDS 200 para a camada condutora central 204 do substrato de núcleo 202.

[0064] As interconexões 272, 274, que podem ser formadas durante um processo de perfuração posterior durante a integração EDS, não se estendem para dentro e/ou através da pastilha 224. Elas param na camada condutora de proteção posterior 270 (a camada de interrupção de laser) formada no lado posterior pad condutor 268 porque, por exemplo, uma preocupação de que os furos de perfuração (por exemplo, furos que se estendem para dentro e/ou através da pastilha, furos que penetram a pastilha) na pastilha 224 durante a integração EDS podem danificar a pastilha 224. É desejável para não danificar a pastilha 224 durante a integração EDS, porque, por exemplo, a substituição da pastilha 224 durante a integração EDS pode não ser possível. O resultado de um dado danificado pode ser uma perda completa de EDS 200.

[0065] O uso da segunda abordagem para um EDS 200 pode vir com um custo. Pastilha com TSV é mais caro do que pastilha sem TSV. Além disso, como afirmado acima, o primeiro TSV 264 e o segundo TSV 266 podem ser formados de ouro. Em contraste, as interconexões 272, 274 podem ser formadas de cobre. A condutividade térmica do ouro é menor que a do cobre. Consequentemente, a transferência de energia térmica da pastilha 224 para, por exemplo, um pad ou traço 280 no lado de trás da camada laminada posterior 242 não é a ideal.

[0066] Em contraste com as abordagens exemplares ilustradas na figura 1 e figura 2, um EDS exemplar tendo pelo menos uma interconexão de pastilha penetrante de segmento único formada em uma pastilha por perfuração na pastilha durante a integração de EDS (não na fundição) pode economizar custos reduzindo custos de TSV de fundição, pode reduzir os custos de galvanização de cobre do lado posterior para perfuração no lado posterior, e pode melhorar o desempenho usando uma interconexão de pastilha penetrante de segmento único formada inteiramente de um condutor como o cobre, que tem uma melhor condutividade térmica do que o ouro.

[0067] A figura 3 ilustra uma vista em corte transversal de um EDS 300 incluindo uma primeira interconexão de pastilha penetrante de segmento único 310 e uma quarta interconexão de pastilha penetrante de segmento único 316 de acordo com os aspectos aqui descritos.

[0068] O termo estrutura de "segmento único" pode ser usado aqui para descrever uma estrutura unitária, uma estrutura indivisível e/ou uma estrutura indivisível. Como usado aqui, o termo "interconexão de pastilha penetrante de segmento único" pode ser usado aqui para descrever uma interconexão unitária, indivisível e/ou não dividida onde uma porção da interconexão se estende (por exemplo, penetra, penetra, passa através de, entra) pelo menos um lado de uma camada (por exemplo, uma camada de substrato, uma camada dielétrica, uma camada laminada) de um EDS 300 e uma pastilha 324 de EDS 300. Um exemplo de uma interconexão de pastilha penetrante de segmento único pode incluir uma estrutura colunar tendo uma parede lateral com uma altura definida diferente de zero, um furo chapeado e/ou um furo preenchido formado de um material condutor tendo uma primeira extremidade (por exemplo, uma primeira extremidade em e/ou uma segunda camada laminada 342 (por exemplo, uma camada laminada no lado posterior) ou uma segunda camada dielétrica 308) e uma segunda extremidade distai (por exemplo, uma extremidade da primeira extremidade, uma segunda extremidade na e/ou em um primeiro pad condutor 328 da pastilha 324 do EDS 300, ou em e/ou em uma camada condutora de proteção 336 (por exemplo, uma parada a laser, uma camada de cobre, uma camada de cobre) provida no primeiro pad condutor 328). Como usado aqui, uma interconexão de pastilha penetrante de segmento único (por exemplo, primeira interconexão de pastilha penetrante de segmento único 310) pode ser formada, por exemplo, perfurando um primeiro furo 310H através de um substrato 302 de EDS 300, na pastilha 324 do EDS 300, e em um pad condutor 328 da pastilha 324 e galvanizando e/ou preenchendo o primeiro furo 310H com um material condutor que liga o pad condutor 328 de dentro do primeiro furo 31 OH. O material condutor pode assentar as paredes laterais do primeiro furo 31 OH e/ou preencher completamente o primeiro furo 31 OH. Em algumas implementações, o primeiro furo 31 OH pode ter um diâmetro constante ou um diâmetro linearmente decrescente (por exemplo, a perfuração do furo é implementada de tal modo que o furo tenha um diâmetro constante ou um diâmetro linearmente decrescente ao longo de todo o furo).

[0069] Em algumas implementações, uma formação de camadas (por exemplo, camadas eletricamente condutoras compreendendo uma pluralidade de segmentos) não seria detectada em uma análise de seção transversal ou uma esmerilação paralela (esmerilação-p) de uma interconexão de pastilha penetrante de segmento único no EDS 300. Em algumas implementações, uma interconexão de pastilha penetrante de segmento único de acordo com aspectos descritos aqui inclui apenas um segmento (por exemplo, camada), em contraste, por exemplo, a uma pilha de uma pluralidade de vias unidas (por exemplo, encostadas).

[0070] A primeira interconexão de pastilha penetrante de segmento único 310 pode ser revestida e/ou preenchida ao longo de todo o seu comprimento com um material condutor. Em algumas implementações, apenas um material condutor é usado. Em outras palavras, em algumas implementações, o único material condutor é distribuído ao longo de todo o comprimento da primeira interconexão 310 que penetra um segmento único. O único material condutor pode formar uma estrutura unitária, indivisível e/ou não dividida. Em algumas implementações, o material condutor pode ser cobre. Em algumas implementações, o material condutor pode ser uma pasta condutora. A primeira interconexão de pastilha penetrante de segmento único 310 pode ser formada durante um processo de perfuração posterior de EDS 300, após a pastilha 324 ser acoplada (por exemplo, fisicamente montada) ao substrato 302. Em algumas implementações, a pastilha 324 usada no O EDS 300 pode ser produzido em uma fundição sem um TSV em uma localização predeterminada para a primeira interconexão de pastilha penetrante de segmento único 310.

[0071] O EDS 300 pode incluir um substrato 302. O substrato 302 pode ter um primeiro lado 301 e um segundo lado oposto 303. O substrato 302 pode ser um substrato nuclear. O substrato 302 pode incluir uma camada condutora 304 colocada entre uma primeira camada dielétrica 306 no primeiro lado 301 do substrato 302 e uma segunda camada dielétrica 308 no segundo lado 303 do substrato 302. A camada condutora 304 pode ser formada por um metal tal como cobre. A camada condutora 304 pode ser mais espessa do que outras camadas condutoras (por exemplo, camada Ml 382, camada M2 384, camada M3 386, camada M4 388) no EDS 300. A espessura da camada condutora 304 pode prover rigidez e/ou suporte estrutural para o EDS 300. A camada condutora 304 pode ser usada como um plano de aterramento ou um plano de potência de EDS 300.

[0072] Em um aspecto alternativo, o substrato 302 pode ser um substrato de núcleo. No aspecto alternativo, é contemplado que o substrato 302 pode incluir uma camada dielétrica (não mostrada) colocada entre uma primeira camada condutora (não mostrada) no primeiro lado 301 do substrato 302 e uma segunda camada condutora (não mostrada) em o segundo lado 303 do substrato 302. Por outras palavras, no aspecto alternativo, o substrato 302 pode ter uma camada dielétrica não condutora que revestida em lados opostos com camadas condutoras. Isoladores apropriados podem ser formados em torno de interconexões que se estendem através das várias camadas para evitar curto-circuito nas camadas condutoras em ambos os lados do dielétrico.

[0073] Uma cavidade 322 pode ser definida dentro do substrato 302. Como aqui descrito, a cavidade 322 pode ser uma abertura ou vazio definido pelas paredes laterais dentro do substrato 302. A cavidade 322 pode ser definida dentro do substrato 302 a partir do primeiro lado 301 do substrato 302. A cavidade 322 pode ser formada no substrato. A cavidade 322 pode ser suficientemente grande para segurar a pastilha 324. A cavidade 322 pode ser formada por métodos, incluindo, por exemplo, perfuração fotolitográfica, mecânica e/ou a laser. O fundo da cavidade 322 pode ser referido como o "piso" da cavidade 322. Em algumas implementações, a cavidade 322 pode ser desprovida da primeira camada dielétrica 306 e da camada condutora 304, e o piso da cavidade 322 pode ser definido pela segunda camada dielétrica 308 exposta na cavidade 322.

[0074] A pastilha 324 pode incluir circuitos/componentes ativos e/ou passivos. A pastilha 324 pode ser acoplada ao piso da cavidade 322 (por exemplo, acoplada à segunda camada dielétrica 308 dentro da cavidade 322) usando um sistema de colocação de componentes de tecnologia de montagem em superfície (SMT), comumente descrito como uma máquina pick-and-place, uma máquina de ligação por pastilha ou um granulador de chip. A pastilha 324 pode ser acoplada ao piso da cavidade 322, por exemplo, usando um adesivo, solda ou epóxi 326.

[0075] A pastilha 324 pode incluir uma pluralidade de pads condutores 328, 330, 332, 334 incluindo um primeiro pad condutor 328, um segundo pad condutor 330, um terceiro pad condutor 332 e uma quarto pad condutor 334 em um lado da pastilha 324 distal para o piso da cavidade 322. A pastilha 324 da ilustração exemplar na figura 3 não ilustra através de vias através de substrato (TSV) que foram formadas dentro da pastilha 324 em uma fundição durante a fabricação da pastilha 324. Em algumas implementações, a pastilha 324 pode incluir um ou mais TSVs formados dentro da pastilha 324 em uma fundição durante a fabricação de pastilha, mas não em uma localização predeterminada para uma interconexão de pastilha penetrante de segmento único, como a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316.

[0076] A pluralidade de pads condutores 328, 330, 332, 334 pode ser formada por qualquer material condutor (por exemplo, ouro). Uma camada condutora protetora 336 pode ser impressa, depositada, formada ou de outro modo provida em cada um dos vários pads condutores 328, 330, 332, 334. A camada condutora protetora 336 pode ser usada como um batente laser no caso de a perfuração a laser ser usada na formação de porções da primeira interconexão de pastilha penetrante de segmento único 310, da segunda interconexão 312, da terceira interconexão 314 e/ou da quarta interconexão de pastilha penetrante de segmento único 316.

[0077] A cavidade 322 pode ser cheia com um material de enchimento 338 para encapsular, proteger e/ou imobilizar a pastilha 324. O material de enchimento 338 pode ser, por exemplo, um material de encapsulamento, o material usado para formar a primeira camada dielétrica 306 ou um material pré-impregnado, tal como o material pré- impregnado laminado em uma superfície superior da primeira camada dielétrica 306.

[0078] Uma primeira camada laminada 340 (por exemplo, uma camada laminada no lado superior) pode ser provida à primeira camada dielétrica 306. Uma segunda camada laminada 342 (por exemplo, uma camada laminada no lado posterior) pode ser provida à segunda camada dielétrica 308. Cada uma das primeiras a camada laminada 340 e a segunda camada laminada 342 podem ser referidas como uma camada pré-impregnada (pré-impregnada). Cada uma das primeiras camadas laminadas 340 e segunda camada laminada 342 pode incluir uma ou mais camadas dielétricas e eletricamente condutoras. As camadas pré-impregnadas, por exemplo, podem ser providas depositando as camadas nas suas superfícies respectivas por pulverização. Outras maneiras de prover camadas pré-impregnadas e/ou camadas adicionais sobre o substrato 302 (por exemplo, laminação, ligação, afixação, aderência, formação) são conhecidas dos versados na técnica.

[0079] Na ilustração exemplar da figura 3, a pastilha 324 pode ser fabricada em uma fundição sem TSVs nos locais pré-designados para a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316. As TSVs em outras localizações são opcionais. Reduzir o número de TSVs em um determinado dado pode reduzir o custo do dado. Em vez de formar TSVs nos locais pré-designados para a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316 durante a fabricação de pastilhas em uma fundição, a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316 pode ser formada durante a integração EDS por perfuração posterior através de pelo menos uma porção do substrato 302 e da pastilha 324.

[0080] O primeiro pad condutor 328 e a quarto pad condutor 334 (que pode acoplar, respectivamente, à primeira interconexão de pastilha penetrante de segmento único 310 e à quarta interconexão de pastilha penetrante de segmento único 316) podem ser acopladas a circuitos ativos e/ou passivos da pastilha 324. Do mesmo modo, o segundo pad condutor 330 e o terceiro pad condutor 332 podem ser acoplados a circuitos ativos e/ou passivos da pastilha 324.

[0081] Em ligação com um processo de perfuração do lado superior associado à segunda interconexão 312 e terceira interconexão 314, a batente laser (por exemplo, camada condutora de proteção 336) impede que um furo formado por uma perfuradora a laser penetre através dos pads condutores 330, 332 (que podem ser formadas de ouro) e na pastilha 324. A segunda interconexão 312 e a terceira interconexão 314 não se estendem para dentro e/ou através da pastilha 324.

[0082] Em conexão com o processo de perfuração do lado posterior, a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316 podem se estender para dentro e/ou através da pastilha 324. Em outras palavras, a primeira interconexão de pastilha penetrante de segmento único 310 e a quarta interconexão de pastilha penetrante de segmento único 316 pode ser formada em um primeiro furo 310H e em um quarto furo 316H, respectivamente, perfurando através da segunda camada laminada 342 (se apropriado), a segunda camada dielétrica 308 (por exemplo, o piso da cavidade 322 formado no substrato 302), e dentro e/ou através da pastilha 324 acoplada ao piso da cavidade 322.

[0083] Note-se que, em ligação com um processo de perfuração posterior associado à primeira interconexão de pastilha penetrante de segmento único 310 e à quarta interconexão de pastilha penetrante de segmento único 316, não existe um batente laser no lado posterior da pastilha 324. De fato, uma parada a laser pode frustrar a formação da primeira interconexão de pastilha penetrante de segmento único 310 e da quarta interconexão de pastilha penetrante de segmento único 316 durante um processo de perfuração posterior implementado com uma perfuradora a laser. A eliminação da parada do laser, pelo menos em locais predeterminados para a formação de interconexões de pastilha penetrante de segmento único, pode economizar custos.

[0084] Na ilustração exemplar da figura 3, uma ou mais do segundo pad condutor 330 e o terceiro pad condutor 332 no lado superior da pastilha 324 podem ser ligadas a um primeiro nó 364 e a um quarto nó 370 (por exemplo, um pad condutor ou traço) a uma camada de EDS 300 abaixo do cunho 324. Um exemplo de um trajeto de encaminhamento para realizar tal ligação foi provido acima em ligação com a figura 1 e não será repetido para concisão.

[0085] Benefícios da implementação da primeira interconexão de pastilha penetrante de segmento único 310 podem incluir o fornecimento de um caminho de condução 376 através de um material condutor (por exemplo, cobre) do primeiro pad condutor 328 (ou camada condutora de proteção 336 no primeiro pad condutor 328) um pad ou traço 366 de camada M4 386 na segunda camada laminada 342. O trajeto de condução 376 pode passar através da pastilha 324 e a porção do substrato 302 entre a pastilha 324 e a segunda camada laminada 342. Porque a primeira interconexão de pastilha penetrante de segmento único 310 pode ser feita de um material condutor, o material condutor pode ser selecionado para minimizar a resistência de aterramento da dissipação térmica e maximizar a condutividade térmica. O trajeto de condução 376 está graficamente ilustrado na figura 3 por uma seta dupla face.

[0086] Os benefícios da implementação da quarta interconexão de pastilha penetrante de segmento único 316 ilustrada na figura 3 podem incluir um trajeto de condução 378 a partir do quarto pad condutor 334 (ou camada condutora protetora 336 no quarto pad condutor 334) para um terceiro nó 368 (por exemplo, uma terceira camada M3 386 de terceiro nó 368 (por exemplo, pad, traço)) sobre a segunda camada dielétrica 308. O trajeto de condução 378 pode passar através da pastilha 324 e da porção do substrato 302 entre a pastilha 324 e a segunda camada laminada 342. Porque a quarta interconexão de pastilha penetrante de segmento único 316 pode ser feita de um material de condução, o material de condução pode ser selecionado para minimizar a resistência de aterramento da dissipação térmica e maximizar a condutividade térmica. O trajeto de condução 378 está graficamente ilustrado na figura 3 por uma seta dupla face.