WO2019009023A1 - 撮像装置 - Google Patents

撮像装置 Download PDFInfo

- Publication number

- WO2019009023A1 WO2019009023A1 PCT/JP2018/022308 JP2018022308W WO2019009023A1 WO 2019009023 A1 WO2019009023 A1 WO 2019009023A1 JP 2018022308 W JP2018022308 W JP 2018022308W WO 2019009023 A1 WO2019009023 A1 WO 2019009023A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- voltage

- transistor

- impurity region

- signal

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/59—Control of the dynamic range by controlling the amount of charge storable in the pixel, e.g. modification of the charge conversion ratio of the floating node capacitance

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/62—Detection or reduction of noise due to excess charges produced by the exposure, e.g. smear, blooming, ghost image, crosstalk or leakage between pixels

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/63—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to dark current

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/65—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to reset noise, e.g. KTC noise related to CMOS structures by techniques other than CDS

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/68—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to defects

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/191—Photoconductor image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8037—Pixels having integrated switching, control, storage or amplification elements the integrated elements comprising a transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/809—Constructional details of image sensors of hybrid image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/811—Interconnections

Definitions

- the present disclosure relates to an imaging device.

- a charge coupled device (CCD) image sensor and a complementary metal oxide semiconductor (CMOS) image sensor are widely used in digital still cameras and digital cameras. As well known, these image sensors have photodiodes formed on a semiconductor substrate.

- CCD charge coupled device

- CMOS complementary metal oxide semiconductor

- a structure in which a photoelectric conversion portion having a photoelectric conversion layer is disposed above a semiconductor substrate has been proposed (for example, Patent Document 1).

- An imaging device having such a structure may be referred to as a stacked imaging device.

- a stacked imaging device is a node having an electrical connection with a photoelectric conversion unit, and has a floating node that temporarily accumulates one of positive and negative charges generated by photoelectric conversion as a signal charge.

- the floating node typically has a diffusion region formed on a semiconductor substrate supporting the photoelectric conversion unit, and a conductive structure electrically connecting the photoelectric conversion unit and the diffusion region to each other.

- the semiconductor substrate is provided with a CCD circuit or a CMOS circuit, and a signal corresponding to the amount of charge stored in the floating node is read out via the CCD circuit or the CMOS circuit.

- a leak current from an impurity region that accumulates charges generated by photoelectric conversion or to an impurity region may cause degradation in an image obtained. Therefore, it is useful to be able to reduce such leakage current.

- the leak current from the impurity region which accumulates the charge generated by photoelectric conversion or to the impurity region may be simply referred to as “dark current”.

- a semiconductor substrate having a first impurity region of n-type conductivity, a photoelectric conversion unit electrically connected to the first impurity region, and converting light into electric charge; a first terminal and a second terminal;

- the first terminal includes a capacitive element electrically connected to the first impurity region, and a voltage supply circuit electrically connected to the second terminal, wherein the voltage supply circuits are different from each other in the first A voltage and a second voltage are supplied to the second terminal, and the first impurity region stores positive charge among charges generated in the photoelectric conversion unit.

- the general or specific aspects may be realized in an element, a device, a module, a system or a method. Also, the comprehensive or specific aspects may be realized by any combination of elements, devices, apparatuses, modules, systems and methods.

- a dark current suppressed imaging device is provided.

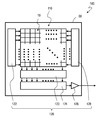

- FIG. 1 is a diagram schematically illustrating an exemplary configuration of an imaging device according to a first embodiment of the present disclosure.

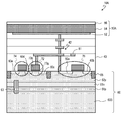

- FIG. 2 is a cross-sectional view schematically showing an exemplary device structure of the pixel 10.

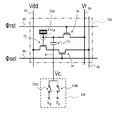

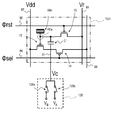

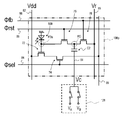

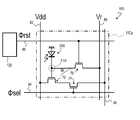

- FIG. 3 is a view schematically showing a typical example of the circuit configuration of the pixel 10A shown in FIG.

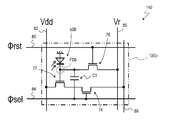

- FIG. 4A is a timing chart for explaining an exemplary operation of the pixel 10A having the circuit configuration shown in FIG.

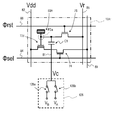

- FIG. 4B is a timing chart for explaining an exemplary operation when a p-type transistor is applied to the reset transistor 76 of the pixel 10A.

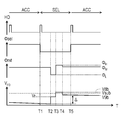

- FIG. 4C is a timing chart for explaining another example of the operation of the pixels 10A, 10Ap and 10Aq.

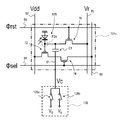

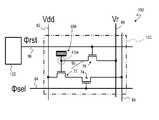

- FIG. 5 is a view schematically showing an example of another circuit configuration of the pixel 10.

- FIG. 6 is a view schematically showing an example of still another circuit configuration of the pixel 10.

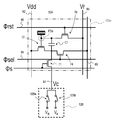

- FIG. 7A is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 7B is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 8 is a timing chart for explaining an exemplary operation of the pixel 10Ar shown in FIG. 7A or the pixel 10As shown in FIG. 7B.

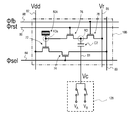

- FIG. 9A is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 9B is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 10 is a timing chart for explaining an exemplary operation of the pixel 10At shown in FIG. 9A or the pixel 10Au shown in FIG. 9B.

- FIG. 11A is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 11B is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 11C is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 12 is a diagram schematically illustrating an example of a circuit configuration of the pixel 10B included in the imaging device according to the second embodiment of the present disclosure.

- FIG. 13 is a diagram showing a more specific example to which the circuit configuration shown in FIG. 12 is applied.

- FIG. 11A is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 11B is a view schematically showing an example of still another circuit configuration of the pixel 10.

- FIG. 11C is a view schematically showing an example of still another circuit

- FIG. 14A is a timing chart for describing an exemplary operation of the pixel 10Bf having the circuit configuration shown in FIG.

- FIG. 14B is a timing chart for describing an exemplary operation when a p-type transistor is applied to the reset transistor 76 and the transistor 78 of the pixel 10Bf.

- FIG. 15 is a view showing a modified example of the imaging device according to the second embodiment of the present disclosure.

- FIG. 16 is a diagram showing another modified example of the imaging device according to the second embodiment of the present disclosure.

- FIG. 17A is a timing chart for illustrating an exemplary operation of the pixel 10Br having the circuit configuration shown in FIG. FIG.

- FIG. 17B is a timing chart for illustrating an exemplary operation when a p-type transistor is applied to the reset transistor 76 and the transistor 78 of the pixel 10Br and electrons are used as signal charges.

- FIG. 18 is a diagram showing still another modified example of the imaging device according to the second embodiment of the present disclosure.

- FIG. 19A is a diagram schematically illustrating an example of a circuit configuration of a pixel included in an imaging device according to a third embodiment of the present disclosure.

- FIG. 19B is a view schematically showing another example of the circuit configuration of the pixel included in the imaging device according to the third embodiment of the present disclosure.

- FIG. 20 is a timing chart for illustrating an exemplary operation of the pixel 10D having the circuit configuration shown in FIG. 19A.

- FIG. 21 is a diagram schematically illustrating an example of a circuit configuration of a pixel included in an imaging device according to a fourth embodiment of the present disclosure.

- FIG. 22A is a timing chart for describing an exemplary operation of the pixel 10C having the circuit configuration shown in FIG.

- FIG. 22B is a timing chart for illustrating an exemplary operation when a p-type transistor is applied to the reset transistor 76 of the pixel 10C and electrons are used as signal charges.

- FIG. 23 is a view showing a modified example of the imaging device according to the fourth embodiment of the present disclosure.

- FIG. 24 is a functional block diagram schematically illustrating an exemplary camera system according to a fifth embodiment of the present disclosure.

- This specification discloses an imaging device described in the following items.

- the imaging device according to claim 1, wherein the first impurity region stores positive charge among charges generated in the photoelectric conversion unit.

- the first transistor further includes a first transistor including the first impurity region as one of a source and a drain.

- the voltage supply circuit supplies the first voltage to the second terminal in a first period in which the first transistor is on, and in a second period after the first period and in which the first transistor is off.

- the first transistor further includes a first transistor including the first impurity region as one of a source and a drain.

- the voltage supply circuit supplies the first voltage to the second terminal during a first period in which the positive charge is accumulated in the first impurity region, and the first transistor is turned on after the first period.

- the semiconductor substrate has a second impurity region

- the first transistor includes the second impurity region as the other of a source and a drain,

- a semiconductor substrate having a first impurity region of p-type conductivity; A photoelectric conversion unit electrically connected to the first impurity region to convert light into charge; A capacitive element having a first terminal and a second terminal, wherein the first terminal is electrically connected to the first impurity region; A voltage supply circuit electrically connected to the second terminal; The voltage supply circuit supplies first and second voltages different from each other to the second terminal,

- the imaging device according to claim 1, wherein the first impurity region stores negative charge among charges generated in the photoelectric conversion unit.

- the first transistor further includes a first transistor including the first impurity region as one of a source and a drain.

- the voltage supply circuit supplies the first voltage to the second terminal in a first period in which the first transistor is on, and in a second period after the first period and in which the first transistor is off.

- the first transistor further includes a first transistor including the first impurity region as one of a source and a drain.

- the voltage supply circuit supplies the first voltage to the second terminal in a first period in which the negative charge is accumulated in the first impurity region, and the first transistor is turned on after the first period.

- the semiconductor substrate has a second impurity region

- the first transistor includes the second impurity region as the other of a source and a drain,

- the capacitive element and the first impurity region are at least a part of a charge storage node that stores charges of one polarity among charges generated in the photoelectric conversion unit,

- the imaging device according to any one of Items 1 to 10, wherein a capacitance value of the capacitive element is smaller than a capacitance value of a portion other than the capacitive element in the charge storage node.

- the photoelectric conversion unit is A first electrode, A second electrode facing the first electrode; A photoelectric conversion layer located between the first electrode and the second electrode; 12.

- the imaging device according to any one of items 1 to 11, wherein the first electrode is electrically connected to the first impurity region.

- a semiconductor substrate having a first impurity region and a second impurity region; A photoelectric conversion unit electrically connected to the first impurity region; A first transistor including a first impurity region as one of a source region and a drain region and including a second impurity region as the other of the source region and the drain region; And a voltage supply circuit electrically connected to the second impurity region, The voltage supply circuit applies a first voltage to the second impurity region in a first period in which the first transistor is on, and after the first period and in a second period in which the first transistor is off, An imaging device applying a different second voltage to the second impurity region.

- the configuration of the item 1 it is possible to prevent the occurrence of dark current due to forward bias applied to the pn junction between the first impurity region and the periphery thereof when the first transistor is turned off.

- a voltage with a smaller voltage difference can be applied as the first voltage and the second voltage.

- a voltage with a smaller voltage difference can be applied as the first voltage and the second voltage.

- the first transistor is n-type, The imaging device according to any one of Items 1 to 10, wherein the second voltage is higher than the first voltage.

- the potential of the first impurity region and / or the potential of the node between the first transistor and the second transistor can be avoided from being lower than the substrate potential of the semiconductor substrate.

- the first transistor is p-type, The imaging device according to any one of Items 1 to 10, wherein the second voltage is lower than the first voltage.

- the potential of the first impurity region and / or the potential of the node between the first transistor and the second transistor exceeds the substrate potential of the semiconductor substrate.

- the reset transistor is n-type, 14.

- the potential of the first impurity region and / or the potential of the node between the first transistor and the second transistor becomes lower than the substrate potential of the semiconductor substrate.

- the influence of dark current on a signal corresponding to the voltage level of the charge storage node after reset can be suppressed.

- the reset transistor is p-type, 14.

- the potential of the first impurity region and / or the potential of the node between the first transistor and the second transistor exceeds the substrate potential of the semiconductor substrate.

- the charge storage node includes an n-type first impurity region formed in the semiconductor substrate, 19.

- the charge storage node includes a p-type first impurity region formed in the semiconductor substrate, 19.

- the photoelectric converter is A first electrode supported on a semiconductor substrate; A second electrode, Further comprising a photoelectric conversion layer located between the first electrode and the second electrode; The imaging device according to any one of Items 1 to 17 or any one of Items 19 to 22, wherein the first electrode is electrically connected to the first impurity region.

- An imaging device comprising a plurality of pixels, wherein Each pixel of the plurality of pixels is A photoelectric conversion unit that generates charges by photoelectric conversion; A charge storage node for storing charge; A reset transistor electrically connected to the charge storage node and resetting the potential of the charge storage node to a reference potential; An amplification transistor electrically connected to the charge storage node and outputting a signal voltage according to the charge stored in the charge storage node; A capacitive element having one end electrically connected to the charge storage node and the other end connected to a voltage source; Equipped with A first voltage is applied to the other end of the capacitive element in the exposure period in which charge is stored in the charge storage node, and the other end of the capacitive element is different from the first voltage in the reset period in the non-exposure period other than the exposure period. 2 voltage is applied, An imaging device, wherein the reset period is a part of a non-exposure period, and a reset transistor resets the potential of the charge storage node to

- an imaging device capable of reducing leakage current is provided.

- the potential of the charge storage node is set to a low potential in the exposure period, and the potential of the charge storage node is high in the non-exposure period. By setting the potential, the dark current can be reduced without deteriorating the circuit characteristics.

- the voltage change of the control signal applied to the other end of the capacitive element can be applied to the FD node through the capacitive element.

- any control signal in the pixel can be used also as a control signal given to the capacitive element, so the number of control signal lines used can be reduced.

- a switch transistor electrically connected between one end of the capacitive element and the charge storage node, or between the voltage source and the other end, for switching connection / disconnection of the capacitive element and the charge storage node, item 26 27.

- the imaging device described in Item 29 it is possible to selectively use the FD potential control mode for controlling the potential of the charge storage node and the high gain mode for efficiently converting the signal charge.

- the charge is a hole, The imaging device according to any one of items 25 to 29, wherein the second voltage is higher than the first voltage.

- imaging device described in Item 30 it is possible to provide an imaging device that can reduce leakage current and that uses holes as signal charges.

- the charge is an electron, The imaging device according to any one of items 25 to 29, wherein the second voltage is lower than the first voltage.

- imaging device described in Item 32 it is possible to provide an imaging device that can reduce leakage current and that uses electrons as signal charges.

- the imaging device described in Item 35 it is possible to suppress the power supply noise of the control signal applied to the capacitive element from being mixed into the charge storage node.

- a high output can be obtained from the amplification transistor even for the potential of the charge storage node at a low level, so that the voltage range necessary for the operation of the current source of the source follower circuit can be secured. It becomes possible.

- the photoelectric converter is A first electrode, A second electrode facing the first electrode; A photoelectric conversion film located between the first electrode and the second electrode and generating charges by photoelectric conversion;

- the imaging device according to any one of Items 25 to 36, having:

- an imaging device including a photoelectric conversion unit having a photoelectric conversion film, which can reduce the leakage current.

- FIG. 1 schematically shows an exemplary configuration of an imaging device according to a first embodiment of the present disclosure.

- An imaging device 100 illustrated in FIG. 1 includes a pixel array 110 including a plurality of pixels 10 and a peripheral circuit 120.

- the pixel array 110 includes a plurality of pixels 10 arranged, for example, in a matrix of m rows and n columns.

- m and n are natural numbers.

- the pixels 10 are two-dimensionally arranged on the semiconductor substrate 60, for example, to form an imaging region.

- the number and arrangement of the pixels 10 in the pixel array 110 are not limited to the illustrated example.

- the number of pixels 10 included in the imaging device 100 may be one.

- the imaging device 100 can be used as a line sensor.

- Each pixel 10 includes a photoelectric conversion unit that receives light and generates a charge.

- the photoelectric conversion portion of each pixel 10 has a structure including a buried photodiode formed on the semiconductor substrate 60 or a part of the photoelectric conversion layer disposed above the region corresponding to the imaging region in the semiconductor substrate 60. obtain.

- terms such as “upper” and “lower” are used only to designate the mutual arrangement between members, and are not intended to limit the posture when using the imaging device 100.

- the peripheral circuit 120 has a predetermined voltage applied to the vertical scanning circuit 122, the signal holding circuit 123, the horizontal scanning circuit 124, the output stage amplifier 126, and each pixel 10 in the pixel array 110. And a voltage supply circuit 128 for supplying the voltage.

- the peripheral circuit 120 is provided on the semiconductor substrate 60 on which the pixel array 110 described above is formed.

- the arrangement of peripheral circuit 120 is not limited to this example, and part or all of peripheral circuit 120 may be arranged on another substrate different from semiconductor substrate 60.

- the vertical scanning circuit 122 is also referred to as a row scanning circuit, and has, for example, a connection with an address signal line and a reset signal line provided corresponding to each row of the plurality of pixels 10.

- the vertical scanning circuit 122 can execute accumulation and readout of signal charges in the pixels 10 and reset of the accumulated signal charges on a row basis by supplying predetermined signals to the address signal line and the reset signal line. it can.

- the peripheral circuit 120 may have two or more vertical scanning circuits 122. In FIG. 1, in order to avoid complication of the drawing, illustration of various signal lines such as address signal lines and reset signal lines is omitted. Arrows in FIG. 1 schematically indicate the flow of signals supplied to various signal lines such as address signal lines and reset signal lines.

- the signal holding circuit 123 is connected to a vertical signal line (not shown) provided corresponding to each column of the plurality of pixels 10, and has a function of temporarily holding a signal output to the vertical signal line.

- the signal may be held in the form of analog values or in the form of digital values subjected to analog-to-digital conversion.

- the signal holding circuit 123 outputs, to the horizontal scanning circuit 124, the difference between the signal read from the pixel 10 after accumulation of the signal charge and the signal read from the pixel 10 after reset of the signal charge. .

- the operations between the signals may be performed in analog or digital form.

- the horizontal scanning circuit 124 also referred to as a column scanning circuit, typically includes an analog-to-digital converter circuit in part.

- the horizontal scanning circuit 124 has a function of reading out the difference signal obtained by the signal holding circuit 123 for each row of the plurality of pixels 10 to the output stage amplifier 126.

- the voltage supply circuit 128 is electrically connected to each pixel 10, and is configured to switch and supply two or more predetermined voltages to each pixel 10 when the imaging device 100 operates.

- the second voltage V B is a voltage different from the first voltage V A.

- the voltage supply circuit 128 may be configured to be capable of applying a predetermined voltage to each pixel 10 when the imaging device 100 operates, and is not limited to a specific power supply circuit.

- the voltage supply circuit 128 may be a circuit that generates a predetermined voltage, or may be a circuit that converts a voltage supplied from another power supply into a predetermined voltage.

- the voltage supply circuit 128 may be part of the vertical scanning circuit 122.

- the voltage applied from the voltage supply circuit 128 to each pixel 10 is not limited to two different voltages.

- the voltage supply circuit 128 may be configured to be able to switch between three or more different voltages and supply them to each pixel 10.

- FIG. 2 schematically illustrates a cross section of an exemplary device structure of the pixel 10.

- FIG. 2 schematically shows the shape, size and arrangement of each part in the pixel 10, and the shape, size and arrangement of each part shown in FIG. 2 do not necessarily reflect the shape, size and arrangement in a real device. The same applies to the other drawings of the present disclosure.

- the pixel 10A illustrated in FIG. 2 is an example of the above-described pixel 10.

- the pixel 10A roughly includes a part of the semiconductor substrate 60 and the photoelectric conversion unit 50A supported by the interlayer insulating layer 40 covering the semiconductor substrate 60.

- the photoelectric conversion unit 50 ⁇ / b> A includes the photoelectric conversion layer 54 located above the region corresponding to the imaging region in the semiconductor substrate 60. That is, a stacked imaging device is illustrated as the imaging device 100 here.

- the semiconductor substrate 60 includes a support substrate 60S and one or more semiconductor layers formed on the support substrate 60S.

- a p-type silicon substrate is illustrated as the support substrate 60S.

- Impurity regions 60 a to 60 e and an element isolation region 65 are provided in the semiconductor substrate 60.

- Each of impurity regions 60a to 60e is typically an n-type diffusion region.

- the photoelectric conversion unit 50A supported by the semiconductor substrate 60 includes the pixel electrode 52 on the interlayer insulating layer 40, the counter electrode 56 positioned farther from the semiconductor substrate 60 than the pixel electrode 52, and the pixel The photoelectric conversion layer 54 located between the electrode 52 and the counter electrode 56 is provided.

- the pixel electrode 52 is an electrode formed of metal such as aluminum or copper, metal nitride, or polysilicon to which conductivity is imparted by doping an impurity.

- the pixel electrode 52 is electrically separated from the pixel electrode 52 in another adjacent pixel 10A by being spatially separated.

- the counter electrode 56 is formed of a transparent conductive material such as ITO.

- transparent means transmitting at least a portion of light in the wavelength range to be detected, and it is not essential to transmit light over the entire wavelength range of visible light.

- the counter electrode 56 may be formed across the plurality of pixels 10A, while the pixel electrode 52 is separated between the pixel electrodes 52 in other adjacent pixels 10A.

- the counter electrode 56 is typically disposed above the semiconductor substrate 60 in the form of a single continuous electrode.

- the photoelectric conversion layer 54 is formed of an organic material or an inorganic material such as amorphous silicon.

- the photoelectric conversion layer 54 is formed, for example, by vacuum evaporation, and may have a thickness of about 500 nm.

- the photoelectric conversion layer 54 may have a layer composed of an organic material and a layer composed of an inorganic material.

- the photoelectric conversion layer 54 receives light incident through the counter electrode 56 and generates positive and negative charges by photoelectric conversion. Similar to the counter electrode 56, the photoelectric conversion layer 54 may also be disposed above the semiconductor substrate 60 in the form of a single continuous layer across the plurality of pixels 10A.

- a voltage line connected to a power supply (not shown) is connected to the counter electrode 56, and the counter electrode 56 has a predetermined bias voltage when the imaging device 100 operates. Receive the supply. By controlling the potential of the counter electrode 56 by application of a predetermined bias voltage, one of the positive and negative charges generated by photoelectric conversion can be collected by the pixel electrode 52 as a signal charge.

- the bias voltage applied to the counter electrode 56 may be supplied from the voltage supply circuit 128 described above.

- a bias voltage that is higher than the pixel electrode 52 may be applied to the counter electrode 56.

- positive charge Typical of positive charges as signal charges are holes. It is of course possible to use a negative charge, eg an electron, as the signal charge.

- a bias voltage that is lower than that of the pixel electrode 52 may be applied to the counter electrode 56.

- the pixel 10A includes the connection portion 42 disposed in the interlayer insulating layer 40. As schematically shown in FIG. 2, one end of the connection portion 42 is connected to the pixel electrode 52 of the photoelectric conversion unit 50.

- the connection unit 42 includes a plurality of wiring layers and a plurality of plugs, and electrically connects the photoelectric conversion unit 50A to a circuit formed on the semiconductor substrate 60.

- the plurality of wiring layers and the plurality of plugs are typically formed of a metal such as copper or tungsten or a metal compound such as metal nitride or metal oxide.

- the signal detection transistor 72, the address transistor 74, and the reset transistor 76 are formed on the semiconductor substrate 60.

- an n-channel field effect transistor represented by an n-channel MOS is exemplified as the signal detection transistor 72, the address transistor 74, and the reset transistor 76.

- a p-type transistor instead of the n-type transistor.

- an n-type silicon substrate may be used as the support substrate 60S, and the p-type is selected as the conductivity type of the impurity regions 60a to 60e.

- the reset transistor 76 includes the impurity region 60a formed in the semiconductor substrate 60 as one of the drain region and the source region, and includes the impurity region 60b as the other of the drain region and the source region.

- the connection portion 42 has a connection with the impurity region 60a, and therefore, the impurity region 60a is electrically connected to the pixel electrode 52 of the photoelectric conversion portion 50A through the connection portion 42. It is connected.

- a reset voltage line for supplying a reset voltage which is a reference voltage for reset is connected to the impurity region 60b.

- the reset transistor 76 is switched on and off to switch supply and cutoff of the reset voltage supplied from the reset voltage line to the impurity region 60a.

- which of the impurity region 60a and the impurity region 60b functions as the drain region of the reset transistor 76 is determined by the potential of the impurity region 60a and the impurity region 60b.

- the impurity region 60a and the impurity region 60b will be described as the drain region and the source region, respectively.

- the drain region and the source region may be interchanged.

- the imaging device 100 includes another transistor connected in series to the reset transistor 76, the same applies to the other transistors connected in series to the reset transistor 76.

- the signal detection transistor 72 includes a gate insulating layer 72g on the semiconductor substrate 60, a gate electrode 72e on the gate insulating layer 72g, an impurity region 60c as a drain region, and an impurity region 60d as a source region.

- a power supply line (not shown) is connected to the impurity region 60c, and a power supply voltage of, for example, 3.3 V is applied to the impurity region 60c from the power supply line when the imaging device 100 operates.

- connection portion 42 is also connected to the gate electrode 72 e of the signal detection transistor 72. That is, the gate electrode 72 e of the signal detection transistor 72 is electrically connected to the pixel electrode 52 of the photoelectric conversion unit 50 A through the connection unit 42.

- address transistor 74 includes an impurity region 60d as a drain region and an impurity region 60e as a source region.

- the address transistor 74 is electrically connected to the signal detection transistor 72 by sharing the impurity region 60 d with the signal detection transistor 72.

- a vertical signal line (not shown) is connected to impurity region 60e.

- the circuit in the pixel 10A is electrically separated from the circuit in the other adjacent pixel 10A by the element isolation region 65.

- the element isolation region 65 is also provided between the signal detection transistor 72 and the reset transistor 76.

- connection portion 42 has a connection with the pixel electrode 52.

- the impurity region 60 a and the gate electrode 72 e of the signal detection transistor 72 are electrically connected to the pixel electrode 52 through the connection portion 42.

- the pixel electrode 52, the connection portion 42, the impurity region 60a, and the gate electrode 72e function as a charge storage node that temporarily holds the signal charge collected by the pixel electrode 52.

- the pixel 10A further includes a control line 81 electrically connected to the connection portion 42.

- the control line 81 is a signal line connected to the voltage supply circuit 128 described above. That is, here, the impurity region 60a has an electrical connection with the voltage supply circuit 128 described above. As described later, a capacitive element or the like may be interposed between the impurity region 60 a and the voltage supply circuit 128.

- a voltage supply circuit 128 to the connecting portion 42 which constitutes a part of the charge storage nodes are electrically connected, switches the output of the voltage supply circuit 128 between the first voltage V A and the second voltage V B. This makes it possible, for example, to temporarily change the potential of the charge storage node after reset.

- the semiconductor substrate 60 has one or more semiconductor layers on the support substrate 60S.

- the semiconductor layer on the support substrate 60S includes a first p-type semiconductor layer 61p, an n-type semiconductor layer 61n, and a second p-type semiconductor layer 62p.

- the above-described impurity regions 60a to 60e and the element isolation region 65 are formed in the second p-type semiconductor layer 62p as ap well.

- the n-type semiconductor layer 61 n is located between the first p-type semiconductor layer 61 p and the second p-type semiconductor layer 62 p, and via an unshown well contact provided outside the imaging region when the imaging device 100 operates. The potential is controlled.

- the n-type semiconductor layer 61 n suppresses the inflow of minority carriers from the support substrate 60S or the peripheral circuit 120 to the charge storage node for storing signal charges.

- the semiconductor substrate 60 is a p-type provided between the second p-type semiconductor layer 62p and the support substrate 60S so as to penetrate the first p-type semiconductor layer 61p and the n-type semiconductor layer 61n. It has a region 63.

- the p-type region 63 has a relatively high impurity concentration, and electrically connects the second p-type semiconductor layer 62p and the support substrate 60S to each other.

- a substrate contact (not shown) is provided outside the imaging region, and the potential of the support substrate 60S and the second p-type semiconductor layer 62p is controlled via the substrate contact when the imaging device 100 operates. In other words, when the imaging device 100 operates, the substrate potential of the semiconductor substrate 60 is controlled via the substrate contact.

- the voltage supply circuit 128 described above may be configured to supply the substrate potential of the semiconductor substrate 60 via the substrate contact.

- an n-type transistor is applied as the signal detection transistor 72, the address transistor 74, and the reset transistor 76 as in the example described here, the substrate potential is typically ground.

- impurity region 60a constitutes a part of the charge storage node that temporarily stores the signal charge generated by photoelectric conversion unit 50A. This is because the junction capacitance formed by the pn junction between the impurity region 60a and the second p-type semiconductor layer 62p functions as a capacitance for accumulating at least a part of the signal charge.

- the pn junction between the impurity region 60a and the second p-type semiconductor layer 62p produces a depletion layer.

- lattice defects are present, and in particular, various lattice defects caused by impurities, dangling bonds, etc. exist on the surface of the semiconductor substrate 60. If a lattice defect exists in the depletion layer, for example, mixing of a charge different from the original signal charge into the impurity region 60a is likely to occur. In other words, lattice defects located in the depletion layer can cause dark current. Dark current results in a reduction in the signal-to-noise ratio and degrades the quality of the obtained image. If the depletion layer in the semiconductor substrate 60 can be reduced as much as possible to reduce lattice defects located in the depletion layer among lattice defects, it is useful because deterioration in image quality due to dark current is suppressed.

- the impurity region 60a in order to reduce the depletion layer formed by the pn junction between the impurity region 60a and the second p-type semiconductor layer 62p, the impurity region 60a after discharging the signal charge from the impurity region 60a. It is effective to make the potential of V close to the substrate potential as much as possible. That is, it is effective to make the potential of the impurity region 60a after reset as close as possible to the substrate potential. For example, when the signal charge is a hole and the substrate potential is ground, it is useful to apply a voltage as low as possible, which is close to 0 V, as the reset voltage.

- the potential of impurity region 60a is increased by electrical coupling through a circuit element such as a transistor connected to impurity region 60a. If it fluctuates, the potential of the impurity region 60a may fall below the substrate potential.

- a field effect transistor when a field effect transistor is connected to an n-type impurity region in a floating node that stores signal charge, the transistor is turned on and on due to the effect of electrical coupling via parasitic capacitance between the source and drain.

- the potential of the impurity region may decrease due to the switching off.

- forward bias is applied to the pn junction between the impurity region and the surrounding p well, and from the p-type silicon substrate as a support substrate Holes will flow into the impurity region. That is, there is a possibility that dark current occurs and the image quality of the obtained image is degraded.

- the present inventors have repeated studies in view of the above, for example, by varying the potential of the charge storage node after the reset by switching the first voltage V A and the second voltage V B, impurities accumulate signal charge region It has been found that it is possible to prevent the charge different from the original signal charge from being mixed in the impurity region with the switching on and off of the connected transistor.

- FIG. 3 schematically shows a typical example of the circuit configuration of the pixel 10A shown in FIG. Note that, in FIG. 2, illustration of voltage lines for supplying a predetermined bias voltage to the counter electrode 56 of the photoelectric conversion unit 50A is omitted in FIG. 2 in order to prevent the drawing from becoming excessively complicated. Likewise, in the following drawings, illustration of voltage lines for supplying a predetermined bias voltage to the counter electrode 56 is omitted.

- the gate of the signal detection transistor 72 is connected to the photoelectric conversion unit 50A. It can be said that the node FDa between the photoelectric conversion unit 50A and the signal detection transistor 72 corresponds to a charge storage node. A voltage corresponding to the signal charge stored in the node FDa is applied to the gate of the signal detection transistor 72. As shown, the drain of the signal detection transistor 72 is connected to a power supply line 82 as a source follower power supply for supplying the power supply voltage Vdd, and the source of the signal detection transistor 72 is a vertical signal via the address transistor 74. Line 89 is connected. That is, the signal detection transistor 72 and the address transistor 74 form a source follower.

- An address signal line 84 connected to the vertical scanning circuit 122 is connected to the gate of the address transistor 74.

- the vertical scanning circuit 122 can read out the signal from the pixel 10 A to the vertical signal line 89 by controlling the address signal selsel applied to the address signal line 84.

- the reset transistor 76 is also connected to the node FDa.

- the side of the source and drain of the reset transistor 76 which is not connected to the node FDa is connected to the reset voltage line 85.

- a predetermined reset voltage Vr is applied to the reset voltage line 85.

- the reset signal line 86 connected to the vertical scanning circuit 122 is connected to the gate of the reset transistor 76. Under control of the reset signal ⁇ rst applied to the reset signal line 86, the vertical scanning circuit 122 can turn on the reset transistor 76 and apply the reset voltage Vr to the charge storage node. As described with reference to FIG.

- the reset transistor 76 includes the impurity region 60a forming a part of the charge storage node as a drain region or a source region. When the reset transistor 76 is turned on, the signal charge is discharged from the charge storage node, and the potential of the charge storage node is reset.

- the voltage supply circuit 128 is further electrically connected to the node FDa.

- the capacitive element C1 is interposed between the node FDa and the control line 81 connected to the voltage supply circuit 128.

- the node FDa is connected to one of the two terminals of the capacitive element C1. That is, in this example, one terminal of the capacitive element C1 is electrically connected to the impurity region 60a.

- the voltage supply circuit 128 is connected to the other of the two terminals of the capacitive element C1.

- the capacitive element C1 may have, for example, a metal-insulator-semiconductor (MIS) structure disposed in the interlayer insulating layer 40, or may be a depression-type MOS (DMOS) capacitor. Alternatively, it may be a MIM (metal-insulator-metal) structure. Adopting the MIM structure makes it easy to obtain a larger capacity value.

- MIS metal-insulator-semiconductor

- DMOS depression-type MOS

- MIM metal-insulator-metal

- voltage supply circuit 128 has switching elements 128a and 128b configured of field effect transistors or the like. That is, here, the voltage supply circuit 128, the switching by switching the switching elements 128a and 128b on and off, the voltage Vc applied to the control line 81 between the first voltage V A and the second voltage V B It is possible.

- FIG. 4A is a timing chart for explaining an exemplary operation of the pixel 10A having the circuit configuration shown in FIG.

- the top chart in FIG. 4A shows pulses of the horizontal synchronization signal HD.

- the period from the rise of a certain pulse to the rise of the next pulse corresponds to 1 H which is one horizontal scanning period.

- the reset of the pixels 10A belonging to one certain row among the plurality of pixels 10A included in the pixel array 110 and the readout of the signal from the pixels 10A are performed.

- the double arrow SEL in FIG. 4A indicates a selection period in which the address transistor 74 of the pixel of interest is turned on, and the arrow ACC indicates a non-selection period in which the address transistor 74 is turned off.

- the bottom chart in FIG. 4A shows temporal changes of the potential of the node FDa, ie, the potential V FD of the impurity region 60a, and the second chart from the bottom is applied from the voltage supply circuit 128 to the control line 81.

- the temporal change of voltage Vc is shown.

- the first voltage V A is applied to the control line 81.

- the address signal selsel After accumulation of signal charges by exposure, the address signal selsel is set to high level at time T1. By setting the address signal selsel to a high level, a first signal of a voltage level corresponding to the signal charge stored in the charge storage node is read out to the vertical signal line 89 through the signal detection transistor 72 and the address transistor 74. The read first signal is temporarily held by the signal holding circuit 123 shown in FIG.

- the reset signal rstrst is set to the high level, and the reset transistor 76 is turned on.

- the reset transistor 76 is turned on, the signal charge is discharged from the charge storage node, and the potential of the charge storage node is reset.

- the potential V FD of the impurity regions 60a by the reset voltage Vr is applied to the node FDa falls to Vr.

- a voltage higher than the substrate potential Vsub is used as the reset voltage Vr. Therefore, here, Vr> Vsub.

- the substrate potential Vsub is 0 V, a positive voltage near 0 V is used as the reset voltage Vr.

- the reset signal rstrst is set to low level, and the reset transistor 76 is turned off.

- the reset transistor 76 includes the impurity region 60 a as a drain region or a source region. Therefore, when the reset transistor 76 is turned off, the potential V FD of the impurity region 60a may be further lowered from Vr due to the electrical coupling caused by the parasitic capacitance of the reset transistor 76. As described above, at this time, if the potential V FD falls below the substrate potential Vsub, extra holes flow into the impurity region 60a.

- the potential V FD of the impurity region 60a immediately after the reset transistor 76 is off is V1a satisfying the relationship of Vr>V1a> Vsub.

- V1a may be about 0.2V. That is, the second voltage V B and appropriate selection, by switching between the output from the voltage supply circuit 128 of the first voltage V A and the second voltage V B, the potential V FD is the substrate potential Vsub of the impurity regions 60a It is prevented that it falls below.

- a potential difference of 0.2 V can be secured at the potential V FD of the impurity region 60 a with reference to the substrate potential. That is, the inflow of unnecessary holes to the impurity region 60a due to the potential V FD falling below the substrate potential Vsub is prevented. In other words, dark current is suppressed.

- V B the source of the reset transistor 76 - in consideration of the magnitude of the parasitic capacitance between the drain potential V FD when off the reset transistor 76 satisfies the relation of V1a> Vsub It is sufficient to select a voltage that will

- a second signal corresponding to the voltage level of the charge storage node after discharge of the signal charge is transmitted through the address transistor 74 during a period until time T4 when the next pulse of the horizontal synchronization signal HD And read out to the vertical signal line 89.

- the signal holding circuit 123 outputs the difference ⁇ between the first signal and the second signal to the horizontal scanning circuit 124 as a signal representing an image.

- the address transistor 74 is turned off, and accumulation of signal charge of the next frame is started.

- the voltage supply circuit 128 applies the first voltage V A to the impurity region 60 a during the first period from time T2 to T3 in which the reset transistor 76 is turned on. It followed, in the second period of time T3 ⁇ T4, and is configured to switch the voltage applied to the impurity regions 60a to a second voltage V B.

- the potential V FD of the impurity regions 60a with the off of the reset transistor 76 is possible to prevent that fall below the substrate potential Vsub. Therefore, it is possible to suppress the dark current generated by the flow of extra holes into impurity region 60a.

- capacitive element C1 since capacitive element C1 has an electrical connection with node FDa, at least one of the charge storage nodes for temporarily holding the signal charge, like impurity region 60a. Make up the department. In other words, the connection of capacitive element C1 to node FDa increases the capacitance value of the entire charge storage node. It is advantageous for the capacitance value of the capacitive element C1 to be as small as possible for the following two reasons.

- the first reason is that an increase in the capacitance value of the entire charge storage node results in a decrease in conversion gain. If the conversion gain is lowered, the influence of noise in the subsequent stage circuit becomes large, and there is a possibility that the SN ratio may be lowered. Therefore, from the viewpoint of avoiding the decrease in the SN ratio, it is useful that the capacitance value of the capacitive element C1 be as small as possible.

- the second reason is that if the capacitive element C1 has a relatively large capacitance value, the influence of noise mixing on the control line 81 via the capacitive element C1 to the node FDa may increase.

- Noise included in the voltage applied to control line 81 can be mixed in node FDa by electrical coupling via capacitive element C1.

- the configuration in which the voltage supplied to control line 81 is commonly applied to the charge storage nodes of the pixels belonging to the same row via the capacitive element C1 in other words, the first voltage V A

- the noise on the control line 81 may appear on the image as a horizontal line noise. It is useful to be able to suppress the horizontal noise because the horizontal noise tends to be easily recognized by the viewer of the image as compared to the random noise in units of pixels.

- capacitance value of capacitance element C1 is C 1 and the capacitance value of a portion other than capacitance element C1 of the charge storage nodes is C FD

- the magnitude of the voltage variation transmitted to node FDa is the voltage variation of control line 81 It is represented by the product of C 1 / (C 1 + C FD )). Therefore, in terms of horizontal noise suppression, capacitance value C 1 of the capacitor C1 is advantageously as small as possible.

- the capacitance value C 1 of the capacitor element C1, the capacitance value of the portions other than the capacitor element C1 of the charge storage node is beneficial to be smaller than C FD. It is made smaller than the capacitance value C FD portion other than the capacitive element C1 of the charge storage node capacitance value C 1 of the capacitor C1, the reduction in the SN ratio caused by connecting a capacitor C1 to the node FDa The degree may be smaller than the degree of reduction of the SN ratio when the F value is increased by one level.

- the capacitance value C 1 of the capacitor element C1 with the degree less than half of the capacitance value C FD, the degree of reduction of the SN ratio caused by connecting a capacitor C1 to node FDa, converted to F value

- the change can be limited to about (1/2) or less.

- the reset voltage Vr Since a larger positive voltage is used as the reset voltage Vr, the influence of the reduction in the potential V FD of the impurity region 60a due to the electrical coupling caused by the parasitic capacitance of the reset transistor 76 accompanying the turning off of the reset transistor 76 is small. It can be said. However, when using electrons as signal charges, it is necessary to use a higher voltage as the reset voltage Vr in order to improve the number of saturated electrons, and from the viewpoint of securing the number of saturated electrons sufficient for the required dynamic range, It is more advantageous to use holes as the charge.

- the conductivity type of each region in the semiconductor substrate 60 may be switched between n-type and p-type.

- the p-type transistor as the reset transistor 76 as described below, as the second voltage V B, using a voltage lower than the first voltage V A.

- FIG. 4B is a timing chart for explaining an exemplary operation when a p-type transistor is applied to the reset transistor 76 of the pixel 10A.

- a p-type transistor is applied to the reset transistor 76

- a higher voltage is used as a substrate potential Vsub than when an n-type transistor is applied to the reset transistor 76.

- Substrate potential Vsub may be, for example, about 3.3V.

- the effect of the change in the potential V FD of the impurity region 60a due to the electrical coupling caused by the parasitic capacitance of the reset transistor 76 is better when holes are used as signal charges. Is small. This is because of the same reason as in the case where an n-type transistor is applied to the reset transistor 76 and electrons are used as signal charges. However, in order to secure a sufficient number of saturated electrons, it is necessary to secure a sufficient potential difference between the substrate potential and the potential V FD of the impurity region 60a. On the other hand, if the signal charge is an electron, a voltage near 3.3 V which is the substrate potential may be used as the reset voltage Vr. When a p-type transistor is applied to the reset transistor 76, the signal charge is Using electrons is easier to secure a sufficient number of saturated electrons in the required dynamic range while avoiding circuit complexity.

- FIG. 4B shows an example of operation in the case where a p-type transistor is applied to the reset transistor 76 and electrons are used as signal charges.

- the reset transistor 76 is a p-type transistor and electrons are used as signal charges

- the signal detection transistor 72 and the address transistor 74 are also formed on the semiconductor substrate 60 as p-type transistors.

- the potential V FD of the impurity region 60a gradually decreases due to the accumulation of the signal charge due to the exposure.

- the address signal selsel is set to low level at time T1 to turn on the address transistor 74, and the first signal is read out to the vertical signal line 89.

- the reset signal rstrst is set to low level, and the reset transistor 76 is turned on.

- the potential V FD of the impurity region 60a rises to Vr.

- the reset voltage Vr at this time for example, a voltage of 2.8 V which is near the substrate potential Vsub and lower than the substrate potential Vsub is used.

- the reset signal rstrst is set to the high level, and the reset transistor 76 is turned off.

- the electrical coupling caused by the parasitic capacitance of the reset transistor 76 may further increase the potential V FD of the impurity region 60a from Vr.

- V FD exceeds the substrate potential Vsub

- a forward bias is applied to the pn junction between the impurity region 60a and the periphery thereof, and an n-type silicon substrate as a support substrate is redundantly connected to the impurity region 60a. Electrons flow in. In other words, dark current occurs.

- the time T3 only a reset signal ⁇ rst a high level, and switches the voltage Vc applied from the voltage supply circuit 128 to the control line 81 to lower than the first voltage V A second voltage V B .

- the potential of the node FDa between the photoelectric conversion unit 50A and the signal detection transistor 72 can be reduced via the capacitive element C1, As shown in FIG. 4B, the potential V FD of the impurity region 60a can be prevented from exceeding the substrate potential Vsub.

- the potential V FD of the impurity region 60a immediately after the reset transistor 76 is turned off is V1b which satisfies the relationship Vsub>V1b> Vr.

- V1b may be about 3.1V.

- the reset transistor 76 After the reset transistor 76 is turned off, the second signal corresponding to the voltage level of the charge storage node after discharging the signal charge is read out to the vertical signal line 89, and the absolute value of the difference ⁇ between the first signal and the second signal is obtained. Obtained as an image signal. After obtaining the second signal, the address transistor 74 is turned off, and accumulation of signal charge of the next frame is started.

- control line 81 is connected between the exposure period for accumulating signal charges in the charge accumulation node and the period for resetting in a non-exposure period other than the exposure period of one frame period.

- the voltages supplied may be different from each other.

- FIG. 4C is a timing chart for explaining another example of the operation of the pixels 10A, 10Ap and 10Aq. Similar to the example shown in FIGS. 4A and 4B, in the operation example shown in FIG. 4C, the exposure period for accumulating the signal charge in the charge storage node and the non-exposure period other than the exposure period are alternately repeated.

- the non-exposure period includes, in part, a reset period for resetting the potential of the charge storage node to a predetermined potential.

- the pixel 10A shown in FIG. 3 is illustrated.

- the address signal selsel is made high.

- ⁇ V FD (V B ⁇ V A ) (C 1 / (C 1 + C FD )) (1)

- the potential of the node FDa at this time is read out to the vertical signal line 89 through the signal detection transistor 72 and the address transistor 74 as a first signal expressing a voltage level corresponding to the signal charge stored in the charge storage node.

- the reset signal rstrst is made high. Thereby, the signal charge is discharged from the charge storage node through the reset transistor 76, and the potential of the charge storage node is reset to the reset voltage Vr.

- the reset signal rstrst is set to low level, and the reset transistor 76 is turned off. From time T3 to time T4 at which the next pulse of horizontal synchronization signal HD rises, the second signal corresponding to the voltage level of the charge storage node after discharge of the signal charge is made vertical via address transistor 74. Read on line 89.

- the difference ⁇ between the first signal read from time T1 to time T2 and the second signal read from time T3 to time T4 represents an image. It becomes a true pixel signal.

- the voltage applied to the control line 81 is returned to the first voltage V A again.

- the potential of the node FDa drops from Vr to V1c due to capacitive coupling via the capacitive element C1.

- the fluctuation amount of the potential of the node FDa at this time (Vr ⁇ V1c) is equal to the above-described ⁇ V FD .

- the fluctuation amount ⁇ V FD is controlled by determining the first voltage V A and the second voltage V B based on the above equation (1). be able to.

- the desired ⁇ V FD can be achieved by the following procedure. First, at the time of product design, the capacitance ratio between the capacitive element C1 and a portion of the charge storage node other than the capacitive element C1 is determined from the total capacitance value of the target charge storage node. Then, the amplitude of the voltage applied to the control line 81 during actual operation, i.e., a specific voltage value of the first voltage V A and the second voltage V B is determined based on equation (1) above.

- either the first voltage VA or the second voltage VB is at ground (0 V). Since the ground side is generally low impedance, it is possible to suppress the mixing of power supply noise from the voltage supply circuit 128 connected to the control line 81 into the charge storage node. For example, when the second voltage V B is grounded, the first voltage V A is a negative level voltage.

- the voltage supply circuit 128, the control line 81, and supplies the first voltage V A to the exposure period for accumulating the signal charges impurity regions 60a to charge storage node includes in its part.

- a second voltage V B different from the first voltage V A is supplied.

- control may be employed to differ between at least the reset period and the other periods after the exposure period. According to such control, for example, the potential of the charge storage node can be temporarily reduced compared to the reset voltage Vr.

- the potential difference between the impurity region 60a and the second p-type semiconductor layer 62p located around it and grounded, for example, can be reduced.

- the depletion layer formed by the pn junction between the impurity region 60a and the second p-type semiconductor layer 62p is reduced, and the reduction of dark current is realized. That is, by setting the potential of the charge storage node to a low potential in the exposure period, an effect of dark current reduction can be expected.

- the potential of the charge storage node is raised by the potential difference amount between the second voltage V B and the first voltage V A. Therefore, by adjusting this potential difference, it is possible to set the source-drain voltage of the signal detection transistor 72 and the transistor of the subsequent stage circuit within the voltage range in which these transistors can operate. Therefore, the signal detection transistor 72 and the rear stage circuit can normally read out the pixel signal or the reference signal.

- FIG. 5 schematically shows an example of another circuit configuration of the pixel 10.

- the pixel 10Ap illustrated in FIG. 5 includes a photoelectric conversion unit 50B instead of the photoelectric conversion unit 50A.

- the photoelectric conversion unit 50B is, for example, a buried photodiode formed in the semiconductor substrate 60.

- the photoelectric conversion unit 50B is connected to the gate of the signal detection transistor 72.

- the node FDb between the photoelectric conversion unit 50B and the signal detection transistor 72 corresponds to a charge storage node.

- the pn junction in the embedded photodiode as the photoelectric conversion unit 50B, the impurity region 60a and the gate electrode 72e function as charge storage nodes for temporarily holding the charge generated by the photoelectric conversion unit 50B.

- Impurity region 60a may be part of a pn junction in the buried photodiode.

- the same operation as the operation described with reference to FIGS. 4A and 4B can be applied to the imaging device 100 having the pixel 10Ap.

- the reset signal ⁇ rst a low level

- to switch the voltage Vc applied to the control line 81 from the voltage supply circuit 128 from the first voltage V A higher than the first voltage V A second voltage V B the potential of the node FDb can be increased through the capacitive element C1.

- the second voltage V B the potential V FD of the impurity regions 60a is avoided that below the substrate potential Vsub, can suppress dark current.

- the reset transistor 76 or the like is a p-type transistor and electrons are stored as signal charges, which is more advantageous because a larger dynamic range can be obtained.

- FIG. 6 schematically shows an example of still another circuit configuration of the pixel 10.

- the pixel 10Aq illustrated in FIG. 6 further includes the transfer transistor 79 connected between the gate of the signal detection transistor 72 and the photoelectric conversion unit 50B.

- the transfer transistor 79 transfers the signal charge obtained by the photoelectric conversion unit 50B to a node FDc between the gate of the signal detection transistor 72 and the transfer transistor 79 at a predetermined timing.

- the transfer transistor 79 is, for example, an n-channel MOS.

- the transfer transistor 79 may share the impurity region 60 a with the reset transistor 76 as one of a source region and a drain region.

- the circuit configuration shown in FIG. 6 similar to the pixel 10Ap shown in FIG. 5, by switching the voltage Vc from the first voltage V A to the second voltage V B, the potential of a floating node node FDc, capacitance

- the potential V FD of the impurity region 60a can be avoided, for example, from rising below the substrate potential Vsub through the element C1.

- Switching of the voltage Vc from the first voltage V A to the second voltage V B is performed, for example, at the timing of turning off the reset transistor 76 after discharging the signal charge transferred to the node FDc by turning on the reset transistor 76. Be done.

- FIG. 7A and 7B schematically show an example of still another circuit configuration of the pixel 10.

- the pixel 10Ar shown in FIG. 7A has a signal detection transistor 72d of a depletion type instead of the signal detection transistor 72.

- a depletion type transistor as the signal detection transistor 72d, a high output can be obtained from the signal detection transistor 72d even when the potential of the node FDa is at a low level. Therefore, it becomes easier to secure the voltage range necessary for the operation of the current source configured of the load circuit and the like connected to the vertical signal line 89.

- the pixel 10As shown in FIG. 7B has a configuration in which the photoelectric conversion unit 50A of the pixel 10Ar shown in FIG. 7A is replaced with a photoelectric conversion unit 50B.

- the photoelectric conversion unit 50B is, for example, a buried photodiode formed in the semiconductor substrate 60. Even in the configuration using a photodiode, a depletion type transistor can be used as the signal detection transistor 72d.

- FIG. 8 is a timing chart for explaining an exemplary operation of the pixel 10Ar shown in FIG. 7A or the pixel 10As shown in FIG. 7B.

- the waveform of the voltage Vc in the non-exposure period is different from the waveform in the operation sequence illustrated in FIG. 4C.

- FIG. 8 wherein, in the non-exposure period, a short period of relatively high second voltage V B voltage Vc to be applied to the control line 81 from the voltage supply circuit 128.

- the voltage Vc is switched from the first voltage V A to the relatively high second voltage V B at the rise timing of the reset signal rstrst at time T 2, and the reset signal rstrst is low at time T 3 After being switched to the level, it is returned to the first voltage V A.

- the reset transistor 76 After the reset transistor 76 is turned off, the voltage Vc applied from the voltage supply circuit 128 to the control line 81 is switched to the first voltage VA , thereby contributing all changes in the voltage Vc to the change in the potential of the charge storage node. It becomes possible.

- the potential of the charge storage node drops from the reset voltage Vr by ⁇ V FD represented by the formula (1).

- the potential of the charge storage node can be lowered to a potential V1d lower than Vr.

- the true pixel signal representing the image of the subject is given by the difference between the first signal corresponding to the potential of the charge storage node at time T1 and the second signal corresponding to the potential of the charge storage node at time T4. .

- the first signal is read out to the vertical signal line 89 between time T1 and time T2, and the second signal is read out to the vertical signal line 89 between time T4 and time T5. That is, in this example, when the first voltage V A is applied to the control line 81, readout of the pixel signal and the reference signal is performed. Similarly, in this example, by using a voltage of 0V as the first voltage V A, it is possible to suppress the contamination of the noise nodes FDa or node FDb in voltage output from the voltage supply circuit 128.

- FIG. 9A and 9B schematically show an example of still another circuit configuration of the pixel 10.

- the pixel 10At shown in FIG. 9A is an example in which p-type transistors are applied as the signal detection transistor 72, the address transistor 74 and the reset transistor 76 in the circuit configuration shown in FIG.

- a pixel 10Au shown in FIG. 9B is an example in which p-type transistors are applied as the signal detection transistor 72, the address transistor 74 and the reset transistor 76 in the circuit configuration shown in FIG.

- electrons are typically used as signal charges.

- a p-type transistor is applied to the reset transistor 76, using electrons as the signal charge secures a sufficient number of saturated electrons in the required dynamic range while avoiding complication of the circuit. Cheap.

- FIG. 10 is a timing chart for explaining an exemplary operation of the pixel 10At shown in FIG. 9A or the pixel 10Au shown in FIG. 9B.

- the address signal ⁇ sel from the high level to the low level, switching the voltage Vc applied to the control line 81 to the relatively low from the first voltage V A second voltage V B .

- the address signal selsel is maintained at the low level in the non-exposure period.

- the potential of the charge storage node is obtained by capacitive coupling via the capacitive element C1. Decreases.

- the variation amount ⁇ V FD of the potential at this time is expressed by the above-mentioned equation (1) by the capacitance ratio between the capacitive element C1 and the portion of the charge storage node other than the capacitive element C1. From time T1 to time T2, a signal corresponding to the voltage V FD at this time is read out to the vertical signal line 89 as a first signal.

- the reset is performed by setting the reset signal rstrst to low level. That is, when the reset signal rstrst is set to low level, the reset transistor 76 is turned on, the signal charge stored in the node FDa or FDb is discharged through the reset transistor 76, and the potential of the charge storage node becomes the voltage Vr. It is reset.

- the reset signal rstrst is set to the high level to turn off the reset transistor 76.

- the second signal corresponding to the reset voltage Vr is read out to the vertical signal line 89 from time T3 to time T4.

- the difference between the first signal read from time T1 to time T2 and the second signal read from time T3 to time T4. are output as true pixel signals.

- the signal detection transistor 72, the address transistor 74, and the reset transistor 76 be p-type transistors.

- the reset transistor 76 is an n-channel MOS, for example, 0 V is used as the substrate potential Vsub.

- the reset transistor 76 is a p-channel MOS, and 0 V is adopted as the substrate potential Vsub.

- voltage V FD is lowered along with accumulation of electrons which are signal charges in the charge storage node, so that the voltage is applied to the pn junction between impurity region 60a and the periphery thereof. It is necessary to reset the potential of the charge storage node to a potential higher than the substrate potential Vsub prior to the accumulation of the signal charge in order to avoid the forward bias of the output voltage.

- the signal charge is an electron

- a voltage of 3.3 V can be used as the reset voltage Vr.

- the potential of the charge storage node drops from, for example, 3.3 V at the start of the exposure, and the potential difference between it and the substrate potential Vsub decreases. Therefore, the depletion layer width is reduced, and the effect of dark current reduction can be expected.