USRE47641E1 - Semiconductor device with super junction region - Google Patents

Semiconductor device with super junction region Download PDFInfo

- Publication number

- USRE47641E1 USRE47641E1 US15/249,157 US201615249157A USRE47641E US RE47641 E1 USRE47641 E1 US RE47641E1 US 201615249157 A US201615249157 A US 201615249157A US RE47641 E USRE47641 E US RE47641E

- Authority

- US

- United States

- Prior art keywords

- conductivity type

- semiconductor layer

- type semiconductor

- region portion

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime, expires

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 369

- 230000015556 catabolic process Effects 0.000 claims abstract description 53

- 230000005684 electric field Effects 0.000 claims abstract description 10

- 239000012535 impurity Substances 0.000 claims description 76

- 238000005520 cutting process Methods 0.000 description 27

- 238000000034 method Methods 0.000 description 24

- 230000012010 growth Effects 0.000 description 17

- 239000013078 crystal Substances 0.000 description 15

- 238000002347 injection Methods 0.000 description 13

- 239000007924 injection Substances 0.000 description 13

- 150000002500 ions Chemical class 0.000 description 13

- 239000011295 pitch Substances 0.000 description 12

- 230000008569 process Effects 0.000 description 12

- 230000007423 decrease Effects 0.000 description 10

- 238000004519 manufacturing process Methods 0.000 description 10

- 238000009792 diffusion process Methods 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 4

- 230000002238 attenuated effect Effects 0.000 description 3

- 239000002019 doping agent Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- 230000008901 benefit Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000012141 concentrate Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000007480 spreading Effects 0.000 description 2

- 238000003892 spreading Methods 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000003466 anti-cipated effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- -1 for example Substances 0.000 description 1

- 239000007792 gaseous phase Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/063—Reduced surface field [RESURF] pn-junction structures

- H01L29/0634—Multiple reduced surface field (multi-RESURF) structures, e.g. double RESURF, charge compensation, cool, superjunction (SJ), 3D-RESURF, composite buffer (CB) structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41741—Source or drain electrodes for field effect devices for vertical or pseudo-vertical devices

Definitions

- the present invention relates to a semiconductor device and a method of manufacturing a semiconductor device, and in particular, to a structure of a junction terminating region portion of a power semiconductor device which is suitable for a switching element for electric power.

- the MOSFET is a majority carrier device

- the MOSFET has an advantage that there is no minority carrier storage time and switching is fast.

- a device which has a high breakdown voltage is disadvantageous with respect to the ON-state resistance as compared with a bipolar device such as an IGBT (Insulated Gate Bipolar Transistor) or the like. This results from the fact that the higher the breakdown voltage a device has, the more the ON-state resistance of the MOSTFET increases, because it is necessary to make an n type base layer thicker and to make the impurity concentration lower in order to obtain a higher breakdown voltage in the MOSFET.

- the ON-state resistance of the power MOSFET greatly depends on the electrical resistance in a conductive layer (n type drift layer) portion. Further, the impurity concentration determining the electrical resistance at the n type drift layer cannot rise to greater than or equal to the limit, in accordance with the breakdown voltage of the pn junction which the p type base and the n type drift layer form. Therefore, a trade-off relationship exists between the device breakdown voltage and the ON-state resistance. It is important to improve this trade-off for a low electric power consumption device. In this trade-off, there is a limit which is determined by the material of the device, and this limit must be exceeded in order to realize a low ON-state resistance device exceeding existing power devices.

- a structure is known in which a resurf structure called a super junction structure is buried in an n type drift layer.

- a conventional power MOSFET having a super junction structure will be described with reference to FIG. 36 . Note that, in the following figures, like parts are denoted by like reference numerals, and detailed descriptions thereof will be omitted.

- FIG. 36 is a cross-sectional view showing a schematic structure of one example of a conventional power MOSFET.

- an n+ type drain layer 100 is formed on one surface of an n ⁇ type drift layer 102

- a drain electrode 40 is formed on the n+ type drain layer 100 .

- a plurality of p type base layers 108 are selectively formed in the other surface portion of the n ⁇ type drift layer 102

- n+ type source layers 110 are selectively formed in the surfaces of the respective p type base layers 108 .

- a gate electrode 114 is formed on the surface region of the n ⁇ type drift layer 102 which are sandwiched by the adjacent p type base layers 108 , the surfaces of the p type base layers 108 sandwiching the n ⁇ type drift layer 102 , and the surface region of the portions of the n+ type source layer 110 facing each other via the p type base layers 108 and the n ⁇ type drift layer 102 , with a gate insulating film 112 interposed therebetween.

- source electrodes 116 are respectively formed on the region of the surfaces of the n+ type source layer 110 and the surface of the p type base layer 108 so as to sandwich the gate electrode 114 .

- a p type drift layer 106 which is formed so as to form a resurf layer and is connected to the p type base layer 108 , is formed.

- the power MOSFET shown in FIG. 36 has a vertical type resurf structure in which the p type drift layers 106 and the portions of the n ⁇ type drift layers 102 sandwiched by these p type drift layers 106 are alternately repeated in the lateral direction.

- a depletion layer spreads at junctions between these p type drift layers 106 and n ⁇ type drift layers 102 . Even if the impurity concentration of the n ⁇ type drift layers 102 is made high, the n ⁇ type drift layers 102 and the p type drift layers 106 are completely depleted before breaking down. In accordance therewith, a breakdown voltage which is the same as that of the conventional MOSFET can be obtained.

- the impurity concentration of the n ⁇ type drift layer 102 does not depend on a breakdown voltage of the device, but it depends on the width of the p type drift layer 106 and the width of the n ⁇ type drift layer 102 itself between these p type drift layers 106 . If the width of the n ⁇ type drift layer 102 and the width of the p type drift layer 106 are made narrower, the impurity concentration of the n ⁇ type drift layer 102 can be made much higher, and a greater reduction of the ON-state resistance and a higher breakdown voltage can be achieved.

- the impurity concentrations of the n ⁇ type drift layer 102 and the p type drift layer 106 are important to determine the breakdown voltage and the ON-state resistance.

- the breakdown voltage at the terminating portion decreases, and an electric field locally concentrates at this place. As a result, there are cases in which the device is broken. In this way, there is the problem that a sufficiently high breakdown voltage cannot be obtained by the entire device in the prior art.

- the process margin for the breakdown voltage is determined by the difference in the impurity amounts between the n ⁇ type drift layer 102 and the p type drift layer 106 .

- the process margin becomes small.

- a semiconductor device comprising:

- a first—first conductivity type semiconductor layer which includes a cell region portion and a junction terminating region portion, the junction terminating region portion being a region portion which is positioned in an outer periphery of the cell region portion to maintain a breakdown voltage by extending a depletion layer to attenuate an electric field;

- first-second conductivity type semiconductor layers which are formed in the cell region portion of the first—first conductivity type semiconductor layer in substantially vertical directions to the one surface of the first—first conductivity type semiconductor layer, respectively, and which are periodically disposed in a first direction which is an arbitrary direction parallel to the one surface;

- a second—second conductivity type semiconductor layer which is selectively formed in the other surface portion of the first—first conductivity type semiconductor layer so as to contact the first-second conductivity type semiconductor layers;

- a second main electrode which is formed so as to contact the second—second conductivity type semiconductor layer and the third-first conductivity type semiconductor layer;

- control electrode which is formed on the surface of the first—first conductivity type semiconductor layer sandwiched by the adjacent second—second conductivity type semiconductor layers, the surface of the adjacent second—second conductivity type semiconductor layers and the surface of the third-first conductivity type semiconductor layer, with a gate insulating film interposed therebetween;

- third-second conductivity type semiconductor layers which are formed in the junction terminating region portion and are periodically disposed in at least one direction of the first direction and a second direction perpendicular to the first direction.

- first conductivity type semiconductor layer epitaxially growing the first conductivity type semiconductor layer on the first conductivity type semiconductor layer and the second conductivity type semiconductor layer such that the thickness of the first conductivity type semiconductor layer increases by a length which is substantially the same as a depth of the trench groove formed by the first process;

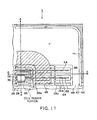

- FIG. 1 is a plan view showing a schematic structure of a first embodiment of a semiconductor device according to the present invention.

- FIG. 2 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 1 .

- FIG. 3 is a cross-sectional view taken along the cutting line B—B of the semiconductor device shown in FIG. 1 .

- FIG. 4 is a plan view showing a schematic structure of a second embodiment of a semiconductor device according to the present invention.

- FIG. 5 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 4 .

- FIG. 7 is a plan view showing a schematic structure of a third embodiment of a semiconductor device according to the present invention.

- FIG. 8 is a plan view showing a schematic structure of a fourth embodiment of a semiconductor device according to the present invention.

- FIG. 9 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 8 .

- FIG. 10 is a cross-sectional view showing a modified example of the semiconductor device shown in FIG. 8 .

- FIG. 11 is a plan view showing a schematic structure of a fifth embodiment of a semiconductor device according to the present invention.

- FIG. 12 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 11 .

- FIG. 13 is a plan view showing a schematic structure of a sixth embodiment of a semiconductor device according to the present invention.

- FIG. 14 is cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 12 .

- FIG. 15 is cross-sectional view taken along the cutting line B—B of the semiconductor device shown in FIG. 12 .

- FIG. 16 is a plan view showing a modified example of the present embodiment shown in FIG. 12 .

- FIG. 17 is a plan view showing a schematic structure of a seventh embodiment of a semiconductor device according to the present invention.

- FIG. 18 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 17 .

- FIG. 19 is a plan view showing a schematic structure of an eighth embodiment of a semiconductor device according to the present invention.

- FIG. 20 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 19 .

- FIG. 21 is a cross-sectional view taken along the cutting line B—B of the semiconductor device shown in FIG. 19 .

- FIG. 22 is a plan view showing a schematic structure of a ninth embodiment of a semiconductor device according to the present invention.

- FIG. 23 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 22 .

- FIG. 24 is a plan view showing a schematic structure of a tenth embodiment of a semiconductor device according to the present invention.

- FIG. 25 is a cross-sectional view taken along the cutting line A—A of the semiconductor device shown in FIG. 24 .

- FIG. 26 is across-sectional view taken along the cutting line B—B of the semiconductor device shown in FIG. 24 .

- FIG. 27 is a cross-sectional view showing a schematic structure of an eleventh embodiment of a semiconductor device according to the present invention.

- FIG. 28 is a graph showing relationships between a p type dopant amount and a breakdown voltage with respect to a cell region portion and a junction terminating region portion, respectively.

- FIG. 29 is a cross-sectional view showing a schematic structure of a twelfth embodiment of a semiconductor device according to the present invention.

- FIG. 30 is a graph showing changes in the breakdown voltage with respect to the impurity balance of a p type resurf layer and an n ⁇ type drift layer.

- FIG. 31 is a cross-sectional view showing a schematic structure of a thirteenth embodiment of a semiconductor device according to the present invention.

- FIG. 32 is a cross-sectional view showing a schematic structure of a fourteenth embodiment of a semiconductor device according to the present invention.

- FIG. 33 is a cross-sectional view showing a schematic structure of a fifteenth embodiment of a semiconductor device according to the present invention.

- FIG. 34 is a cross-sectional view showing a schematic structure of a sixteenth embodiment of a semiconductor device according to the present invention.

- FIGS. 35A through 35F are schematic cross-sectional views showing one embodiment of a method of manufacturing the semiconductor device according to the present invention.

- FIG. 36 is a cross-sectional view showing a schematic structure of a power MOSFET having a super junction structure in accordance with a prior art.

- the semiconductor device according to the present invention is not limited to a power MOSFET, and can be applied to an SBD or MPS diode having a super junction structure, a switching element such as an SIT, a JFET, an IGBT, or the like, and a complex element or an integrated element of the diodes and the switching elements.

- FIG. 1 is a plan view showing a schematic structure of a first embodiment of the semiconductor device according to the present invention.

- FIG. 2 and FIG. 3 are cross-sectional views of the semiconductor device of the present embodiment along taken along the cutting lines A—A and B—B of FIG. 1 , respectively.

- the semiconductor device 1 of the present embodiment is characterized in that n ⁇ type drift layers 26 and p-type drift layers 28 are formed not only in a cell region portion, but are formed also up to the vicinity of the periphery of a junction terminating region portion.

- the structure of the semiconductor device 1 of the present embodiment will be described in even more detail.

- the semiconductor device 1 of the present embodiment has an n+ type drain layer 20 , a drain electrode 40 , the n type drift layers 26 , the p type drift layers 28 , p type base layers 30 , an n+ type source layer 32 , a source electrode 38 , an insulated gate electrode 36 , and a fieldplate electrode 48 .

- the drain electrode 40 is formed on one surface of the n+ type drain layer 20 , and is formed on the bottom surface in FIG. 2 and FIG. 3 .

- the p type drift layers 28 are respectively structured in the n type semiconductor layers 26 so as to be in a striped shape from the boundary surface with the n+ type drain layer 20 up to the surface portion of the n type semiconductor layers 26 which represent the other surface portion, i.e., the top surface portion in FIG. 2 and FIG. 3 , of the n+ type drain layer 20 .

- the respective stripe-shaped p type drift layers 28 are arranged not only in the cell region portion, but also up to the junction terminating region portion at predetermined intervals in a predetermined direction which is horizontal to the surface of the n+ type drain layer 20 .

- Regions sandwiched between these p type drift layers 28 in the n type semiconductor layers 26 structure the n type drift layers 26 .

- the impurity concentration of both of the n type semiconductor layers 26 and the p type drift layers 28 for example, when each of their widths is 5 ⁇ m, the impurity concentration is about 4 ⁇ 10 15 cm ⁇ 3 , respectively, and when each of the widths is 1 ⁇ m, the impurity concentration is about 2 ⁇ 10 16 cm ⁇ 3 , respectively.

- the p type base layers 30 are selectively formed in the surface portion in the n type semiconductor layers 26 so as to connect to the p type drift layers 28 .

- the n+ type source layers 32 are selectively formed in the surface portion of the p type base layers 30 .

- the source electrodes 38 are formed so as to connect the adjacent n+ type source layer 32 on the surface of the p type base layer 30 and the p type base layer 30 sandwiched thereby.

- the insulated gate electrode 36 is disposed via an insulating film 34 above the surface of the n type drift layer 26 , the surface of the p type base layer 30 adjacent to the surface of the n type drift layer 26 , and the surface of the n+ source layer 32 contacting the p type base layer 30 , so as to be surrounded by the source electrodes 38 .

- the semiconductor device 1 constitutes an n channel MOSFET for electron injection in which the surface portion of the p type base layer 30 immediately under the insulated gate 36 is a channel region.

- a planer type gate structure is provided will be described.

- a trench type gate structure may be used. This point is the same for the following respective embodiments as well.

- the semiconductor device 1 also comprises a p type base layer 30 a which is formed so as to surround the cell region portion in the surface portion at the vicinity of the boundary with the cell region portion in the junction terminating region portion.

- the p type base layer 30 a is discretely connected to the p type drift layer 28 a which is closest to the cell region portion among the p type drift layers 28 a provided in the junction terminating region portion.

- an insulating film 46 is formed on the part other than a part of the p type base layer 30 a.

- a fieldplate electrode 48 is formed on the insulating film 46 so as to surround the cell region, and contacts the surface of the p type base layer 30 a, and is electrically connected to the source electrodes 38 .

- a high-concentration n+ type channel stopper layer 42 is formed on the surface portion of the n type drift layer 26 , and the electrode 44 is formed on the n+ channel stopper layer 42 .

- the broken lines in FIG. 2 and FIG. 3 denote equipotential lines, which are the result of a simulation in which calculation is carried out by using the conditions that the widths of the n type drift layer 26 and the p type drift layer 28 are 8 ⁇ m, the impurity concentrations thereof are 2 ⁇ 10 15 cm ⁇ 3 , and the thickness thereof are 50 ⁇ m.

- the depletion progresses from a side close to the cell region portion of the n type drift layer 26 a and the p type drift layer 28 a toward the periphery of the device, and in the horizontal direction, the depletion progresses over the boundary surface at the same time from the device peripheral portions of the drift layers 26 a and 28 a to the cell region portion.

- the structure of the n type drain layer 20 is not limited to the form shown in FIG. 1 through FIG. 3 , and for example, an epitaxial wafer substrate, a layer in which a predetermined depth of the epitaxial wafer substrate is subjected to thermal diffusion, a diffusion layer in which an impurity is subjected to thermal diffusion, or the like can be applied.

- the present embodiment is the two-layer structure of the n type drain layer 20 and the n type semiconductor layer 26 .

- an intermediate layer whose concentration continuously changes may be set between these two layers.

- the fieldplate electrode 48 is formed on the insulating film 46 having a uniform thickness.

- the present invention is not limited thereto, and for example, as in eleventh through sixteenth embodiments which will be described later, it may be set such that the thickness of the insulating film 46 is made to gradually become greater as the insulating film 46 approaches the peripheral portion.

- FIG. 4 is a plan view showing a schematic structure of a second embodiment of a semiconductor device according to the present invention.

- FIG. 5 and FIG. 6 are cross-sectional views of the semiconductor device of the present embodiment taken along the cutting lines A—A and B—B of FIG. 4 , respectively.

- the semiconductor device 2 of the present embodiment has, in place of the fieldplate electrode 48 which the semiconductor 1 shown in FIG. 1 has, a p ⁇ type resurf layer 52 which is connected to the p type base layer 30 a disposed so as to surround the cell region in the junction terminating region portion, and which is formed so as to further surround the p type base layer 30 a.

- the other structures of the semiconductor device 2 are substantially the same as those of the semiconductor device 1 shown in FIG. 1 .

- FIG. 7 is a plan view showing a schematic structure of a third embodiment of a semiconductor device according to the present invention. Note that a cross-sectional view taken along the cutting line A—A in the view is substantially the same as FIG. 2 .

- the semiconductor device 3 of the present embodiment is characterized in that p type drift layers 54 , 54 a have a circular plane shape, which is different from the above-described embodiments. Due to the p type drift layers being structured in such a shape, the depletion layers can be extended in all directions in a plane which is horizontal to the surface of the device.

- FIG. 7 although an example of circular patterns is shown, there may be polygonal patterns such as quadrangular patterns, hexagonal patterns, or the like. Further, it may be formed such that the n type drift layers 26 have a pattern. Further, in the same way as in the above-described second embodiment, a resurf layer can be applied in place of the fieldplate electrode 48 .

- FIG. 8 is a plan view showing a schematic structure of a fourth embodiment of a semiconductor device according to the present invention.

- FIG. 9 is a cross-sectional view of the semiconductor device of the present embodiment taken along the cutting line A—A of FIG. 8 .

- a semiconductor device 4 of the present embodiment has an n ⁇ type base layer 68 as the n type base layer in the junction terminating region portion, the concentration of the n ⁇ type base layer 68 being lower than that of the n type drift layer 26 in the cell region portion. Moreover, the semiconductor device 4 does not have drift layers in the junction terminating region portion other than a p type drift layer 27 which will be described later.

- the p type base layer 30 a and a plurality of p type guard ring layers 62 are selectively formed so as to surround the cell region portion in the surface portion of the n ⁇ type base layer 68 .

- the p type drift layer 27 is formed so as to correspond to the arrangement of the p type base layer 30 a, and thus, the p type base layer 30 a is connected to the drain electrode 40 via the drain layer 20 .

- a stable high breakdown voltage can be obtained by a single super junction structure surrounding the cell region portion and the p type guard ring layers 62 formed so as to surround the cell region portion in the same way in the surface portion of the periphery of the super junction structure.

- FIG. 10 A cross-sectional view of a modified example of the present embodiment is shown in FIG. 10 .

- a semiconductor device 4 ′ shown in the view has, in the junction terminating region portion, n type base layers 22 whose concentration is the same as that of the n type drift layer 26 in the cell region portion, and p type drift layers 29 are provided in the junction terminating region portion and are connected to p type guard ring layers 62 ′ which are selectively provided on the surface portion of the n type base layers 22 .

- a p type drift layer 29 ′ is formed so as to be exposed on the surface of the n type base layers 22 .

- FIG. 11 is a plan view showing a schematic structure of a fifth embodiment of a semiconductor device according to the present invention.

- FIG. 12 is a cross-sectional view of the semiconductor device of the present embodiment taken along the cutting line A—A of FIG. 11 . Note that the cross-sectional view taken along the cutting line B—B of FIG. 11 is the same as the FIG. 3 .

- the present embodiment provides a junction terminating regional structure which is suitable for a semiconductor device having an insulating film formed parallel to the horizontal direction in the n type drift layer 26 in the cell region portion.

- a trench groove 64 is formed in a horizontal direction in the n type drift layer 26 ( 26 a), and an insulating film 66 is formed therein.

- Such an insulating film can be manufactured by forming the stripe shaped trench grooves 64 so as to extend from the cell region portion to the junction terminating region portion on the substrate structured from, for example, a low-concentration n ⁇ type base layer 68 , and by applying thermal diffusion after an n type impurity and a p type impurity are introduced into the side walls of the trench grooves 64 by using a method such as an ion injection or the like.

- the n type drift layer 26 ( 26 a) and the p type drift layer 28 ( 28 a) are formed so as to surround the insulating film 66 . Accordingly, in the junction terminating region portion, the insulating film 66 and the both drift layers 26 a, 28 a extend in the horizontal direction up to the vicinity of the peripheral portion. However, the insulating film 66 and the drift layers are not formed in the vertical direction.

- the semiconductor device 5 of the present embodiment further comprises the field plate electrode 48 provided above the low-concentration n ⁇ type base layer 68 in the junction terminating region via the insulating film 46 so as to surround the cell region. Therefore, the depletion layer sufficiently extends, and a high breakdown voltage can be obtained.

- FIG. 13 is a plan view showing a schematic structure of a sixth embodiment of a semiconductor device of the present invention.

- FIG. 14 and FIG. 15 are cross-sectional views of the semiconductor device of the present embodiment taken along the cutting lines A—A, B—B of FIG. 13 .

- the insulating film 66 is formed only in the cell region portion, and does not extend to the junction terminating region portion. Moreover, in the junction terminating region portion of the semiconductor device 6 , both the n type drift layers and the p type drift layers are not formed.

- the n ⁇ type base layer 68 whose concentration is lower than that of the n type drift layer 26 is formed in the junction terminating region portion, and the p type base layer 30 a and a plurality of p type guard ring layers 62 are selectively formed so as to surround the cell region on the surface portion of the n ⁇ type base layer 68 .

- the source electrode 38 a contacts the surface of the p type base layer 30 a. Further, below the p type base layer 30 a, the p type drift layer 27 is formed so as to correspond to the arrangement of the p type base layer 30 a, and thereby the p type base layer 30 a is connected to the drain electrode 40 via the drain layer 20 . In accordance with such a structure of the junction terminating region portion, the semiconductor device 6 of the present embodiment can obtain a sufficiently high breakdown voltage.

- FIG. 16 is a plan view showing a modified example of the present embodiment.

- an insulating film 72 is formed also in a vertical direction only in the cell region portion, and then the insulating film 72 has a reticulated plan shape.

- Other structures of the semiconductor device 6 ′ are substantially the same as those of the semiconductor device 6 shown in FIG. 13 . Even when the insulating film 72 has such a structure in the cell region portion, the semiconductor device 6 ′ can obtain a sufficiently high breakdown voltage because the insulating film 72 does not extend to the junction terminating region portion and the p type guard ring layers 62 are formed in the junction terminating region portion.

- FIG. 17 is a plan view showing a schematic structure of a seventh embodiment of a semiconductor device according to the present invention.

- FIG. 18 is a cross-sectional view of the semiconductor device of the present embodiment taken along the cutting line A—A of FIG. 17 . Note that the cross-sectional view taken along the cutting line B—B of FIG. 17 is the same as FIG. 3 .

- a semiconductor device 7 of the present embodiment further comprises insulating films 76 formed in the vertical direction in the junction terminating region portion, and n type drift layers 166 and p type drift layers 168 which are respectively formed in the vertical direction in the junction terminating region portion and which are periodically disposed in the horizontal direction.

- the depletion layers sufficiently extend at the time of turning-off because the positive holes in the p type drift layers 168 are discharged in the vertical direction in the same way as in the horizontal direction, and a high breakdown voltage can thus be obtained.

- FIG. 19 is a plan view showing a schematic structure of an eighth embodiment of a semiconductor device according to the present invention.

- FIG. 20 and FIG. 21 are cross-sectional views of the semiconductor device of the present embodiment taken along the cutting lines A—A and B—B of FIG. 19 , respectively.

- the insulating films 76 and the drift layers 26 a, 28 a which are formed so as to extend from the cell region portion toward the junction terminating region portion, are periodically disposed in the vertical direction as well, and are formed up to the vicinity of the periphery of the junction terminating region portion. Further, on the surface portion of the junction terminating region portion, a p ⁇ type resurf layer 52 having a predetermined width is provided so as to surround the cell region. Moreover, electrodes 78 for voltage fixing are provided above or on the respective p type drift layers 28 a 4 through 28 a 7 periodically disposed in the vertical direction in the junction terminating region portion (see FIG. 20 ).

- Electrodes 78 are extendedly formed so as to bend in circular arcs having a center in common with the corner portion of a source electrode 38 a with a constant interval between one another, and so as to intersect the p type drift layers 28 al through 28 a 3 .

- the electrodes 78 are connected to these p type drift layers 28 a 1 through 28 a 3 at the extended portions (see FIG. 21 ).

- FIG. 22 is a plan view showing a schematic structure of a ninth embodiment of a semiconductor device according to the present invention.

- FIG. 23 is a cross-sectional view of the semiconductor device of the present embodiment taken along the cutting line A—A of FIG. 22 . Note that the cross-sectional view taken along the cutting line B—B of FIG. 22 is the same as FIG. 3 .

- insulating films 84 which are formed in stripe shapes in the respective horizontal directions in the junction terminating region portion and which are periodically disposed in the vertical direction, and n type drift layers 172 which are formed so as to surround the insulating films 84 , are respectively divided in the horizontal direction, and are formed so as to be lattice-shaped in a plan view.

- portions of the p type drift layers 178 in the horizontal directions are connected to one another in the vertical directions.

- positive holes are discharged at the time of turning-off.

- the semiconductor device 9 of the present embodiment comprises a fieldplate electrode 48 which is formed so as to connect to the p type base layer 30 a formed so as to surround the cell region and which is formed so as to extend onto the insulating film 46 formed on the junction terminating region portion.

- a fieldplate electrode 48 which is formed so as to connect to the p type base layer 30 a formed so as to surround the cell region and which is formed so as to extend onto the insulating film 46 formed on the junction terminating region portion.

- FIG. 24 is a plan view showing a schematic structure of a tenth embodiment of a semiconductor device according to the present invention.

- FIG. 25 and FIG. 26 are cross-sectional views of the semiconductor device of the present embodiment taken along the cutting lines A—A and B—B of FIG. 24 , respectively.

- a semiconductor device 10 of the present embodiment comprises Resistive Field Plates RFPs (which are hereinafter called as RFPs) 50 which are made from semi-insulated polysilicon or the like and are formed in the junction terminating region portion so as to surround the cell region, in place of the p ⁇ type resurf layer 52 and the electrode 78 of the semiconductor device 8 shown in FIG. 19 .

- the RFPs 50 are, directly or via the p type base layer 30 in the vicinity of the boundary with the cell region, connected to the source electrode 38 a, and are connected to the p type drift layers 28 a.

- the p type drift layers 28 a 1 and 28 a 2 which correspond to the portion at which the p type drift layers 28 in the cell region portion are extended in the horizontal direction, contact the RFPs 50 over substantially the entire length thereof (see FIG. 26 ).

- the p type drift layers 28 a 4 through 28 a 7 which are periodically formed in the vertical direction in the junction terminating region portion, discretely contact the RFPs 50 over a width corresponding to the width of the cell region portion in the horizontal direction (see FIG. 25 ).

- FIG. 27 is a cross-sectional view showing a schematic structure of an eleventh embodiment of a semiconductor device according to the present invention.

- a vertical type power MOSFET 11 shown in FIG. 27 comprises a semiconductor layer 102 forming a n ⁇ base layer, an n+ drain layer 100 , a drain electrode 40 , a plurality of p type resurf layers 106 , 130 forming the super junction structure, p type base layers 108 , n+ type source layers 110 , gate electrodes 114 , and source electrodes 116 .

- the n+ type drain layer 100 is formed on one surface of the n ⁇ type base layer 102 , i.e., on the bottom surface in FIG. 27 , and the drain electrode 40 is formed on the n+ drain layer 100 .

- the p type resurf layers 106 , 130 are periodically disposed in a predetermined direction not only in the cell region portion but also in the junction terminating region portion, on the other surface portion of the n ⁇ type base layer 102 , i.e., the top surface portion in FIG. 27 . Thereby, a super junction structure is formed, and the p type resurf layer 106 functions as the p type drift layer 106 . Further, region portions sandwiched by these p type drift layers 106 of the n ⁇ type base layers 102 function as the n ⁇ type drift layer 102 .

- the p type base layer 108 is selectively formed so as to connect to the p type drift layer 106 at the surface portion of the n ⁇ type base layer 102 in the cell region portion.

- the n+ type source layer 110 is selectively diffusion-formed so as to have a striped plane shape in the surface portion of the p type base layer 108 .

- the p type base layer 108 is formed such that, for example, when its impurity concentration is about 3 ⁇ 10 17 cm ⁇ 3 , the depth is about 2.0 ⁇ m, and the n+ type source layer 110 is formed such that, for example, when its impurity concentration is about 1 ⁇ 10 20 cm ⁇ 3 , the depth is about 0.2 ⁇ m.

- the gate electrode 114 is formed via a gate insulating film 112 e.g. an Si oxide film 112 whose film thickness is 0.1 ⁇ m on the surface region from the surface of the n+ type source layer 110 and the surface of the p type base layer 108 up to the surface of the adjacent p type base layer 108 and the surface of the n+ type source layer 110 via the surface of the n ⁇ type drift layer 102 .

- the gate electrode 114 is formed so as to be a striped plane shape.

- the source electrode 116 is formed so as to be a striped plane shape on the surface region of the n+ type source layer 110 in the surface portion of the p type base layer 108 , the surface region of the p type base layer 108 , and the surface region of the adjacent n+ type source layer 110 .

- the source electrodes 116 are disposed so as to sandwich the gate electrode 114 .

- a conductive film 117 such as metal, polysilicon, or the like is formed via the insulating film 126 .

- a field plate structure is constituted in the junction terminating region portion.

- a field stopper 42 is provided on the surface portion of the periphery of the device, which is formed from an n layer and stops depletion.

- the super junction structure portion in the junction terminating region portion is rapidly depleted by the field plate 128 at the time of applying high voltage, and the junction terminating region portion then equivalently becomes a low impurity concentration layer. Therefore, the concentration of an electric field in the junction terminating region portion is suppressed, and a high breakdown voltage is maintained. Note that even if a resurf layer is formed on the surface portion in the junction terminating region portion, the super junction structure portion is rapidly depleted in the same way as the field plate. Therefore, the same effects can be obtained.

- the field plate 117 has a structure having an electric potential which is the same as the source electrode 116 . However, it is not limited to this structure, and the field plate 117 may be manufactured so as to have the same electric potential as the gate electrode 114 .

- the impurity amount of the p type drift layer 130 in the junction terminating region portion is greater than the impurity amount of the p type drift layer 106 in the cell region portion, decrease of breakdown voltage in the junction terminating region portion can be suppressed.

- the impurity amount of the p type drift layers 106 , 130 is a product of the width and the impurity concentration, respectively.

- the p type drift layer 130 in the junction terminating region portion is formed so as to have a width which is wider than that of the p type drift layer 106 in the cell region portion, the p type drift layer 130 is formed so as to have an impurity concentration which is the same as that of p type drift layer 106 .

- the impurity amount of the p type dopant in the junction terminating region portion increases, and as a result, decrease of breakdown voltage in the junction terminating region portion can be suppressed.

- the present invention is not limited to this structure.

- the width of the p type drift layer 106 in the cell region portion and the width of the p type drift layer 130 in the junction terminating region portion are made to be the same, and only the impurity concentration in the junction terminating region portion is made to be higher, the same effects can be obtained.

- FIG. 28 is a graph showing changes in breakdown voltage when the amount of the p type impurity is changed, with respect to the cell region portion and the junction terminating region portion, respectively.

- the abscissa of the graph is the ratio of the impurity amount Np of the p type drift layer with respect to the impurity amount Nn of the n ⁇ type drift layer.

- the highest breakdown voltage can be obtained when the impurity amount of the n ⁇ type drift layer and the impurity amount of the p type drift layer are equal (the unbalance is 0%), and if the impurity amount of the p type drift layer is relatively higher or lower, the breakdown voltage symmetrically decreases around the point of 0% in accordance with the proportion.

- the highest breakdown voltage can be obtained when the impurity amount of the p type drift layer is relatively 10% higher.

- the optimum impurity amounts of the p type drift layer in the cell region portion and in the junction terminating region portion are different from one another.

- the breakdown voltage in the junction terminating region portion decreases.

- the optimum impurity amount in the junction terminating region portion is higher than that in the cell region portion.

- the impurity amount of the p type drift layer in the cell region portion is optimally set to 80 to 120% of that of the n ⁇ type drift layer, including the process margin.

- the impurity amount of the p type drift layer in the junction terminating region portion is optimally set to 90 to 130% of that of the n ⁇ type drift layer, including the process margin. Therefore, the impurity amount of the p type drift layer at the terminating portion is preferably set to 75 to 163% of the impurity amount of the p type drift layer in the cell region portion.

- the impurity amount of the p type drift layer, at which the highest breakdown voltage can be obtained, is higher at the terminating portion. Therefore, the impurity amount of the p type drift layer at the terminating portion is more preferably set to 100 to 163% of the impurity amount in the cell region portion.

- the method for forming the super junction structure may be any of, for example, a method in which an ion injection and buried crystal growth are repeated, a method in which a trench groove is formed and buried epitaxy is carried out, and a method in which an ion injection is carried out from an oblique direction after a trench groove is formed.

- ion injection may be carried out individually in the cell region portion and in the junction terminating region portion, or an ion injection may be carried out at the same time in the cell region portion and the junction terminating region portion, with the mask opening width for ion injection being changed.

- the trench groove width or the mesa width may be varied in the cell region portion and the junction terminating region portion.

- the impurity amount of the p type drift layer is made to be the same in the cell region portion and in the junction terminating region portion, and the impurity amount of the n ⁇ type drift layer in the junction terminating region portion is made to be lower than that in the cell region portion, the same effects can be obtained.

- the semiconductor device 12 of the present embodiment is characterized in that the super junction structure is structured by p type drift layers whose cell pitches are different from one another in the cell region portion and the junction terminating region portion. Specifically, a cell pitch of a p type drift layer 132 in the junction terminating region portion is made to be narrower than that of the p type drift layer 106 in the cell region portion. Due to the cell width in the junction terminating region portion being made narrow, depletion in the junction terminating region portion then rapidly proceeds at the time of turning-off. As a result, a lowering of the breakdown voltage in the junction terminating region portion is suppressed.

- FIG. 30 is a graph showing changes in breakdown voltage with respect to the impurity balance between the p type drift layer and the n ⁇ type drift layer.

- the impurity concentration of the n ⁇ type drift layer is set to 2.5 ⁇ 10 15 cm ⁇ 3 . Comparing a case in which the cell pitch is 16 ⁇ m and a case in which the cell pitch is 8 ⁇ m, the decrease in the breakdown voltage is smaller with respect to the balance of the impurity in the case of 8 ⁇ m in which the cell pitch is narrower than 16 ⁇ m. Thereby, it can be understood that the margin with respect to the impurity concentration balance can be made larger by making the cell pitch narrower.

- the impurity amount of the p type drift layer at which the highest breakdown voltage is obtained is greater than the impurity amount of the n ⁇ type drift layer.

- the impurity amount of the p type drift layer in the junction terminating region portion is greater than that in the cell region portion.

- FIG. 31 is a cross-sectional view showing a schematic structure of a thirteenth embodiment of a semiconductor device according to the present invention.

- the semiconductor device 13 of the present embodiment is characterized in the shape of a p type drift layer 134 in the junction terminating region portion.

- the p type drift layer 134 is buried so as not to have a pillar-shaped cross-sectional shape as in the respective embodiments described above but so as to have a circular cross sectional shape. If the p type drift layer 134 structuring the super junction structure have such a circular cross sectional shape in the cell region portion, once it is depleted by turning-off in the p type drift layer, the depletion is maintained.

- the p type drift layers 134 in the junction terminating region portion does not affect the on operation of the semiconductor device 13 because the p type drift layers 134 in circular cross sectional shapes are formed only in the junction terminating region portion.

- the p type drift layer 134 of the present embodiment has a structure which can be obtained when diffusion after burying and growing is used in order to solve such a problem. Specifically, in accordance with diffusion after burying and growing, the concentration of the buried p layer is higher in the cell region portion and is lower in the junction terminating region portion. As a result, the upper and lower p layers are connected in the cell region portion, and the p type drift layer is formed in a pillar-shaped cross sectional shape.

- the respective buried layers are not connected, and have circular cross sectional shapes.

- the cell pitch in the junction terminating region portion is preferably set to a value greater than or equal to half of the cell pitch in the cell region portion.

- FIG. 32 is a cross-sectional view showing a schematic structure of a fourteenth embodiment of a semiconductor device according to the present invention.

- a semiconductor device 14 of the present embodiment is formed such that the cell width of the super junction structure in the junction terminating region portion is narrower than the cell width in the cell region portion, and is formed such that the mesa width of the p type drift layer 136 in the junction terminating region portion is relatively wider. Thereby, the impurity concentration of the p type drift layer 136 in the junction terminating region portion can be made higher than that in the cell region portion. With such a structure, lowering of the breakdown voltage in the junction terminating region portion can be suppressed in the semiconductor device 14 of the present embodiment.

- FIG. 33 is a cross-sectional view showing a schematic structure of a fifteenth embodiment of a semiconductor device according to the present invention.

- a semiconductor device 15 of the present embodiment is characterized in that it further comprises an n ⁇ type drift layer 142 provided between the super junction structure and the n+ drain layer 100 , and the n ⁇ type drift layer 142 and the super junction structure also constitute n type drift layers.

- the n ⁇ type drift layer 142 is formed so as to have an impurity concentration which is lower than that of the n ⁇ type drift layer 102 in the super junction structure.

- FIG. 34 is a cross-sectional view showing a schematic structure of a sixteenth embodiment of a semiconductor device according to the present invention.

- n type drift layers are constituted by the n ⁇ type drift layer 142 and the super junction structure.

- the n ⁇ type drift layer 142 has an impurity concentration which is lower than that of the n ⁇ type drift layer 102 in the super junction structure.

- the n ⁇ type semiconductor layer is further epitaxially grown so as to cover the n ⁇ type semiconductor layer 151 and the p ⁇ type semiconductor layer 158 , and an n ⁇ type semiconductor layer 160 having a film thickness which is the same as the film thickness of the p ⁇ type semiconductor layer 158 is formed ( FIG. 35D ).

- a trench groove 162 matching the trench groove 154 is formed in the n ⁇ type semiconductor layer 160 ( FIG. 35E ).

- the n ⁇ type semiconductor layer 164 is epitaxially grown so as to cover the n ⁇ type semiconductor layer 153 and the p ⁇ type semiconductor layer 158 ( FIG. 35F ).

- the super junction structure can thus be formed by a number of crystal growths which is less than that of the conventional process in which ion injection and buried crystal growth are repeated.

- the super junction structure can be formed by carrying out trench buried crystal growths twice.

- the present invention is not limited thereto.

- the trench buried crystal growth may be repeated three times or more with the aspect ratio per one time being set to one of third of a required aspect ratio.

- the super junction structures of the first time and the second time are formed in a striped shape and are formed so as to intersect one another, alignment can be exactly carried out.

- the present invention has been described above. However, the present invention is not limited to these embodiments, and can be modified and achieved within the scope and the sprits thereof.

- the super junction structure, the p type base layer, the n+ source layer, and the gate electrode are formed in striped shapes. However, they may be formed so as to be in lattice shapes or staggered shapes.

- vertical power MOSFETs using silicon (Si) serving as semiconductor materials have been described.

- Si silicon

- diamond can be used in addition to compound semiconductors such as silicon carbide (SiC), gallium nitride (GaN), aluminum nitride (AlN), or the like.

Abstract

A semiconductor device includes a first-conductivity-type semiconductor layer which includes a cell region portion and a junction terminating region portion. The junction terminating region portion is a region portion which is positioned in an outer periphery of the cell region portion to maintain a breakdown voltage by extending a depletion layer to attenuate an electric field.

Description

This application claims benefit of priority under 35USC § 119 to Japanese patent application No. 2002-74633, filed on Mar. 18, 2002, the contents of which are incorporated by reference herein.

1. Field of the Invention

The present invention relates to a semiconductor device and a method of manufacturing a semiconductor device, and in particular, to a structure of a junction terminating region portion of a power semiconductor device which is suitable for a switching element for electric power.

2. Related Background Art

In response to the demand to make electrical power equipment compact and high-performance in recent years in the power electronics field, performance improvements with respect to making lowering loss, increasing speed and improving the ruggedness have been carried out in addition to making them have a high breakdown voltage and making them able to handle great current in the power semiconductor devices. Among them, a power MOSFET (Metal Oxide Semiconductor Field Effect Transistor) has been established as a key device in the switching power source field or the like because of the high-speed switching performance thereof.

Because the MOSFET is a majority carrier device, the MOSFET has an advantage that there is no minority carrier storage time and switching is fast. However, on the other hand, because there is no electric conductivity modulation, a device which has a high breakdown voltage is disadvantageous with respect to the ON-state resistance as compared with a bipolar device such as an IGBT (Insulated Gate Bipolar Transistor) or the like. This results from the fact that the higher the breakdown voltage a device has, the more the ON-state resistance of the MOSTFET increases, because it is necessary to make an n type base layer thicker and to make the impurity concentration lower in order to obtain a higher breakdown voltage in the MOSFET.

The ON-state resistance of the power MOSFET greatly depends on the electrical resistance in a conductive layer (n type drift layer) portion. Further, the impurity concentration determining the electrical resistance at the n type drift layer cannot rise to greater than or equal to the limit, in accordance with the breakdown voltage of the pn junction which the p type base and the n type drift layer form. Therefore, a trade-off relationship exists between the device breakdown voltage and the ON-state resistance. It is important to improve this trade-off for a low electric power consumption device. In this trade-off, there is a limit which is determined by the material of the device, and this limit must be exceeded in order to realize a low ON-state resistance device exceeding existing power devices.

As one example of MOSFETs for solving this problem, a structure is known in which a resurf structure called a super junction structure is buried in an n type drift layer. A conventional power MOSFET having a super junction structure will be described with reference to FIG. 36 . Note that, in the following figures, like parts are denoted by like reference numerals, and detailed descriptions thereof will be omitted.

In an OFF-state, a depletion layer spreads at junctions between these p type drift layers 106 and n− type drift layers 102. Even if the impurity concentration of the n− type drift layers 102 is made high, the n− type drift layers 102 and the p type drift layers 106 are completely depleted before breaking down. In accordance therewith, a breakdown voltage which is the same as that of the conventional MOSFET can be obtained.

The impurity concentration of the n− type drift layer 102 does not depend on a breakdown voltage of the device, but it depends on the width of the p type drift layer 106 and the width of the n− type drift layer 102 itself between these p type drift layers 106. If the width of the n− type drift layer 102 and the width of the p type drift layer 106 are made narrower, the impurity concentration of the n− type drift layer 102 can be made much higher, and a greater reduction of the ON-state resistance and a higher breakdown voltage can be achieved.

At the time of designing such a MOSFET, the impurity concentrations of the n− type drift layer 102 and the p type drift layer 106 are important to determine the breakdown voltage and the ON-state resistance. In principle, due to the respective impurity concentrations of the n− type drift layer 102 and the p type resurf layer 106 being made equal, the impurity concentrations equivalently become zero, the high breakdown voltage can be obtained.

However, with respect to the semiconductor device having a conventional super junction structure, no structure has been developed which is effective for obtaining a high breakdown voltage in a blocking state (OFF-state) or at the time of turning-off at a junction terminating region portion which is positioned at the outer periphery of an element active region portion (hereinafter referred to as a cell region portion) and which is a region portion for maintaining the breakdown voltage by attenuating the electrical field by extending the depletion layers. Therefore, because the way of spreading of the depletion layers in the cell region portion and the junction terminating region portion are different from one another, the optimum impurity concentrations are different from one another. Accordingly, if the device is manufactured such that the impurity amounts in the cell region portion and the junction terminating region portion are the same, the breakdown voltage at the terminating portion decreases, and an electric field locally concentrates at this place. As a result, there are cases in which the device is broken. In this way, there is the problem that a sufficiently high breakdown voltage cannot be obtained by the entire device in the prior art.

Further, because there are dispersions among the processes at the time of actual manufacturing, it is difficult to make the respective impurity amounts of the n− type drift layer 102 and the p type drift layer 106 completely equal, and the breakdown voltage deteriorates in accordance therewith. Accordingly, it is necessary to carry out designing of the device in consideration of such a decrease of the breakdown voltage due to the process margin. In order to lower the ON-state resistance, it is effective to raise the impurity concentration of the n− type drift layer 102. On the other hand, the process margin for the breakdown voltage is determined by the difference in the impurity amounts between the n− type drift layer 102 and the p type drift layer 106. Therefore, when the impurity amount of the n− type drift layer 102 is increased, because the difference itself determining the process margin is not changed, the ratio between the allowed impurity amount and the impurity amount of the n− type drift layer 102 becomes small. Namely, the process margin becomes small.

According to a first aspect of the present invention, there is provided a semiconductor device comprising:

a first—first conductivity type semiconductor layer which includes a cell region portion and a junction terminating region portion, the junction terminating region portion being a region portion which is positioned in an outer periphery of the cell region portion to maintain a breakdown voltage by extending a depletion layer to attenuate an electric field;

a second-first conductivity type semiconductor layer which is formed on one surface of the first—first conductivity type semiconductor layer;

a first main electrode which is electrically connected to the second-first conductivity type semiconductor layer;

first-second conductivity type semiconductor layers which are formed in the cell region portion of the first—first conductivity type semiconductor layer in substantially vertical directions to the one surface of the first—first conductivity type semiconductor layer, respectively, and which are periodically disposed in a first direction which is an arbitrary direction parallel to the one surface;

a second—second conductivity type semiconductor layer which is selectively formed in the other surface portion of the first—first conductivity type semiconductor layer so as to contact the first-second conductivity type semiconductor layers;

a third-first conductivity type semiconductor layer which is selectively formed in the surface portion of the second—second conductivity type semiconductor layer;

a second main electrode which is formed so as to contact the second—second conductivity type semiconductor layer and the third-first conductivity type semiconductor layer;

a control electrode which is formed on the surface of the first—first conductivity type semiconductor layer sandwiched by the adjacent second—second conductivity type semiconductor layers, the surface of the adjacent second—second conductivity type semiconductor layers and the surface of the third-first conductivity type semiconductor layer, with a gate insulating film interposed therebetween; and

third-second conductivity type semiconductor layers which are formed in the junction terminating region portion and are periodically disposed in at least one direction of the first direction and a second direction perpendicular to the first direction.

According to a second aspect of the invention, there is provided a method of manufacturing a semiconductor device having a super junction structure with a first conductivity type semiconductor layer on which a trench groove whose aspect ratio is R is provided and a second conductivity type semiconductor layer which is buried in the trench groove, the method of manufacturing the semiconductor device comprising:

forming a trench groove having an aspect ratio of R/N (N is a natural number greater than 1) in a first conductivity type semiconductor layer;

epitaxially growing a second conductivity type semiconductor layer so as to bury the trench groove;

removing the second conductivity type semiconductor layer until a surface of the first conductivity type semiconductor layer is exposed;

epitaxially growing the first conductivity type semiconductor layer on the first conductivity type semiconductor layer and the second conductivity type semiconductor layer such that the thickness of the first conductivity type semiconductor layer increases by a length which is substantially the same as a depth of the trench groove formed by the first process;

selectively removing the first conductivity type semiconductor layer such that the second conductivity type semiconductor layer which is buried in the trench groove formed by the first process is exposed; and

repeating the epitaxially growing the second conductivity type semiconductor layer through selectively removing the first conductivity type semiconductor layer (N−1) times.

Several embodiments of the present invention will be described with reference to the drawings. Hereinafter, first, embodiments of a semiconductor device according to the present invention will be described, and finally, an embodiment of a method of manufacturing the semiconductor device according to the present invention will be described.

(A) Embodiments of the Semiconductor Device

Hereinafter, a power MOSFET having a super junction structure will be described. However, the semiconductor device according to the present invention is not limited to a power MOSFET, and can be applied to an SBD or MPS diode having a super junction structure, a switching element such as an SIT, a JFET, an IGBT, or the like, and a complex element or an integrated element of the diodes and the switching elements.

(1) First Embodiment

The semiconductor device 1 of the present embodiment has an n+ type drain layer 20, a drain electrode 40, the n type drift layers 26, the p type drift layers 28, p type base layers 30, an n+ type source layer 32, a source electrode 38, an insulated gate electrode 36, and a fieldplate electrode 48.