KR20180098148A - 메모리 전원 공급 회로, 제어 장치, 및 메모리 전원 공급 방법 - Google Patents

메모리 전원 공급 회로, 제어 장치, 및 메모리 전원 공급 방법 Download PDFInfo

- Publication number

- KR20180098148A KR20180098148A KR1020180020647A KR20180020647A KR20180098148A KR 20180098148 A KR20180098148 A KR 20180098148A KR 1020180020647 A KR1020180020647 A KR 1020180020647A KR 20180020647 A KR20180020647 A KR 20180020647A KR 20180098148 A KR20180098148 A KR 20180098148A

- Authority

- KR

- South Korea

- Prior art keywords

- power supply

- memory

- voltage

- supply

- capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/148—Details of power up or power down circuits, standby circuits or recovery circuits

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Power Sources (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Read Only Memory (AREA)

Abstract

메모리 전원 생성부(12)는, 동작 전원의 공급 개시 시에 미리 정해진 비율로 출력 전압을 상승시킴으로써, 콘덴서(15)에 대하여 메모리 전원을 서서히 공급하고, 역류 방지부(14)가 동작 전원(Pw)의 전압(Vw)이 콘덴서(15)의 충전 전압(Vc)을 하회한 경우에는, 콘덴서(15)로부터 메모리 전원 생성부(12)로 흐르는 역류 전류를 방지하며, 공급 제어부(17)는, Vc가 Vcon 이상인 경우에 불휘발성 메모리(ROM)에 대하여 메모리 전원을 공급하고, Vc가 Vcoff 이하인 경우에 ROM에 대한 메모리 전원의 공급을 정지한다.

Description

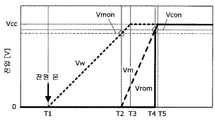

도 2는 동작 전원 공급 개시 시에 있어서의 회로 전압의 변화를 나타내는 그래프이다.

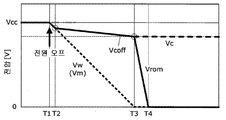

도 3은 동작 전원 공급 정지 시에서의 회로 전압의 변화를 나타내는 그래프이다.

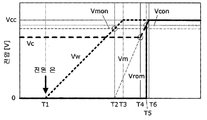

도 4는 동작 전원 공급 재개 시에서의 회로 전압의 변화를 나타내는 그래프이다.

도 5는 제2 실시의 형태에 따른 제어 장치의 구성을 나타내는 블럭도이다.

도 6은 전원 상태 판정 시에서의 회로 전압의 변화를 나타내는 타이밍 차트이다.

도 7은 제2 실시의 형태에 따른 전원 상태 판정 시에서의 회로 전압의 변화를 나타내는 그래프이다.

도 8은 제3 실시의 형태에 따른 전원 상태 판정 시에서의 회로 전압의 변화를 나타내는 그래프이다.

Claims (8)

- 메모리 전원 공급 회로에 있어서,

전원 회로로부터 공급된 동작 전원에 기초하여, 불휘발성 메모리의 동작에 이용하는 메모리 전원을 생성하는 메모리 전원 생성부와,

상기 메모리 전원 생성부에서 생성된 상기 메모리 전원을 백업하는 콘덴서와,

상기 불휘발성 메모리에 대한 상기 메모리 전원의 공급/정지를 제어하는 공급 제어부와,

상기 메모리 전원 생성부와 상기 콘덴서 사이에 접속되어, 상기 동작 전원의 전압이 상기 콘덴서의 충전 전압을 상회한 경우에는, 상기 메모리 전원 생성부의 출력 전압을 상기 콘덴서에 공급하고, 상기 동작 전원의 전압이 상기 충전 전압을 하회한 경우에는, 상기 콘덴서로부터 상기 메모리 전원 생성부로 흐르는 역류 전류를 방지하는 역류 방지부

를 포함하고,

상기 메모리 전원 생성부는, 상기 동작 전원의 공급 개시 시에 미리 정해진 비율로 상기 출력 전압을 상승시킴으로써, 상기 콘덴서에 대하여 상기 메모리 전원을 서서히 공급하고,

상기 공급 제어부는, 상기 충전 전압이 제1 전압 이상인 경우에, 상기 불휘발성 메모리에 대하여 상기 메모리 전원을 공급하고, 상기 충전 전압이 제2 전압 이하인 경우에, 상기 불휘발성 메모리에 대한 상기 메모리 전원의 공급을 정지하는 것을 특징으로 하는 메모리 전원 공급 회로. - 제1항에 있어서,

상기 역류 방지부 대신에, 상기 전원 회로와 상기 메모리 전원 생성부 사이에 접속되어, 상기 동작 전원의 전압이 상기 충전 전압을 상회한 경우에는, 상기 동작 전원을 상기 메모리 전원 생성부에 공급하고, 상기 동작 전원의 전압이 상기 충전 전압을 하회한 경우에는, 상기 콘덴서로부터 상기 메모리 전원 생성부를 개재하여 상기 전원 회로로 흐르는 역류 전류를 방지하는 역류 방지부를 포함하는 것을 특징으로 하는 메모리 전원 공급 회로. - 제1항 또는 제2항에 있어서,

상기 메모리 전원 생성부는, 상기 전원 회로의 전압이 제3 전압 이상이 된 경우에, 상기 출력 전압의 출력을 개시하는 것을 특징으로 하는 메모리 전원 공급 회로. - 제어에 이용하는 각종 데이터를 불휘발성 메모리에서 보존하는 제어 장치에 있어서,

상기 불휘발성 메모리에 대하여 메모리 전원을 공급하는 회로로서, 제1항 또는 제2항에 기재된 메모리 전원 공급 회로를 포함하는 것을 특징으로 하는 제어 장치. - 제4항에 있어서,

상기 동작 전원의 생성에 이용되는 주전원의 주전원 전압이 제4 전압을 하회한 경우, 상기 주전원의 차단을 예고하는 주전원 저하 출력을 출력하는 전원 차단 예고부와,

상기 동작 전원의 전압이 제5 전압의 저하를 하회한 경우, 상기 동작 전원의 전압 저하를 나타내는 동작 전원 저하 출력을 출력하는 전원 전압 검출부와,

상기 주전원 저하 출력이 상기 주전원의 차단을 예고하고, 상기 동작 전원 저하 출력이 상기 동작 전원의 전압 저하를 나타내고 있지 않은 경우, 상기 동작 전원의 전원 공급 상태가 전원 저하 상태에 있다고 판정하는 전원 상태 판정부와,

상기 주전원 저하 출력에 의해 상기 주전원의 차단이 예고된 경우, 상기 불휘발성 메모리에 기록해야 할 데이터의 유무를 확인하고, 얻어진 확인 결과에 기초하여, 상기 메모리 전원에 관한 강제 차단의 필요와 불필요를 나타내는 강제 차단 제어 출력을 출력하는 연산 제어 회로와,

상기 전원 상태 판정부에 의해 상기 동작 전원이 상기 전원 저하 상태에 있다고 판정되어 있는 기간에 있어서, 상기 연산 제어 회로로부터 출력된 새로운 강제 차단 제어 출력을 받아들여, 상기 공급 제어부로 유지 출력하는 강제 차단 유지부

를 더 포함하고,

상기 공급 제어부는, 상기 강제 차단 유지부로부터의 유지 출력이 강제 차단 필요를 나타내는 경우, 상기 불휘발성 메모리에 대한 상기 메모리 전원의 공급을 강제적으로 차단하는 것을 특징으로 하는 제어 장치. - 제5항에 있어서,

상기 전원 차단 예고부는, 상기 주전원의 복구에 따라서 상기 주전원 전압이 제6 전압 이상으로 상승한 경우, 상기 주전원 저하 출력의 출력을 정지하고,

상기 전원 상태 판정부는, 상기 주전원 저하 출력의 출력이 정지하고 있고, 상기 동작 전원 저하 출력이 상기 동작 전원의 전압 저하를 나타내고 있지 않은 경우, 상기 동작 전원의 전원 공급 상태가 전원 공급 상태에 있다고 판정하고,

상기 강제 차단 유지부는, 상기 전원 상태 판정부에서의 판정 결과가 상기 전원 저하 상태로부터 상기 전원 공급 상태로 변화한 경우, 강제 차단 불필요를 상기 공급 제어부로 유지 출력하며,

상기 공급 제어부는, 상기 강제 차단 유지부로부터의 유지 출력이 강제 차단 불필요를 나타내는 경우, 상기 불휘발성 메모리에 대한 상기 메모리 전원의 강제 차단을 해제하는 것을 특징으로 하는 제어 장치. - 메모리 전원 공급 방법에 있어서,

메모리 전원 생성부가, 전원 회로로부터 공급된 동작 전원에 기초하여, 불휘발성 메모리의 동작에 이용하는 메모리 전원을 생성하는 메모리 전원 생성 단계와,

콘덴서가, 상기 메모리 전원 생성부에서 생성된 상기 메모리 전원을 백업하는 단계와,

공급 제어부가, 상기 불휘발성 메모리에 대한 상기 메모리 전원의 공급/정지를 제어하는 공급 제어 단계와,

상기 메모리 전원 생성부와 상기 콘덴서 사이에 접속된 역류 방지부가, 상기 동작 전원의 전압이 상기 콘덴서의 충전 전압을 상회한 경우에는, 상기 메모리 전원 생성부의 출력 전압을 상기 콘덴서에 공급하고, 상기 동작 전원의 전압이 상기 충전 전압을 하회한 경우에는, 상기 콘덴서로부터 상기 메모리 전원 생성부로 흐르는 역류 전류를 방지하는 역류 방지 단계

를 포함하고,

상기 메모리 전원 생성 단계는, 상기 동작 전원의 공급 개시 시에 미리 정해진 비율로 상기 출력 전압을 상승시킴으로써, 상기 콘덴서에 대하여 상기 메모리 전원을 서서히 공급하고,

상기 공급 제어 단계는, 상기 충전 전압이 제1 전압 이상인 경우에, 상기 불휘발성 메모리에 대하여 상기 메모리 전원을 공급하고, 상기 충전 전압이 제2 전압이하인 경우에, 상기 불휘발성 메모리에 대한 상기 메모리 전원의 공급을 정지하는 것을 특징으로 하는 메모리 전원 공급 방법. - 제7항에 있어서,

상기 역류 방지 단계 대신에, 상기 전원 회로와 상기 메모리 전원 생성부 사이에 접속된 상기 역류 방지부가, 상기 동작 전원의 전압이 상기 충전 전압을 상회한 경우에는, 상기 동작 전원을 상기 메모리 전원 생성부에 공급하고, 상기 동작 전원의 전압이 상기 충전 전압을 하회한 경우에는, 상기 콘덴서로부터 상기 메모리 전원 생성부를 개재하여 상기 전원 회로로 흐르는 역류 전류를 방지하는 역류 방지 단계를 포함하는 것을 특징으로 하는 메모리 전원 공급 방법.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JPJP-P-2017-033393 | 2017-02-24 | ||

| JP2017033393 | 2017-02-24 | ||

| JP2018003593A JP7007922B2 (ja) | 2017-02-24 | 2018-01-12 | 制御装置、および制御方法 |

| JPJP-P-2018-003593 | 2018-01-12 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20180098148A true KR20180098148A (ko) | 2018-09-03 |

| KR102154722B1 KR102154722B1 (ko) | 2020-09-10 |

Family

ID=63528082

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020180020647A Active KR102154722B1 (ko) | 2017-02-24 | 2018-02-21 | 메모리 전원 공급 회로, 제어 장치, 및 메모리 전원 공급 방법 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP7007922B2 (ko) |

| KR (1) | KR102154722B1 (ko) |

| CN (1) | CN108511009B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20220103853A (ko) * | 2021-01-15 | 2022-07-25 | 삼성전자주식회사 | 불휘발성 메모리 장치의 데이터 보존성 개선을 위한 장치 및 방법 |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2021044037A (ja) * | 2019-09-10 | 2021-03-18 | キオクシア株式会社 | メモリシステム及び電源回路 |

| JP7332493B2 (ja) * | 2020-01-30 | 2023-08-23 | キオクシア株式会社 | メモリシステムおよび半導体記憶装置 |

| JP2022051181A (ja) * | 2020-09-18 | 2022-03-31 | キオクシア株式会社 | メモリシステム及び電源回路 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003005871A (ja) | 2001-06-26 | 2003-01-08 | Omron Corp | データ処理装置のデータバックアップ方法および装置 |

| JP2005140661A (ja) * | 2003-11-07 | 2005-06-02 | Omron Corp | 計測機器 |

| JP3805973B2 (ja) * | 2000-11-21 | 2006-08-09 | 株式会社東芝 | 半導体記憶装置 |

| KR20120067955A (ko) * | 2010-12-16 | 2012-06-26 | 캐논 가부시끼가이샤 | 셧다운 처리를 적절하게 실행할 수 있는 정보 처리 장치, 정보 처리 장치의 제어 방법, 및 저장 매체 |

| JP2014054141A (ja) * | 2012-09-10 | 2014-03-20 | Ricoh Co Ltd | 給電装置、及び給電システム |

| JP2015219897A (ja) * | 2014-05-21 | 2015-12-07 | 富士電機株式会社 | データ制御装置 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6395825A (ja) * | 1986-10-09 | 1988-04-26 | 株式会社東芝 | バツクアツプ電源回路 |

| JPH06276677A (ja) * | 1993-03-19 | 1994-09-30 | Fujitsu Ltd | 突入電流防止回路 |

| JP3244377B2 (ja) * | 1994-04-20 | 2002-01-07 | 三洋電機株式会社 | 電圧生成回路 |

| JPH1115571A (ja) * | 1997-06-20 | 1999-01-22 | Toshiba Corp | プログラマブルコントロ−ラ |

| JPH11288319A (ja) * | 1998-01-28 | 1999-10-19 | Seiko Instruments Inc | 電子機器 |

| JP3604991B2 (ja) * | 2000-03-14 | 2004-12-22 | Necエレクトロニクス株式会社 | 低電源電圧検知回路 |

| JP3979417B2 (ja) * | 2004-11-29 | 2007-09-19 | セイコーエプソン株式会社 | 電力供給制御回路、電子機器、半導体装置、電力供給制御回路の制御方法および電子機器の制御方法 |

| JP2010122857A (ja) * | 2008-11-19 | 2010-06-03 | Yamatake Corp | バックアップ装置 |

| US8806271B2 (en) * | 2008-12-09 | 2014-08-12 | Samsung Electronics Co., Ltd. | Auxiliary power supply and user device including the same |

| TW201108555A (en) * | 2009-08-19 | 2011-03-01 | guo-shu Zheng | Fast charging device and its method |

| CN101997342A (zh) * | 2009-08-19 | 2011-03-30 | 郑国书 | 快速充电装置及其方法 |

| JP5429638B2 (ja) * | 2010-06-28 | 2014-02-26 | 株式会社リコー | 画像形成装置及び画像形成装置の電源制御方法 |

| US9190120B2 (en) * | 2010-10-20 | 2015-11-17 | Samsung Electronics Co., Ltd. | Storage device including reset circuit and method of resetting thereof |

| JP5633545B2 (ja) * | 2012-09-19 | 2014-12-03 | Tdk株式会社 | フラッシュメモリシステム、及び電源供給制御方法 |

| JP6123282B2 (ja) * | 2012-12-20 | 2017-05-10 | 富士電機株式会社 | プログラマブルコントローラおよび電源切断対処方法 |

| JP2015170332A (ja) * | 2014-03-11 | 2015-09-28 | キヤノン株式会社 | Nandフラッシュモジュール制御方法 |

| JP6384306B2 (ja) * | 2014-12-16 | 2018-09-05 | Tdk株式会社 | 電源回路及びこれを備えるフラッシュメモリシステム並びに電源回路の制御方法 |

| JP2016194878A (ja) * | 2015-04-01 | 2016-11-17 | 富士電機株式会社 | 電源制御装置 |

-

2018

- 2018-01-12 JP JP2018003593A patent/JP7007922B2/ja active Active

- 2018-02-21 KR KR1020180020647A patent/KR102154722B1/ko active Active

- 2018-02-23 CN CN201810155090.XA patent/CN108511009B/zh active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3805973B2 (ja) * | 2000-11-21 | 2006-08-09 | 株式会社東芝 | 半導体記憶装置 |

| JP2003005871A (ja) | 2001-06-26 | 2003-01-08 | Omron Corp | データ処理装置のデータバックアップ方法および装置 |

| JP2005140661A (ja) * | 2003-11-07 | 2005-06-02 | Omron Corp | 計測機器 |

| KR20120067955A (ko) * | 2010-12-16 | 2012-06-26 | 캐논 가부시끼가이샤 | 셧다운 처리를 적절하게 실행할 수 있는 정보 처리 장치, 정보 처리 장치의 제어 방법, 및 저장 매체 |

| JP2014054141A (ja) * | 2012-09-10 | 2014-03-20 | Ricoh Co Ltd | 給電装置、及び給電システム |

| JP2015219897A (ja) * | 2014-05-21 | 2015-12-07 | 富士電機株式会社 | データ制御装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20220103853A (ko) * | 2021-01-15 | 2022-07-25 | 삼성전자주식회사 | 불휘발성 메모리 장치의 데이터 보존성 개선을 위한 장치 및 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR102154722B1 (ko) | 2020-09-10 |

| CN108511009A (zh) | 2018-09-07 |

| JP7007922B2 (ja) | 2022-01-25 |

| JP2018142392A (ja) | 2018-09-13 |

| CN108511009B (zh) | 2022-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20180098148A (ko) | 메모리 전원 공급 회로, 제어 장치, 및 메모리 전원 공급 방법 | |

| KR101070601B1 (ko) | 비휘발성 메모리를 위한 향상된 기록 중단 메커니즘 | |

| US8555090B2 (en) | Information processing apparatus and method of controlling power thereof | |

| JP4111890B2 (ja) | 無停電電源装置 | |

| JP5464851B2 (ja) | インバータ装置 | |

| US20220179467A1 (en) | Power supply circuit, power supply controlling method and storage medium | |

| CN105807885B (zh) | 一种掉电保护方法及装置 | |

| JP2014017948A (ja) | 車載用電源装置 | |

| KR20130129840A (ko) | 화상형성장치, 화상형성장치의 제어 방법, 및 기억 매체 | |

| WO2019224863A1 (ja) | 電力変換装置 | |

| JP4411014B2 (ja) | コンピュータおよびその電源バックアップ方法 | |

| US20060220723A1 (en) | Controlling circuit for controlling operating clock and/or driving voltage of logic circuit, and method thereof | |

| JP2011077673A (ja) | リセット回路 | |

| JP2015170332A (ja) | Nandフラッシュモジュール制御方法 | |

| CN115862711A (zh) | 掉电保护方法、掉电保护电路、芯片、电子设备及系统 | |

| JP4543328B2 (ja) | 情報処理装置、無停電電源装置、給電方法、記録媒体、および、プログラム | |

| JPH0728572A (ja) | 停電時自動データ保存装置 | |

| CN121070161B (zh) | 存储系统的供电管理方法及电子设备 | |

| US20240402776A1 (en) | Magnetic disk device, method for controlling magnetic disk device, and computer program product | |

| JP2008079438A (ja) | プログラマブルコントローラおよびプログラマブルコントローラのデータバックアップ方法 | |

| JP6966361B2 (ja) | 電圧低下検知システム | |

| JP2007124781A (ja) | 電源装置、無停電電源装置および電力出力制御方法 | |

| CN119882975A (zh) | 一种vpx计算板系统盘多级掉电保护方法及系统 | |

| JPS61148554A (ja) | C−mos使用のメモリ装置 | |

| JP2003216281A (ja) | 制御装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| R15-X000 | Change to inventor requested |

St.27 status event code: A-3-3-R10-R15-oth-X000 |

|

| R16-X000 | Change to inventor recorded |

St.27 status event code: A-3-3-R10-R16-oth-X000 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E90F | Notification of reason for final refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| U11 | Full renewal or maintenance fee paid |

Free format text: ST27 STATUS EVENT CODE: A-4-4-U10-U11-OTH-PR1001 (AS PROVIDED BY THE NATIONAL OFFICE) Year of fee payment: 6 |