KR20170106442A - 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 - Google Patents

상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 Download PDFInfo

- Publication number

- KR20170106442A KR20170106442A KR1020177023166A KR20177023166A KR20170106442A KR 20170106442 A KR20170106442 A KR 20170106442A KR 1020177023166 A KR1020177023166 A KR 1020177023166A KR 20177023166 A KR20177023166 A KR 20177023166A KR 20170106442 A KR20170106442 A KR 20170106442A

- Authority

- KR

- South Korea

- Prior art keywords

- voltage

- negative

- circuit

- region

- gate

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- H01L27/11521—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0425—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a merged floating gate and select transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G11C16/16—Circuits for erasing electrically, e.g. erase voltage switching circuits for erasing blocks, e.g. arrays, words, groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/02—Structural aspects of erasable programmable read-only memories

- G11C2216/04—Nonvolatile memory cell provided with a separate control gate for erasing the cells, i.e. erase gate, independent of the normal read control gate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

Abstract

비휘발성 메모리 디바이스가 제1 전도성 타입의 반도체 기판을 포함한다. 비휘발성 메모리 셀들의 어레이가 반도체 기판에 위치되고, 복수의 로우들 및 컬럼들로 배열된다. 각각의 메모리 셀은 제2 전도성 타입의 반도체 기판의 표면 상의 제1 영역, 및 제2 전도성 타입의 반도체 기판의 표면 상의 제2 영역을 포함한다. 채널 영역이 제1 영역과 제2 영역 사이에 있다. 워드 라인이 채널 영역의 제1 부분 위에 놓여 있으면서 그로부터 절연되고, 제1 영역에 인접하면서 제1 영역과 거의 또는 전혀 중첩되지 않는다. 플로팅 게이트가 채널 영역의 제2 부분 위에 놓여 있고, 제1 부분에 인접하면서 그로부터 절연되고, 제2 영역에 인접한다. 커플링 게이트가 플로팅 게이트 위에 놓여 있다. 비트 라인이 제1 영역에 접속된다. 프로그래밍, 판독, 또는 소거의 동작들 동안, 네거티브 전압이 선택된 또는 비선택된 메모리 셀들의 워드 라인들 및/또는 커플링 게이트들에 인가될 수 있다.

Description

본 발명은 비휘발성 메모리 셀 디바이스 및 그의 동작 방법에 관한 것이다. 보다 구체적으로, 본 발명은 상보성 전압 서플라이들이 사용되는 그러한 메모리 디바이스에 관한 것이다. 네거티브 전압이 판독, 프로그래밍, 또는 소거의 동작들 동안에 제어 게이트 및/또는 워드 라인이나 선택된 또는 비선택된 메모리 셀에 인가된다.

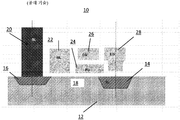

비휘발성 메모리 셀들은 본 기술 분야에 잘 알려져 있다. 종래 기술의 하나의 비휘발성 분리형 게이트 메모리 셀(10)이 도 1에 도시되어 있다. 메모리 셀(10)은 P 타입과 같은 제1 전도성 타입의 반도체 기판(12)을 포함한다. 기판(12)은 N 타입과 같은 제2 전도성 타입의 제1 영역(14)(소스 라인(SL)으로도 알려져 있음)이 형성되어 있는 표면을 갖는다. 또한 N 타입의 제2 영역(16)(드레인 라인(drain line)으로도 알려져 있음)이 기판(12)의 표면 상에 형성된다. 제1 영역(14)과 제2 영역(16) 사이에는 채널 영역(18)이 있다. 비트 라인(bit line, BL)(20)이 제2 영역(16)에 접속된다. 워드 라인(WL)(22)이 채널 영역(18)의 제1 부분 위에 위치되면서 그로부터 절연된다. 워드 라인(22)은 제2 영역(16)과 거의 또는 전혀 중첩되지 않는다. 플로팅 게이트(floating gate, FG)(24)가 채널 영역(18)의 다른 부분 위에 있다. 플로팅 게이트(24)는 워드 라인(22)에 인접하고 그로부터 절연된다. 플로팅 게이트(24)는 또한 제1 영역(14)에 인접한다. 플로팅 게이트(24)는 제1 영역(14)과 중첩되어 영역(14)으로부터 플로팅 게이트(24) 내로의 커플링을 제공할 수 있다. 커플링 게이트(coupling gate, CG)(26)(제어 게이트로도 알려져 있음)가 플로팅 게이트(24) 위에 있으면서 그로부터 절연된다. 소거 게이트(erase gate, EG)(28)가 제1 영역(14) 위에 있고, 플로팅 게이트(24) 및 커플링 게이트(26)에 인접하면서 그들로부터 절연된다. 플로팅 게이트(24)의 상측 코너는 소거 효율을 향상시키기 위해 T자형 소거 게이트(28)의 내측 코너를 향해 가리킬 수 있다. 소거 게이트(28)는 또한 제1 영역(14)으로부터 절연된다. 셀(10)은 미국 특허 제7,868,375호에 더욱 상세하게 설명되며, 그 개시 내용은 전체적으로 본 명세서에 참고로 포함된다.

종래 기술의 비휘발성 메모리 셀(10)의 소거 및 프로그래밍에 대한 한 가지 예시적인 동작은 다음과 같다. 셀(10)은 다른 단자들이 0 볼트인 상태에서 소거 게이트(28) 상에 고전압을 인가함으로써 파울러-노드하임 터널링 메커니즘(Fowler-Nordheim tunneling mechanism)을 통해 소거된다. 전자들은 플로팅 게이트(24)로부터 소거 게이트(28) 내로 터널링하여 플로팅 게이트(24)가 포지티브로 대전되게 하여, 셀(10)을 판독 상태에서 턴온시킨다. 생성된 셀 소거 상태는 '1' 상태로 알려져 있다. 셀(10)은, 커플링 게이트(26) 상에 고전압을, 소스 라인(14) 상에 고전압을, 소거 게이트(28) 상에 중간 전압을, 그리고 비트 라인(20) 상에 프로그래밍 전류를 인가함으로써, 소스측 열전자 프로그래밍 메커니즘을 통해 프로그래밍된다. 워드 라인(22)과 플로팅 게이트(24) 사이의 갭을 가로질러서 유동하는 전자들 중 일부는 플로팅 게이트(24) 내에 주입하기에 충분한 에너지를 획득하여 플로팅 게이트(24)가 네거티브로 대전되게 하여, 셀(10)을 판독 상태에서 턴오프시킨다. 생성된 셀 프로그래밍 상태는 '0' 상태로 알려져 있다.

종래 기술에서, 포지티브 또는 0 전압들의 다양한 조합들이 워드 라인(22), 커플링 게이트(26), 및 플로팅 게이트(24)에 판독, 프로그래밍, 및 소거 동작들을 수행하도록 인가되었다. 종래 기술은 이들 동작들에 대해 네거티브 전압들을 인가하지 않았다.

본 발명의 하나의 목적은, 동작에 따라, 선택된 또는 비선택된 셀들에 대한 판독, 프로그래밍, 및/또는 소거 동작들 동안에 네거티브 전압이 워드 라인(22) 및/또는 커플링 게이트(26)에 인가되도록 비휘발성 메모리 셀 디바이스에 대한 네거티브 및 포지티브 전압들을 활용하는 것이다. 이는, 종래 기술에서보다 더 낮은 포지티브 전압 서플라이의 사용을 허용할 것인데, 이는 메모리 셀 디바이스에 대한 더 조밀하고 공간 효율적인 레이아웃을 허용할 것이다.

본 발명은, 동작에 따라, 선택된 또는 비선택된 셀들에 대한 판독, 프로그래밍, 및/또는 소거 동작들 동안에 네거티브 전압이 워드 라인(22) 및/또는 커플링 게이트(26)에 인가되도록 비휘발성 메모리 셀 디바이스에 대한 네거티브 및 포지티브 전압들을 활용한다. 그 결과, 본 발명은 종래 기술보다 메모리 셀 디바이스에 대해 더 조밀하고 공간 효율적인 레이아웃을 허용한다.

도 1은 본 발명의 방법이 적용될 수 있는 종래 기술의 비휘발성 메모리 셀의 단면도이다.

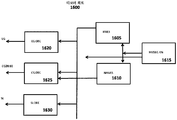

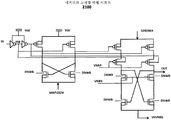

도 2는 도 1에 도시된 종래 기술의 비휘발성 메모리 셀을 사용하는 비휘발성 메모리 디바이스의 블록 다이어그램이다.

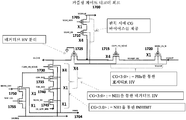

도 3은 비휘발성 메모리 디바이스의 프로그래밍 동작에 대한 예시적인 파형들을 도시한다.

도 4는 비휘발성 메모리 디바이스의 소거 동작에 대한 예시적인 파형들을 도시한다.

도 5는 비휘발성 메모리 디바이스의 정상 판독 동작에 대한 예시적인 파형들을 도시한다.

도 6은 "0" 및 "1"을 판독하기 위한 공차 임계치들을 이용한 비휘발성 메모리 디바이스의 판독 동작에 대한 예시적인 파형들을 도시한다.

도 7a는 비휘발성 메모리 셀의 단면을 도시한다.

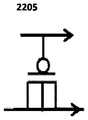

도 7b는 도 7a의 메모리 셀의 기호 표현을 도시한다.

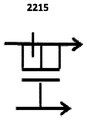

도 7c는 도 7a의 메모리 셀의 기호 표현을 도시한다.

도 8은 네거티브 고전압 레벨 시프터를 도시한다.

도 9는 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 10은 다른 네거티브 고전압 레벨 시프터를 도시한다.

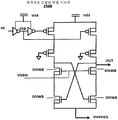

도 11은 전압 서플라이 회로를 도시한다.

도 12는 다른 전압 서플라이 회로를 도시한다.

도 13은 네거티브 고전압 방전 회로를 도시한다.

도 14는 다른 네거티브 고전압 방전 회로를 도시한다.

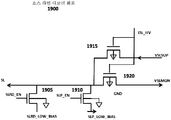

도 15는 접지 스위치를 도시한다.

도 16은 디코더 회로를 도시한다.

도 17은 커플링 게이트 디코더 회로를 도시한다.

도 18은 소거 게이트 디코더 회로를 도시한다.

도 19는 소스 라인 디코더 회로를 도시한다.

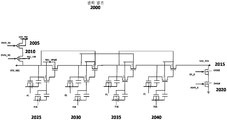

도 20은 전하 펌프를 도시한다.

도 21은 네거티브 고전압 레벨 시프터를 도시한다.

도 22a, 도 22b, 및 도 22c는 커패시터들을 도시한다.

도 23은 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 24는 멀티플렉서를 도시한다.

도 25는 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 2는 도 1에 도시된 종래 기술의 비휘발성 메모리 셀을 사용하는 비휘발성 메모리 디바이스의 블록 다이어그램이다.

도 3은 비휘발성 메모리 디바이스의 프로그래밍 동작에 대한 예시적인 파형들을 도시한다.

도 4는 비휘발성 메모리 디바이스의 소거 동작에 대한 예시적인 파형들을 도시한다.

도 5는 비휘발성 메모리 디바이스의 정상 판독 동작에 대한 예시적인 파형들을 도시한다.

도 6은 "0" 및 "1"을 판독하기 위한 공차 임계치들을 이용한 비휘발성 메모리 디바이스의 판독 동작에 대한 예시적인 파형들을 도시한다.

도 7a는 비휘발성 메모리 셀의 단면을 도시한다.

도 7b는 도 7a의 메모리 셀의 기호 표현을 도시한다.

도 7c는 도 7a의 메모리 셀의 기호 표현을 도시한다.

도 8은 네거티브 고전압 레벨 시프터를 도시한다.

도 9는 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 10은 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 11은 전압 서플라이 회로를 도시한다.

도 12는 다른 전압 서플라이 회로를 도시한다.

도 13은 네거티브 고전압 방전 회로를 도시한다.

도 14는 다른 네거티브 고전압 방전 회로를 도시한다.

도 15는 접지 스위치를 도시한다.

도 16은 디코더 회로를 도시한다.

도 17은 커플링 게이트 디코더 회로를 도시한다.

도 18은 소거 게이트 디코더 회로를 도시한다.

도 19는 소스 라인 디코더 회로를 도시한다.

도 20은 전하 펌프를 도시한다.

도 21은 네거티브 고전압 레벨 시프터를 도시한다.

도 22a, 도 22b, 및 도 22c는 커패시터들을 도시한다.

도 23은 다른 네거티브 고전압 레벨 시프터를 도시한다.

도 24는 멀티플렉서를 도시한다.

도 25는 다른 네거티브 고전압 레벨 시프터를 도시한다.

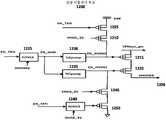

도 2는 다이(200)를 포함하는 플래시 메모리 시스템에 대한 아키텍처의 일 실시예를 도시한다. 다이(200)는, 데이터를 저장하기 위한 메모리 어레이(215) 및 메모리 어레이(220), 도 1의 메모리 셀(10)로서 이전에 기술된 타입의 메모리 셀들의 로우(row)들 및 컬럼(column)들을 포함하는 메모리 어레이들(215, 220), 다이(200)의 다른 컴포넌트들과, 전형적으로, 와이어 본드들(도시되지 않음) - 와이어 본드들은, 이어서 패키징된 칩의 외부로부터 집적 회로에 액세스하는 데 사용되는 핀들(도시되지 않음) 또는 패키지 범프들, 또는 SOC(system on chip) 상에서 다른 매크로들과 상호접속하기 위한 매크로 인터페이스 핀들(도시되지 않음)과 접속함 - 사이의 전기적 연통을 가능하게 하기 위한 패드(240) 및 패드(280); 시스템에 포지티브 및 네거티브 전압 서플라이들을 제공하는 데 사용되는 고전압 회로(275); 리던던시 및 내장형 자가 테스팅(built-in self-testing)과 같은 다양한 제어 기능들을 제공하기 위한 제어 로직(270); 아날로그 회로(265); 각각, 메모리 어레이(215) 및 메모리 어레이(220)로부터 데이터를 판독하는 데 사용되는 감지 회로들(260, 261); 각각, 메모리 어레이(215) 및 메모리 어레이(220) 내의 판독되거나 기록될 로우에 액세스하는 데 사용되는 로우 디코더 회로(245) 및 로우 디코더 회로(246); 각각, 메모리 어레이(215) 및 메모리 어레이(220) 내의 판독되거나 기록될 바이트들에 액세스하는 데 사용되는 컬럼 디코더 회로(255) 및 컬럼 디코더 회로(256); 각각, 메모리 어레이(215) 및 메모리 어레이(220)에 대한 프로그래밍 및 소거 동작들을 위해 증가된 전압들을 제공하는 데 사용되는 전하 펌프 회로(250) 및 전하 펌프 회로(251); 판독 및 기록 동작들을 위해 메모리 어레이(215) 및 메모리 어레이(220)에 의해 공유되는 네거티브 전압 드라이버 회로(230); 및 판독 및 기록 동작들 동안에 메모리 어레이(215)에 의해 사용되는 고전압 드라이버 회로(225), 및 판독 및 기록 동작들 동안에 메모리 어레이(220)에 의해 사용되는 고전압 드라이버 회로(226)를 포함한다.

판독, 소거 또는 프로그래밍 커맨드에 응답하여, 로직 회로(270)는 다양한 전압들이 선택된 메모리 셀(10) 및 비선택된 메모리 셀들(10) 양측 모두의 다양한 부분들에 시기적절한 최소 교란(disturb) 방식으로 공급되게 한다.

선택된 및 비선택된 메모리 셀(10)에 대해, 인가된 전압과 전류는 다음과 같다. 이후에 사용되는 바와 같이, 하기의 약어들, 즉 소스 라인 또는 제1 영역(14)(SL), 비트 라인(20)(BL), 워드 라인(22)(WL), 및 커플링 게이트(26)(CG)가 사용된다.

선택된 메모리 셀(10) 또는 비선택된 메모리 셀(10)에 대한 판독, 소거, 및 프로그래밍 동작들을 수행하는 종래 기술의 방법은 하기의 전압들을 인가하는 것을 수반한다:

동작 #1: PEO(포지티브 소거 동작) 테이블

일 실시예에서, 메모리 셀(10)이 판독 및 프로그래밍 동작들 동안에 비선택될 때 네거티브 전압들이 워드 라인(22)에 인가되어, 하기의 전압들이 인가되게 할 수 있다:

동작 #2: PEO(포지티브 소거 동작) 테이블

다른 실시예에서, 메모리 셀(10)이 판독, 소거, 및 프로그래밍 동작들 동안에 비선택될 때 네거티브 전압들이 워드 라인(22)에 인가될 수 있고, 소거 동작 동안에 네거티브 전압들이 커플링 게이트(26)에 인가되어, 하기의 전압들이 인가되게 할 수 있다:

동작 #3: PNEO(포지티브 네거티브 소거 동작) 테이블

상기에 열거된 CGINH 신호는 소거 게이트(28)를 선택된 셀과 공유하는 비선택된 셀의 커플링 게이트(26)에 인가되는 금지 신호이다.

도 3을 참조하면, 전술된 동작 #3 하의 프로그래밍 동작에 대한 신호 타이밍 파형들의 일례가 도시되어 있다. 메모리 셀(10)의 단자들 WL, BL, CG, EG, SL, EG에 각각 대응하는 바와 같은 신호들 WL, BL, CG, SL, EG는 상기한 바와 같다. 프로그래밍을 위해, 신호 WL(302)이 (예컨대, 후술되는 디코더 회로(1600) 내에서 제어 신호를 설정하기 위해) 먼저 하이 상태(high)(예컨대, ~ Vdd)가 되고, 이어서 (바이어스 전압 Vpwl로) 정착(settle down)하기 시작한다. 이어서, 신호 BL(304) 및 CG(306)는 각각 하이 상태, 예컨대, ~ Vinh = ~ Vdd 및 10 내지 11 V로 되고, 이어서 SL(308)은 하이 상태(예컨대, ~ 4.5 V 내지 5 V)가 된다. 대안으로, CG(306)는 (점선으로 된 파형으로 도시된 바와 같이) SL(308) 이후에 하이 상태가 된다. 신호 CGINH(312)는 신호 CG(306)와 동시에 또는 거의 동시에 하이 상태, 예컨대 3 내지 6 V가 되며, 바람직하게는 신호 EG(310)가 하이 상태, 예컨대 6 내지 9 V가 되기 이전에 하이 상태가 되어, CGINH 레벨을 갖는 비선택된 CG에 대한 교란 효과를 감소시킨다. 대안으로, 신호 CGINH(312)는 신호 EG(310)와 거의 동시에 하이 상태가 될 수 있다. 신호 WL(302)은 전압 Vpwl, 예컨대 1 V로 정착되고, 신호 BL(304)은 CG가 하이 상태가 될 때 전압 Vdp, 예컨대 ~0.5 V로 정착된다. 비선택된 WL들은 선택된 WL(302)이 하이 상태가 되기 이전에 또는 그와 동시에 0 V 또는 네거티브, 예컨대 -0.5 V로 하강한다. 비선택된 CG들 및 EG들은 대기 상태의 값, 예컨대 0 내지 2.6 V에 머무른다. 비선택된 SL들은, CG(306)가 하이 상태가 될 때, 대기 상태의 값, 예컨대 0 V에 머무르거나, 또는 바이어스 전압, 예컨대 1 V로 전환된다(비선택된 SL이 바이어스 레벨로 전환되어 BL들을 통하여 비선택된 셀들을 통한 누설 전류를 방지한다). P 기판(12)은 0 볼트에 있거나, 또는, 대안으로, 프로그래밍 시에 네거티브 전압 레벨에 있을 수 있다.

다양한 신호들이 프로그래밍 전압들로 램핑(ramping)하는 동안 아직 정착되지 않음으로 인한 의도하지 않은 프로그램 교란을 방지하기 위해 신호 BL(304)이 먼저 Vinh(금지 전압(inhibit voltage))로 하이 상태가 된다. 타이밍 시퀀스 CG(306) 대 SL(310)이 교란 효과를 감소시키도록 최적화되는데, 예컨대 어느 신호든 더 많은 교란을 야기하는 신호가 마지막에 하이 상태가 된다. 프로그래밍 펄스들의 램핑 다운은 교란을 최소화하기 위해 반전된다(즉, 먼저 상승한 신호가 이제 마지막에 하강한다). 신호 SL(310)이 하강하고, 이어서 CG(306)가 하강하고, 이어서 WL(302) 및 BL(304)이 하강한다. 기판 P가 네거티브로, 예컨대 -1 V로 되는 프로그래밍의 실시예에서, 이러한 네거티브 전환은 신호 WL이 로우 상태(low)가 되거나 또는 CG가 하이 상태가 되는 것과 동시에 일어난다. EG(310) 및 CGINH(312)의 타이밍된 시퀀스는 도시된 바와 같이 교란 효과(공유된 EG의 비선택된 로우에서의 소프트 소거(soft erase))를 감소시키도록 최적화된다. 신호 CGINH(312)는 신호 EG(312) 이전에 또는 그와 거의 동시에 하이 상태가 된다. 램핑 다운이 반전되면서, CGINH(312)가 신호 EG(312) 이후에 또는 그와 거의 동시에 하강한다.

도 4를 참조하면, 전술된 동작 #3 하의 소거 동작에 대한 신호 타이밍 파형들의 일례가 도시되어 있다. 소거를 위해, (예컨대, 후술되는 디코더 회로(1600)에서 제어 신호를 설정하기 위해) 신호 WL(302)이 하이 상태, 예컨대 Vdd가 되고, 이어서 로우 상태, 예컨대 0 V(또는, 대안으로, -0.5 V와 같은 네거티브)가 된다. WL(302)이 로우 상태가 되는 것과 거의 동시에 또는 그 이후의 단시간에, 신호 CG(306)는 네거티브, 예컨대 -6 V 내지 -9 V가 된다. 이어서, 선택된 EG(310)는 하이 상태, 예컨대 9 V 내지 6 V가 된다. 신호들 BL(304) 및 SL(308)은 대기 상태의 값, 예컨대 0 V에 머무른다. 비선택된 WL들은 선택된 EG(310)가 하이 상태가 되기 이전에 또는 그와 동시에 0 V 또는 네거티브, 예컨대 -0.5 V로 하강한다. 비선택된 CG들 및 EG들은 대기 상태의 값, 예컨대 0 내지 2.6 V에 머무른다. 대안으로, 비선택된 CG들은 네거티브 레벨에 있을 수 있다(선택된 CG 네거티브 레벨과 같을 수 있다). 비선택된 SL들은 대기 상태의 값, 예컨대 0 V에 머무른다. P 기판(12)은 0 볼트에 있거나, 또는 대안으로, 네거티브 전압 레벨에 있어서 소거를 향상시킬 수 있다.

소거 펄스들의 램핑 다운은 대략 차례로 반전된다(즉, 먼저 상승한 신호가 이제 마지막에 하강한다). 신호들 EG(310) 및 CG(306)는 대기 상태의 값, 예컨대 0 V가 된다.

도 5를 참조하면, 전술된 동작 #3 하의 판독 동작에 대한 신호 타이밍 파형들의 일례가 도시되어 있다. 도 6을 참조하면, 본 발명의 메모리 디바이스(10)에서 사용하기 위한, 전술된 바와 같은 포지티브/네거티브 바이어스 레벨들을 위한 판독 신호들에 대한 신호 타이밍 파형의 일례가 도시되어 있다. 이러한 판독 신호 파형은 완전한 비휘발성 소거/프로그래밍/판독 동작을 위해 도 3의 프로그래밍 및 소거 신호 파형과 함께 한다. 정상 판독(Read Normal) 파형에 대해, SL(308)은 대기 상태 값, 예컨대 0 V에 있다. CG(306)는 대기 상태 값, 예컨대 0 V 또는 2.6 V에 있거나, 또는 대안으로, (판독 조건에서 FG 전위와 커플링하는 CG 전압으로 인한 메모리 셀 전류의 증가를 돕기 위해) 판독 시에 더 높은 바이어스 값, 예컨대 3.6 V로 전환한다. EG(310)는 대기 상태 값, 예컨대 0 V 또는 2.6 V에 있거나, 또는 대안으로, (판독 조건에서 FG 전위와 커플링하는 EG 전압으로 인한 메모리 셀 전류의 증가를 돕기 위해) 판독 시에 더 높은 바이어스 값, 예컨대 3.6 V로 전환한다. 대기 상태 값들은 프로그래밍 및 소거 조건에 대한 값들과 유사하다. WL(302) 및 BL(304)은 판독을 위해 선택된 메모리 셀들에 대해 판독 시의 바이어스 레벨, 예컨대 2.6 V 및 1.0 V로 각각 전환된다. 비선택된 WL들은 (비선택된 로우들 상에서의 누설을 감소시키기 위해) 0 볼트 또는 네거티브 전압 레벨, 예컨대 -0.5 V에서 바이어싱될 수 있다. 비선택된 SL들은 (비선택된 로우들 상에서의 누설을 감소시키기 위해) 0 볼트 또는 포지티브 전압 레벨, 예컨대 0.1 내지 0.7 V에서 바이어싱될 수 있다. 비선택된 BL들은 0 볼트에서 바이어싱될 수 있거나, 또는 대안으로, 플로팅될 수 있는데, 이는 어떠한 전압도 인가되지 않음(판독 시에 BL-BL 커패시턴스를 효과적으로 감소시킴)을 의미할 수 있다.

도 6을 참조하면, 약한 프로그래밍 셀들을 검출하기 위해 전체 어레이를 프로그래밍한 이후, 마진0 판독(Read Margin0) 동작이 수행된다. 프로그래밍 이후, 셀 전류는, 보통 나노 암페어(nA) 미만인 매우 낮은 값에 있고, 이는 '0' 디지털 값(셀 전류가 없음)의 판독에 해당한다. 그러나, 일부 셀들은 (셀 누설, 약한 셀 프로그래밍 커플링 비(weak cell programming coupling ratio), 프로세스 기하학적 효과 등과 같은 다양한 원인들로 인한 약한 프로그래밍으로 인하여) 미미하게 수 마이크로 암페어에 머무를 수 있고, 이는 메모리 디바이스(10)의 동작 수명 동안 '0'의 판독이 실패하게 되는 원인일 수 있다. 마진0 판독은 그들 약한 셀들을 스크린아웃(screen out)하는 데 사용된다. 마진0 판독 파형에 대해, SL(308)은 대기 상태 값, 예컨대 0 V에 있다. WL(302) 및 BL(304)은 정상 판독 조건에서와 같이 판독을 위한 선택된 메모리 셀들에 대해 판독 시의 바이어스 레벨, 예컨대 2.6 V 및 1.0 V로 각각 전환된다. CG(306)는 약하게 프로그래밍된 셀들을 검출하기 위해 판독 시의 마진0 값, 예컨대 3 V로 바이어싱된다. CG 전압은 약한 프로그래밍 효과를 증폭하고, 셀 전류를 효과적으로 증가시켜서 약한 셀들이 이제 '0'이 아니라 '1'로 판독되도록(사실상, 셀 전류가 없는 것이 아니라 셀 전류가 존재하도록) 하기 위해 FG 전위로 커플링될 것이다.

약하게 소거된 셀들을 검출하기 위해 전체 어레이를 소거한 이후 마진1 판독(Read Margin1) 동작이 수행된다. 네거티브 CG가 이제 이러한 조건을 검출하는 데 활용된다. SL(308)은 대기 상태 값, 예컨대 0 V에 있다. WL(302) 및 BL(304)은 정상 판독 조건에서와 같이 판독을 위한 선택된 메모리 셀들에 대해 판독 시의 바이어스 레벨, 예컨대 2.6 V 및 1.0 V로 각각 전환된다. CG(306)는 약하게 소거된 셀들을 검출하기 위해 판독 시의 마진1 값, 예컨대 -3 V 내지 -5 V로 바이어싱된다. CG 전압은 약하게 소거된 결과를 증폭하고, 셀 전류(더 적은 FG 전위)를 효과적으로 감소시켜서, 약하게 소거된 셀들이 이제 '1'이 아니라 '0'으로 판독되도록(사실상, 셀 전류가 있는 것이 아니라 셀 전류가 없도록) 하기 위해 FG 전위로 네거티브로 커플링될 것이다.

도 7a를 참조하면, 메모리 셀(10)에 대한 디바이스 단면의 일 실시예가 도시되어 있다. 메모리 셀(10)에 대한 디바이스 단면의 대안의 실시예가 고전압 P-웰(710) 및 깊은 N-웰(720)이 없이 P 기판(730) 내에 있다. 소스 영역(14), 비트 라인 영역(16), 채널 영역(18), 및 기판 영역(12)을 갖는 메모리 셀(10)이 영역 고전압(HV) P-웰(710) 내부에 있는 것으로 도시되어 있다(메모리 셀(10)의 다른 영역들 또는 단자들은 도시되어 있지 않다). 영역 P-웰(710)은 깊은 N-웰(DNW) 영역(720) 내부에 있다. 깊은 N-웰 영역(720)은 P 기판(730) 내부에 있다. 전형적으로 0 V 또는 Vdd에 접속된 DNW 영역(720)의 분리 특징부로 인해, HV P-웰(710)은 네거티브로 바이어싱되어, 예컨대 소거 또는 프로그래밍 시에 메모리 셀들의 전기적 성능을 향상시킬 수 있다.

도 7의 디바이스 단면은, 또한, 메모리 셀(10)의 영역(16, 14, 18)을 각각 대체하는 고전압 NMOS 소스, 드레인, 및 채널을 갖는 깊은 N-웰 내의 고전압 NMOS 트랜지스터에 적용가능하다. 깊은 N-웰(720)은 유사하게 전압 분리 영역으로서의 역할을 하여, 고전압 NMOS가 네거티브 전압 동작에서 적용될 수 있게 한다. 실시예들은, DNW 내의 HV NMOS의 트랜지스터 단자들 및 접합부들에 걸쳐서 응력 감소를 보장하도록 행해진다.

도 7b를 참조하면, 메모리 셀(10)의 기호 표현(740)이 도시되어 있는데, 깊은 N-웰(720)은 "DNW"로 도시되어 있고 HV P-웰(710)은 "P-웰"로 도시되어 있다. 도 7b에는, 깊은 N-웰(720) 내부의 HV P-웰(710) 내의 NMOS에 대한 트랜지스터 기호(750)가 도시되어 있다.

도 8을 참조하면, 레벨 시프터의 제1 실시예로서, 도 2의 로직(270), 네거티브 전압 드라이버 회로(230), 고전압 드라이버 회로(225), 및/또는 고전압 드라이버 회로(226)에 포함될 수 있는 네거티브 고전압 레벨 시프터(800)가 도시되어 있다.

네거티브 고전압 레벨 시프터(800)는 입력 IN을 수신하고, 출력 VNBN을 생성한다. 네거티브 고전압 레벨 시프터(800)는 트랜지스터(820) 및 트랜지스터(830)의 깊은 N-웰 DNWB(804)를 구동하여, 트랜지스터(820) 및 트랜지스터(830)의 층들 사이에서의 항복(breakdown)의 발생을 최소화한다. DNW 제어 회로(835)는 입력 IN2(802)를 수신하여 출력 DNWB(804) 레벨을 적절하게 생성하여, 트랜지스터들(820, 830)에 대한 전압 응력을 감소시킨다. 인버터(805)는 입력 IN을 수신하여 인버터 출력 INB를 생성하는데, 이러한 인버터 출력 INB는 인버터(810) 및 PMOS 트랜지스터(825)의 게이트 내로의 입력이다. 인버터(810)의 출력은 PMOS 트랜지스터(815)의 게이트에 커플링된다. PMOS 트랜지스터들(815, 825)은, 도시된 바와 같이, NMOS 트랜지스터들(820, 830)에 커플링된다. 출력 VOUT(808)은 VHVNEG(806) 내지 Vdd(이러한 예에서는, 각각 -8 V 및 2 V임) 사이에서 변화할 수 있다. DNWB 레벨은, 예를 들어 0 V 내지 Vdd(예컨대, 2.5 V)일 수 있고, 그것은 VHVNEG가 -8 V인 경우에는 0 V이다. 이는 트랜지스터들(820, 830)의 DNWB와 HV P-웰과 소스/드레인 사이에서의 전압 응력을 (8 V + 2.5 V = 10.5 V가 아니라) 8 V로 최소화한다. 대안으로, DNWB 레벨은 VHVNEG가 -8 V일 때 (P 기판-DNW 접합부의 포워딩 없이) -0.5 V로 구동되어, 전압 응력을 더욱 최소화할 수 있다. 다른 때, 예컨대 VHVNEG가 0 볼트 또는 작은 네거티브 전압에 있을 때, DNW 제어 회로(835)는 DNWB를 포지티브, 예컨대 Vdd 레벨로 구동하여, 잡음 또는 래치-업을 최소화할 수 있다(P 기판을 깊은 N-웰 접합부로 포워딩하는 것을 방지한다). DNWB를 구동하기 위한 이러한 기법은 기술되는 모든 실시예들에 대해 적용가능하다.

도 9를 참조하면, 레벨 시프터의 제2 실시예로서, 도 2의 로직(270), 네거티브 전압 드라이버 회로(230), 고전압 드라이버 회로(225), 및/또는 고전압 드라이버 회로(226)에 포함될 수 있는 네거티브 고전압 레벨 시프터(900)가 도시되어 있다. 네거티브 고전압 레벨 시프터(900)는 네거티브 고전압 레벨 시프터(800)와 동일한 컴포넌트들을 포함하며, 도시된 바와 같이, 캐스코딩(cascoding) PMOS 트랜지스터들(935, 945) 및 캐스코딩 NMOS 트랜지스터들(940, 950)이 추가된다. 네거티브 고전압 레벨 시프터(900)는 입력 IN을 수신하고, 출력 OUT(908)을 생성한다. 출력 OUT(908)은 VHVNEG(906) 내지 Vdd(이러한 예에서는, 각각 -8 V 및 2 V임) 사이에서 변화한다. DNWB 신호(904)는 네거티브 고전압 레벨 시프터 회로(800)의 것과 유사하게 구동되어 전압 응력을 최소화하게 한다. PMOS 트랜지스터들(935, 945)의 게이트들이 접지(= Vdd가 아니라 = 0 V)에 접속되어, 게이트-소스/드레인 단자들에 걸쳐서 전압 응력을 최소화하게 한다. NMOS 트랜지스터들(940, 950)의 게이트들은 VNBN(960)(= Vdd 내지 중간 네거티브 레벨, 예컨대 -3 V 사이)에 접속되어, 게이트-소스/드레인(예컨대, 8 + Vdd = 10.5 V가 아니라 8 V - 3 V = 5 V) 및 소스-드레인(예컨대, 8 + Vdd = 10.5 V가 아니라 8 V - 3 V - Vt = ~4 V, Vt = NMOS 임계 전압)에 걸쳐서 전압 응력을 최소화하게 한다.

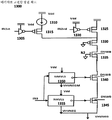

도 10을 참조하면, 레벨 시프터의 제3 실시예로서, 도 2의 로직(270), 네거티브 전압 드라이버 회로(230), 고전압 드라이버 회로(225), 및/또는 고전압 드라이버 회로(226)에 포함될 수 있는 네거티브 고전압 레벨 시프터(1000)가 도시되어 있다. 네거티브 고전압 레벨 시프터(1000)는 네거티브 고전압 레벨 시프터(900)와 동일한 컴포넌트들을 포함하며, PMOS 트랜지스터들(1075, 1085) 및 NMOS 트랜지스터들(1080, 1090)로 이루어진 중간(중위) 네거티브 레벨 시프터(1002)가 추가된다. 중간 네거티브 레벨 VHVNEGM, 예컨대 -3 V를 갖는 중간 네거티브 레벨 시프터(1002)와, PMOS 트랜지스터들의 게이트들의 VNBP(1065) 및 NMOS 트랜지스터들의 게이트들에 대한 VNBN 추가적인 중간 네거티브 바이어스 레벨의 도입은 네거티브 (고)레벨 시프터 내의 PMOS 및 NMOS 트랜지스터들의 단자들에 걸친 전압 응력을 감소시키기 위한 것이다. 네거티브 고전압 레벨 시프터(1000)는 입력 IN을 수신하고, 출력 OUT(1008)을 생성한다. 출력 OUT(1008)은, 이러한 예에서는, 각각 -8 V와 0 V와 2 V인 VHVNEG(1006)와 GND와 Vdd 사이에서 변화한다. 출력 OUT(1008)은 VHVNEG(1006) 내지 GND(= VDDSWX(1012))(이러한 예에서는, VHVNEG(1006)가 최대 네거티브 고전압 -8 V에 있을 때 각각 -8 V 및 0 V임) 사이에서 변화한다. VHVNEGM은 -3 V의 네거티브 전력 서플라이를 포함할 수 있다. 중간 네거티브 레벨 시프터(1002)의 출력 OUTM(1086) 및 OUTM_N(1076)은 VHVNEGM 내지 Vdd(이러한 예에서는, 각각 -3 V 및 2 V임) 사이에서 변화한다. VDDSWX(1012)는 2 V와 0 V 사이에서 전환되는 전환형 서플라이일 수 있다. VDDSWX(Vdd 고전압 서플라이)(1012)는 초기에 Vdd, 예컨대 2 V이며, VHVNEG(1006)가 최대 네거티브 전압의 대략 절반, 예컨대 -4 V에 또는 최대 네거티브 전압, 예컨대 -8 V에 있을 때 0 V로 전환된다. VNBP(1065)는 0 V와 -3 V 사이에서 전환될 수 있다. VDDSWX(1012)가 0 V에 있고 VNBP(1065)가 -3 V에 있을 때, 출력 OUTM_N(1076)은 -3 V(= VHVNEGM)에 있어서, 0 V를 출력 OUT(1008)으로 전달한다. 전압 VNBP(1065)가 중간 네거티브 전압 -3 V에 있으므로, 트랜지스터들(1035, 1045)의 게이트-소스/드레인에 걸친 전압 응력은 감소된다. 전압 VNBN(1060)이 중간 네거티브 전압 -3 V에 있으므로, 트랜지스터들(1040, 1050)의 게이트-소스/드레인에 걸친 전압 응력은 감소되고, 트랜지스터들(1020, 1030)의 소스-드레인에 걸친 전압 응력은 감소된다. 전압 OUT(1008)이 (= Vdd가 아니라) 0 V에 있으므로, 트랜지스터들(1020, 1030)의 게이트-소스/드레인에 걸친 전압 응력은 감소되고, 트랜지스터들(1040, 1050)의 소스-드레인에 걸친 전압 응력은 감소된다. 캐스코딩 PMOS 트랜지스터들(1035, 1045)은 그의 벌크(N-웰)가 그의 소스에 접속되어, 벌크와 드레인/소스 사이에서의 전압 응력을 감소하게 한다. 캐스코딩 NMOS 트랜지스터들(1040, 1050)은 그의 벌크(P-웰)가 그의 소스에 접속되어, 벌크와 드레인/소스 사이에서의 전압 응력을 감소하게 한다.

도 11을 참조하면, 전압 서플라이 회로(1100)가 도시되어 있다. 전압 서플라이 회로(1100)는 제1 네거티브 전압 레벨 시프터 회로(1105) 및 제2 네거티브 전압 레벨 시프터 회로(1110)를 포함하는데, 각각의 회로는 네거티브 고전압 레벨 시프터들(800, 900, 1000) 중 하나를 포함할 수 있다. 이러한 실시예에서, 제1 네거티브 전압 레벨 시프터 회로(1105) 및 제2 네거티브 전압 레벨 시프터 회로(1110)는 함께 네거티브 고전압 레벨 시프터(1000)를 포함하고 입력 IN을 수신하며, 이러한 예에서 2 V 내지 -3 V의 범위에 있는 중간(중위) 네거티브 전압 VHVNEGM, 및 이러한 예에서 0 V 내지 -8 V의 범위에 있는 네거티브 고전압 VHVNEG를 생성한다. 제1 네거티브 전압 레벨 시프터 회로(1105) 및 제2 네거티브 전압 레벨 시프터 회로(1110)는, 도시된 바와 같이, NMOS 트랜지스터(1115)(캐스코딩 트랜지스터) 및 NMOS 트랜지스터(1120)에 커플링된다. DNWB는 Vdd 또는 0 V의 값들을 수신하고, VPNext_pin(1101)이 2 V 또는 -8 V의 전압을 수신한다. 회로(1100)가 인에이블되는 경우에, 회로(1105, 1110)의 출력은, 예를 들어 2 V와 동일한데, 이는 NMOS 트랜지스터들(1115, 1120)을 인에이블시켜서 VPNext_pin(1101) 레벨을 VHVNEG(1106)로 전달한다. 회로(1100)가 디스에이블되는 경우에, 회로(1105, 1110)의 출력은, 예를 들어 각각 -3 V 및 -8 V인데, 이들은 NMOS 트랜지스터들(1115, 1120)을 디스에이블시킨다.

도 12를 참조하면, 전압 서플라이 회로(1200)가 도시되어 있다. 전압 서플라이 회로(1100)는 네거티브 전압 레벨 시프터 회로들(1225, 1240)을 포함하는데, 각각의 회로는 네거티브 고전압 레벨 시프터들(800, 900, 1000) 중 하나를 포함한다. 전압 서플라이 회로(1200)는, "오프(off)" 상태에서 0 V이고 "on" 상태에서 2 V인 인에이블 신호 EN_TXN을 수신하며, 이러한 예에서 0 V 내지 -8 V의 범위에 있는 네거티브 고전압 VHVNEG를 생성한다. VNEG_3V는 2 V 또는 -3 V이다. 네거티브 전하 펌프(1230, 1235) 각각은 -8 V의 입력을 -12 V의 출력으로 펌핑한다. 회로(1200)가 인에이블되는 경우에, 회로들(1230, 1235)의 출력들은, 예를 들어 -12 V에 있고, 따라서, PMOS 트랜지스터들(1215, 1220)을 인에이블시켜서 VPNext_pin 레벨로부터의 전압을 VHVNEG(1206)로 전달한다. 회로(1200)가 디스에이블되는 경우에, 회로들(1230, 1235)의 출력들은, 예를 들어 각각 2 V 및 0 V에 있고, 따라서, PMOS 트랜지스터들(1215, 1220)을 디스에이블시킨다. PMOS 트랜지스터들(1210, 1245)은 캐스코딩 트랜지스터들로서의 역할을 하여 트랜지스터들(1205, 1250)에 대한 전압 응력을 각각 감소시킨다.

도 13을 참조하면, 네거티브 고전압 방전 회로(1300)가 도시되어 있다. 입력들 IN3, IN1st 및 IN2nd가 상태를 인에이블로 변화시키고, 트랜지스터들(1315, 1325)이 인에이블되고, 회로(1350, 1355)의 출력들이 예를 들어 Vdd(2 V)와 동일한 경우에, VHVNEG는 -8 V로부터 N2를 지나서 약 -0.7 V로 방전된다. NMOS 트랜지스터들(1340, 1345)(캐스코딩 트랜지스터)의 게이트들은, 예를 들어 오프 상태(회로(1350, 1355)가 디스에이블되어 있음)에서 -3 V 및 -8 V와 동일하여 네거티브 레벨 VHVNEG를 NMOS 트랜지스터(1335)로부터 분리시킨다. 방전 전류는 초기에 전류 바이어스(1310)(입력 IN1st에 의해 인에이블됨)에 의해 제어되고, 이어서 트랜지스터(1325)(입력 IN2nd에 의해 인에이블됨)에 의해 제어된다.

도 14를 참조하면, 네거티브 고전압 방전 회로(1400)가 도시되어 있다. 입력들 IN1st 및 IN2nd가 상태를 인에이블로 변화시키는 경우에, VHVNEG가 -8 V로부터 중간 네거티브 전압 레벨로 방전되는데, 이러한 레벨은 다이오드 접속된 NMOS 트랜지스터들(1455, 1460)의 Vt(임계 전압)의 수치에 의해 결정된다. 방전 전류는 초기에 전류 바이어스(1435)(입력 IN1st에 의해 인에이블됨)에 의해 제어되고, 이어서 트랜지스터(1445)(입력 IN2nd에 의해 인에이블됨)에 의해 제어된다. 이어서, VHVNEG가 중간 네거티브 레벨로부터 N1 트랜지스터(1415) 및 N2 트랜지스터(1420)를 지나서 약 0.0 V로 빠르게 방전된다. NMOS 트랜지스터들(1415, 1420)(캐스코딩 트랜지스터)의 게이트들은 중간 네거티브 레벨 시프터(1405) 및 네거티브 고레벨 시프터(1410)에 의해 각각 제어된다.

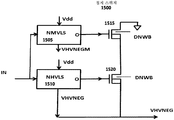

도 15를 참조하면, 접지 스위치 회로(1500)가 도시되어 있다. 접지 스위치 회로(1500)는 네거티브 고전압 회로(1505), 네거티브 고전압 회로(1510), NMOS 트랜지스터(1515), 및 NMOS 트랜지스터(1520)를 포함한다. 접지 스위치 회로(1500)는 입력 신호 IN을 수신하고, 출력 신호 VHVNEG를 생성한다.

도 16을 참조하면, 디코더 회로(1600)가 도시되어 있다. 디코더 회로(1600)는 도 2의 로직(270), 네거티브 전압 드라이버 회로(230), 고전압 드라이버 회로(225), 및/또는 고전압 드라이버 회로(226) 내에 포함될 수 있다. 디코더 회로(1600)는 고전압 레벨 시프터(1605), 네거티브 고전압 레벨 시프터(1610), 고전압 결정기 인에이블 회로(1615), 소거 게이트 디코더(1620), 제어 게이트 디코더(1625), 및 소스 라인 디코더(1630)를 포함한다. 고전압 인에이블 회로(1615)는 고전압 레벨 시프터(1605)로부터의 고전압 및/또는 네거티브 고전압 레벨 시프터(1610)로부터의 네거티브 고전압을 소거 게이트 디코더(1620), 커플링 게이트 디코더(1625), 및/또는 소스 라인 디코더(1630)에 인가하는 데 사용된다.

도 17을 참조하면, 제어 게이트 디코더(1625)에 대한 일 실시예(1700)가 도시되어 있다. 제어 게이트 디코더(1700)는, PMOS 트랜지스터(1705)에 의해 제어되는 전류에 의한 판독 동작 동안에 바이어스 전압 VCGSUPR을 제어 게이트에 제공하는 PMOS 트랜지스터들(1705, 1710), 네거티브 고전압에 대한 분리를 제공하는 PMOS 트랜지스터(1725), PMOS 트랜지스터들을 통해 프로그래밍 시에 포지티브 고전압을 제공하는 PMOS 트랜지스터들(1715, 1720), 제어 게이트에 대한 프로그래밍 시에 금지 전압을 제공할 수 있는 NMOS 트랜지스터들(1730, 1735, 1740, 1745), 및 NMOS 트랜지스터(1730)와 함께, 제어 게이트에 대한 소거 시에 네거티브 고전압을 제공할 수 있는 NMOS 트랜지스터(1750, 1755)를 포함한다. NMOS 트랜지스터(1755)는 제어 게이트들에 대한 네거티브 전압 서플라이에 대한 전류 제어부로서의 역할을 한다. NMOS 트랜지스터(1750)는 소거 시에 로컬 디코딩된 섹터 인에이블링 라인 SECHV_EN에 의해 인에이블된 네거티브 전압 레벨 시프터에 의해 인에이블된다. 도시된 바와 같이, 회로(1700)는 4개의 제어 게이트 CG[3:0], 하나의 소거 게이트 EG, 및 하나의 소스 라인 SL에 대한 디코딩을 제공한다. 게이트들이 4개의 포괄적 사전디코딩된 CG 라인들 CGPH_HV_N[3:0]에 의해 인에이블되는 4개의 PMOS 트랜지스터들(1715)이 있다. 게이트들이 로컬 디코딩된 섹터 인에이블링 라인 SECHV_EN에 의해 인에이블되는 4개의 PMOS 트랜지스터들(1710)이 있다. 게이트들이 접지 라인에 의해 인에이블되는 4개의 분리 PMOS 트랜지스터들(1725)이 있다. 게이트들이 4개의 포괄적(global) 사전디코딩된 CG 라인들 CGNH_HV_N[3:0]에 의해 인에이블되는 4개의 NMOS 트랜지스터들(1730)이 있다. PMOS 트랜지스터(1720)는 로컬 디코딩된 섹터 인에이블링 라인 SECHV_EN_N에 의해 인에이블되어, 포지티브 고전압 VCGSUP를 제어 게이트들로 전달한다. NMOS 트랜지스터들(1735, 1740)은 CG_LOW_BIAS(예컨대, 프로그래밍 시의 금지 전압)를 전달하거나 또는 분리 전압의 역할을 하기 위해 포괄적 제어 신호 CGN_ISO1 및 CGN_ISO2, 예컨대 각각 -8 V 및 -3 V에 의해 각각 인에이블된다. NMOS 트랜지스터(1745)는 로컬 디코딩된 섹터 인에이블링 라인 SECHV_EN에 의해 인에이블되어, CG_LOW_BIAS 레벨을 제어 게이트로 전달한다. DNWB(1704)는 VHVNEG가 네거티브 전압, 예컨대 -8 V에 있을 때 0 V가 되도록 제어된다. 도시된 바와 같이, CG 디코더(1700)에서 포지티브 CG 디코딩 기능에 필요한 캐스코딩 트랜지스터는 없다. 대안으로, 네거티브 CG 디코딩을 위해, 캐스코딩 NMOS 트랜지스터(1740)는 선택적이다. 대안으로, 네거티브 CG 디코딩을 위한 전류 제어형 NMOS 트랜지스터(1755)는 선택적이다.

도 18을 참조하면, 소거 게이트 디코더(1620)에 대한 일 실시예(1800)가 도시되어 있다. 소거 게이트 디코더(1800)는 PMOS 트랜지스터들(1805, 1810) 및 NMOS 트랜지스터(1815)를 포함한다. PMOS 트랜지스터(1810)는 전압 또는 고전압 VEGSUP를 소거 게이트로 전달하기 위한 전류 제어형이다. PMOS 트랜지스터(1805)는 로컬 디코딩된 섹터 인에이블링 라인 EN_HV_N에 의해 인에이블되어, 전압 VEGSUP 레벨을 소거 게이트에 전달한다. NMOS 트랜지스터(1815)는 전압 EG_LOW_BIAS 레벨, 예컨대 0 V 내지 2.6 V를 소거 게이트에 전달하는 데 사용된다. 디코딩된 소거 게이트는 메모리 셀들의 다수의 로우들에 걸쳐서 공유된다. 도시된 바와 같이, EG 디코더(1620)에 필요한 캐스코딩 트랜지스터는 없다. 대안으로, 캐스코딩 트랜지스터 PMOS 및 NMOS가 EG 디코더(1629)에 대해 구현될 수 있다.

도 19를 참조하면, 소스 라인 디코더(1630)에 대한 일 실시예(1900)가 도시되어 있다. 소스 라인 디코더(1900)는 NMOS 트랜지스터들(1905, 1910, 1915, 1920)을 포함한다. 소스 라인 디코더(1900)는 약 0.5 V의 값에 있는 바이어스 전압 SLP_LOW_BIAS를 비선택된 셀에 대한 소스 라인에 제공한다. 이러한 바이어스 전압을 인가하는 것은 비선택된 메모리 셀들에 대한 누설을 방지한다. NMOS 트랜지스터(1915)는 프로그래밍 시에 VSLSUP 레벨을 소스 라인으로 전달하는 데 사용된다. 디코딩된 소스 라인은 메모리 셀들의 다수의 로우들에 걸쳐서 공유된다. NMOS 트랜지스터(1920)는 프로그래밍 시에 소스 라인으로부터의 VSLMON 레벨을 모니터링하는 데 사용된다. NMOS 트랜지스터(1905)는 판독 시에 SLRD_LOW_BIAS 레벨, 예컨대 0 V를 소스 라인으로 전달하는 데 사용된다.

도 20을 참조하면, 고전압 네거티브 전하 펌프 회로(2000)가 도시되어 있다. 고전압 네거티브 전하 펌프 회로(2000)는 네거티브 펌핑된 출력에 커플링된 PMOS 트랜지스터(2005) 및 PMOS 트랜지스터(2010), 포지티브 펌핑된 출력에 커플링된 NMOS 트랜지스터(2015) 및 NMOS 트랜지스터(2020), 및 펌프 스테이지 회로들(2025, 2030, 2035, 2040)을 포함한다. 고전압 네거티브 전하 펌프 회로(2000)는 네거티브 고전압 VHV_NEG, 및 포지티브 고전압 VHV_POS를 제공하는데, 펌프 스테이지 회로들(2025, 2030, 2035, 2045) 각각은 전압을 수신하고 더 높은 포지티브 고전압 또는 네거티브 고전압을 출력한다. 각각의 스테이지의 패스(pass) NMOS 트랜지스터의 벌크(P-웰)는, 도시된 바와 같이, 이전 스테이지의 출력에 커플링된다. NMOS 트랜지스터들의 DNWB는 네거티브 전압 펌핑 시에 0 V에서, 포지티브 전압 펌핑 시에 HV에서, 그리고 선택적으로, 다른 때에는 Vdd에서 바이어싱된다.

도 22a, 도 22b, 및 도 22c를 참조하면, PMOS 트랜지스터(2205), 커패시터(2210), 및 NMOS 트랜지스터(2215)의 사용을 포함하여 전하 펌프 회로(2000)에서 사용될 수 있는 커패시터들의 예들이 도시되어 있다.

도 21을 참조하면, 네거티브 고전압 레벨 시프터(2100)가 도시되어 있다. 네거티브 고전압 레벨 시프터(2100)의 컴포넌트들은 도 10에 도시된 네거티브 고전압 레벨 시프터(1000)의 것들과 동일한데, 차이는, 특정 트랜지스터가 오프 상태일 때 0 V에서 도 21에서 HV N-웰(PMOS 트랜지스터의 벌크)이 입력 인버터들에 의해 구동되어, 트랜지스터 내의 접합 항복을 최소화한다는 것이다.

도 23을 참조하면, 네거티브 고전압 레벨 시프터(2300)가 도시되어 있다. 네거티브 고전압 레벨 시프터(2300)는 입력 IN을 수신하고, 출력 OUT을 생성한다. OUT은 이러한 예에서 -8 V 또는 2 V이다. DNWB는 Vdd 또는 0 V에 의해 구동된다. 이러한 회로에서, 레벨 시프터의 각각의 레그(leg)에는 2개의 PMOS가 직렬로 존재하지만 NMOS는 단 하나만이 존재한다.

도 24를 참조하면, NMOS 패스 게이트만이 있는 멀티플렉싱 회로(2400)가 도시되어 있다.

도 25를 참조하면, 네거티브 고전압 레벨 시프터(2500)가 도시되어 있다. 네거티브 고전압 레벨 시프터(2100)의 컴포넌트들은 도 9에 도시된 네거티브 고전압 레벨 시프터(900)의 것들과 동일한데, 차이는, 캐스코딩 목적을 위한 PMOS 및 NMOS 트랜지스터들이 그 자신의 개별 벌크를 갖는다는 것이다.

판독, 소거 및 프로그래밍의 동작들 동안에 네거티브 전압을 비선택된 또는 선택된 메모리 셀들(10)의 워드 라인(22) 또는 커플링 게이트(26)에 인가하는 것의 이점은 메모리 셀이 더욱 효과적으로 스케일을 낮추도록 허용하는 것이다. 소거 동안, 선택된 메모리 셀들의 워드 라인 상의 네거티브 전압은 전체적인 소거 전압이 낮아지는 것을 허용하여 따라서 셀의 치수가 더 작아지도록 허용한다(다양한 셀간(inter-cell) 또는 층간(inter-layer) 치수인 수평 또는 수직 간격, 분리, 폭, 길이 등에 걸쳐서 더 낮은 전압을 유지함). 프로그래밍 동안, 비선택된 메모리 셀들의 워드 라인 상의 네거티브 전압은 비선택된 메모리 셀들에 대한 누설을 감소시켜서 (동일 섹터 내의 비선택된 셀들에 대해) 더 적은 교란, 더 정확한 프로그래밍 전류(선택된 셀들에 대해, 더 적은 누설 간섭), 및 더 적은 전력 소비로 이어진다. 판독의 경우에, 비선택된 메모리 셀들의 워드 라인 상의 네거티브 전압은 누설로부터의 더 적은 간섭으로 인해 더욱 정확한 감지로 이어진다. 메모리 어레이 동작에서 사용하기 위해 네거티브 워드 라인, 네거티브 커플링 게이트 및 네거티브 P 기판을 조합하면, 낮아진 소거/프로그래밍 전압들 및 전류, 더욱 효과적인 소거 및 프로그래밍, 더 적은 셀 교란, 더 적은 셀 누설의 결과를 가져온다는 것이 또한 유리하다.

Claims (44)

- 비휘발성 메모리 디바이스로서,

제1 전도성 타입의 반도체 기판;

상기 반도체 기판에서 복수의 로우(row)들 및 컬럼(column)들로 배열된 비휘발성 메모리 셀들의 어레이;

제1 네거티브 전압을 생성하기 위한 전하 펌프 회로; 및

커맨드 신호를 수신하고, 복수의 제어 신호들을 생성하여 상기 복수의 메모리 셀들의 커플링 게이트에 대한 상기 제1 네거티브 전압의 인가를 제어하기 위한 제어 회로를 포함하고,

각각의 메모리 셀은,

상기 반도체 기판의 표면 상의 제2 전도성 타입의 제1 영역,

상기 반도체 기판의 상기 표면 상의 상기 제2 전도성 타입의 제2 영역,

상기 제1 영역과 상기 제2 영역 사이의 채널 영역,

상기 채널 영역의 제1 부분 위에 놓여 있으면서 그로부터 절연되고, 상기 제1 영역에 인접하면서 상기 제1 영역과 거의 또는 전혀 중첩되지 않는 워드 라인,

상기 제1 부분에 인접한 상기 채널 영역의 제2 부분 위에 놓여 있으면서, 그로부터 절연되고, 상기 제2 영역에 인접한 플로팅 게이트,

상기 플로팅 게이트 위에 놓인 커플링 게이트, 및

상기 제1 영역에 접속된 비트 라인을 포함하는, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

상기 복수의 제어 신호들은 소거 커맨드에 응답하여 생성되는, 비휘발성 메모리 디바이스. - 청구항 2에 있어서,

상기 제1 네거티브 전압은 -5 내지 -9 볼트인, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

상기 제어 회로는 네거티브 고전압 레벨 시프터 회로를 포함하는, 비휘발성 메모리 디바이스. - 청구항 4에 있어서,

상기 제어 회로는 네거티브 중간 전압 레벨 시프터 회로를 포함하는, 비휘발성 메모리 디바이스. - 청구항 4에 있어서,

상기 네거티브 고전압 레벨 시프터 회로는 상기 제1 네거티브 전압을 생성하는, 비휘발성 메모리 디바이스. - 청구항 5에 있어서,

상기 네거티브 중간 전압 레벨 시프터 회로는 제2 네거티브 전압을 생성하는, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

상기 제어 회로는 커플링 게이트 디코더 회로를 포함하는, 비휘발성 메모리 디바이스. - 청구항 8에 있어서,

상기 커플링 게이트 디코더 회로는 하나 이상의 전류 리미터 회로를 포함하는, 비휘발성 메모리 디바이스. - 청구항 8에 있어서,

상기 커플링 게이트 디코더 회로는 비선택된 메모리 셀의 커플링 게이트에 바이어스 전압을 제공하는, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

각각의 메모리 셀은 분리형 게이트 플래시 메모리 셀인, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

각각의 메모리 셀은 깊은 N-웰 내부의 P-웰 내에 위치되는, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

상기 제1 네거티브 전압을 방전하기 위한 방전 회로를 추가로 포함하는, 비휘발성 메모리 디바이스. - 청구항 1에 있어서,

상기 전하 펌프 회로는 복수의 펌프 스테이지들을 포함하고, 적어도 하나의 펌프 스테이지의 벌크는 다른 펌프 스테이지의 출력에 커플링되는, 비휘발성 메모리 디바이스. - 청구항 14에 있어서,

상기 전하 펌프는 네거티브 전압 또는 포지티브 전압을 생성하도록 구성될 수 있는, 비휘발성 메모리 디바이스. - 청구항 15에 있어서,

트랜지스터의 깊은 N-웰은, 상기 전하 펌프가 네거티브 전압을 생성하는 데 사용되는 경우에 0 볼트이고, 상기 전하 펌프가 포지티브 전압을 생성하는 데 사용되는 경우에 포지티브 전압인, 비휘발성 메모리 디바이스. - 소정 타입의 비휘발성 메모리 디바이스를 동작시키는 방법으로서,

상기 비휘발성 메모리 디바이스는,

제1 전도성 타입의 반도체 기판; 및 상기 반도체 기판에서 복수의 로우들 및 컬럼들로 배열된 비휘발성 메모리 셀들의 어레이 - 각각의 메모리 셀은, 상기 반도체 기판의 표면 상의 제2 전도성 타입의 제1 영역, 상기 반도체 기판의 상기 표면 상의 상기 제2 전도성 타입의 제2 영역, 상기 제1 영역과 상기 제2 영역 사이의 채널 영역, 상기 채널 영역의 제1 부분 위에 놓여 있으면서 그로부터 절연되고, 상기 제1 영역에 인접하면서 상기 제1 영역과 거의 또는 전혀 중첩되지 않는 워드 라인, 상기 제1 부분에 인접하는 상기 채널 영역의 제2 부분 위에 놓여 있으면서, 그로부터 절연되고, 상기 제2 영역에 인접한 플로팅 게이트, 상기 플로팅 게이트 위에 놓인 커플링 게이트, 및 상기 제1 영역에 접속된 비트 라인을 가짐 - 를 갖고, 상기 방법은,

제1 네거티브 전압을 복수의 메모리 셀들 각각의 커플링 게이트에 인가하는 단계; 및

비네거티브 전압(non-negative voltage)을 상기 복수의 메모리 셀들 각각의 워드 라인, 비트 라인, 및 제2 영역에 인가하는 단계를 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

상기 방법은 선택된 메모리 셀을 소거하기 위한 것인, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 18에 있어서,

상기 제1 네거티브 전압은 -5 내지 -9 볼트인, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

상기 메모리 디바이스는 네거티브 고전압 레벨 시프터 회로를 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 20에 있어서,

상기 제어 회로는 네거티브 중간 전압 레벨 시프터 회로를 포함하는, 방법. - 청구항 20에 있어서,

상기 네거티브 고전압 레벨 시프터 회로는 상기 제1 네거티브 전압을 생성하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 21에 있어서,

상기 네거티브 중간 전압 레벨 시프터 회로는 제2 네거티브 전압을 생성하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

상기 메모리 디바이스는 커플링 게이트 디코더 회로를 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 24에 있어서,

상기 커플링 게이트 디코더 회로는 하나 이상의 전류 리미터 회로를 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 24에 있어서,

상기 커플링 게이트 디코더 회로는 비선택된 메모리 셀들의 커플링 게이트들에 바이어스 전압을 제공하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

각각의 메모리 셀은 분리형 게이트 플래시 메모리 셀인, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

방전 회로를 사용하여 상기 제1 네거티브 전압을 방전하는 단계를 추가로 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 17에 있어서,

상기 전하 펌프 회로가 복수의 펌프 스테이지들을 포함하고, 적어도 하나의 펌프 스테이지의 벌크는 다른 펌프 스테이지의 출력에 커플링되는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 29에 있어서,

상기 전하 펌프는 네거티브 전압 또는 포지티브 전압을 생성하도록 구성될 수 있는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 30에 있어서,

트랜지스터의 깊은 N-웰에 0 볼트를 인가하여 네거티브 전압을 생성하는 단계를 추가로 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 청구항 30에 있어서,

트랜지스터의 깊은 N-웰에 포지티브 전압을 인가하여 포지티브 전압을 생성하는 단계를 추가로 포함하는, 비휘발성 메모리 디바이스를 동작시키는 방법. - 플래시 메모리 셀의 커플링 게이트와 함께 사용하기 위한 디코더 회로로서,

상기 플래시 메모리 셀이 판독 동작을 위해 선택될 때 상기 커플링 게이트에 바이어스 전압을 제공하기 위한 제1 회로;

상기 플래시 메모리 셀이 프로그래밍 동작을 위해 선택될 때 상기 커플링 게이트에 포지티브 전압을 제공하기 위한 제2 회로;

상기 플래시 메모리 셀이 소거 동작을 위해 선택될 때 상기 커플링 게이트에 소정 전압을 제공하기 위한 제3 회로; 및

상기 플래시 메모리 셀이 비선택될 때 상기 커플링 게이트에 금지 전압(inhibit viltage)을 제공하기 위한 제4 회로를 포함하는, 디코더 회로. - 청구항 33에 있어서,

상기 디코더 회로는 캐스코딩(cascoding) 트랜지스터들을 포함하지 않는, 디코더 회로. - 청구항 33에 있어서,

상기 제3 회로는 상기 커플링 게이트에 네거티브 전압을 제공하는, 디코더 회로. - 플래시 메모리 셀과 함께 사용하기 위한 디코더 회로로서,

상기 플래시 메모리 셀의 소거 게이트와 함께 사용하기 위한 소거 게이트 디코더 회로;

상기 플래시 메모리 셀의 소스 라인과 함께 사용하기 위한 소스 라인 디코더 회로; 및

상기 플래시 메모리 셀의 커플링 게이트와 함께 사용하기 위한 커플링 게이트 디코더 회로를 포함하고,

상기 커플링 게이트 디코더 회로는,

상기 플래시 메모리 셀이 판독 동작을 위해 선택될 때 상기 커플링 게이트에 바이어스 전압을 제공하기 위한 제1 회로;

상기 플래시 메모리 셀이 프로그래밍 동작을 위해 선택될 때 상기 커플링 게이트에 포지티브 전압을 제공하기 위한 제2 회로;

상기 플래시 메모리 셀이 소거 동작을 위해 선택될 때 상기 커플링 게이트에 소정 전압을 제공하기 위한 제3 회로; 및

상기 플래시 메모리 셀이 비선택될 때 상기 커플링 게이트에 금지 전압을 제공하기 위한 제4 회로를 포함하는, 디코더 회로. - 청구항 36에 있어서,

상기 커플링 데이트 디코더 회로는 캐스코딩 트랜지스터들을 포함하지 않는, 디코더 회로. - 청구항 36에 있어서,

상기 제3 회로는 상기 커플링 게이트에 네거티브 전압을 제공하는, 디코더 회로. - 제1 세트의 메모리 셀들 및 제2 세트의 메모리 셀들을 포함하는 플래시 메모리 디바이스를 동작시키는 방법으로서,

상기 제1 세트의 메모리 셀들을 소거하는 단계 - 상기 소거하는 단계는,

상기 제1 세트의 메모리 셀들의 각각의 커플링 게이트에 제1 네거티브 전압을 인가하는 단계,

상기 제1 세트의 메모리 셀들의 각각의 워드 라인 및 비트 라인에 비네거티브 전압을 인가하는 단계, 및

상기 제1 세트의 메모리 셀들의 각각의 소거 게이트에 제1 포지티브 전압을 인가하는 단계를 포함함 -; 및

상기 제2 세트의 메모리 셀들의 각각의 커플링 게이트에 제2 포지티브 전압을 인가함으로써 상기 제2 세트의 메모리 셀들의 소거를 금지하는 단계를 포함하는, 플래시 메모리 디바이스를 동작시키는 방법. - 청구항 39에 있어서,

상기 제2 포지티브 전압을 인가하는 단계는 상기 제1 네거티브 전압을 인가하는 단계와 동시에 또는 거의 동시에 그리고 상기 제1 포지티브 전압을 인가하는 단계 이전에 발생하는, 플래시 메모리 디바이스를 동작시키는 방법. - 입력을 수신하고 출력을 생성하기 위한 네거티브 고전압 레벨 시프터로서,

제1 PMOS 트랜지스터, 제2 PMOS 트랜지스터, 제1 NMOS 트랜지스터, 및 제2 NMOS 트랜지스터를 포함하는 캐스코드 회로 - 상기 제1 NMOS 트랜지스터는 깊은 N-웰을 포함하고, 상기 제2 NMOS 트랜지스터는 깊은 N-웰을 포함함 - 를 포함하고,

상기 제1 NMOS 트랜지스터의 단자는 상기 제2 NMOS 트랜지스터의 단자에 커플링되고, 상기 입력에 응답하여 상기 출력으로 네거티브 고전압을 생성하는, 네거티브 고전압 레벨 시프터. - 청구항 41에 있어서,

상기 깊은 N-웰은 상기 출력이 네거티브 고전압을 생성할 때 0 전압으로 구동되는, 네거티브 고전압 레벨 시프터. - 청구항 41에 있어서,

네거티브 중간 전압 레벨 시프터 회로를 추가로 포함하는, 네거티브 고전압 레벨 시프터. - 청구항 41에 있어서,

상기 네거티브 고전압 레벨 시프터의 출력이 네거티브 전압을 생성할 때 Vdd 고전압 서플라이가 접지로 전환되는, 네거티브 고전압 레벨 시프터.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/602,262 | 2015-01-21 | ||

| US14/602,262 US9361995B1 (en) | 2015-01-21 | 2015-01-21 | Flash memory system using complementary voltage supplies |

| PCT/US2015/064082 WO2016118238A1 (en) | 2015-01-21 | 2015-12-04 | Split gate flash memory system using complementary voltage supplies |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197036378A Division KR102153247B1 (ko) | 2015-01-21 | 2015-12-04 | 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170106442A true KR20170106442A (ko) | 2017-09-20 |

Family

ID=54884436

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177023166A KR20170106442A (ko) | 2015-01-21 | 2015-12-04 | 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 |

| KR1020197036378A KR102153247B1 (ko) | 2015-01-21 | 2015-12-04 | 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197036378A KR102153247B1 (ko) | 2015-01-21 | 2015-12-04 | 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 |

Country Status (7)

| Country | Link |

|---|---|

| US (4) | US9361995B1 (ko) |

| EP (2) | EP3248193B1 (ko) |

| JP (2) | JP2018504731A (ko) |

| KR (2) | KR20170106442A (ko) |

| CN (3) | CN113241100A (ko) |

| TW (2) | TWI621126B (ko) |

| WO (1) | WO2016118238A1 (ko) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9953719B2 (en) | 2016-05-18 | 2018-04-24 | Silicon Storage Technology, Inc. | Flash memory cell and associated decoders |

| US9911501B2 (en) | 2016-05-24 | 2018-03-06 | Silicon Storage Technology, Inc. | Sensing amplifier comprising a built-in sensing offset for flash memory devices |

| US10684669B1 (en) * | 2017-07-28 | 2020-06-16 | Maxim Integrated Products, Inc. | Logic level shifter interface between power domains |

| WO2019033340A1 (zh) * | 2017-08-17 | 2019-02-21 | 深圳市汇顶科技股份有限公司 | 一种可输出正负电压的电平转换器 |

| US10796763B2 (en) | 2018-01-26 | 2020-10-06 | Stmicroelectronics (Rousset) Sas | Method for programming a split-gate memory cell and corresponding memory device |

| US10910061B2 (en) * | 2018-03-14 | 2021-02-02 | Silicon Storage Technology, Inc. | Method and apparatus for programming analog neural memory in a deep learning artificial neural network |

| CN108648777B (zh) * | 2018-05-10 | 2020-08-11 | 上海华虹宏力半导体制造有限公司 | 双分离栅闪存的编程时序电路及方法 |

| US10847225B2 (en) * | 2018-06-20 | 2020-11-24 | Microchip Technology Incorporated | Split-gate flash memory cell with improved read performance |

| DE102019132067A1 (de) | 2019-01-25 | 2020-07-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Strombegrenzer für speichervorrichtung |

| US10991426B2 (en) * | 2019-01-25 | 2021-04-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device current limiter |

| CN110931614B (zh) * | 2019-05-08 | 2021-08-13 | 深圳第三代半导体研究院 | 一种正装集成单元二极管芯片 |

| US11532354B2 (en) | 2020-03-22 | 2022-12-20 | Silicon Storage Technology, Inc. | Precision tuning of a page or word of non-volatile memory cells and associated high voltage circuits for an analog neural memory array in an artificial neural network |

| FR3113976B1 (fr) * | 2020-09-07 | 2023-07-28 | St Microelectronics Rousset | Mémoire type mémoire morte électriquement programmable et effaçable |

| KR20220036634A (ko) | 2020-09-16 | 2022-03-23 | 삼성전자주식회사 | 네거티브 레벨 쉬프터 및 이를 포함하는 비휘발성 메모리 장치 |

| CN112185447B (zh) * | 2020-09-29 | 2023-08-01 | 中科南京智能技术研究院 | 一种8管双分裂控制存储单元、存储阵列及存内计算装置 |

| CN114822657A (zh) * | 2020-12-21 | 2022-07-29 | 长江存储科技有限责任公司 | 半导体器件的深阱电压的控制方法 |

| EP4341935A1 (en) * | 2021-05-18 | 2024-03-27 | Silicon Storage Technology, Inc. | Non-volatile memory cell array formed in a p-well in a deep n-well in a p-substrate |

| US11405039B1 (en) | 2021-06-02 | 2022-08-02 | Sandisk Technologies Llc | Level shifter with improved negative voltage capability |

| US11942972B2 (en) * | 2021-06-28 | 2024-03-26 | Skyworks Solutions, Inc. | Radio frequency switch control circuitry |

| WO2023091172A1 (en) | 2021-11-22 | 2023-05-25 | Silicon Storage Technology, Inc. | Address fault detection in a memory system |

| US20240049470A1 (en) * | 2022-08-08 | 2024-02-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory cell array with increased source bias voltage |

Family Cites Families (65)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5396459A (en) * | 1992-02-24 | 1995-03-07 | Sony Corporation | Single transistor flash electrically programmable memory cell in which a negative voltage is applied to the nonselected word line |

| US5331188A (en) * | 1992-02-25 | 1994-07-19 | International Business Machines Corporation | Non-volatile DRAM cell |

| JPH0758212A (ja) * | 1993-08-19 | 1995-03-03 | Sony Corp | Cmos集積回路 |

| US5515319A (en) * | 1993-10-12 | 1996-05-07 | Texas Instruments Incorporated | Non-volatile memory cell and level shifter |

| CN1187907A (zh) * | 1995-07-17 | 1998-07-15 | 西门子公司 | 电可擦除可编程的、非易失的存储单元 |

| KR100481841B1 (ko) * | 1997-11-25 | 2005-08-25 | 삼성전자주식회사 | 음의고전압을방전시키기위한회로를구비한플래시메모리장치 |

| JP3389856B2 (ja) * | 1998-03-24 | 2003-03-24 | 日本電気株式会社 | 半導体装置 |

| KR19990088517A (ko) * | 1998-05-22 | 1999-12-27 | 마 유에 예일 | 비휘발성메모리셀구조및비휘발성메모리셀을작동시키는방법 |

| US6005810A (en) * | 1998-08-10 | 1999-12-21 | Integrated Silicon Solution, Inc. | Byte-programmable flash memory having counters and secondary storage for disturb control during program and erase operations |

| US6757196B1 (en) * | 2001-03-22 | 2004-06-29 | Aplus Flash Technology, Inc. | Two transistor flash memory cell for use in EEPROM arrays with a programmable logic device |

| US6477091B2 (en) * | 2001-03-30 | 2002-11-05 | Intel Corporation | Method, apparatus, and system to enhance negative voltage switching |

| US20020149067A1 (en) * | 2001-04-12 | 2002-10-17 | Mitros Jozef C. | Isolated high voltage MOS transistor |

| TW565846B (en) * | 2001-07-06 | 2003-12-11 | Halo Lsi Inc | Twin MONOS array metal bit organization and single cell operation |

| US6798008B2 (en) * | 2002-03-19 | 2004-09-28 | 02Ic, Inc. | Non-volatile dynamic random access memory |

| JP2004095893A (ja) * | 2002-08-30 | 2004-03-25 | Nec Electronics Corp | 半導体記憶装置及びその制御方法と製造方法 |

| US7005338B2 (en) * | 2002-09-19 | 2006-02-28 | Promos Technologies Inc. | Nonvolatile memory cell with a floating gate at least partially located in a trench in a semiconductor substrate |

| JP3865238B2 (ja) * | 2002-10-29 | 2007-01-10 | 株式会社ルネサステクノロジ | 不揮発性半導体メモリ |

| US7031192B1 (en) * | 2002-11-08 | 2006-04-18 | Halo Lsi, Inc. | Non-volatile semiconductor memory and driving method |

| JP2004234739A (ja) * | 2003-01-29 | 2004-08-19 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

| JP4156986B2 (ja) * | 2003-06-30 | 2008-09-24 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| GB2408644B (en) * | 2003-11-26 | 2007-04-25 | Wolfson Ltd | Amplifier |

| US7570466B2 (en) * | 2005-03-01 | 2009-08-04 | Intel Corporation | Dual mode negative voltage switching |

| JP4683995B2 (ja) * | 2005-04-28 | 2011-05-18 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| US7242051B2 (en) * | 2005-05-20 | 2007-07-10 | Silicon Storage Technology, Inc. | Split gate NAND flash memory structure and array, method of programming, erasing and reading thereof, and method of manufacturing |

| US7592661B1 (en) * | 2005-07-29 | 2009-09-22 | Cypress Semiconductor Corporation | CMOS embedded high voltage transistor |

| JP2007149186A (ja) * | 2005-11-25 | 2007-06-14 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

| KR100780951B1 (ko) * | 2006-02-15 | 2007-12-03 | 삼성전자주식회사 | 레벨 쉬프터 회로 |

| ITMI20070977A1 (it) * | 2007-05-15 | 2008-11-16 | St Microelectronics Srl | "circuito traslatore di livello e dispositivo di memoria comprendente detto circuito" |

| US20090039410A1 (en) * | 2007-08-06 | 2009-02-12 | Xian Liu | Split Gate Non-Volatile Flash Memory Cell Having A Floating Gate, Control Gate, Select Gate And An Erase Gate With An Overhang Over The Floating Gate, Array And Method Of Manufacturing |

| JP2010097676A (ja) * | 2008-10-20 | 2010-04-30 | Toshiba Corp | 不揮発性半導体記憶装置およびその閾値制御方法 |

| JP2009146521A (ja) * | 2007-12-14 | 2009-07-02 | Sharp Corp | 不揮発性半導体記憶装置のワード線駆動回路 |

| US8391078B2 (en) * | 2008-02-12 | 2013-03-05 | Chip Memory Technology, Inc. | Method and apparatus of operating a non-volatile DRAM |

| KR20100010673A (ko) * | 2008-07-23 | 2010-02-02 | 주식회사 하이닉스반도체 | 비휘발성 메모리 장치, 그의 독출 및 구동방법 |

| KR20100023280A (ko) * | 2008-08-21 | 2010-03-04 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것을 포함하는 메모리 시스템 |

| KR20100035445A (ko) * | 2008-09-26 | 2010-04-05 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그 구동 방법 |

| US8228726B2 (en) * | 2008-12-14 | 2012-07-24 | Chip Memory Technology, Inc. | N-channel SONOS non-volatile memory for embedded in logic |

| US8351264B2 (en) * | 2008-12-19 | 2013-01-08 | Unity Semiconductor Corporation | High voltage switching circuitry for a cross-point array |

| JP2010257559A (ja) * | 2009-04-22 | 2010-11-11 | Genusion Inc | 高電圧発生回路およびそれを備える不揮発性半導体記憶装置 |

| US8283964B2 (en) * | 2009-07-22 | 2012-10-09 | Qualcomm, Incorporated | Level shifters and high voltage logic circuits |

| CN101640205B (zh) * | 2009-08-25 | 2012-08-08 | 上海宏力半导体制造有限公司 | 一种闪存 |

| JP5537099B2 (ja) * | 2009-09-08 | 2014-07-02 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| IT1397227B1 (it) * | 2009-12-30 | 2013-01-04 | St Microelectronics Srl | Dispositivo di memoria con programmazione e cancellazione basata su effetto fowler-nordheim |

| US8933500B2 (en) * | 2010-09-15 | 2015-01-13 | Aplus Flash Technology, Inc. | EEPROM-based, data-oriented combo NVM design |

| WO2012036739A2 (en) * | 2010-09-15 | 2012-03-22 | Aplus Flash Technology, Inc. | An eeprom-based, data-oriented combo nvm design |

| US8106701B1 (en) * | 2010-09-30 | 2012-01-31 | Sandisk Technologies Inc. | Level shifter with shoot-through current isolation |

| US8325521B2 (en) * | 2010-10-08 | 2012-12-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and inhibited operation of flash memory with split gate |

| KR101772582B1 (ko) * | 2011-07-06 | 2017-08-30 | 삼성전자주식회사 | 음전압을 제공하는 비휘발성 메모리 장치 |

| US8923049B2 (en) * | 2011-09-09 | 2014-12-30 | Aplus Flash Technology, Inc | 1T1b and 2T2b flash-based, data-oriented EEPROM design |

| JP5219170B2 (ja) * | 2011-09-21 | 2013-06-26 | 株式会社フローディア | 不揮発性半導体記憶装置 |

| WO2013075067A1 (en) * | 2011-11-18 | 2013-05-23 | Aplus Flash Technology, Inc. | Low voltage page buffer for use in nonvolatile memory design |

| US8570809B2 (en) * | 2011-12-02 | 2013-10-29 | Cypress Semiconductor Corp. | Flash memory devices and systems |

| US8750051B1 (en) * | 2011-12-02 | 2014-06-10 | Cypress Semiconductor Corporation | Systems and methods for providing high voltage to memory devices |

| KR20130098002A (ko) * | 2012-02-27 | 2013-09-04 | 삼성전자주식회사 | 수직형 저항 메모리 장치의 프로그램 방법 |

| KR20130098643A (ko) * | 2012-02-28 | 2013-09-05 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것을 포함하는 임베디드 메모리 시스템 |

| JP2013187534A (ja) * | 2012-03-08 | 2013-09-19 | Ememory Technology Inc | 消去可能プログラマブル単一ポリ不揮発性メモリ |

| US8811093B2 (en) * | 2012-03-13 | 2014-08-19 | Silicon Storage Technology, Inc. | Non-volatile memory device and a method of operating same |

| KR20130104270A (ko) * | 2012-03-13 | 2013-09-25 | 삼성전자주식회사 | 스플릿 게이트형 비휘발성 메모리 장치 및 스플릿 게이트형 비휘발성 메모리 장치가 임베디드된 반도체 장치 |

| WO2014020724A1 (ja) * | 2012-08-01 | 2014-02-06 | ルネサスエレクトロニクス株式会社 | レベルシフト回路、半導体装置 |

| CN102856338B (zh) * | 2012-09-19 | 2015-10-28 | 南京大学 | 分裂栅型mosfet成像探测器及其操作方法 |

| US9123401B2 (en) * | 2012-10-15 | 2015-09-01 | Silicon Storage Technology, Inc. | Non-volatile memory array and method of using same for fractional word programming |

| CN104050999B (zh) * | 2013-03-11 | 2016-12-28 | 北京兆易创新科技股份有限公司 | 一种为浮栅存储器提供正负高压的字线驱动方法 |

| US8867281B2 (en) * | 2013-03-15 | 2014-10-21 | Silicon Storage Technology, Inc. | Hybrid chargepump and regulation means and method for flash memory device |

| US9293205B2 (en) * | 2013-09-14 | 2016-03-22 | Aplus Flash Technology, Inc | Multi-task concurrent/pipeline NAND operations on all planes |

| US20150155039A1 (en) * | 2013-12-02 | 2015-06-04 | Silicon Storage Technology, Inc. | Three-Dimensional Flash NOR Memory System With Configurable Pins |

| US9286982B2 (en) * | 2014-08-08 | 2016-03-15 | Silicon Storage Technology, Inc. | Flash memory system with EEPROM functionality |

-

2015

- 2015-01-21 US US14/602,262 patent/US9361995B1/en active Active

- 2015-12-04 WO PCT/US2015/064082 patent/WO2016118238A1/en active Application Filing

- 2015-12-04 CN CN202110506606.2A patent/CN113241100A/zh active Pending

- 2015-12-04 EP EP15813222.5A patent/EP3248193B1/en active Active

- 2015-12-04 CN CN201580074175.XA patent/CN107210056B/zh active Active

- 2015-12-04 JP JP2017538340A patent/JP2018504731A/ja active Pending

- 2015-12-04 EP EP19203643.2A patent/EP3629331B1/en active Active

- 2015-12-04 KR KR1020177023166A patent/KR20170106442A/ko active Application Filing

- 2015-12-04 CN CN202110506608.1A patent/CN113241101B/zh active Active

- 2015-12-04 KR KR1020197036378A patent/KR102153247B1/ko active IP Right Grant

- 2015-12-16 TW TW106110808A patent/TWI621126B/zh active

- 2015-12-16 TW TW104142264A patent/TWI587305B/zh active

-

2016

- 2016-04-21 US US15/135,346 patent/US9508443B2/en active Active

- 2016-11-27 US US15/361,473 patent/US10186322B2/en active Active

-

2018

- 2018-12-12 US US16/218,398 patent/US10325666B2/en active Active

-

2019

- 2019-05-17 JP JP2019093479A patent/JP6911075B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| TW201638962A (zh) | 2016-11-01 |

| EP3248193A1 (en) | 2017-11-29 |

| TWI587305B (zh) | 2017-06-11 |

| EP3629331B1 (en) | 2023-10-04 |

| US10186322B2 (en) | 2019-01-22 |

| US10325666B2 (en) | 2019-06-18 |

| TWI621126B (zh) | 2018-04-11 |

| US9361995B1 (en) | 2016-06-07 |

| US9508443B2 (en) | 2016-11-29 |

| US20160240260A1 (en) | 2016-08-18 |

| US20190115088A1 (en) | 2019-04-18 |

| JP6911075B2 (ja) | 2021-07-28 |

| CN107210056A (zh) | 2017-09-26 |

| TW201727655A (zh) | 2017-08-01 |

| KR102153247B1 (ko) | 2020-09-07 |

| CN113241101B (zh) | 2024-01-30 |

| CN113241100A (zh) | 2021-08-10 |

| CN113241101A (zh) | 2021-08-10 |

| WO2016118238A1 (en) | 2016-07-28 |

| EP3248193B1 (en) | 2020-02-05 |

| US20170076809A1 (en) | 2017-03-16 |

| EP3629331A1 (en) | 2020-04-01 |

| JP2019169233A (ja) | 2019-10-03 |

| KR20190139341A (ko) | 2019-12-17 |

| JP2018504731A (ja) | 2018-02-15 |

| CN107210056B (zh) | 2021-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102153247B1 (ko) | 상보성 전압 서플라이들을 사용하는 분리형 게이트 플래시 메모리 시스템 | |

| CN107077891B (zh) | 非易失性分裂栅存储器装置及其操作方法 | |

| KR101538284B1 (ko) | 비휘발성 메모리 디바이스 및 그 동작 방법 | |

| TWI679643B (zh) | 快閃路徑中的高速高電壓耐受性電路 | |

| US8867281B2 (en) | Hybrid chargepump and regulation means and method for flash memory device | |

| JP2011171582A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| AMND | Amendment | ||

| E902 | Notification of reason for refusal | ||

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| X091 | Application refused [patent] | ||

| E601 | Decision to refuse application | ||

| E801 | Decision on dismissal of amendment | ||

| A107 | Divisional application of patent |