KR100310565B1 - 반도체장치의제조방법및반도체장치 - Google Patents

반도체장치의제조방법및반도체장치 Download PDFInfo

- Publication number

- KR100310565B1 KR100310565B1 KR1019970048682A KR19970048682A KR100310565B1 KR 100310565 B1 KR100310565 B1 KR 100310565B1 KR 1019970048682 A KR1019970048682 A KR 1019970048682A KR 19970048682 A KR19970048682 A KR 19970048682A KR 100310565 B1 KR100310565 B1 KR 100310565B1

- Authority

- KR

- South Korea

- Prior art keywords

- film

- insulating film

- oxide film

- silicon nitride

- nitride film

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 65

- 238000000034 method Methods 0.000 title abstract description 48

- 229910052581 Si3N4 Inorganic materials 0.000 claims abstract description 64

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims abstract description 64

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 56

- 229910052814 silicon oxide Inorganic materials 0.000 claims abstract description 56

- 239000000758 substrate Substances 0.000 claims abstract description 40

- 230000002093 peripheral effect Effects 0.000 claims description 28

- 238000000059 patterning Methods 0.000 claims description 6

- 230000000149 penetrating effect Effects 0.000 claims description 6

- 239000011229 interlayer Substances 0.000 abstract description 32

- 238000004519 manufacturing process Methods 0.000 abstract description 24

- 238000003860 storage Methods 0.000 abstract description 24

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 12

- 229910052710 silicon Inorganic materials 0.000 abstract description 12

- 239000010703 silicon Substances 0.000 abstract description 12

- 230000014759 maintenance of location Effects 0.000 abstract description 9

- 230000002542 deteriorative effect Effects 0.000 abstract 1

- 150000004767 nitrides Chemical class 0.000 description 37

- 238000005530 etching Methods 0.000 description 27

- 238000000206 photolithography Methods 0.000 description 19

- 238000001312 dry etching Methods 0.000 description 16

- 229910052698 phosphorus Inorganic materials 0.000 description 16

- 239000011574 phosphorus Substances 0.000 description 16

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 14

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 229920005591 polysilicon Polymers 0.000 description 12

- 239000005380 borophosphosilicate glass Substances 0.000 description 9

- 239000003990 capacitor Substances 0.000 description 9

- 239000010410 layer Substances 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 238000002955 isolation Methods 0.000 description 8

- 230000003647 oxidation Effects 0.000 description 7

- 238000007254 oxidation reaction Methods 0.000 description 7

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 6

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 5

- 229910021342 tungsten silicide Inorganic materials 0.000 description 5

- 230000006866 deterioration Effects 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- -1 phosphorus ions Chemical class 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 239000012535 impurity Substances 0.000 description 3

- XAGFODPZIPBFFR-BJUDXGSMSA-N Aluminum-26 Chemical compound [26Al] XAGFODPZIPBFFR-BJUDXGSMSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823475—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type interconnection or wiring or contact manufacturing related aspects

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

- H01L27/105—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration including field-effect components

Abstract

본 발명에 따르면, 반도체 장치, 특히 메모리 장치의 제조에 있어서, 데이터 유지 특성을 열화시키지 않고, 또한 공정수를 감소시킬 수 있다.

본 발명에 따르면, 실리콘 반도체 기판에 게이트 산화막과 게이트 전극을 형성하고, 이 게이트 전극 위에 실리콘 산화막을 형성한다. 그 후, 전면을 실리콘 질화막으로 피복하고, 또한 층간 산화막을 형성한다. 서로 이웃하는 게이트 전극 사이의 소스/드레인 영역에, 실리콘 질화막을 이용한 SAC 기술에 의해 비트선 콘택트를 형성한다. 또한, 다른 소스/드레인 영역에서는 실리콘 질화막에 개구를 형성하여 저장 노드 콘택트를 형성한다.

Description

본 발명은 반도체 장치 및 그 제조 방법에 관한 것으로, 특히 반도체 메모리 장치 등에 적용하여 효과가 큰 것에 관한 것이다.

더욱 자세하게는, 반도체 장치의 활성 영역상에 자기 정합적(自己整合的)으로 콘택트 홀을 형성하는 셀프 얼라인드 콘택트(SAC : Self Alligned Contact) 기술을 이용한 반도체 장치의 구조 및 제조 방법에 관한 것으로서, 데이터 유지 특성의 열화(劣化)를 가져오는 일이 없는 DRAM 장치 등을 얻을 수 있는 것이다.

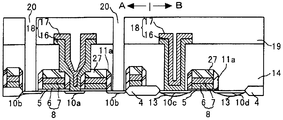

이하에 SAC 기술을 이용한 종래의 반도체 장치의 제조 방법에 대하여, 디자인룰이 0.3㎛ 정도인 DRAM의 제조 방법을 예로 들어 설명한다. 도 21 내지 도 40은 종래의 DRAM 제조 방법과 그 구조를 설명하기 위한 단면도이다.

제조 방법에 대하여 우선 도 21을 참조해 설명하면, 실리콘 반도체 기판(1)의 전면에 열산화법으로 100Å 정도의 실리콘 열산화막(2)을 형성한 후, CVD법으로 500Å 정도의 실리콘 질화막(3)을 퇴적시킨다. 다음에, 사진 제판 및 에칭 기술로 소자를 만들어 넣을 영역에만 실리콘 질화막(3)을 남긴다.

다음에, 도 22를 참조하면 질화막(3) 사이에 열산화법으로 3000Å 정도의 열산화막(4)을 선택적으로 형성하여 소자 분리 산화막으로 하고, 질화막(3)을 제거하여 소자 형성 영역을 만든다. 도면 중, 좌측 절반이 메모리 셀부 A이고, 우측 절반이 주변 회로부 B로 된다.

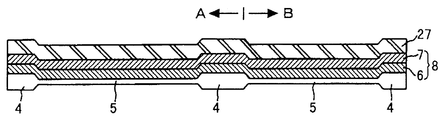

다음에, 열산화법으로 트랜지스터의 게이트 산화막으로 되는 열산화막(5)을 90Å 정도 형성한다. 그 후, 인(P)이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘(phosphorus-doped polysilicon)(6)과 텅스텐 실리사이드(WSi2)(7)를 CVD법으로 500Å 정도씩 퇴적시켜, 이층막(8)(이하, 필요에 따라 폴리사이드라 약칭한다)을 형성한다.

또한 CVD법으로 실리콘 질화막(27)을 1000Å 정도 퇴적시킨다. 이러한 실리콘 질화막(27)은 폴리사이드 게이트 형성시에 에칭 마스크와, SAC 개구 형성시에 에칭 스토퍼(stopper)로서의 역할을 한다. 또, 도 22 이후에서는 반도체 기판(1)의 부호의 표시를 생략한다.

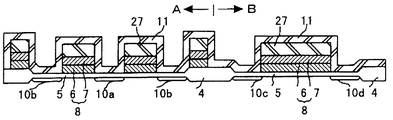

도 23을 참조하면, 사진 제판 및 질화막 이방성 에칭 기술로 소망하는 부분만 질화막(27)을 남기고, 또한 질화막(27)을 마스크로 하여 폴리사이드(8)를 이방성 에칭해서 게이트 길이 0.3㎛ 정도의 게이트 전극(8)을 형성한다. 이 때, 폴리 사이드 에칭은 게이트 산화막(5) 위에서 정지시킨다.

계속해서, 이온 주입 기술로 게이트 전극(8) 및 소자 분리 산화막(4)에 대하여 자기 정합적으로 인(燐) 이온을 1×1013개/㎠ 정도 주입하여, MOS 트랜지스터의저 농도의 소스/드레인 영역, 이른바 n-소스/드레인 영역(10a, 1Ob, 1Oc, 1Od)을 형성한다. 도면 중, 소스/드레인 영역(10a)에는 이후의 공정에서 콘택트 홀을 거쳐 비트선이 접속되고, 소스/드레인 영역(10b)에는 이후의 공정에서 별도의 콘택트 홀을 거쳐 캐패시터 하부 전극이 접속된다.

도 24를 참조하면, CVD법으로 실리콘 질화막(11)을 800Å 정도 퇴적시킨다. 이 질화막(11)은 LDD 구조를 갖는 트랜지스터의 측벽(side wall) 역할을 한다.

도 25를 참조하면, 이방성 질화막 에칭 기술로 게이트 전극(8)의 측벽에 질화막의 측벽(11a)을 형성한다. 이 때, 측벽 폭 W1은 800Å 정도로 된다. 이 때, 얇은 게이트 산화막(5)은 질화막 에칭의 스토퍼로는 되지 않고, 오버 에칭으로 용이하게 제거되어 소스/드레인 영역(10a, 10b)이 노출된다.

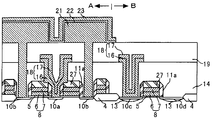

도 26을 참조하면, 사진 제판 기술로 메모리 셀부 A를 레지스트(12)로 피복하고, 이온 주입 기술로 게이트 전극(8), 소자 분리 산화막(4) 및 질화막 측벽(11a)에 대하여 자기 정합적으로 비소 이온을 5×1015개/㎠ 정도 주입하여 MOS 트랜지스터의 고 소스/드레인 영역, 이른바 n+소스/드레인 영역(13)을 형성한다.

이 때, 메모리 셀부 A는 레지스트(12)로 피복하여 n+소스/드레인 영역을 형성하지 않도록 한다. 메모리 셀부 A에 n+소스/드레인 영역을 형성하면, 접합 리크 전류가 증가하여 데이터 유지 특성이 열화하기 때문에, 메모리 셀부에는 저 농도의n-소스/드레인 영역만을 형성한다.

도 27를 참조하면, 메모리 셀부 A의 레지스트(12)를 제거하여 CVD법으로 붕소나 인을 포함한 산화막(이하, BPSG라 약칭한다)을 4000Å 정도 퇴적시켜서 층간 절연막(14)을 형성한다.

이 경우, TEOS 산화막 등의 특히 붕소나 인을 포함하지 않은 산화막을 이용하는 것은 적절하지 않다. 붕소나 인을 포함하지 않은 산화막은 SAC 개구 형성시 에칭 스토퍼의 질화막과의 에칭 선택비가 작기 때문이다.

도 28을 참조하면, 질소 분위기중에서 850℃ 정도의 열처리를 20분 정도 실시하여 BPSG를 열적으로 새그(sag)시켜 층간 절연막(14)을 평탄하게 한다. 이 때, 게이트 전극(8) 사이의 SAC를 형성하는 부분의 산화막(14)의 두께 t1은 약 6000Å 정도로 된다.

도 29를 참조하면, 사진 제판 및 이방성 산화막 건식 에칭(anisotropic oxide film-dry etching) 기술로 메모리 셀부 A의 소스/드레인(10a) 위와, 주변 회로부 B의 소스/드레인(10c) 위에, 비트선과 활성 영역을 접속하기 위한, 지름 0.3㎛ 정도의 비트선 콘택트 홀(15)을 형성한다. 이 때, 오버 에칭량을 30%로 하여 9000Å 상당의 BPSG를 에칭하면, 질화막의 에칭 속도는 BPSG의 약 1/20 정도이기 때문에, 메모리 셀부의 소스/드레인(10a) 위의 질화막(27)은 250Å 정도의 두께 t2가 에칭되게 된다.

도 30을 참조하면, 게이트 전극(8)과 마찬가지로, 인 도프트 폴리실리콘(16)과 텅스텐 실리사이드(WSi2)(17)로 이루어지는 폴리 사이드(18)를 CVD법으로 퇴적시켜 비트선 콘택트 홀을 매립한 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 패턴을 형성한다. 이 폴리 사이드 배선(18)의 선폭 W2는 0.3∼0.5㎛ 정도로, 이것은 DRAM의 비트선으로 되며, 각각 비트선 콘택트 홀(15)을 거쳐 소스/드레인 영역(10a, 10c)에 접속된다.

도 31을 참조하면, CVD법으로 3000Å 정도의 실리콘 산화막을 퇴적시켜 층간 절연막(19)을 형성한다.

도 32를 참조하면, 사진 제판 및 이방성 산화막 건식 에칭 기술로 메모리 셀부의 소스/드레인(10b) 위에, 지름 0.3㎛ 정도의 저장 노드·콘택트 홀(20)을 형성한다. 이것은 캐패시터 하부 전극(이하, 저장 노드라 칭한다)과 활성 영역(10b)을 접속하기 위한 콘택트 홀이다.

도 33을 참조하면, 인이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘을 7000Å 정도 CVD법으로 퇴적시킨 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 부분만 인 도프트 폴리 실리콘을 남겨서 저장 노드(21)를 형성한다. 저장 노드(21) 사이의 간격 W3은 저장 노드(21)의 표면적을 크게하기 위해서 가능한 한 좁게 0.25㎛ 정도로 한다. 또한, 저장 노드(21)는 저장 노드 콘택트 홀(20)을 거쳐 메모리 셀부 A의 n-소스/드레인 영역(10b)에 접속된다.

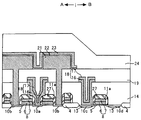

도 34를 참조하면, CVD법으로 캐패시터 유전막으로 되는 질화막(22)과, 캐패시터 상부 전극(이하, 셀 플레이트(cell plate)라 칭한다)(23)으로 되는, 인이5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘을 각각 60Å/1000Å 정도 연속하여 퇴적시킨다. 사진 제판 및 이방성 건식 에칭 기술로 메모리 셀부 A 이외의 인 도프트 폴리 실리콘(23)을 제거하고 셀 플레이트(23)를 형성하여 캐패시터가 완성된다.

도 35를 참조하면, CVD법으로 BPSG를 5000Å 정도 퇴적시켜 층간 절연막(24)을 형성한다.

도 36을 참조하면, 층간 절연막(14)과 마찬가지로, 질소 분위기에서 850℃ 정도의 열처리를 약 30분 실시하여 층간 절연막(24)의 표면 형상을 매끄럽게 한다.

도 37을 참조하면, 사진 제판 및 이방성 산화막 건식 에칭 기술로, 주변 회로부 B의 소스/드레인(10d)의 위 및 주변 회로부 B에 형성된 비트선(18)의 위에, 각각 지름 0.3∼0.4㎛ 정도의 콘택트 홀(25a)을 형성한다. 이 때, 주변 회로부 B의 게이트 전극(8)에 대한 콘택트는 게이트 전극(8) 위에 질화막(27)이 있기 때문에 산화막 에칭이 질화막(27) 위에서 정지되어 버리므로 동시에는 형성할 수 없다.

도 38을 참조하면, 주변 회로부 B의 게이트 전극(8)의 위에 게이트 콘택트 홀(25b)을 형성한다. 여기서는 이방성 산화막 건식 에칭 기술로 일단 질화막(27) 위까지 개구를 형성한다.

도 39를 참조하면, 계속해서 게이트 콘택트 홀(25b)로부터 질화막 에칭을 실행하여 질화막(27)에 개구를 형성하고, 게이트 전극(8)의 상면을 노출시킨다.

도 40을 참조하면, 스퍼터법으로 알루미늄(26)을 5000Å 정도 퇴적시켜 콘택트 홀(25a, 25b)을 매립한 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 부분을 남기고 선폭 0.4㎛ 정도의 알루미늄 배선(26)을 형성한다.

이상이 SAC 기술을 이용한 종래의 DRAM 제조 방법이다. 이 방법에서는 도 25의 질화막 측벽(11a)을 형성하는 이방성 질화막 에칭의 공정에서, 메모리 셀부 A에 있어서, 저장 노드 콘택트 홀(20)이 형성되고, 저장 노드(21)와 콘택트가 취해지는 소스/드레인 영역(10b)이 에칭에 의해 손상을 받아, 데이터 유지 특성을 현저히 열화시켜 버린다.

또한, 주변 회로부 B에서는, 게이트 전극(8) 위에 실리콘 질화막(27)이 있기 때문에, 소스/드레인 영역(10d) 및 비트선(18) 위에 콘택트 홀(25a)을 형성하는 공정과, 게이트 전극(8)상에 콘택트 홀(25b)을 마련하는 공정으로, 콘택트 홀의 형성 공정이 두 번 필요하게 된다.

본 발명의 목적은 이러한 종래 기술의 결점을 극복하여, 데이터 유지 특성의 열화를 초래하는 일이 없이, 또한 공정수를 감소시킬 수 있는, SAC 기술에 의한 반도체 장치와 그 제조 방법을 제공하는 것이다.

도 1 내지 20은 본 발명의 실시예 1에 따른 DRAM의 제조 방법을 설명하기 위한 단면도,

도 21 내지 40은 종래의 DRAM의 제조 방법을 설명하기 위한 단면도.

도면의 주요부분에 대한 부호의 설명

1 : 실리콘 반도체 기판4 : 소자 분리 산화막

5 : 실리콘 산화막, 게이트 산화막(제 1 절연막)

8 : 폴리 사이드, 게이트 전극(제 1 도전막)

9 : 실리콘 산화막

10a, 10b, 10c, 10d : 소스/드레인 영역(활성 영역)

11 : 실리콘 질화막11a : 질화막 측벽(side wall)

14 : 실리콘 산화막, 층간 절연막(제 2 절연막)

15 : 비트선 콘택트 홀18 : 폴리 사이드, 비트선(18),

19 : 실리콘 산화막, 층간 절연막20 : 저장 노드·콘택트 홀

21 : 저장 노드24 : 층간 절연막

25 : 콘택트 홀26 : 알루미늄 배선

A : 메모리 셀부B : 주변 회로부

본 발명에 의한 반도체 장치의 제조 방법은, 실리콘 반도체 기판의 주표면에 제 1 절연막을 형성하는 공정과, 이 제 1 절연막 위에 제 1 도전층을 형성하는 공정과, 이 제 1 절연층 위에 실리콘 산화막을 형성하는 공정과, 상기 실리콘 산화막 및 상기 제 1 도전층을 패터닝하여 상면에 산화막을 갖는 복수의 게이트 전극을 형성하는 공정과, 상기 게이트 전극 사이의 상기 반도체 기판의 주표면에 불순물을 도입하여 복수의 활성 영역을 형성하는 공정과, 상기 제 1 절연막 및 상기 게이트 전극을 포함하는 상기 반도체 기판의 전면에 실리콘 질화막을 형성하는 공정과, 이 실리콘 질화막 위에 제 2 절연막을 형성하는 공정과, 상기 복수의 게이트 전극 중 선택된 서로 이웃하는 게이트 전극 사이에서 상기 제 2 절연막에 개구를 형성하는 공정과, 상기 서로 이웃하는 게이트 전극의 각각 측면의 실리콘 질화막 사이에 있어서 상기 개구로부터 상기 제 1 절연막 위의 실리콘 질화막 및 상기 제 1 절연막에 개구를 형성하여 상기 반도체 기판의 상기 활성 영역에 이르는 콘택트를 형성하는 공정을 포함하는 것을 특징으로 한다.

또한, 본 발명에 의한 반도체 장치의 제조 방법은, 실리콘 반도체 기판의 주표면에 제 1 절연막을 형성하는 공정과, 이 제 1 절연막 위에 제 1 도전막을 형성하는 공정과, 이 제 1 도전막 위에 실리콘 산화막을 형성하는 공정과, 상기 실리콘 산화막 및 상기 제 1 도전막을 패터닝하여 상면에 실리콘 산화막을 갖는 복수의 게이트 전극을 형성하는 공정과, 상기 게이트 전극 사이의 상기 반도체 기판의 주표면에 불순물을 도입하여 복수의 활성 영역을 형성하는 공정과, 상기 제 1 절연막 및 상기 게이트 전극을 포함하는 상기 반도체 기판의 전면에 실리콘 질화막을 형성하는 공정과, 상기 실리콘 질화막을 이방성 에칭하여 상기 게이트 전극의 측면에 실리콘 질화막의 측벽을 형성하는 공정과, 상기 게이트 전극의 상기 실리콘 산화막및 실리콘 질화막 측벽을 포함하는 상기 반도체 기판 위의 전면에 제 2 절연막을 형성하는 공정과, 상기 게이트 전극 위에 있어서 상기 제 2 절연막과 상기 실리콘 산화막에 개구를 형성하여 상기 게이트 전극에 이르는 콘택트를 형성함과 동시에, 상기 반도체 기판의 활성 영역 위에 있어서 상기 제 2 절연막에 개구를 형성하여 상기 활성 영역에 이르는 콘택트를 형성하는 공정을 포함하는 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치의 제조 방법은, 메모리 셀 형성부와 주변 회로 형성부를 포함하는 실리콘 반도체 기판의 주표면에 제 1 절연막을 형성하는 공정과, 이 제 1 절연막 위에 제 1 도전층을 형성하는 공정과, 이 제 1 절연층 위에 실리콘 산화막을 형성하는 공정과, 상기 실리콘 산화막 및 상기 제 1 도전층을 패터닝하여 상면에 실리콘 산화막을 갖는 복수의 게이트 전극을 형성하는 공정과, 상기 게이트 전극 사이의 상기 반도체 기판의 주표면에 불순물을 도입하여 복수의 활성 영역을 형성하는 공정과, 상기 제 1 절연막 및 상기 게이트 전극을 포함하는 상기 반도체 기판의 전면에 실리콘 질화막을 형성하는 공정과, 상기 반도체 기판의 주변 회로 형성부에서 상기 실리콘 질화막을 이방성 에칭하여 상기 게이트 전극의 측면에 실리콘 질화막의 측벽을 형성하는 공정과, 상기 메모리 셀 형성부에서의 상기 실리콘 질화막 및 상기 주변 회로 형성부의 상기 게이트 전극의 상기 실리콘 산화막 및 실리콘 질화막 측벽을 포함하는 상기 반도체 기판 위의 전면에 동시에 제 2 절연막을 형성하는 공정과,

상기 메모리 셀 형성부에 있어서, 상기 복수의 게이트 전극 중 선택된 각 한쌍의 게이트 전극 사이에서 상기 제 2 절연막에 개구를 형성하는 공정과, 상기 메모리 셀 형성부에 있어서, 상기 개구로부터 상기 실리콘 질화막 및 상기 제 1 절연막에 개구를 형성하여 상기 반도체 기판의 상기 활성 영역에 이르는 콘택트를 형성하는 공정과,

상기 주변 회로 형성부에 있어서, 상기 게이트 전극 위에서 상기 제 2 절연막과 상기 실리콘 산화막에 개구를 형성하여 상기 게이트 전극에 이르는 콘택트를 형성함과 동시에, 상기 반도체 기판의 활성 영역 위에서 상기 제 2 절연막에 개구를 형성하여 상기 활성 영역에 이르는 콘택트를 형성하는 공정을 포함하는 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치의 제조 방법은, 상기 제 2 절연막을 실리콘 산화막으로 형성한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치의 제조 방법은, 상기 제 1 절연막을 실리콘 산화막으로 형성한 것을 특징으로 하는 것이다.

다음에, 본 발명에 의한 반도체 장치는, 반도체 기판의 주표면에 형성된 복수의 활성 영역과, 상기 복수의 활성 영역 중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과, 이 제 1 절연막 위에 형성된 제 1 도전막과, 이 제 1 도전막 위에 형성된 실리콘 산화막과, 이 실리콘 산화막 및 상기 제 1 도전막의 측면을 피복하도록 상기 반도체 기판의 전면에 형성된 실리콘 질화막과, 이 실리콘 질화막 위에 형성된 제 2 절연막과, 서로 이웃하는 상기 게이트 전극 사이에 있어서 각 게이트 전극 측면의 실리콘 질화막 사이에서 상기 제 2 절연막과 상기 제 1 절연막 위의실리콘 질화막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 구비한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치는, 반도체 기판의 주표면에 형성된 복수의 활성 영역과, 상기 복수의 활성 영역 중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과, 이 제 1 절연막 위에 형성된 제 1 도전막과, 이 제 1 도전막 위에 형성된 실리콘 산화막과, 상기 제 1 도전막의 측면에 형성된 실리콘 질화막과, 상기 실리콘 산화막 및 실리콘 질화막을 피복하도록 상기 반도체 기판의 전면에 형성된 제 2 절연막과, 상기 게이트 전극 위에서 상기 제 2 절연막과 상기 실리콘 산화막을 관통하여 상기 게이트 전극에 이르는 콘택트와, 상기 활성 영역 위에서 상기 제 2 절연막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 구비한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치는, 메모리 셀부와 주변 회로부를 갖는 반도체 기판의 주표면에 형성된 복수의 활성 영역과, 상기 복수의 활성 영역 중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과, 이 제 1 절연막 위에 형성된 제 1 도전막과, 이 제 1 도전막 위에 형성된 실리콘 산화막을 구비하고,

또한 상기 메모리 셀부에 있어서, 상기 실리콘 산화막 및 상기 제 1 도전막의 측면을 피복하도록 상기 반도체 기판의 전면에 형성된 실리콘 질화막과, 이 실리콘 질화막 위에 형성된 제 2 절연막과, 서로 이웃하는 상기 게이트 전극 사이에 있어서 각 게이트 전극의 측면의 실리콘 질화막 사이에서 상기 제 2 절연막과 상기 제 1 절연막 위의 실리콘 질화막과 상기 제 1 절연막을 관통하여 상기 활성 영역에이르는 콘택트를 구비하며,

또한, 상기 주변 회로부에 있어서, 상기 제 1 도전막의 측면에 형성된 실리콘 질화막과, 상기 실리콘 산화막 및 상기 실리콘 질화막을 피복하도록 상기 반도체 기판의 전면에 형성된 제 2 절연막과, 상기 게이트 전극의 위에서 상기 제 2 절연막과 상기 실리콘 산화막을 관통하여 상기 게이트 전극에 이르는 콘택트와, 상기 활성 영역 위에서 상기 제 2 절연막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 구비한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치는, 상기 활성 영역을 M0S 트랜지스터의 소스/드레인으로서 형성한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치는, 상기 메모리 셀부에 있어서의 상기 콘택트를 메모리 셀의 비트선과의 콘택트 또는 저장 노드와의 콘택트로서 형성한 것을 특징으로 하는 것이다.

또한, 본 발명에 의한 반도체 장치는, 상기 반도체 장치의 제조 방법에 의해 제조된 것을 특징으로 하는 것이다.

발명의 실시예

(실시예 1)

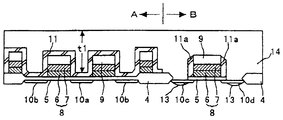

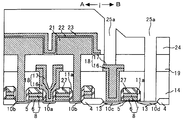

이하에 본 발명의 실시예 1에 따른 반도체 장치 및 그 제조 방법을, 디자인룰이 0.3㎛ 정도인 DRAM의 제조 방법과, 그 제조 방법에 의해 제조된 DRAM을 예로 들어 설명한다. 도 1 내지 도 20은, 이 실시예에 따른 DRAM의 제조 방법과 그 구조를 설명하기 위한 단면도이다.

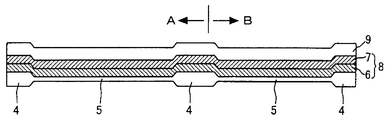

우선, 제조 방법부터 설명한다. 우선, 도 1을 참조하면, 실리콘 반도체 기판(1)의 전면에 열산화법으로 100Å 정도의 실리콘 열산화막(2)을 형성한다. 다음에, CVD법으로 500Å 정도의 실리콘 질화막(3)을 퇴적시킨다.

도 2를 참조하면, 사진 제판 및 에칭 기술로, 메모리 셀부 혹은 주변 회로부로서의 각 소자를 만들어 넣을 영역에만 질화막(3)을 남긴다.

도 3을 참조하면, 열산화법으로 3000Å 정도의 실리콘 열산화막을 선택적으로 형성하여 소자 분리 산화막(4)으로 한 후, 질화막(3)을 제거하여 메모리 셀부 및 주변 회로부의 소자 형성 영역을 만든다. 도면 중 좌측 절반을 메모리 셀부 A로 하고, 우측 절반을 주변 회로부 B로 한다.

도 4를 참조하면, 열산화법으로 트랜지스터의 게이트 산화막으로 되는 실리콘 열산화막(5)(제 1 절연막)을 90Å 정도 형성한다. 그 후, 인이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘(6)과 텅스텐 실리사이드(WSi2)(7)를 CVD법으로 500Å 정도씩 퇴적시켜, 이른바 폴리 사이드의 이층막(8)(제 1 도전막)(이하, 필요에 따라 폴리 사이드라 한다)을 형성한다. 또한, CVD법으로 실리콘 산화막(9)을 1000Å 정도 퇴적시킨다. 또, 도 4 이후에는 간략하게 하기 위해 반도체 기판(1)의 부호 표시를 생략한다.

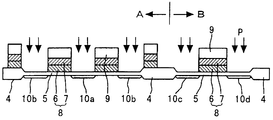

도 5를 참조하면, 사진 제판 및 산화막 이방성 에칭 기술로 소망하는 부분만 실리콘 산화막(9)을 남기고, 또한 산화막(9)을 마스크로 하여 폴리 사이드(8)를 이방성 에칭하여 게이트 길이 0.3㎛ 정도의 게이트 전극(8)을 형성한다. 이 때, 폴리 사이드 에칭은 게이트 산화막(5) 위에서 정지시킨다.

계속해서, 이온 주입 기술로 게이트 전극(8) 및 소자 분리 산화막(4)에 대하여, 자기 정합적으로 인 이온을 1×1O13개/㎠ 정도 주입하고 활성 영역으로 되는, M0S 트랜지스터의 저 농도의 소스/드레인 영역, 이른바 n-소스/드레인 영역(10a, 10b, 10c, 10d)을 형성한다. 도면 중, 메모리 셀부 A의 소스/드레인 영역(10a)에는 이후의 공정에서 콘택트 홀을 거쳐 비트선이 접속되고, 소스/드레인 영역(10b)에는 이후의 공정에서 별도의 콘택트 홀을 거쳐 캐패시터 하부 전극이 접속된다.

도 6을 참조하면, CVD법으로 실리콘 질화막(11)을 800Å 정도 퇴적시킨다. 이 실리콘 질화막(11)은 LDD 구조를 갖는 MOS 트랜지스터의 측벽 역할을 한다.

도 7을 참조하면, 사진 제판 기술로 메모리 셀부 A를 레지스트(12)로 피복하고, 이방성 질화막 에칭 기술로 주변 회로부 B의 트랜지스터의 게이트 전극(8)의 측벽에 두께 W1가 약 800Å인 질화막의 측벽(11a)을 형성한다.

계속해서, 주변 회로부 B에 있어서, 이온 주입 기술로 게이트 전극(8) 및 소자 분리 산화막(4) 및 질화막 측벽(11a)에 대하여, 비소 이온을 5×1015개/㎠ 정도 주입하여, 자기 정합적으로 활성 영역으로서의 MOS 트랜지스터의 고 농도의 소스/드레인 영역, 이른바 n+소스/드레인 영역(13)을 형성한다.

또, 메모리 셀부 A에 n+소스/드레인 영역을 형성하면, 접합 리크 전류가 증가하여 데이터 유지 특성이 열화하기 때문에, 메모리 셀부 A에는 고 농도의 소스/드레인 영역은 형성하지 않고, 저 농도의 n-소스/드레인 영역만으로 형성한다.

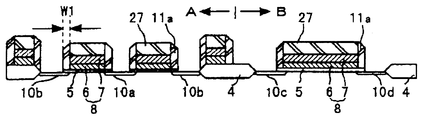

도 8을 참조하면, 메모리 셀부 A의 레지스트(12)를 제거하고, 전면에 CVD법으로 붕소나 인을 포함한 산화막(이하, 필요에 따라 BPSG라 약칭한다)을 4000Å 정도 퇴적시켜 층간 절연막(14)(제 2 절연막)을 형성한다.

또, 이 경우, TEOS 산화막 등의 특히 붕소나 인을 포함하지 않은 산화막은 이용하지 않는다. 붕소나 인을 포함하지 않은 산화막은 SAC 개구 형성시의 에칭 스토퍼인 질화막과의 에칭 선택비가 작기 때문에 바람직하지 않기 때문이다.

도 9를 참조하면, 질소 분위기속에서 850℃ 정도의 열처리를 20분 정도 실시하여, BPSG를 열적으로 새그(sag)시켜 층간 절연막(14)을 평탄하게 한다. 이 때, 게이트 전극(8) 사이의 SAC를 형성하는 부분의 산화막의 두께 t1은 약 6000Å 정도가 된다.

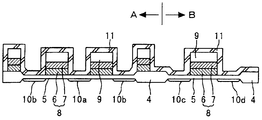

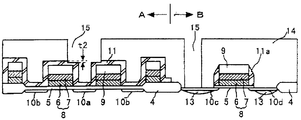

도 10을 참조하면, 사진 제판 및 이방성 산화막 건식 에칭 기술로, 메모리 셀부 A에서, 서로 이웃하는 게이트 전극(8) 사이에서, 또한 소스/드레인 영역(10a) 위에서, 및 주변 회로부 B의 소스/드레인 영역(10c) 위에서, 산화막(14)에 개구를 형성하여 지름 0.3㎛ 정도의 비트선 콘택트 홀(15)을 형성한다. 이 때, 메모리 셀부 A의 소스/드레인 영역(10a) 위의 에칭은, 실리콘 질화막(11) 위에서 정지시킨다. 산화막(14)의 오버 에칭량을 30%로 하여 9000Å 상당의 BPSG를 에칭한다고 하면, 실리콘 질화막(11)의 에칭 속도는 BPSG의 약 1/20 정도이기 때문에, 실리콘 질화막(11)은 250Å 정도의 두께 t2가 에칭되게 된다.

도 11을 참조하면, 메모리 셀부 A의 소스/드레인 영역(10a) 위에서, 또한 비트선 콘택트 홀(15) 내부의, 게이트 산화막(5) 위의 질화막(11) 및 게이트 산화막(5)을 이방성 질화막 에칭 기술로 에칭하여 소스/드레인 영역(10a)을 노출시킨다.

도 12를 참조하면, 게이트 전극(8)과 마찬가지로, 인이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘(16)과 텅스텐 실리사이드(WSi2)(17)를 CVD법으로 500Å 정도씩 퇴적시켜서, 이층막(18)(폴리 사이드)을 형성한다. 그 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 패턴을 형성한다. 이 폴리 사이드 배선(18)의 선폭 W2는 0.3∼0.5㎛ 정도로, 이것은 DRAM의 비트선으로 되며, 비트선 콘택트 홀(15)을 거쳐 각각 소스/드레인 영역(10a, 1Oc)에 접속된다.

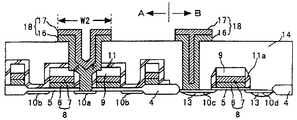

도 13을 참조하면, CVD법으로 3000Å 정도의 실리콘 산화막을 퇴적시켜서 층간 절연막(19)을 형성한다.

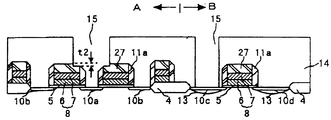

도 14를 참조하면, 사진 제판 및 이방성 산화막 건식 에칭 기술로, 메모리 셀부 A에 있어서 서로 이웃하는 게이트 전극(8) 사이에서, 또한 소스/드레인 영역(10b) 위에서 산화막(19 및 14)에 개구를 형성하고, 계속해서 이방성 질화막 건식 에칭 기술로, 이 개구로부터 산화막(5)과 그 위의 질화막(11)에 개구를 형성하여, 소스/드레인(10b) 위에 지름 0.3㎛ 정도의 저장 노드·콘택트 홀(20)을 형성한다. 이것은 저장 노드와 활성 영역(10b)을 접속하기 위한 콘택트 홀이다.

또, 도 14에 있어서, 저장 노드·콘택트 홀(20)은 그 양측의 게이트(8)의 측면의 질화막(11)에는 접하지 않도록 도시한다. 그러나, 양측의 게이트(8)의 간격이 작은 경우에는, 도 10에 있어서의 비트선 콘택트 홀(15)의 형성과 마찬가지로, 양측의 게이트(8)를 피복하는 질화막(11)에 의해 SAC를 형성하게 된다.

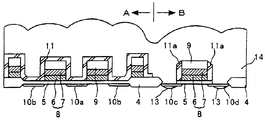

도 15를 참조하면, 인(P)이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘을 7000Å 정도 CVD법으로 퇴적시켜 저장 노드 콘택트 홀(20)을 매립한 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 부분만 인 도프트 폴리 실리콘을 남겨서 저장 노드(21)를 형성한다. 저장 노드(21) 사이의 간격 W3은 저장 노드(21)의 표면적을 크게하기 위해서 가능한 한 좁게 0.25㎛ 정도로 한다. 또한, 저장 노드(21)는 각각 콘택트 홀(20)을 거쳐 메모리 셀부 A의 엷은 농도의 n-소스/드레인 영역(10b)에 접속된다.

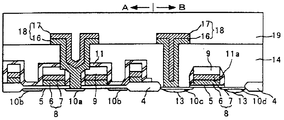

도 16을 참조하면, CVD법으로 캐패시터 유전막으로 되는 실리콘 질화막(22)과, 셀 플레이트(23)로 되는, 인이 5×1020개/㎤ 정도 도핑된 인 도프트 폴리 실리콘(23)을, 각각 60Å/1000Å 정도 연속하여 퇴적시킨다. 사진 제판 및 이방성 건식 에칭 기술로, 메모리 셀부 A 이외의 도핑된 폴리 실리콘(23)을 제거하고 셀 플레이트(23)를 형성함으로써 캐패시터가 완성된다.

도 17을 참조하면, CVD법으로 BPSG를 5000Å 정도 퇴적시켜 층간 절연막(24)을 형성한다.

도 18을 참조하면, 층간 절연막(14)과 마찬가지로 질소 분위기에서 850℃ 정도의 열처리를 약 30분 실시하여 층간 절연막(24)의 표면 형상을 매끄럽게 한다.

도 19를 참조하면, 주변 회로부 B에 있어서, 사진 제판 및 이방성 산화막 건식 에칭 기술로, 소스/드레인(10d)의 위, 게이트 전극(8)의 위, 및 비트선(18)의 위에, 각각 지름 0.3∼0.4㎛ 정도의 콘택트 홀(25)을 형성한다. 이 때, 게이트 전극(8) 위에는 실리콘 산화막(9)이 형성되어 있고, 층간 절연막은 모두 실리콘 산화막(9, 14, 19, 24)이기 때문에, 모든 콘택트 홀(25)을 동시에 형성할 수 있다.

도 20을 참조하면, 스퍼터법으로 알루미늄(26)을 5000Å 정도 퇴적시켜 콘택트 홀(25)을 매립한 후, 사진 제판 및 이방성 건식 에칭 기술로 소망하는 부분을 남기고 선폭 0.4∼0.5㎛ 정도의 알루미늄 배선(26)을 형성한다.

이상과 같이 본 실시예에 의하면, 메모리 셀부 A의 소스/드레인 영역(10b)은, 도 14의 공정에서 저장 콘택트 홀이 형성될 때까지 질화막(11)으로 보호되어 있고, 그 이전 단계에서 에칭에 의해 손상을 받는 일이 없기 때문에, 데이터 유지 특성의 열화를 초래하는 일이 없다. 또한, 주변 회로부에 있어서는 게이트 전극(8) 위에 질화막이 없기 때문에, 도 19에 도시하는 바와 같이 콘택트 홀(25)의 형성이 한 번에 가능하게 된다.

이상의 설명으로부터 명백한 바와 같이, 본 발명의 실시예에 따른 DRAM의 구조는 도 20을 참조하면 다음과 같이 정리된다.

이 DRAM은 반도체 기판(1)의 주표면의 분리 산화막(4)을 사이에 두고, 메모리 셀부 A와 주변회로부 B를 갖는다. 반도체 기판(1)의 주표면에는, MOS 트랜지스터 형성을 위해, 복수의 저 농도의 활성 영역(10a, 1Ob, 10c, 1Od)(소스/드레인 영역)이 형성되어 있다. 또한, 주변 회로부 B에는 저 농도의 활성 영역(10c, 10d)의 하측에 고 농도의 활성 영역(13)(소스/드레인 영역)이 형성되어 있다. 이들 복수의 활성 영역 중 각 한 쌍의 활성 영역 (1Oa)와 (10b) 사이, (10c)와 (10d) 사이 등에 게이트 절연막(5)(제 1 절연막)이 형성되어 있다. 또한, 이 게이트 절연막(5) 위에는, 인 도프트 폴리 실리콘(6)과 텅스텐 실리사이드(7)로 이루어지는 이층막(폴리 사이드)의 게이트 전극(8)(제 1 도전막)이 형성되고, 이 게이트 전극(8) 위에는 실리콘 산화막(9)이 형성되어 있다.

또한, 메모리 셀부 A에 있어서는, 실리콘 산화막(9) 및 게이트 전극(8)의 측면을 피복하도록 반도체 기판의 전면에 실리콘 질화막(11)이 형성되어 있다. 또한, 이 실리콘 질화막(11) 위에는 층간 실리콘 산화막(14)(제 2 절연막)이 형성되어 있다.

또한, 활성 영역(10a) 위에서, 서로 이웃하는 게이트 전극(8) 사이에 있어서, 각 게이트 전극(8)의 측면의 실리콘 질화막(11) 사이에서, 층간 실리콘 산화막(14)과, 게이트 절연막(5) 위의 실리콘 질화막(11)과, 상기 게이트 절연막(5)을 관통하여 활성 영역(10a)에 이르는 콘택트(비트선(18)과의 콘택트)가 형성되어 있다.

또한, 활성 영역(10b) 위에서, 서로 이웃하는 게이트 전극(8) 사이에 있어서, 각 게이트 전극(8)의 측면의 실리콘 질화막(11) 사이에서, 층간 실리콘 산화막(14)과, 게이트 절연막(5) 위의 실리콘 질화막(11)과, 게이트 절연막(5)을 관통하여 활성 영역(10b)에 이르는 콘택트(저장 노드(21)와의 콘택트)가 형성되어있다.

또한, 층간 산화막(14) 위에 비트선(18)이 형성되어 있고, 이 위에 층간 실리콘 산화막(19)이 형성되어 있다. 또한, 층간 실리콘 산화막(19) 위에는 저장 노드(21)가 형성되고, 유전체막(22)을 사이에 두고 셀 플레이트(23)가 형성되며, 캐패시터가 구성되어 있다. 셀 플레이트(23) 위에는 층간 실리콘 산화막(24)이 형성되고, 또한 그 위에는 알루미늄 배선(26)이 배치되어 있다.

한편, 주변 회로부 B에 있어서는, 게이트 전극(8)(제 1 도전막)의 측면에 측벽 형상의 실리콘 질화막(11a)이 형성되어 있다. 그리고, 실리콘 산화막(9) 및 실리콘 질화막(11a)을 피복하도록 반도체 기판의 전면에 층간 실리콘 산화막(14)(제 2 절연막)이 형성되어 있다.

또한, 게이트 전극(8) 위에서, 층간 실리콘 산화막(14)과 실리콘 산화막(9)을 관통하여 게이트 전극(8)에 이르는 게이트 콘택트가 형성되어 있다.

또한, 활성 영역(10d) 위에서, 층간 실리콘 산화막(14)과 게이트 절연막(5)을 관통하여 활성 영역(1Od)에 이르는 콘택트가 형성되어 있다.

또한, 층간 산화막(14) 위에는, 비트선(18)이 형성되어 있으며, 이는 그 비트선 콘택트에 의해 활성 영역(1Oc)에 접속되어 있다.

비트선(18) 위에는, 층간 산화막(19)이 형성되고, 또한 그 위에는 층간 산화막(24)이 형성되어 있다. 이들의 층간 산화막(24, 19)에 개구를 형성하여, 비트선(18)으로의 알루미늄 배선(26)에 의한 콘택트가 형성되어 있다. 앞서 서술한 활성 영역(10d)으로의 콘택트, 및 게이트(8)로의 콘택트는 모두 층간 산화막(24및 19)에 개구를 형성한 콘택트 홀을 거쳐 알루미늄 배선(26)에 의해 콘택트가 취해져 있다.

본 실시예의 DRAM은, 이상과 같이 구성되어 있기 때문에, 메모리 셀부 A의 소스/드레인 영역(10b)은 에칭에 의해 손상을 받는 일이 없으므로 데이터 유지 특성의 열화를 초래하는 일이 없다. 또한, 주변 회로부에 있어서는, 게이트 전극(8) 위에 질화막이 없기 때문에, 콘택트 홀(25)을 한번에 형성할 수 있다.

이상 설명한 바와 같이, 본 발명에 따르면, 에칭에 의해 손상을 받는 일이 없는 콘택트를 구비한 반도체 장치의 제조 방법과 그에 따른 반도체 장치를 얻을 수 있다. 이에 따라, 반도체 기억 장치 등에서의 데이터 유지 특성의 열화를 막을 수 있다. 또한, 다른 영역에 복수의 콘택트를 동시에 형성하여, 공정을 단축시킨 반도체 장치의 제조 방법과 그에 따른 반도체 장치를 얻을 수 있다.

Claims (3)

- 반도체 기판의 주표면에 형성된 복수의 활성 영역과,상기 복수의 활성 영역중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과,상기 제 1 절연막 위에 형성된 제 1 도전막과,상기 제 1 도전막 위에 형성된 실리콘 산화막과,제 1 절연막과 제 1 도전막을 패터닝하여 형성한 게이트 전극과,상기 실리콘 산화막 및 상기 제 1 도전막의 측면을 피복하도록 상기 반도체 기판 전면에 형성된 실리콘 질화막과,상기 실리콘 질화막 위에 형성된 제 2 절연막과,서로 이웃하는 상기 게이트 전극 사이에 있어서 각 게이트 전극의 측면의 실리콘 질화막에 접하지 않도록 상기 제 2 절연막과 상기 제 1 절연막 위의 실리콘 질화막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 포함한 것을 특징으로 하는 반도체 장치.

- 반도체 기판의 주표면에 형성된 복수의 활성 영역과,상기 복수의 활성 영역 중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과,상기 제 1 절연막 위에 형성된 제 1 도전막과,상기 제 1 도전막 위에 형성된 실리콘 산화막과,제 1 절연막과 제 1 도전막을 패터닝하여 형성한 게이트 전극과,상기 제 1 도전막의 측면에 형성된 실리콘 질화막과,상기 실리콘 산화막 및 실리콘 질화막을 피복하도록 상기 반도체 기판 전면에 형성된 제 2 절연막과,상기 게이트 전극 위에서 상기 제 2 절연막과 상기 실리콘 산화막을 관통하여 상기 게이트 전극에 이르는 콘택트와,상기 활성 영역 위에서 상기 제 2 절연막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 포함한 것을 특징으로 하는 반도체 장치.

- 메모리 셀부와 주변 회로부를 갖는 반도체 기판의 주표면에 형성된 복수의 활성 영역과,상기 복수의 활성 영역 중 각 한 쌍의 활성 영역 사이에 형성된 제 1 절연막과,상기 제 1 절연막 위에 형성된 제 1 도전막과,상기 제 1 도전막 위에 형성된 실리콘 산화막과,제 1 절연막과 제 1 도전막을 패터닝하여 형성한 게이트 전극을 포함하고, 또한 상기 메모리 셀부에 있어서,상기 실리콘 산화막 및 상기 제 1 도전막의 측면을 피복하도록 상기 반도체 기판의 전면에 형성된 실리콘 질화막과,상기 실리콘 질화막 위에 형성된 제 2 절연막과,서로 이웃하는 상기 게이트 전극 사이에 있어서 각 게이트 전극의 측면의 실리콘 질화막에 접하지 않도록 상기 제 2 절연막과 상기 제 1 절연막 위의 실리콘 질화막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 포함하며,또한 상기 주변 회로부에 있어서,상기 제 1 도전막 측면에 형성된 실리콘 질화막과,상기 실리콘 산화막 및 상기 실리콘 질화막을 피복하도록 상기 반도체 기판 전면에 형성된 제 2 절연막과,상기 게이트 전극 위에서 상기 제 2 절연막과 상기 실리콘 산화막을 관통하여 상기 게이트 전극에 이르는 콘택트와,상기 활성 영역 위에서 상기 제 2 절연막과 상기 제 1 절연막을 관통하여 상기 활성 영역에 이르는 콘택트를 포함한 것을 특징으로 하는 반도체 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9044094A JPH10242419A (ja) | 1997-02-27 | 1997-02-27 | 半導体装置の製造方法及び半導体装置 |

| JP97-044094 | 1997-02-27 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980069965A KR19980069965A (ko) | 1998-10-26 |

| KR100310565B1 true KR100310565B1 (ko) | 2002-05-09 |

Family

ID=12682043

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970048682A KR100310565B1 (ko) | 1997-02-27 | 1997-09-25 | 반도체장치의제조방법및반도체장치 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6559494B1 (ko) |

| JP (1) | JPH10242419A (ko) |

| KR (1) | KR100310565B1 (ko) |

| CN (1) | CN1097311C (ko) |

| DE (1) | DE19739755A1 (ko) |

| TW (1) | TW365062B (ko) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6798002B1 (en) * | 1999-10-13 | 2004-09-28 | Advanced Micro Devices, Inc. | Dual-purpose anti-reflective coating and spacer for flash memory and other dual gate technologies and method of forming |

| US6274409B1 (en) * | 2000-01-18 | 2001-08-14 | Agere Systems Guardian Corp. | Method for making a semiconductor device |

| KR100338781B1 (ko) * | 2000-09-20 | 2002-06-01 | 윤종용 | 반도체 메모리 소자 및 그의 제조방법 |

| DE10228571A1 (de) * | 2002-06-26 | 2004-01-22 | Infineon Technologies Ag | Herstellungsverfahren für eine Halbleiterstruktur mit einer Mehrzahl von Gatestapeln auf einem Halbleitersubstrat und entsprechende Halbleiterstruktur |

| KR100475084B1 (ko) * | 2002-08-02 | 2005-03-10 | 삼성전자주식회사 | Dram 반도체 소자 및 그 제조방법 |

| DE10243380A1 (de) * | 2002-09-18 | 2004-04-01 | Infineon Technologies Ag | Verfahren zur Herstellung einer integrierten Halbleiterschaltung |

| US6909152B2 (en) * | 2002-11-14 | 2005-06-21 | Infineon Technologies, Ag | High density DRAM with reduced peripheral device area and method of manufacture |

| JP4841106B2 (ja) * | 2003-08-28 | 2011-12-21 | ルネサスエレクトロニクス株式会社 | Mis型半導体装置及びその製造方法 |

| JP5292878B2 (ja) * | 2008-03-26 | 2013-09-18 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| DE102009039421B4 (de) | 2009-08-31 | 2017-09-07 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Doppelkontaktmetallisierung mit stromloser Plattierung in einem Halbleiterbauelement |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06163535A (ja) * | 1992-11-26 | 1994-06-10 | Rohm Co Ltd | 半導体装置およびその製造方法 |

| JPH06177147A (ja) * | 1992-12-10 | 1994-06-24 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JPH07263554A (ja) * | 1994-03-25 | 1995-10-13 | Nec Corp | 半導体装置及びその製造方法 |

| JPH0837145A (ja) * | 1994-07-26 | 1996-02-06 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4818714A (en) * | 1987-12-02 | 1989-04-04 | Advanced Micro Devices, Inc. | Method of making a high performance MOS device having LDD regions with graded junctions |

| JP2859288B2 (ja) * | 1989-03-20 | 1999-02-17 | 株式会社日立製作所 | 半導体集積回路装置及びその製造方法 |

| JPH0824169B2 (ja) * | 1989-05-10 | 1996-03-06 | 富士通株式会社 | 半導体記憶装置の製造方法 |

| JPH04215471A (ja) | 1990-12-14 | 1992-08-06 | Sony Corp | 半導体メモリ |

| US5126280A (en) | 1991-02-08 | 1992-06-30 | Micron Technology, Inc. | Stacked multi-poly spacers with double cell plate capacitor |

| JP2796656B2 (ja) * | 1992-04-24 | 1998-09-10 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP3197064B2 (ja) | 1992-07-17 | 2001-08-13 | 株式会社東芝 | 半導体記憶装置 |

| JP3004177B2 (ja) * | 1993-09-16 | 2000-01-31 | 株式会社東芝 | 半導体集積回路装置 |

| US5441906A (en) * | 1994-04-04 | 1995-08-15 | Motorola, Inc. | Insulated gate field effect transistor having a partial channel and method for fabricating |

| JP2643870B2 (ja) * | 1994-11-29 | 1997-08-20 | 日本電気株式会社 | 半導体記憶装置の製造方法 |

| JPH09107082A (ja) * | 1995-08-09 | 1997-04-22 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

| US5700731A (en) * | 1995-12-07 | 1997-12-23 | Vanguard International Semiconductor Corporation | Method for manufacturing crown-shaped storage capacitors on dynamic random access memory cells |

| JP2765544B2 (ja) * | 1995-12-26 | 1998-06-18 | 日本電気株式会社 | 半導体装置の製造方法 |

| US5567640A (en) * | 1996-01-11 | 1996-10-22 | Vanguard International Semiconductor Corporation | Method for fabricating T-shaped capacitors in DRAM cells |

| US5733808A (en) * | 1996-01-16 | 1998-03-31 | Vanguard International Semiconductor Corporation | Method for fabricating a cylindrical capacitor for a semiconductor device |

| US5554557A (en) | 1996-02-02 | 1996-09-10 | Vanguard International Semiconductor Corp. | Method for fabricating a stacked capacitor with a self aligned node contact in a memory cell |

| US5721154A (en) * | 1996-06-18 | 1998-02-24 | Vanguard International Semiconductor | Method for fabricating a four fin capacitor structure |

| US5668036A (en) * | 1996-06-21 | 1997-09-16 | Vanguard International Semiconductor Corporation | Fabrication method of the post structure of the cell for high density DRAM |

| US5792687A (en) * | 1996-08-01 | 1998-08-11 | Vanguard International Semiconductor Corporation | Method for fabricating high density integrated circuits using oxide and polysilicon spacers |

| US5763311A (en) * | 1996-11-04 | 1998-06-09 | Advanced Micro Devices, Inc. | High performance asymmetrical MOSFET structure and method of making the same |

| US5792681A (en) * | 1997-01-15 | 1998-08-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fabrication process for MOSFET devices and a reproducible capacitor structure |

-

1997

- 1997-02-27 JP JP9044094A patent/JPH10242419A/ja not_active Ceased

- 1997-08-11 US US08/909,309 patent/US6559494B1/en not_active Expired - Fee Related

- 1997-08-21 TW TW086111999A patent/TW365062B/zh active

- 1997-09-10 DE DE19739755A patent/DE19739755A1/de not_active Ceased

- 1997-09-25 KR KR1019970048682A patent/KR100310565B1/ko not_active IP Right Cessation

- 1997-09-25 CN CN97119580A patent/CN1097311C/zh not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06163535A (ja) * | 1992-11-26 | 1994-06-10 | Rohm Co Ltd | 半導体装置およびその製造方法 |

| JPH06177147A (ja) * | 1992-12-10 | 1994-06-24 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| JPH07263554A (ja) * | 1994-03-25 | 1995-10-13 | Nec Corp | 半導体装置及びその製造方法 |

| JPH0837145A (ja) * | 1994-07-26 | 1996-02-06 | Hitachi Ltd | 半導体集積回路装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE19739755A1 (de) | 1998-09-10 |

| KR19980069965A (ko) | 1998-10-26 |

| US6559494B1 (en) | 2003-05-06 |

| CN1192045A (zh) | 1998-09-02 |

| TW365062B (en) | 1999-07-21 |

| CN1097311C (zh) | 2002-12-25 |

| JPH10242419A (ja) | 1998-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100320332B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR100338413B1 (ko) | 이중 작용 기능 도핑 및 보호 절연 캡을 제공하는 방법 | |

| US6312982B1 (en) | Method of fabricating a trench capacitor | |

| JP3545768B2 (ja) | Soi型トランジスタの製造方法 | |

| US5173752A (en) | Semiconductor device having interconnection layer contacting source/drain regions | |

| US6417097B1 (en) | Methods of forming a contact structure in a semiconductor device | |

| KR100310565B1 (ko) | 반도체장치의제조방법및반도체장치 | |

| US6353241B1 (en) | Memory circuitry with spaced conductive lines of different elevational thickness | |

| KR100414382B1 (ko) | 반도체장치의 제조방법 | |

| US6207571B1 (en) | Self-aligned contact formation for semiconductor devices | |

| KR960005249B1 (ko) | 반도체 집적 소자의 디램(dram) 제조방법 | |

| US6245629B1 (en) | Semiconductor structures and manufacturing methods | |

| JP3355511B2 (ja) | 半導体装置の製造方法 | |

| JPH06209088A (ja) | 半導体記憶装置及びその製造方法 | |

| KR920008294B1 (ko) | 반도체 장치의 제조방법 | |

| KR100470164B1 (ko) | 반도체 소자의 콘택 제조 방법 | |

| KR100265370B1 (ko) | 디램제조방법 | |

| KR100418090B1 (ko) | 반도체 소자의 제조 방법 | |

| KR100745063B1 (ko) | 반도체장치의 랜딩 플러그 제조 방법 | |

| KR100668723B1 (ko) | 반도체 메모리 소자 형성방법 | |

| KR100390041B1 (ko) | 디램 메모리 셀의 제조방법 | |

| KR100317196B1 (ko) | 반도체장치의 플러그 형성방법 | |

| KR20000018663A (ko) | 반도체 메모리 소자의 제조 방법 | |

| GB2362756A (en) | Semiconductive device having a self-aligned contact and landing pad structure and method of making same | |

| KR20030063943A (ko) | 플랫 셀 구조의 복합 메모리 장치의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| J201 | Request for trial against refusal decision | ||

| AMND | Amendment | ||

| B701 | Decision to grant | ||

| GRNT | Written decision to grant | ||

| LAPS | Lapse due to unpaid annual fee |