JP6909566B2 - 配線回路基板およびその製造方法 - Google Patents

配線回路基板およびその製造方法 Download PDFInfo

- Publication number

- JP6909566B2 JP6909566B2 JP2016173689A JP2016173689A JP6909566B2 JP 6909566 B2 JP6909566 B2 JP 6909566B2 JP 2016173689 A JP2016173689 A JP 2016173689A JP 2016173689 A JP2016173689 A JP 2016173689A JP 6909566 B2 JP6909566 B2 JP 6909566B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring pattern

- insulating layer

- support substrate

- ground layer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/0218—Reduction of cross-talk, noise or electromagnetic interference by printed shielding conductors, ground planes or power plane

- H05K1/0224—Patterned shielding planes, ground planes or power planes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/05—Insulated conductive substrates, e.g. insulated metal substrate

- H05K1/056—Insulated conductive substrates, e.g. insulated metal substrate the metal substrate being covered by an organic insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/0218—Reduction of cross-talk, noise or electromagnetic interference by printed shielding conductors, ground planes or power plane

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/4806—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed specially adapted for disk drive assemblies, e.g. assembly prior to operation, hard or flexible disk drives

- G11B5/484—Integrated arm assemblies, e.g. formed by material deposition or by etching from single piece of metal or by lamination of materials forming a single arm/suspension/head unit

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/4806—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed specially adapted for disk drive assemblies, e.g. assembly prior to operation, hard or flexible disk drives

- G11B5/486—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed specially adapted for disk drive assemblies, e.g. assembly prior to operation, hard or flexible disk drives with provision for mounting or arranging electrical conducting means or circuits on or along the arm assembly

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/0218—Reduction of cross-talk, noise or electromagnetic interference by printed shielding conductors, ground planes or power plane

- H05K1/0224—Patterned shielding planes, ground planes or power planes

- H05K1/0225—Single or multiple openings in a shielding, ground or power plane

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/0228—Compensation of cross-talk by a mutually correlated lay-out of printed circuit traces, e.g. for compensation of cross-talk in mounted connectors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/025—Impedance arrangements, e.g. impedance matching, reduction of parasitic impedance

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

- H05K1/0298—Multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/05—Insulated conductive substrates, e.g. insulated metal substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4685—Manufacturing of cross-over conductors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/0245—Lay-out of balanced signal pairs, e.g. differential lines or twisted lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0277—Bendability or stretchability details

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0393—Flexible materials

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/05—Insulated conductive substrates, e.g. insulated metal substrate

- H05K1/053—Insulated conductive substrates, e.g. insulated metal substrate the metal substrate being covered by an inorganic insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/09—Use of materials for the conductive, e.g. metallic pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0154—Polyimide

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0183—Dielectric layers

- H05K2201/0187—Dielectric layers with regions of different dielectrics in the same layer, e.g. in a printed capacitor for locally changing the dielectric properties

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0183—Dielectric layers

- H05K2201/0191—Dielectric layers wherein the thickness of the dielectric plays an important role

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0183—Dielectric layers

- H05K2201/0195—Dielectric or adhesive layers comprising a plurality of layers, e.g. in a multilayer structure

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/07—Electric details

- H05K2201/0776—Resistance and impedance

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09227—Layout details of a plurality of traces, e.g. escape layout for Ball Grid Array [BGA] mounting

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09254—Branched layout

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/0929—Conductive planes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/0929—Conductive planes

- H05K2201/093—Layout of power planes, ground planes or power supply conductors, e.g. having special clearance holes therein

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10007—Types of components

- H05K2201/10083—Electromechanical or electro-acoustic component, e.g. microphone

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/05—Patterning and lithography; Masks; Details of resist

- H05K2203/0502—Patterning and lithography

- H05K2203/0514—Photodevelopable thick film, e.g. conductive or insulating paste

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

Description

(1)サスペンション基板の構造

図1は、本発明の第1の実施の形態に係るサスペンション基板の平面図である。図1において、矢印が向かう方向を前方と呼び、その逆方向を後方と呼ぶ。図1に示すように、サスペンション基板1は、サスペンション本体部として例えばステンレス鋼からなる支持基板10を備える。図1においては、支持基板10は、略前後方向に延びている。

書込用配線パターンW1,W2および電源用配線パターンP1の構成について説明する。図2は、図1の書込用配線パターンW1,W2および電源用配線パターンP1の構成を示す模式図である。

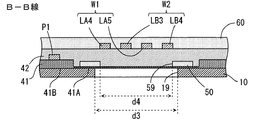

図7は、図2の交差領域CN1の拡大平面図である。図8は、図7のD−D線断面図である。図7では、図4の第1の絶縁層41、第2の絶縁層42および第3の絶縁層60の図示を省略している。また、図7では、書込用配線パターンW1(図2)の線路LA3,LA5および書込用配線パターンW2(図2)の線路LB3を太い実線およびハッチングで示す。また、接地層50を実線およびドットパターンで示す。さらに、支持基板10を二点鎖線で示す。図2の交差領域CN2は、交差領域CN1と同様の構成を有する。

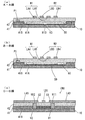

サスペンション基板1の製造方法について説明する。図9〜図15は、図1のサスペンション基板1の製造方法を示す模式的工程断面図である。図9〜図15の各図においては、(a)が図3のA−A線断面図に対応し、(b)が図3のB−B線断面図に対応し、(c)が図7のD−D線断面図に対応する。ここでは、図1のタング部12、複数の接続端子21〜26,31〜36、複数の孔部H、読取用配線パターンR1,R2および電源用配線パターンP2の形成工程についての説明は省略する。

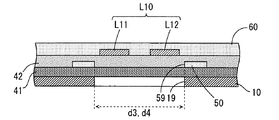

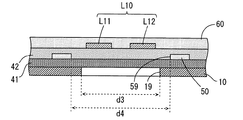

本実施の形態に係るサスペンション基板1においては、支持基板10上に第1の絶縁層41が形成される。第1の絶縁層41の薄肉部41A上に接地層50が形成され、第1の絶縁層41の厚肉部41B上に電源用配線パターンP1が形成される。また、接地層50および電源用配線パターンP1を覆うように第1の絶縁層41上に第2の絶縁層42が形成される。さらに、少なくとも一部が接地層50に重なるように第2の絶縁層42上に書込用配線パターンW1,W2が形成される。この場合、電源用配線パターンP1および書込用配線パターンW1,W2の各々に電気信号を伝送させることができる。

第2の実施の形態に係るサスペンション基板について、第1の実施の形態に係るサスペンション基板1とは異なる点を説明する。図16、図17および図18は、第2の実施の形態に係るサスペンション基板の一部拡大平面図である。図16、図17および図18は、それぞれ図3のA−A線断面図、B−B線断面図およびC−C線断面図に相当する。

(1)上記実施の形態においては、支持基板10の配線部10Xを通して線路LA3と線路LA5とが電気的に接続されるが、本発明はこれに限定されない。図19は、他の実施の形態に係るサスペンション基板のうち図7のD−D線に対応する部分の断面図である。

以下、請求項の各構成要素と実施の形態の各部との対応の例について説明するが、本発明は下記の例に限定されない。

(1)第1の実施の形態についての実施例および比較例

第1の実施の形態についての実施例1,2および比較例1,2として、以下のサスペンション基板を想定する。図20(a)は実施例1に係るサスペンション基板の平面図であり、図20(b)は図20(a)のJ1−J1線断面図である。

第2の実施の形態についての実施例3および比較例3,4として、以下のサスペンション基板を想定する。図26は、実施例3に係るサスペンション基板の断面図である。図26の断面図は、図17のB−B線断面図に対応する。後述する図27および図28においても同様である。

10 支持基板

10X 配線部

10Y 支持部

11 開口部

12 タング部

18 環状開口部

19,59 開口部

21〜26 接続端子

31〜36 接続端子

41,42,60 絶縁層

41A 薄肉部

41B 厚肉部

41p 感光性ポリイミド樹脂前駆体

50 接地層

51 中継パターン

90 支持プレート

91 前端領域

92 後端領域

93 中央領域

94 圧電素子実装領域

94h 貫通孔

95,96 圧電素子

CN1,CN2 交差領域

d1,d2,d13 間隔

d3〜d6 寸法

d11,d14 幅

d12,d15,d20〜d23 厚み

G1,G2 接続部

H 孔部

H1〜H4,H11〜H13 貫通孔

L10 上部配線パターン

L11,L12,LA1〜LA5,LB1〜LB5 線路

L20 下部配線パターン

P1,P2 電源用配線パターン

R1,R2 読取用配線パターン

V1〜V3 ビア

W1,W2 書込用配線パターン

Claims (13)

- 導電性材料により形成される支持基板と、

前記支持基板上に形成される第1の絶縁層と、

前記支持基板に電気的に接続されるように前記第1の絶縁層上に形成され、前記支持基板よりも高い電気伝導率を有する接地層と、

前記第1の絶縁層上に形成される下部配線パターンと、

前記接地層および前記下部配線パターンを覆うように前記第1の絶縁層上に形成される第2の絶縁層と、

前記接地層に重なるように前記第2の絶縁層上に形成される上部配線パターンとを備え、

前記支持基板、前記第1の絶縁層および前記第2の絶縁層の積層方向において、前記接地層と前記上部配線パターンとの間隔は、前記下部配線パターンと前記上部配線パターンとの間隔よりも大きい、配線回路基板。 - 前記第1の絶縁層は、第1の厚みを有する第1の部分と前記第1の厚みよりも大きい第2の厚みを有する第2の部分とを含み、

前記接地層は、前記第1の絶縁層の前記第1の部分上に形成され、

前記下部配線パターンは、前記第1の絶縁層の前記第2の部分上に形成される、請求項1記載の配線回路基板。 - 前記支持基板には、第1の開口部が形成され、

前記接地層には、前記支持基板の前記第1の開口部に重なる第2の開口部が形成され、

前記上部配線パターンの少なくとも一部は、前記接地層の前記第2の開口部に重なる、請求項1または2記載の配線回路基板。 - 前記接地層の前記第2の開口部の寸法は、前記上部配線パターンと前記支持基板との間に前記接地層の一部が存在するように設定される、請求項3記載の配線回路基板。

- 導電性材料により形成される支持基板と、

前記支持基板上に形成される第1の絶縁層と、

前記支持基板に電気的に接続されるように前記第1の絶縁層上に形成され、前記支持基板よりも高い電気伝導率を有する接地層と、

前記接地層を覆うように前記第1の絶縁層上に形成される第2の絶縁層と、

前記接地層に重なるように前記第2の絶縁層上に形成される上部配線パターンとを備え、

前記支持基板には、第1の開口部が形成され、

前記接地層には、前記支持基板の前記第1の開口部に重なる第2の開口部が形成され、

前記上部配線パターンの少なくとも一部は、前記接地層の前記第2の開口部に重なり、

前記接地層の前記第2の開口部の寸法は、前記上部配線パターンと前記支持基板との間に前記接地層の一部が存在するように設定される、配線回路基板。 - 前記上部配線パターンは第1の方向に延び、

前記第2の開口部は、前記第1の方向に並ぶように前記接地層に間欠的に複数形成される、請求項3〜5のいずれか一項に記載の配線回路基板。 - 前記第1および第2の絶縁層を貫通する第1および第2のビアをさらに備え、

前記支持基板は、前記接地層に電気的に接続された支持部と、前記支持部から電気的に絶縁された配線部とを含み、

前記上部配線パターンは、信号線路対を構成する第1および第2の信号線路を含み、

前記第1の信号線路は、第1および第2の分岐線路を含み、

前記第2の信号線路は、互いに電気的に接続された第3および第4の分岐線路を含み、

前記第1の信号線路の前記第1および第2の分岐線路と前記第2の信号線路の前記第3および第4の分岐線路とは、交互に並ぶように配置され、

前記第1のビアは、前記第1の信号線路の前記第1の分岐線路と前記支持基板の前記配線部とを電気的に接続し、

前記第2のビアは、前記第1の信号線路の前記第2の分岐線路と前記支持基板の前記配線部とを電気的に接続する、請求項1〜6のいずれか一項に記載の配線回路基板。 - 前記第1の絶縁層上に形成される中継パターンと、

前記第2の絶縁層を貫通する第1および第2のビアをさらに備え、

前記上部配線パターンは、信号線路対を構成する第1および第2の信号線路を含み、

前記第1の信号線路は、第1および第2の分岐線路を含み、

前記第2の信号線路は、互いに電気的に接続された第3および第4の分岐線路を含み、

前記第1の信号線路の前記第1および第2の分岐線路と前記第2の信号線路の前記第3および第4の分岐線路とは、交互に並ぶように配置され、

前記第1のビアは、前記第1の信号線路の前記第1の分岐線路と前記中継パターンとを電気的に接続し、

前記第2のビアは、前記第1の信号線路の前記第2の分岐線路と前記中継パターンとを電気的に接続する、請求項1〜6のいずれか一項に記載の配線回路基板。 - 前記第1の絶縁層を貫通して前記接地層と前記支持基板とを電気的に接続する第3のビアをさらに備える、請求項1〜8のいずれか一項に記載の配線回路基板。

- 前記支持基板はステンレスを含み、前記接地層は銅を含む、請求項1〜9のいずれか一項に記載の配線回路基板。

- 前記上部配線パターンを覆うように前記第2の絶縁層上に形成される第3の絶縁層をさらに備える、請求項1〜10のいずれか一項に記載の配線回路基板。

- 導電性材料により形成される支持基板上に積層された第1の絶縁層を準備するステップと、

前記支持基板に電気的に接続されるように前記第1の絶縁層上に前記支持基板よりも高い電気伝導率を有する接地層を形成し、前記第1の絶縁層上に下部配線パターンを形成するステップと、

前記接地層および前記下部配線パターンを覆うように前記第1の絶縁層上に第2の絶縁層を形成するステップと、

前記接地層に重なるように前記第2の絶縁層上に上部配線パターンを形成するステップとを含み、

前記接地層および前記下部配線パターンを形成するステップは、前記支持基板、前記第1の絶縁層および前記第2の絶縁層の積層方向において、前記接地層と前記上部配線パターンとの間隔が前記下部配線パターンと前記上部配線パターンとの間隔よりも大きくなるように前記接地層および前記下部配線パターンを形成することを含む、配線回路基板の製造方法。 - 導電性材料により形成される支持基板上に積層された第1の絶縁層を準備するステップと、

前記支持基板に電気的に接続されるように前記第1の絶縁層上に前記支持基板よりも高い電気伝導率を有する接地層を形成するステップと、

前記接地層を覆うように前記第1の絶縁層上に第2の絶縁層を形成するステップと、

前記接地層に重なるように前記第2の絶縁層上に上部配線パターンを形成するステップと、

前記支持基板に第1の開口部を形成するステップと、

前記接地層に前記支持基板の前記第1の開口部に重なる第2の開口部を形成するステップとを含み、

前記上部配線パターンを形成するステップは、前記上部配線パターンの少なくとも一部が前記接地層の前記第2の開口部に重なるように前記上部配線パターンを形成することを含み、

前記第2の開口部を形成するステップは、前記上部配線パターンと前記支持基板との間に前記接地層の一部が存在するように前記第2の開口部の寸法を設定することを含む、配線回路基板の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016173689A JP6909566B2 (ja) | 2016-09-06 | 2016-09-06 | 配線回路基板およびその製造方法 |

| CN201710795624.0A CN107801294B (zh) | 2016-09-06 | 2017-09-06 | 布线电路基板及其制造方法 |

| US15/696,270 US10327327B2 (en) | 2016-09-06 | 2017-09-06 | Printed circuit board and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016173689A JP6909566B2 (ja) | 2016-09-06 | 2016-09-06 | 配線回路基板およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018041795A JP2018041795A (ja) | 2018-03-15 |

| JP2018041795A5 JP2018041795A5 (ja) | 2019-09-12 |

| JP6909566B2 true JP6909566B2 (ja) | 2021-07-28 |

Family

ID=61281538

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016173689A Active JP6909566B2 (ja) | 2016-09-06 | 2016-09-06 | 配線回路基板およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10327327B2 (ja) |

| JP (1) | JP6909566B2 (ja) |

| CN (1) | CN107801294B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3261417A1 (en) * | 2016-06-22 | 2017-12-27 | OSRAM GmbH | A support structure for lighting devices, corresponding lighting device and method |

| CN113811442B (zh) * | 2019-05-30 | 2024-01-02 | 松下知识产权经营株式会社 | 构造体、系统及构造物 |

| US20210392742A1 (en) * | 2020-06-11 | 2021-12-16 | Innogrit Technologies Co., Ltd. | Embedded microstrip with open slot for high speed signal traces |

| KR20220097718A (ko) * | 2020-12-31 | 2022-07-08 | 삼성전자주식회사 | 배선 기판 및 이를 포함하는 반도체 모듈 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3891912B2 (ja) | 2002-10-09 | 2007-03-14 | 日本発条株式会社 | ディスクドライブ用サスペンション |

| JP4222882B2 (ja) * | 2003-06-03 | 2009-02-12 | 日東電工株式会社 | 配線回路基板 |

| JP4403090B2 (ja) | 2005-03-02 | 2010-01-20 | 日東電工株式会社 | 配線回路基板 |

| JP4640802B2 (ja) * | 2005-07-07 | 2011-03-02 | 日東電工株式会社 | 回路付サスペンション基板 |

| JP4339834B2 (ja) * | 2005-08-23 | 2009-10-07 | 日東電工株式会社 | 回路付サスペンション基板の製造方法 |

| JP4611159B2 (ja) * | 2005-09-20 | 2011-01-12 | 日東電工株式会社 | 配線回路基板 |

| JP4330580B2 (ja) * | 2005-12-09 | 2009-09-16 | 日本発條株式会社 | 多層グランド層のヘッド・サスペンション及びその製造方法、多層グランド層のフレキシャ及びその製造方法 |

| JP2008034639A (ja) | 2006-07-28 | 2008-02-14 | Nitto Denko Corp | 配線回路基板 |

| JP2008282995A (ja) | 2007-05-10 | 2008-11-20 | Nitto Denko Corp | 配線回路基板 |

| JP4960918B2 (ja) * | 2008-04-02 | 2012-06-27 | 日東電工株式会社 | 配線回路基板 |

| JP5388071B2 (ja) * | 2008-06-06 | 2014-01-15 | 国立大学法人東北大学 | 多層配線基板 |

| JP5139169B2 (ja) | 2008-06-20 | 2013-02-06 | 日東電工株式会社 | 配線回路基板およびその製造方法 |

| JP4547035B2 (ja) * | 2008-11-10 | 2010-09-22 | 日東電工株式会社 | 配線回路基板およびその製造方法 |

| CN101908344B (zh) * | 2009-06-02 | 2015-03-04 | 日东电工株式会社 | 布线电路基板 |

| JP5870496B2 (ja) * | 2011-03-18 | 2016-03-01 | 大日本印刷株式会社 | サスペンション用フレキシャー基板、サスペンション、ヘッド付サスペンション、およびハードディスクドライブ |

| JP5861274B2 (ja) * | 2011-05-24 | 2016-02-16 | 大日本印刷株式会社 | サスペンション用フレキシャー基板、サスペンション、ヘッド付サスペンション、およびハードディスクドライブ |

| JP2014049170A (ja) * | 2012-09-04 | 2014-03-17 | Dainippon Printing Co Ltd | サスペンション用基板、サスペンション、素子付サスペンション、ハードディスクドライブおよびそれらの製造方法 |

| JP6407511B2 (ja) * | 2013-09-05 | 2018-10-17 | 日東電工株式会社 | 配線回路基板の導通検査方法および配線回路基板の製造方法 |

| JP6808266B2 (ja) * | 2016-05-18 | 2021-01-06 | 日東電工株式会社 | 配線回路基板およびその製造方法 |

-

2016

- 2016-09-06 JP JP2016173689A patent/JP6909566B2/ja active Active

-

2017

- 2017-09-06 CN CN201710795624.0A patent/CN107801294B/zh active Active

- 2017-09-06 US US15/696,270 patent/US10327327B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018041795A (ja) | 2018-03-15 |

| CN107801294A (zh) | 2018-03-13 |

| US20180070438A1 (en) | 2018-03-08 |

| US10327327B2 (en) | 2019-06-18 |

| CN107801294B (zh) | 2022-04-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6909566B2 (ja) | 配線回路基板およびその製造方法 | |

| JP6627648B2 (ja) | 回路基板及びこれを用いた電子回路モジュール | |

| JP5249870B2 (ja) | 配線回路基板およびその製造方法 | |

| JP3397707B2 (ja) | 伝送時間とインピーダンス制御のための各種開口パターンのあるシールド平面を具えた基板 | |

| CN107306475B (zh) | 布线电路基板和其制造方法 | |

| US9301386B2 (en) | Printed circuit board and method of manufacturing the same | |

| US9940957B2 (en) | Printed circuit board and method of manufacturing the same | |

| JP2011198402A (ja) | サスペンション用フレキシャー基板、サスペンション、ヘッド付サスペンション、およびハードディスクドライブ | |

| JP2003008154A (ja) | 印刷配線板、同軸ケーブル及び電子装置 | |

| JP5669499B2 (ja) | プリント回路板 | |

| US10154579B2 (en) | Printed circuit board and method of manufacturing the same | |

| JP7021329B2 (ja) | 配線回路基板およびその製造方法 | |

| JP4083142B2 (ja) | 半導体装置 | |

| JP6807180B2 (ja) | 配線回路基板およびその製造方法 | |

| JP2010010550A (ja) | 電子部品の実装構造 | |

| JP2006049496A (ja) | 印刷配線板 | |

| JP2012243857A (ja) | プリント基板及びプリント基板の製造方法 | |

| JP5469261B2 (ja) | 配線回路基板およびその製造方法 | |

| JP2006114623A (ja) | 基板モジュール及び印刷配線板並びにこれを用いた電子装置 | |

| CN117677029A (zh) | 信号传输结构及制作方法 | |

| JP2021132074A (ja) | コイル部品及びこれを備える回路基板 | |

| KR100954991B1 (ko) | 전송선 임피던스 매칭 | |

| JP2002368353A (ja) | プリント配線板 | |

| JP2009147100A (ja) | 多層プリント配線板 | |

| JP2006156911A (ja) | プリント配線基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190731 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190731 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200427 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200602 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201215 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210615 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210705 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6909566 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |