JP6632302B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP6632302B2 JP6632302B2 JP2015197091A JP2015197091A JP6632302B2 JP 6632302 B2 JP6632302 B2 JP 6632302B2 JP 2015197091 A JP2015197091 A JP 2015197091A JP 2015197091 A JP2015197091 A JP 2015197091A JP 6632302 B2 JP6632302 B2 JP 6632302B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- wiring layer

- insulating layer

- semiconductor chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 28

- 239000010410 layer Substances 0.000 claims description 450

- 239000004065 semiconductor Substances 0.000 claims description 70

- 239000011241 protective layer Substances 0.000 claims description 55

- 238000000034 method Methods 0.000 claims description 38

- 229910052751 metal Inorganic materials 0.000 claims description 33

- 239000002184 metal Substances 0.000 claims description 33

- 238000007788 roughening Methods 0.000 claims description 28

- 238000005530 etching Methods 0.000 claims description 20

- 239000000463 material Substances 0.000 claims description 12

- 238000010030 laminating Methods 0.000 claims description 2

- 230000000149 penetrating effect Effects 0.000 claims description 2

- 239000011888 foil Substances 0.000 description 62

- 229910000679 solder Inorganic materials 0.000 description 52

- 239000011347 resin Substances 0.000 description 35

- 229920005989 resin Polymers 0.000 description 35

- 239000010949 copper Substances 0.000 description 32

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 28

- 229910052802 copper Inorganic materials 0.000 description 23

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 22

- 238000012986 modification Methods 0.000 description 20

- 230000004048 modification Effects 0.000 description 20

- 230000004888 barrier function Effects 0.000 description 17

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 16

- 239000007864 aqueous solution Substances 0.000 description 15

- 238000010586 diagram Methods 0.000 description 12

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 10

- 239000010408 film Substances 0.000 description 10

- 229910052759 nickel Inorganic materials 0.000 description 9

- 238000009713 electroplating Methods 0.000 description 8

- 239000000243 solution Substances 0.000 description 8

- 230000000694 effects Effects 0.000 description 7

- -1 and for example Substances 0.000 description 6

- 239000000758 substrate Substances 0.000 description 6

- 238000007772 electroless plating Methods 0.000 description 5

- 230000003647 oxidation Effects 0.000 description 5

- 238000007254 oxidation reaction Methods 0.000 description 5

- 238000007747 plating Methods 0.000 description 5

- 229920001187 thermosetting polymer Polymers 0.000 description 5

- LCPVQAHEFVXVKT-UHFFFAOYSA-N 2-(2,4-difluorophenoxy)pyridin-3-amine Chemical compound NC1=CC=CN=C1OC1=CC=C(F)C=C1F LCPVQAHEFVXVKT-UHFFFAOYSA-N 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- ROOXNKNUYICQNP-UHFFFAOYSA-N ammonium peroxydisulfate Substances [NH4+].[NH4+].[O-]S(=O)(=O)OOS([O-])(=O)=O ROOXNKNUYICQNP-UHFFFAOYSA-N 0.000 description 4

- VAZSKTXWXKYQJF-UHFFFAOYSA-N ammonium persulfate Chemical compound [NH4+].[NH4+].[O-]S(=O)OOS([O-])=O VAZSKTXWXKYQJF-UHFFFAOYSA-N 0.000 description 4

- 229910001870 ammonium persulfate Inorganic materials 0.000 description 4

- CHQMHPLRPQMAMX-UHFFFAOYSA-L sodium persulfate Substances [Na+].[Na+].[O-]S(=O)(=O)OOS([O-])(=O)=O CHQMHPLRPQMAMX-UHFFFAOYSA-L 0.000 description 4

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 229910000365 copper sulfate Inorganic materials 0.000 description 3

- ARUVKPQLZAKDPS-UHFFFAOYSA-L copper(II) sulfate Chemical compound [Cu+2].[O-][S+2]([O-])([O-])[O-] ARUVKPQLZAKDPS-UHFFFAOYSA-L 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 230000002265 prevention Effects 0.000 description 3

- 238000003672 processing method Methods 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 239000000654 additive Substances 0.000 description 2

- 229920006231 aramid fiber Polymers 0.000 description 2

- 239000003365 glass fiber Substances 0.000 description 2

- RAXXELZNTBOGNW-UHFFFAOYSA-N imidazole Natural products C1=CNC=N1 RAXXELZNTBOGNW-UHFFFAOYSA-N 0.000 description 2

- 239000004745 nonwoven fabric Substances 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 238000003825 pressing Methods 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 239000002759 woven fabric Substances 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N 1H-pyrrole Natural products C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 1

- JYLNVJYYQQXNEK-UHFFFAOYSA-N 3-amino-2-(4-chlorophenyl)-1-propanesulfonic acid Chemical compound OS(=O)(=O)CC(CN)C1=CC=C(Cl)C=C1 JYLNVJYYQQXNEK-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000003287 bathing Methods 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- XLJMAIOERFSOGZ-UHFFFAOYSA-M cyanate Chemical compound [O-]C#N XLJMAIOERFSOGZ-UHFFFAOYSA-M 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 150000003949 imides Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 239000012286 potassium permanganate Substances 0.000 description 1

- 239000003755 preservative agent Substances 0.000 description 1

- 230000002335 preservative effect Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 239000002335 surface treatment layer Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/528—Geometry or layout of the interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being of a type provided for in group H01L27/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1058—Bump or bump-like electrical connections, e.g. balls, pillars, posts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Description

[第1の実施の形態に係る配線基板の構造]

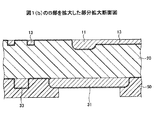

まず、第1の実施の形態に係る配線基板の構造について説明する。図1は、第1の実施の形態に係る配線基板を例示する図であり、図1(a)は部分平面図、図1(b)は図1(a)のA−A線に沿う断面図である。なお、図1(a)では、便宜上、配線層10を梨地模様で示している。

次に、第1の実施の形態に係る配線基板の製造方法について説明する。図3〜図6は、第1の実施の形態に係る配線基板の製造工程を例示する図である。本実施の形態では、支持体上に複数の配線基板となる部分を作製し支持体を除去後個片化して各配線基板とする工程の例を示すが、支持体上に1個ずつ配線基板を作製し支持体を除去する工程としてもよい。

第1の実施の形態の変形例1では、配線基板1の製造方法の他の例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第1の実施の形態の変形例2では、配線基板1の製造方法の更に他の例を示す。なお、第1の実施の形態の変形例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第1の実施の形態の変形例3では、配線基板1の製造方法の更に他の例を示す。なお、第1の実施の形態の変形例3において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第2の実施の形態では、3層構造の配線基板の例を示す。なお、第2の実施の形態において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

配線基板の応用例1では、第1の実施の形態に係る配線基板に半導体チップが搭載(フリップチップ実装)された半導体パッケージの例を示す。なお、配線基板の応用例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

配線基板の応用例2では、半導体パッケージ上に更に他の半導体パッケージが搭載された所謂POP(Package on package)構造の半導体パッケージの例を示す。なお、配線基板の応用例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

3、4、5 半導体パッケージ

10 配線層

11、12、31、71 パッド

13、33、73 配線パターン

20、60 絶縁層

20x、60x ビアホール

30、70 配線層

40、50 ソルダーレジスト層

40x、50x 開口部

90、110 バンプ

100 半導体チップ

120 アンダーフィル樹脂

300、300A 支持体

310 プリプレグ

320、320A キャリア付き金属箔

321、321A 薄箔

322 厚箔

330 バリア層

335 保護層

340 レジスト層

345 マスク

Claims (12)

- 半導体チップ搭載面と、前記半導体チップ搭載面の反対面である外部接続面と、を有する配線基板であって、

前記半導体チップ搭載面側の最外の配線層となる第1配線層と、

前記外部接続面側の最外の配線層となる第2配線層と、

前記第1配線層と前記第2配線層との間に形成された絶縁層と、を有し、

前記第1配線層は、半導体チップ搭載用パッドと、前記半導体チップ搭載用パッドから延出する第1配線パターンと、を含み、

前記第1配線層は単一の金属層からなり、

前記第1配線層は、前記絶縁層に埋め込まれており、前記絶縁層の前記半導体チップ搭載面側の面から露出する第1露出面と、前記絶縁層に被覆された側面と、前記絶縁層に被覆された前記第1露出面の反対面と、を備え、

前記第1配線層の側面全体が粗面であり、

前記第1配線層において、前記第1露出面の粗度は、前記側面の粗度よりも小さく、

前記第1露出面の粗度は、前記絶縁層の前記外部接続面側の面から露出する前記第2配線層の第2露出面の粗度よりも小さいことを特徴とする配線基板。 - 半導体チップ搭載面と、前記半導体チップ搭載面の反対面である外部接続面と、を有する配線基板であって、

前記半導体チップ搭載面側の最外の配線層となる第1配線層と、

前記外部接続面側の最外の配線層となる第2配線層と、

前記第1配線層と前記第2配線層との間に形成された絶縁層と、を有し、

前記第1配線層は単一の金属層からなり、

前記第1配線層は、第1の部分と、前記第1の部分よりも幅が広い第2の部分と、を備え、

前記第1の部分は、前記第2の部分よりも層厚が薄く形成され、

前記第1の部分が第1配線パターンを含み、前記第2の部分が半導体チップ搭載用パッドを含み、

前記第2配線層は、前記絶縁層を貫通して前記第2の部分と接続されるビア配線を備え、

前記絶縁層の前記半導体チップ搭載面側の面から露出する前記第1配線層の第1露出面の粗度は、前記絶縁層の前記外部接続面側の面から露出する前記第2配線層の第2露出面の粗度よりも小さいことを特徴とする配線基板。 - 前記第2の部分が、前記ビア配線が接続されるビア配線接続用パッドを含むことを特徴とする請求項2に記載の配線基板。

- 前記第1露出面は、前記絶縁層の前記半導体チップ搭載面側の面と面一であることを特徴とする請求項1乃至3の何れか一項に記載の配線基板。

- 前記第2配線層は、第2配線パターンを含み、

前記第1配線パターンのライン/スペースは、前記第2配線パターンのライン/スペースよりも小さいことを特徴とする請求項1乃至4の何れか一項に記載の配線基板。 - 前記第1露出面の粗度は、前記絶縁層の前記半導体チップ搭載面側の面の粗度よりも小さいことを特徴とする請求項1乃至5の何れか一項に記載の配線基板。

- 前記第2配線層の一部は、前記絶縁層の前記外部接続面側の面上に形成されており、

前記第2配線層において、前記第2露出面は、前記絶縁層の前記外部接続面側の面に接する面の反対面、及び側面であることを特徴とする請求項1乃至6の何れか一項に記載の配線基板。 - 前記第1配線層及び前記第2配線層を含む複数の配線層と、前記絶縁層を含む複数の絶縁層とが積層され、

前記第1配線層は、前記半導体チップ搭載面を有する絶縁層に埋め込まれており、

前記第2配線層は、前記外部接続面を有する絶縁層に設けられている請求項1乃至7の何れか一項に記載の配線基板。 - 半導体チップ搭載面と、前記半導体チップ搭載面の反対面である外部接続面と、を有する配線基板の製造方法であって、

支持体上に、前記半導体チップ搭載面側の最外の配線層となる第1配線層を形成する工程と、

前記第1配線層の前記支持体側を向く面以外の面全体に第1の粗化処理を施す工程と、

前記第1配線層を被覆するように、前記支持体上に絶縁層を形成する工程と、

前記絶縁層上に、前記外部接続面側の最外の配線層となる第2配線層を形成する工程と、

前記第2配線層の前記絶縁層側の面以外の面に第2の粗化処理を施す工程と、

前記支持体を除去する工程と、を有し、

前記第1配線層は単一の金属層からなり、

前記第1配線層は、前記絶縁層に埋め込まれ、前記第1配線層の前記支持体側を向く面が、前記絶縁層の前記半導体チップ搭載面側の面から露出する前記第1配線層の第1露出面となり、前記第1配線層の側面と前記第1露出面の反対面が前記絶縁層に被覆され、

前記第1配線層の側面全体が粗面であり、

前記第1配線層において、前記第1露出面の粗度は、前記側面の粗度よりも小さく、

前記第2配線層の前記絶縁層と接する面以外の面が、前記絶縁層の前記外部接続面側の面から露出する前記第2配線層の第2露出面となり、

前記第1露出面の粗度は、前記第2露出面の粗度よりも小さいことを特徴とする配線基板の製造方法。 - 前記支持体上に第1配線層を形成する工程は、

前記支持体上に保護層を形成する工程と、

前記保護層上に前記第1配線層を形成する工程と、を含み、

前記保護層と前記第2配線層とは同一材料からなり、

前記保護層を除去する工程を有し、

前記保護層を除去する工程では、エッチングにより、前記保護層を除去すると同時に、前記第2配線層の前記絶縁層と接する面以外の面に前記第2の粗化処理を施すことを特徴とする請求項9に記載の配線基板の製造方法。 - 前記第1の粗化処理を施す工程では、前記第1配線層の前記保護層と接する面以外の面に粗化処理を施すと同時に、前記保護層の表面に粗化処理を施し、

前記保護層を除去する工程では、前記保護層の表面と接していた前記絶縁層の面に、前記保護層の凹凸が転写されることを特徴とする請求項10に記載の配線基板の製造方法。 - 前記絶縁層を形成する工程と前記第2配線層を形成する工程との間に、前記絶縁層上に一層以上の他の配線層と一層以上の他の絶縁層とを積層する工程を有し、

前記第1配線層を形成する工程では、前記支持体に接する前記絶縁層に前記半導体チップ搭載面が設けられると共に、前記第1配線層が前記絶縁層に埋め込まれ、

前記第2配線層を形成する工程では、最上層に設けられた絶縁層に前記外部接続面が設けられると共に、前記第2配線層が形成される請求項9乃至11の何れか一項に記載の配線基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015197091A JP6632302B2 (ja) | 2015-10-02 | 2015-10-02 | 配線基板及びその製造方法 |

| US15/244,197 US9911695B2 (en) | 2015-10-02 | 2016-08-23 | Wiring board including multiple wiring layers that are different in surface roughness |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015197091A JP6632302B2 (ja) | 2015-10-02 | 2015-10-02 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017069524A JP2017069524A (ja) | 2017-04-06 |

| JP2017069524A5 JP2017069524A5 (ja) | 2018-10-04 |

| JP6632302B2 true JP6632302B2 (ja) | 2020-01-22 |

Family

ID=58448046

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015197091A Active JP6632302B2 (ja) | 2015-10-02 | 2015-10-02 | 配線基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9911695B2 (ja) |

| JP (1) | JP6632302B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| ES2573137T3 (es) * | 2012-09-14 | 2016-06-06 | Atotech Deutschland Gmbh | Método de metalización de sustratos de célula solar |

| JP2018006391A (ja) * | 2016-06-28 | 2018-01-11 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US11871525B2 (en) | 2019-03-15 | 2024-01-09 | Kyocera Corporation | Wiring board and manufacturing method for same |

| JP2022119418A (ja) * | 2021-02-04 | 2022-08-17 | イビデン株式会社 | 配線基板及び配線基板の製造方法 |

| KR20220154555A (ko) * | 2021-05-13 | 2022-11-22 | 엘지이노텍 주식회사 | 회로기판 및 이를 포함하는 패키지 기판 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4108643B2 (ja) * | 2004-05-12 | 2008-06-25 | 日本電気株式会社 | 配線基板及びそれを用いた半導体パッケージ |

| JP2008091638A (ja) * | 2006-10-02 | 2008-04-17 | Nec Electronics Corp | 電子装置およびその製造方法 |

| JP5203108B2 (ja) * | 2008-09-12 | 2013-06-05 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP5580374B2 (ja) * | 2012-08-23 | 2014-08-27 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP2014229698A (ja) * | 2013-05-21 | 2014-12-08 | イビデン株式会社 | 配線板及び配線板の製造方法 |

| JP6266907B2 (ja) * | 2013-07-03 | 2018-01-24 | 新光電気工業株式会社 | 配線基板及び配線基板の製造方法 |

| JP6131135B2 (ja) | 2013-07-11 | 2017-05-17 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP6220799B2 (ja) * | 2015-02-03 | 2017-10-25 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

-

2015

- 2015-10-02 JP JP2015197091A patent/JP6632302B2/ja active Active

-

2016

- 2016-08-23 US US15/244,197 patent/US9911695B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20170098600A1 (en) | 2017-04-06 |

| US9911695B2 (en) | 2018-03-06 |

| JP2017069524A (ja) | 2017-04-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5203108B2 (ja) | 配線基板及びその製造方法 | |

| JP6133227B2 (ja) | 配線基板及びその製造方法 | |

| US9515018B2 (en) | Wiring substrate and method for manufacturing wiring substrate | |

| JP5649490B2 (ja) | 配線基板及びその製造方法 | |

| JP6632302B2 (ja) | 配線基板及びその製造方法 | |

| JP5570855B2 (ja) | 配線基板及びその製造方法並びに半導体装置及びその製造方法 | |

| JP6158676B2 (ja) | 配線基板、半導体装置及び配線基板の製造方法 | |

| JP6223909B2 (ja) | 配線基板及びその製造方法 | |

| JP5580374B2 (ja) | 配線基板及びその製造方法 | |

| US10892216B2 (en) | Wiring substrate and semiconductor device | |

| JP2013214578A (ja) | 配線板及びその製造方法 | |

| US20140097009A1 (en) | Wiring substrate | |

| JP6510884B2 (ja) | 配線基板及びその製造方法と電子部品装置 | |

| JP2018026437A (ja) | 配線基板及びその製造方法 | |

| JP2006339186A (ja) | 配線基板およびその製造方法 | |

| JP2015159197A (ja) | 配線基板及びその製造方法 | |

| JP2020191388A (ja) | 配線基板、及び配線基板の製造方法 | |

| JP6671256B2 (ja) | 配線基板及びその製造方法 | |

| JP6689691B2 (ja) | 配線基板及びその製造方法 | |

| JP6457881B2 (ja) | 配線基板及びその製造方法 | |

| JP2019212692A (ja) | 配線基板及びその製造方法 | |

| JP6082233B2 (ja) | 配線板及びその製造方法 | |

| JP2010067888A (ja) | 配線基板及びその製造方法 | |

| JP6392140B2 (ja) | 配線基板及び半導体パッケージ | |

| JP5315447B2 (ja) | 配線基板及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180820 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180820 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190419 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190507 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190619 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190827 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191028 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20191126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20191210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6632302 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |