JP6689691B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP6689691B2 JP6689691B2 JP2016137740A JP2016137740A JP6689691B2 JP 6689691 B2 JP6689691 B2 JP 6689691B2 JP 2016137740 A JP2016137740 A JP 2016137740A JP 2016137740 A JP2016137740 A JP 2016137740A JP 6689691 B2 JP6689691 B2 JP 6689691B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- wiring board

- insulating layer

- pad

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

- H10W70/635—Through-vias

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/111—Pads for surface mounting, e.g. lay-out

- H05K1/112—Pads for surface mounting, e.g. lay-out directly combined with via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

- H05K1/116—Lands, clearance holes or other lay-out details concerning the surrounding of a via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/007—Manufacture or processing of a substrate for a printed circuit board supported by a temporary or sacrificial carrier

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4611—Manufacturing multilayer circuits by laminating two or more circuit boards

- H05K3/4614—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination

- H05K3/4617—Manufacturing multilayer circuits by laminating two or more circuit boards the electrical connections between the circuit boards being made during lamination characterized by laminating only or mainly similar single-sided circuit boards

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/68—Shapes or dispositions thereof

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in printed circuit boards [PCB], e.g. insert-mounted components [IMC]

- H05K1/185—Printed circuits structurally associated with non-printed electric components associated with components mounted in printed circuit boards [PCB], e.g. insert-mounted components [IMC] associated with components encapsulated in the insulating substrate of the PCBs; associated with components incorporated in internal layers of multilayer circuit boards

- H05K1/186—Printed circuits structurally associated with non-printed electric components associated with components mounted in printed circuit boards [PCB], e.g. insert-mounted components [IMC] associated with components encapsulated in the insulating substrate of the PCBs; associated with components incorporated in internal layers of multilayer circuit boards manufactured by mounting on or connecting to patterned circuits before or during embedding

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0364—Conductor shape

- H05K2201/0376—Flush conductors, i.e. flush with the surface of the printed circuit

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09736—Varying thickness of a single conductor; Conductors in the same plane having different thicknesses

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09745—Recess in conductor, e.g. in pad or in metallic substrate

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09854—Hole or via having special cross-section, e.g. elliptical

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/09863—Concave hole or via

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/20—Details of printed circuits not provided for in H05K2201/01 - H05K2201/10

- H05K2201/2072—Anchoring, i.e. one structure gripping into another

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

- H05K3/4053—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques

- H05K3/4069—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques for via connections in organic insulating substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/7424—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support used as a support during the manufacture of self-supporting substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/743—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support used as a support during manufacture of interconnect decals or build up layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/0198—Manufacture or treatment batch processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07202—Connecting or disconnecting of bump connectors using auxiliary members

- H10W72/07204—Connecting or disconnecting of bump connectors using auxiliary members using temporary auxiliary members, e.g. sacrificial coatings

- H10W72/07207—Temporary substrates, e.g. removable substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07231—Techniques

- H10W72/07236—Soldering or alloying

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/073—Connecting or disconnecting of die-attach connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/073—Connecting or disconnecting of die-attach connectors

- H10W72/07302—Connecting or disconnecting of die-attach connectors using an auxiliary member

- H10W72/07304—Connecting or disconnecting of die-attach connectors using an auxiliary member the auxiliary member being temporary, e.g. a sacrificial coating

- H10W72/07307—Connecting or disconnecting of die-attach connectors using an auxiliary member the auxiliary member being temporary, e.g. a sacrificial coating the auxiliary member being a temporary substrate, e.g. a removable substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/221—Structures or relative sizes

- H10W72/225—Bumps having a filler embedded in a matrix

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/251—Materials

- H10W72/252—Materials comprising solid metals or solid metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/251—Materials

- H10W72/253—Materials not comprising solid metals or solid metalloids, e.g. polymers or ceramics

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/30—Die-attach connectors

- H10W72/321—Structures or relative sizes of die-attach connectors

- H10W72/325—Die-attach connectors having a filler embedded in a matrix

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/30—Die-attach connectors

- H10W72/351—Materials of die-attach connectors

- H10W72/353—Materials of die-attach connectors not comprising solid metals or solid metalloids, e.g. ceramics

- H10W72/354—Materials of die-attach connectors not comprising solid metals or solid metalloids, e.g. ceramics comprising polymers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/15—Encapsulations, e.g. protective coatings characterised by their shape or disposition on active surfaces of flip-chip devices, e.g. underfills

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/734—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W99/00—Subject matter not provided for in other groups of this subclass

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

- Manufacturing Of Printed Wiring (AREA)

Description

[第1の実施の形態に係る配線基板の構造]

まず、第1の実施の形態に係る配線基板の構造について説明する。図1は、第1の実施の形態に係る配線基板を例示する図であり、図1(a)は部分平面図、図1(b)は図1(a)のA−A線に沿う断面図である。なお、図1(a)では、便宜上、配線層10を梨地模様で示している。

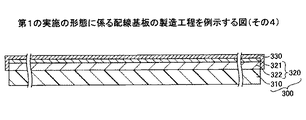

次に、第1の実施の形態に係る配線基板の製造方法について説明する。図2〜図5は、第1の実施の形態に係る配線基板の製造工程を例示する図である。本実施の形態では、支持体上に複数の配線基板となる部分を作製し支持体を除去後個片化して各配線基板とする工程の例を示すが、支持体上に1個ずつ配線基板を作製し支持体を除去する工程としてもよい。

第1の実施の形態の変形例1では、配線層10の一方の面と絶縁層20の一方の面との位置関係が第1の実施の形態とは異なる例を示す。なお、第1の実施の形態の変形例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第1の実施の形態の変形例2では、配線基板1の製造方法の他の例を示す。なお、第1の実施の形態の変形例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

第1の実施の形態の変形例3では、絶縁層20の他方の面に支持体(キャリア)を設けた例を示す。なお、第1の実施の形態の変形例3において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

配線基板の応用例1では、第1の実施の形態に係る配線基板に半導体チップが搭載(フリップチップ実装)された半導体パッケージの例を示す。なお、配線基板の応用例1において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

配線基板の応用例2では、半導体パッケージ上に更に他の半導体パッケージが搭載された所謂POP(Package on package)構造の半導体パッケージの例を示す。なお、配線基板の応用例2において、既に説明した実施の形態と同一構成部についての説明は省略する場合がある。

配線幅が狭い部分(ここではファインライン部と称する)と、配線幅が広い部分(ここではラフライン部と称する)について、電解銅めっきの条件を変更して、形成された配線のめっき厚の検討を行った。

レジスト層のアスペクト比を1〜4まで0.5置きに変えたサンプルを作製した。そして、硫酸銅と硫酸を濃度比5で建浴した電解銅めっき液を用い、電流密度を1.0ASD、めっき時間を60分として、アスペクト比の異なるレジスト層を用いて電解めっきを行った。その後、レジスト層を剥離し、レジスト剥離の不良率を測定した。

4、5 半導体パッケージ

10 配線層

11、12 パッド

12x、20y 凹部

12y アンダーカット

13 配線パターン

20 絶縁層

20x、40x、340x 開口部

40 ソルダーレジスト層

50 粘着層

60、300、300A 支持体

90、110 バンプ

100 半導体チップ

120 アンダーフィル樹脂

130 封止樹脂

310 プリプレグ

320、320A キャリア付き金属箔

321、321A 薄箔

322 厚箔

330 バリア層

340 レジスト層

Claims (10)

- 絶縁層と、

前記絶縁層の一方の面側に埋め込まれた銅からなる配線層と、を有し、

前記配線層は、第1の部分と、前記第1の部分よりも幅及び間隔が広い第2の部分と、を備え、

前記第1の部分は、前記第2の部分よりも層厚が1.0μm以上薄く形成されており、

前記第1の部分の一方の面及び前記第2の部分の一方の面は、前記絶縁層の一方の面から露出し、

前記第2の部分の他方の面の一部は、前記絶縁層の他方の面側に開口する開口部内に露出している配線基板。 - 前記第1の部分の一方の面と前記第2の部分の一方の面とが同一平面上にある請求項1に記載の配線基板。

- 前記第1の部分の側面及び他方の面は前記絶縁層に被覆され、

前記第2の部分の側面及び他方の面は前記絶縁層に被覆され、

前記第2の部分の他方の面の一部が前記開口部内に露出している請求項1又は2に記載の配線基板。 - 前記第1の部分は配線パターンを含み、前記第2の部分はパッドを含む請求項1乃至3の何れか一項に記載の配線基板。

- 前記パッドは、

前記開口部内に露出する部分に設けられた外部接続用のパッドと、

該外部接続用のパッドと異なる部分に設けられた半導体チップ接続用のパッドと、を含む請求項4に記載の配線基板。 - 前記第1の部分の一方の面と前記第2の部分の一方の面は、前記絶縁層の一方の面よりも窪んだ位置に露出している請求項1乃至5の何れか一項に記載の配線基板。

- 前記絶縁層の他方の面側に、粘着層を介して支持体が設けられた請求項1乃至6の何れか一項に記載の配線基板。

- 支持体上にめっきを析出し、第1の部分と、前記第1の部分よりも幅及び間隔が広い第2の部分と、を備え、前記第1の部分及び前記第2の部分の一方の面が前記支持体と接する銅からなる配線層を形成する工程と、

前記支持体上に、前記第1の部分及び前記第2の部分を被覆するように、一方の面が前記支持体と接する絶縁層を形成する工程と、

前記絶縁層に、前記絶縁層の他方の面側に開口し前記第2の部分の他方の面の一部を露出する開口部を形成する工程と、

前記支持体を除去する工程と、を有し、

前記配線層を形成する工程では、前記第1の部分は、前記第2の部分よりも層厚が1.0μm以上薄く形成される配線基板の製造方法。 - 前記開口部を形成する工程と前記支持体を除去する工程との間に、前記絶縁層の他方の面側に粘着層を介して他の支持体を設ける工程を有する請求項8に記載の配線基板の製造方法。

- 前記配線層を形成する工程では、

硫酸銅と硫酸を所定の濃度比で建浴した電解銅めっき液を用いた電解めっき法により、前記第1の部分及び前記第2の部分を銅めっきで形成し、

前記所定の濃度比を予め調整することで、前記第1の部分の層厚を前記第2の部分の層厚よりも薄く形成する請求項8又は9に記載の配線基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016137740A JP6689691B2 (ja) | 2016-07-12 | 2016-07-12 | 配線基板及びその製造方法 |

| US15/645,017 US10170405B2 (en) | 2016-07-12 | 2017-07-10 | Wiring substrate and semiconductor package |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016137740A JP6689691B2 (ja) | 2016-07-12 | 2016-07-12 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018010931A JP2018010931A (ja) | 2018-01-18 |

| JP2018010931A5 JP2018010931A5 (ja) | 2019-04-04 |

| JP6689691B2 true JP6689691B2 (ja) | 2020-04-28 |

Family

ID=60940698

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016137740A Active JP6689691B2 (ja) | 2016-07-12 | 2016-07-12 | 配線基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10170405B2 (ja) |

| JP (1) | JP6689691B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113016067B (zh) * | 2018-11-15 | 2024-02-02 | 罗姆股份有限公司 | 半导体器件 |

| KR102698875B1 (ko) * | 2018-12-13 | 2024-08-27 | 엘지이노텍 주식회사 | 인쇄회로기판 |

| KR20210154450A (ko) * | 2020-06-12 | 2021-12-21 | 엘지이노텍 주식회사 | 인쇄회로기판 및 이의 제조 방법 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4811081A (en) * | 1987-03-23 | 1989-03-07 | Motorola, Inc. | Semiconductor die bonding with conductive adhesive |

| JP2641869B2 (ja) * | 1987-07-24 | 1997-08-20 | 三菱電機株式会社 | 半導体装置の製造方法 |

| KR920702545A (ko) * | 1990-06-26 | 1992-09-04 | 아이자와 스스무 | 반도체 장치 및 그 제조 방법 |

| US5678301A (en) * | 1991-06-04 | 1997-10-21 | Micron Technology, Inc. | Method for forming an interconnect for testing unpackaged semiconductor dice |

| US5602419A (en) * | 1993-12-16 | 1997-02-11 | Nec Corporation | Chip carrier semiconductor device assembly |

| JPH08236586A (ja) * | 1994-12-29 | 1996-09-13 | Nitto Denko Corp | 半導体装置及びその製造方法 |

| JPH08288424A (ja) * | 1995-04-18 | 1996-11-01 | Nec Corp | 半導体装置 |

| US6114763A (en) * | 1997-05-30 | 2000-09-05 | Tessera, Inc. | Semiconductor package with translator for connection to an external substrate |

| US6140707A (en) * | 1998-05-07 | 2000-10-31 | 3M Innovative Properties Co. | Laminated integrated circuit package |

| US6100112A (en) * | 1998-05-28 | 2000-08-08 | The Furukawa Electric Co., Ltd. | Method of manufacturing a tape carrier with bump |

| JP3843919B2 (ja) * | 2002-09-09 | 2006-11-08 | 株式会社デンソー | 半導体ウェハのめっき方法 |

| JP4108643B2 (ja) * | 2004-05-12 | 2008-06-25 | 日本電気株式会社 | 配線基板及びそれを用いた半導体パッケージ |

| JP5003812B2 (ja) | 2009-12-10 | 2012-08-15 | イビデン株式会社 | プリント配線板及びプリント配線板の製造方法 |

| JP6133227B2 (ja) * | 2014-03-27 | 2017-05-24 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

| JP2016122808A (ja) * | 2014-12-25 | 2016-07-07 | Shマテリアル株式会社 | 半導体装置用基板及びその製造方法 |

-

2016

- 2016-07-12 JP JP2016137740A patent/JP6689691B2/ja active Active

-

2017

- 2017-07-10 US US15/645,017 patent/US10170405B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018010931A (ja) | 2018-01-18 |

| US10170405B2 (en) | 2019-01-01 |

| US20180019196A1 (en) | 2018-01-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10892216B2 (en) | Wiring substrate and semiconductor device | |

| US9406599B2 (en) | Wiring substrate and method for manufacturing wiring substrate | |

| JP6223909B2 (ja) | 配線基板及びその製造方法 | |

| KR101968957B1 (ko) | 배선 기판 및 그 제조 방법, 반도체 패키지 | |

| US9997441B2 (en) | Support member, wiring substrate, method for manufacturing wiring substrate, and method for manufacturing semiconductor package | |

| US9334576B2 (en) | Wiring substrate and method of manufacturing wiring substrate | |

| JP6691451B2 (ja) | 配線基板及びその製造方法と電子部品装置 | |

| KR20000029352A (ko) | 반도체 장치 및 그 제조 방법 | |

| JP2017073520A (ja) | 配線基板、半導体装置及び配線基板の製造方法 | |

| JP6510897B2 (ja) | 配線基板及びその製造方法と電子部品装置 | |

| JP2018026437A (ja) | 配線基板及びその製造方法 | |

| JP6632302B2 (ja) | 配線基板及びその製造方法 | |

| TWI731195B (zh) | 配線基板的製造方法 | |

| JP2019016683A (ja) | 配線基板及びその製造方法、半導体パッケージ | |

| JP4170266B2 (ja) | 配線基板の製造方法 | |

| JP6689691B2 (ja) | 配線基板及びその製造方法 | |

| US11923282B2 (en) | Wiring substrate | |

| JP6457881B2 (ja) | 配線基板及びその製造方法 | |

| KR100925669B1 (ko) | 코어리스 패키지 기판 제조 공법에 의한 솔더 온 패드 제조방법 | |

| JP6623056B2 (ja) | 配線基板、半導体装置 | |

| KR101314712B1 (ko) | 비아층을 구비하는 인쇄회로기판 및 이의 제조 방법 | |

| KR101340349B1 (ko) | 패키지 기판 및 이의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190221 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190221 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20191121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200324 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200408 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6689691 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |