JP6620112B2 - 処理システムを使用した空隙構造の組込 - Google Patents

処理システムを使用した空隙構造の組込 Download PDFInfo

- Publication number

- JP6620112B2 JP6620112B2 JP2016559150A JP2016559150A JP6620112B2 JP 6620112 B2 JP6620112 B2 JP 6620112B2 JP 2016559150 A JP2016559150 A JP 2016559150A JP 2016559150 A JP2016559150 A JP 2016559150A JP 6620112 B2 JP6620112 B2 JP 6620112B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- dielectric constant

- low dielectric

- processing

- processing system

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012545 processing Methods 0.000 title claims description 112

- 239000011800 void material Substances 0.000 title claims description 27

- 238000010348 incorporation Methods 0.000 title 1

- 238000000034 method Methods 0.000 claims description 77

- 239000000463 material Substances 0.000 claims description 68

- 239000007789 gas Substances 0.000 claims description 51

- 239000000758 substrate Substances 0.000 claims description 36

- 230000008569 process Effects 0.000 claims description 35

- 238000000151 deposition Methods 0.000 claims description 32

- 238000001312 dry etching Methods 0.000 claims description 25

- 239000003989 dielectric material Substances 0.000 claims description 24

- 230000009969 flowable effect Effects 0.000 claims description 23

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 21

- 229910052802 copper Inorganic materials 0.000 claims description 21

- 239000010949 copper Substances 0.000 claims description 21

- 230000008021 deposition Effects 0.000 claims description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 8

- 229910052710 silicon Inorganic materials 0.000 claims description 8

- 239000010703 silicon Substances 0.000 claims description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 6

- 229910052799 carbon Inorganic materials 0.000 claims description 6

- QLOAVXSYZAJECW-UHFFFAOYSA-N methane;molecular fluorine Chemical compound C.FF QLOAVXSYZAJECW-UHFFFAOYSA-N 0.000 claims description 3

- 239000000377 silicon dioxide Substances 0.000 claims description 3

- 239000001257 hydrogen Substances 0.000 claims description 2

- 229910052739 hydrogen Inorganic materials 0.000 claims description 2

- 150000001247 metal acetylides Chemical class 0.000 claims description 2

- 150000004767 nitrides Chemical class 0.000 claims description 2

- 238000005498 polishing Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 116

- 230000004888 barrier function Effects 0.000 description 21

- 230000015572 biosynthetic process Effects 0.000 description 16

- 238000005229 chemical vapour deposition Methods 0.000 description 15

- 239000004020 conductor Substances 0.000 description 14

- 239000002243 precursor Substances 0.000 description 11

- 239000012530 fluid Substances 0.000 description 10

- 238000010926 purge Methods 0.000 description 10

- 238000012546 transfer Methods 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 9

- 239000002184 metal Substances 0.000 description 9

- 238000005137 deposition process Methods 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 6

- 238000009826 distribution Methods 0.000 description 6

- 238000010438 heat treatment Methods 0.000 description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 6

- 238000000231 atomic layer deposition Methods 0.000 description 5

- 238000004891 communication Methods 0.000 description 5

- 238000004590 computer program Methods 0.000 description 5

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 5

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 238000005086 pumping Methods 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- 238000000429 assembly Methods 0.000 description 3

- 230000000712 assembly Effects 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 2

- -1 BLACK Substances 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- RRZKHZBOZDIQJG-UHFFFAOYSA-N azane;manganese Chemical compound N.[Mn] RRZKHZBOZDIQJG-UHFFFAOYSA-N 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 229910010293 ceramic material Inorganic materials 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000010432 diamond Substances 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 230000003028 elevating effect Effects 0.000 description 2

- 239000013529 heat transfer fluid Substances 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 108091028072 EteRNA Proteins 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- WYEMLYFITZORAB-UHFFFAOYSA-N boscalid Chemical compound C1=CC(Cl)=CC=C1C1=CC=CC=C1NC(=O)C1=CC=CN=C1Cl WYEMLYFITZORAB-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000002826 coolant Substances 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 230000007717 exclusion Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/7682—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing the dielectric comprising air gaps

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/301—AIII BV compounds, where A is Al, Ga, In or Tl and B is N, P, As, Sb or Bi

- C23C16/303—Nitrides

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/36—Carbonitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32082—Radio frequency generated discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02167—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon carbide not containing oxygen, e.g. SiC, SiC:H or silicon carbonitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

- H01L21/31116—Etching inorganic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31127—Etching organic layers

- H01L21/31133—Etching organic layers by chemical means

- H01L21/31138—Etching organic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76819—Smoothing of the dielectric

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76832—Multiple layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76834—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers formation of thin insulating films on the sidewalls or on top of conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/0217—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Plasma & Fusion (AREA)

- Analytical Chemistry (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

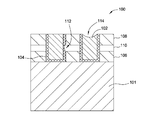

[0027] ブロック402で実施されるドライエッチング処理は、処理システム800のチャンバ200内で実行されうる(図8参照)。図2は、一体型層スタックから材料をドライエッチング又は除去するように構成された、例示的な処理チャンバ200の断面図である。ドライエッチングは、異方的エッチング、等方性エッチング、又はこれらの任意の組み合わせを含みうる。チャンバ200は、モールド層502のドライエッチングに特に適している。一ないし複数の実施形態の実行に適した処理チャンバ200は、限定するものではないが、FRONTIER(商標)処理チャンバ及びSiCoNi(商標)処理チャンバを含みうる。どちらもカリフォルニア州サンタクララのアプライドマテリアルズ社から入手可能である。他の製造業者から入手可能な他の真空処理チャンバも、本実施形態を実行するように適合されうることに留意されたい。

[0048] ブロック404で実行されるライナー堆積処理は、図3に示されるチャンバ300と同様のチャンバ内で実施されうる(図3参照)。一般的に、チャンバ300は、一体型層スタック上にライナーを堆積することに適しており、ALD、CVD、HPCVD、PEALD、PECVD、マイクロ波支援CVD又はNBECVDなど、循環堆積に適合されたガス供給装置330を含む。所望の厚みでコンフォーマル層を形成するためには、複数の薄層を堆積するため、前駆体の順次導入が反復されうる。

[0061] 図8は処理システム800の平面図を示している。一実施形態では、ブロック402及び404、並びに方法400のブロック406の少なくとも一部は、処理システム800内で実行される。処理システム800は、チャンバ200及び300を含む一体型クラスタツールである。一実施形態では、処理システム800は、第1移送チャンバ804に連結された複数の第1処理チャンバ802を含む。一実施形態では、第1処理チャンバ802はチャンバ200すなわちドライエッチングのためのもので、方法400のブロック402におけるドライエッチングはチャンバ200内で実行される。第1移送チャンバ804はまた、一ないし複数のロードロックチャンバ806に連結されている。第1移送チャンバ804は、処理チャンバ802と第1ロードロックチャンバ806との間で基板を移送するための、中央に配置された移送ロボット(図示せず)を有する。処理システム800はまた、第2移送チャンバ810に連結された複数の第2処理チャンバ808を含む。一実施形態では、第2処理チャンバ808は、チャンバ300などのライナー堆積のためのチャンバを含み、ブロック404で実行されるライナー520の堆積、及びブロック406で実行される層スタック堆積処理は、チャンバ300内で実施される。このような好適なチャンバの1つは、カリフォルニア州サンタクララのアプライドマテリアルズ社のCENTINEL(商標)チャンバであってもよい。

Claims (11)

- 一体型層スタック内に空隙構造を形成する方法であって、

真空下の処理システムにおいて前記一体型層スタック上に配置されたモールド層をドライエッチング処理するステップであって、前記モールド層は一ないし複数の銅配線の間に配置され、前記モールド層のドライエッチング処理は前記一ないし複数の銅配線の少なくとも一部を露出させる、ステップと、

前記ドライエッチング処理によって露出された前記一ないし複数の銅配線の露出部分の上にコンフォーマルなライナー層を堆積するステップであって、前記ドライエッチング処理と前記コンフォーマルなライナー層の堆積とが前記処理システムにおいて真空を遮断せずに実行される、ステップと、

前記処理システムにおいて真空を遮断せずに、真空下で前記一ないし複数の銅配線の上に、犠牲膜層及び一ないし複数の流動性低誘電率材料層を含む層スタックを堆積するステップと、

前記層スタックを硬化し、前記犠牲膜層を取り除いて空隙構造を形成するステップと、

を含む、方法。 - 前記モールド層は、シリコンベース酸化物又は低誘電率材料である、請求項1に記載の方法。

- 前記コンフォーマルなライナー層は、炭化物及び窒化物からなるグループから選択される誘電体材料を含む、請求項1に記載の方法。

- 前記一ないし複数の流動性低誘電率材料層は、炭素がドープされた酸化物、フッ素化炭素、ナノクラスタリングシリカ、又はメソポーラス酸化物を含む、請求項1に記載の方法。

- 前記犠牲膜層は、炭素又は高分子炭素−水素材料を含む、請求項1に記載の方法。

- 一体型層スタック内に空隙構造を形成する方法であって、

真空下の処理システムにおいて第1処理チャンバの前記一体型層スタック上に配置された酸化物モールド層をドライエッチング処理するステップであって、前記酸化物モールド層は一ないし複数の銅配線の間に配置され、前記酸化物モールド層の前記ドライエッチング処理は一ないし複数の前記銅配線の少なくとも一部を露出させる、ステップと、

真空下で前記処理システム内の第2処理チャンバの前記一ないし複数の銅配線の露出部分の上に約2ナノメートル未満の厚みを有する低誘電率材料ライナー層をコンフォーマルに堆積することによって、前記一ないし複数の銅配線に堆積されたコンフォーマルな低誘電率材料ライナー層を形成するステップであって、前記ドライエッチング処理と前記低誘電率材料ライナー層の堆積とが前記処理システムにおいて真空を遮断せずに実行される、ステップと、

前記処理システムにおいて真空を遮断することなく、真空下で前記一ないし複数の銅配線の上に、犠牲膜層及び一ないし複数の流動性低誘電率材料層を含む層スタックを堆積するステップと、

前記層スタックを硬化し、前記犠牲膜層を取り除いて空隙構造を形成するステップと、

を含む、方法。 - 前記低誘電率材料ライナー層は炭窒化ケイ素(SiCN)を含み、前記犠牲膜層は炭素を含む、請求項6に記載の方法。

- 前記銅配線の上部を露出するため、前記一ないし複数の流動性低誘電率材料層の一部及び前記低誘電率材料ライナー層を研磨するステップを更に含む、請求項6に記載の方法。

- 前記ドライエッチングは、約2mTorr〜約20mTorrの圧力で、NF3、NH3又はCxFyガスを使用する、請求項6に記載の方法。

- 処理システム内で基板上に誘電体構造を形成する方法であって、

真空下で第1処理チャンバの前記基板上にモールド層をドライエッチング処理するステップであって、前記モールド層は一ないし複数の銅配線の間に配置され、前記モールド層の前記ドライエッチング処理は前記一ないし複数の銅配線の少なくとも一部を露出させるステップと、

真空下で前記第1処理チャンバから、一ないし複数の第2処理チャンバまで前記基板を移送するステップと、

真空下で前記一ないし複数の第2処理チャンバの前記基板上の前記一ないし複数の銅配線の露出部分の上にコンフォーマルにライナー層を堆積することによって、前記一ないし複数の銅配線に堆積されたコンフォーマルなライナー層を形成するステップと、

真空下で前記一ないし複数の第2処理チャンバの前記基板上に形成される前記ライナー層の上に一ないし複数の誘電体層及び犠牲層を堆積するステップと、

前記一ないし複数の誘電体層及び前記犠牲層を硬化し、前記犠牲層を取り除いて空隙構造を形成するステップと、

を含む方法。 - ライナー層の堆積と一ないし複数の誘電体層の堆積は、別々の第2処理チャンバにおいて実行される、請求項10に記載の方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361916726P | 2013-12-16 | 2013-12-16 | |

| US61/916,726 | 2013-12-16 | ||

| US14/523,523 | 2014-10-24 | ||

| US14/523,523 US9312168B2 (en) | 2013-12-16 | 2014-10-24 | Air gap structure integration using a processing system |

| PCT/US2014/068344 WO2015094667A1 (en) | 2013-12-16 | 2014-12-03 | Air gap structure integration using a processing system |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017501591A JP2017501591A (ja) | 2017-01-12 |

| JP2017501591A5 JP2017501591A5 (ja) | 2018-01-18 |

| JP6620112B2 true JP6620112B2 (ja) | 2019-12-11 |

Family

ID=53369385

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016559150A Active JP6620112B2 (ja) | 2013-12-16 | 2014-12-03 | 処理システムを使用した空隙構造の組込 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9312168B2 (ja) |

| JP (1) | JP6620112B2 (ja) |

| KR (1) | KR102308047B1 (ja) |

| CN (1) | CN105814678B (ja) |

| TW (1) | TWI626688B (ja) |

| WO (1) | WO2015094667A1 (ja) |

Families Citing this family (62)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9132436B2 (en) | 2012-09-21 | 2015-09-15 | Applied Materials, Inc. | Chemical control features in wafer process equipment |

| US10256079B2 (en) | 2013-02-08 | 2019-04-09 | Applied Materials, Inc. | Semiconductor processing systems having multiple plasma configurations |

| US11637002B2 (en) | 2014-11-26 | 2023-04-25 | Applied Materials, Inc. | Methods and systems to enhance process uniformity |

| US20160225652A1 (en) | 2015-02-03 | 2016-08-04 | Applied Materials, Inc. | Low temperature chuck for plasma processing systems |

| US9741593B2 (en) | 2015-08-06 | 2017-08-22 | Applied Materials, Inc. | Thermal management systems and methods for wafer processing systems |

| US10504700B2 (en) | 2015-08-27 | 2019-12-10 | Applied Materials, Inc. | Plasma etching systems and methods with secondary plasma injection |

| WO2017052540A1 (en) * | 2015-09-23 | 2017-03-30 | Intel Corporation | Ultra thin helmet dielectric layer for maskless air gap and replacement ild processes |

| US9449871B1 (en) | 2015-11-18 | 2016-09-20 | International Business Machines Corporation | Hybrid airgap structure with oxide liner |

| US9349687B1 (en) | 2015-12-19 | 2016-05-24 | International Business Machines Corporation | Advanced manganese/manganese nitride cap/etch mask for air gap formation scheme in nanocopper low-K interconnect |

| US9887128B2 (en) | 2015-12-29 | 2018-02-06 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method and structure for interconnection |

| JP6329199B2 (ja) * | 2016-03-30 | 2018-05-23 | 株式会社日立国際電気 | 半導体装置の製造方法、基板処理装置およびプログラム |

| US9553019B1 (en) | 2016-04-15 | 2017-01-24 | International Business Machines Corporation | Airgap protection layer for via alignment |

| US10504754B2 (en) | 2016-05-19 | 2019-12-10 | Applied Materials, Inc. | Systems and methods for improved semiconductor etching and component protection |

| TWI729457B (zh) | 2016-06-14 | 2021-06-01 | 美商應用材料股份有限公司 | 金屬及含金屬化合物之氧化體積膨脹 |

| US10546729B2 (en) | 2016-10-04 | 2020-01-28 | Applied Materials, Inc. | Dual-channel showerhead with improved profile |

| TWI719262B (zh) | 2016-11-03 | 2021-02-21 | 美商應用材料股份有限公司 | 用於圖案化之薄膜的沉積與處理 |

| EP3539154A4 (en) | 2016-11-08 | 2020-06-03 | Applied Materials, Inc. | GEOMETRIC CONTROL OF PRESSURE COLUMNS FOR SAMPLE APPLICATIONS |

| US10431429B2 (en) | 2017-02-03 | 2019-10-01 | Applied Materials, Inc. | Systems and methods for radial and azimuthal control of plasma uniformity |

| WO2018156710A1 (en) | 2017-02-22 | 2018-08-30 | Applied Materials, Inc. | Critical dimension control for self-aligned contact patterning |

| US10943834B2 (en) | 2017-03-13 | 2021-03-09 | Applied Materials, Inc. | Replacement contact process |

| WO2018200212A1 (en) | 2017-04-25 | 2018-11-01 | Applied Materials, Inc. | Selective deposition of tungsten for simplified process flow of tungsten oxide pillar formation |

| US11276590B2 (en) | 2017-05-17 | 2022-03-15 | Applied Materials, Inc. | Multi-zone semiconductor substrate supports |

| US11276559B2 (en) | 2017-05-17 | 2022-03-15 | Applied Materials, Inc. | Semiconductor processing chamber for multiple precursor flow |

| US10403542B2 (en) * | 2017-06-10 | 2019-09-03 | Applied Materials, Inc. | Methods of forming self-aligned vias and air gaps |

| US10840186B2 (en) | 2017-06-10 | 2020-11-17 | Applied Materials, Inc. | Methods of forming self-aligned vias and air gaps |

| TWI719316B (zh) * | 2017-06-12 | 2021-02-21 | 美商應用材料股份有限公司 | 利用鎢氧化還原之無縫鎢填充 |

| TW201906035A (zh) | 2017-06-24 | 2019-02-01 | 美商微材料有限責任公司 | 生產完全自我對準的介層窗及觸點之方法 |

| US10297458B2 (en) | 2017-08-07 | 2019-05-21 | Applied Materials, Inc. | Process window widening using coated parts in plasma etch processes |

| JP7225211B2 (ja) * | 2017-08-18 | 2023-02-20 | ティーイーエル マニュファクチュアリング アンド エンジニアリング オブ アメリカ,インコーポレイテッド | 低温流体を噴霧するための装置 |

| US10573555B2 (en) | 2017-08-31 | 2020-02-25 | Micromaterials Llc | Methods of producing self-aligned grown via |

| WO2019046399A1 (en) | 2017-08-31 | 2019-03-07 | Micromaterials Llc | METHODS FOR PRODUCING SELF-ALIGNED INTERCONNECTION HOLES |

| WO2019050735A1 (en) | 2017-09-06 | 2019-03-14 | Micromaterials Llc | METHODS FOR PRODUCING SELF-ALIGNED INTERCONNECTION HOLES |

| CN110034017A (zh) | 2017-12-07 | 2019-07-19 | 微材料有限责任公司 | 用于使金属和阻挡层-衬垫可控凹陷的方法 |

| EP3499557A1 (en) | 2017-12-15 | 2019-06-19 | Micromaterials LLC | Selectively etched self-aligned via processes |

| US10903054B2 (en) | 2017-12-19 | 2021-01-26 | Applied Materials, Inc. | Multi-zone gas distribution systems and methods |

| US11328909B2 (en) | 2017-12-22 | 2022-05-10 | Applied Materials, Inc. | Chamber conditioning and removal processes |

| US20190206718A1 (en) | 2018-01-02 | 2019-07-04 | Globalfoundries Inc. | Back-end-of-line structures with air gaps |

| US10854426B2 (en) | 2018-01-08 | 2020-12-01 | Applied Materials, Inc. | Metal recess for semiconductor structures |

| US10964512B2 (en) | 2018-02-15 | 2021-03-30 | Applied Materials, Inc. | Semiconductor processing chamber multistage mixing apparatus and methods |

| KR20190104902A (ko) | 2018-03-02 | 2019-09-11 | 마이크로머티어리얼즈 엘엘씨 | 금속 산화물들을 제거하기 위한 방법들 |

| US10319600B1 (en) | 2018-03-12 | 2019-06-11 | Applied Materials, Inc. | Thermal silicon etch |

| US10886137B2 (en) | 2018-04-30 | 2021-01-05 | Applied Materials, Inc. | Selective nitride removal |

| US10790191B2 (en) | 2018-05-08 | 2020-09-29 | Micromaterials Llc | Selective removal process to create high aspect ratio fully self-aligned via |

| TW202011547A (zh) | 2018-05-16 | 2020-03-16 | 美商微材料有限責任公司 | 用於產生完全自對準的通孔的方法 |

| US10699953B2 (en) | 2018-06-08 | 2020-06-30 | Micromaterials Llc | Method for creating a fully self-aligned via |

| US10892198B2 (en) | 2018-09-14 | 2021-01-12 | Applied Materials, Inc. | Systems and methods for improved performance in semiconductor processing |

| US11049755B2 (en) | 2018-09-14 | 2021-06-29 | Applied Materials, Inc. | Semiconductor substrate supports with embedded RF shield |

| US11062887B2 (en) | 2018-09-17 | 2021-07-13 | Applied Materials, Inc. | High temperature RF heater pedestals |

| US11417534B2 (en) | 2018-09-21 | 2022-08-16 | Applied Materials, Inc. | Selective material removal |

| US11682560B2 (en) | 2018-10-11 | 2023-06-20 | Applied Materials, Inc. | Systems and methods for hafnium-containing film removal |

| US11121002B2 (en) | 2018-10-24 | 2021-09-14 | Applied Materials, Inc. | Systems and methods for etching metals and metal derivatives |

| US11437242B2 (en) | 2018-11-27 | 2022-09-06 | Applied Materials, Inc. | Selective removal of silicon-containing materials |

| US11721527B2 (en) * | 2019-01-07 | 2023-08-08 | Applied Materials, Inc. | Processing chamber mixing systems |

| US10920319B2 (en) | 2019-01-11 | 2021-02-16 | Applied Materials, Inc. | Ceramic showerheads with conductive electrodes |

| US11004687B2 (en) | 2019-02-11 | 2021-05-11 | Applied Materials, Inc. | Gate contact over active processes |

| US11164938B2 (en) | 2019-03-26 | 2021-11-02 | Micromaterials Llc | DRAM capacitor module |

| US11643724B2 (en) * | 2019-07-18 | 2023-05-09 | Asm Ip Holding B.V. | Method of forming structures using a neutral beam |

| TWI819233B (zh) * | 2019-08-15 | 2023-10-21 | 美商應用材料股份有限公司 | 非共形膜的選擇性蝕刻臨界尺寸控制 |

| KR20210021420A (ko) | 2019-08-16 | 2021-02-26 | 삼성전자주식회사 | 저유전체 물질 층을 포함하는 반도체 소자 형성 방법 |

| US11482447B2 (en) * | 2020-07-08 | 2022-10-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming an integrated chip having a cavity between metal features |

| CN111933688B (zh) * | 2020-09-18 | 2021-02-09 | 晶芯成(北京)科技有限公司 | 一种半导体结构及其制备方法 |

| TWI801058B (zh) * | 2021-12-23 | 2023-05-01 | 明遠精密科技股份有限公司 | 一種複合式電漿源及其運作方法 |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6815329B2 (en) * | 2000-02-08 | 2004-11-09 | International Business Machines Corporation | Multilayer interconnect structure containing air gaps and method for making |

| US6406975B1 (en) * | 2000-11-27 | 2002-06-18 | Chartered Semiconductor Manufacturing Inc. | Method for fabricating an air gap shallow trench isolation (STI) structure |

| US6603204B2 (en) * | 2001-02-28 | 2003-08-05 | International Business Machines Corporation | Low-k interconnect structure comprised of a multilayer of spin-on porous dielectrics |

| US6642151B2 (en) | 2002-03-06 | 2003-11-04 | Applied Materials, Inc | Techniques for plasma etching silicon-germanium |

| JP2004103971A (ja) * | 2002-09-12 | 2004-04-02 | Hitachi High-Technologies Corp | ダマシン処理方法、ダマシン処理装置および、ダマシン構造 |

| EP1398831A3 (en) * | 2002-09-13 | 2008-02-20 | Shipley Co. L.L.C. | Air gaps formation |

| US7088003B2 (en) * | 2004-02-19 | 2006-08-08 | International Business Machines Corporation | Structures and methods for integration of ultralow-k dielectrics with improved reliability |

| US7247946B2 (en) * | 2005-01-18 | 2007-07-24 | International Business Machines Corporation | On-chip Cu interconnection using 1 to 5 nm thick metal cap |

| KR100817088B1 (ko) | 2007-02-16 | 2008-03-26 | 삼성전자주식회사 | 다마신 공정을 이용한 반도체 소자의 미세 금속 배선 패턴형성 방법 |

| US7879683B2 (en) | 2007-10-09 | 2011-02-01 | Applied Materials, Inc. | Methods and apparatus of creating airgap in dielectric layers for the reduction of RC delay |

| US7666754B2 (en) * | 2007-10-18 | 2010-02-23 | Tokyo Electron Limited | Method and system for forming an air gap structure |

| US20100051578A1 (en) * | 2008-09-04 | 2010-03-04 | Shuo-Che Chang | Method for fabricating an integrated circuit |

| US8557712B1 (en) * | 2008-12-15 | 2013-10-15 | Novellus Systems, Inc. | PECVD flowable dielectric gap fill |

| JP2010165864A (ja) * | 2009-01-15 | 2010-07-29 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| JP2011165876A (ja) * | 2010-02-09 | 2011-08-25 | Consortium For Advanced Semiconductor Materials & Related Technologies | 半導体装置、及びその製造方法 |

| US8456009B2 (en) | 2010-02-18 | 2013-06-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor structure having an air-gap region and a method of manufacturing the same |

| US8288268B2 (en) * | 2010-04-29 | 2012-10-16 | International Business Machines Corporation | Microelectronic structure including air gap |

| KR20120053799A (ko) * | 2010-11-18 | 2012-05-29 | 삼성전자주식회사 | 반도체 장치 및 반도체 장치의 형성 방법 |

| US20120213941A1 (en) * | 2011-02-22 | 2012-08-23 | Varian Semiconductor Equipment Associates, Inc. | Ion-assisted plasma treatment of a three-dimensional structure |

| JP5898991B2 (ja) * | 2012-02-10 | 2016-04-06 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体装置の製造方法 |

| KR20130092884A (ko) | 2012-02-13 | 2013-08-21 | 에스케이하이닉스 주식회사 | 반도체 소자의 배선 구조체 및 제조 방법 |

| US20130323930A1 (en) * | 2012-05-29 | 2013-12-05 | Kaushik Chattopadhyay | Selective Capping of Metal Interconnect Lines during Air Gap Formation |

| KR102002815B1 (ko) * | 2012-09-05 | 2019-07-23 | 삼성전자주식회사 | 반도체 장치 및 이의 제조 방법 |

-

2014

- 2014-10-24 US US14/523,523 patent/US9312168B2/en active Active

- 2014-12-03 JP JP2016559150A patent/JP6620112B2/ja active Active

- 2014-12-03 CN CN201480068113.3A patent/CN105814678B/zh not_active Expired - Fee Related

- 2014-12-03 KR KR1020167019332A patent/KR102308047B1/ko active IP Right Grant

- 2014-12-03 WO PCT/US2014/068344 patent/WO2015094667A1/en active Application Filing

- 2014-12-05 TW TW103142446A patent/TWI626688B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| TW201526106A (zh) | 2015-07-01 |

| CN105814678B (zh) | 2019-06-14 |

| TWI626688B (zh) | 2018-06-11 |

| US9312168B2 (en) | 2016-04-12 |

| JP2017501591A (ja) | 2017-01-12 |

| KR102308047B1 (ko) | 2021-09-30 |

| CN105814678A (zh) | 2016-07-27 |

| KR20160098483A (ko) | 2016-08-18 |

| WO2015094667A1 (en) | 2015-06-25 |

| US20150170956A1 (en) | 2015-06-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6620112B2 (ja) | 処理システムを使用した空隙構造の組込 | |

| KR102360220B1 (ko) | 듀얼 다마신 구조에서 유전체 배리어 층을 에칭하기 위한 방법들 | |

| US7618889B2 (en) | Dual damascene fabrication with low k materials | |

| TWI645506B (zh) | 形成具有氣隙之半導體元件的方法 | |

| US20090104774A1 (en) | Method of manufacturing a semiconductor device | |

| US5861674A (en) | Multilevel interconnection in a semiconductor device and method for forming the same | |

| JP6793711B2 (ja) | 選択的にエッチングされた自己整合ビアプロセス | |

| US20070224827A1 (en) | Methods for etching a bottom anti-reflective coating layer in dual damascene application | |

| TW201017819A (en) | Semiconductor device manufacturing method and storage medium | |

| TWI769611B (zh) | 半導體結構及其製造方法 | |

| US7718543B2 (en) | Two step etching of a bottom anti-reflective coating layer in dual damascene application | |

| KR100684905B1 (ko) | 다마신 공정의 방법 | |

| KR20220166338A (ko) | 유전체 재료 충전 및 처리 방법들 | |

| US20200251340A1 (en) | Methods and apparatus for filling a feature disposed in a substrate | |

| US7393795B2 (en) | Methods for post-etch deposition of a dielectric film | |

| US20110300706A1 (en) | Method for fabricating interconnection structure | |

| KR20230030536A (ko) | 완전히 자가 정렬된 비아 통합 공정들 | |

| WO2013123679A1 (zh) | 扩散阻挡层、金属互连结构及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171201 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20171201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20181106 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190205 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190408 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190507 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20191023 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20191118 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6620112 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |