JP6534557B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6534557B2 JP6534557B2 JP2015085631A JP2015085631A JP6534557B2 JP 6534557 B2 JP6534557 B2 JP 6534557B2 JP 2015085631 A JP2015085631 A JP 2015085631A JP 2015085631 A JP2015085631 A JP 2015085631A JP 6534557 B2 JP6534557 B2 JP 6534557B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- region

- oxide semiconductor

- conductive film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 476

- 230000015572 biosynthetic process Effects 0.000 claims description 28

- 239000001257 hydrogen Substances 0.000 claims description 19

- 229910052739 hydrogen Inorganic materials 0.000 claims description 19

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 16

- 238000000034 method Methods 0.000 description 120

- 239000000758 substrate Substances 0.000 description 117

- 230000006870 function Effects 0.000 description 72

- 239000013078 crystal Substances 0.000 description 58

- 239000004973 liquid crystal related substance Substances 0.000 description 52

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 46

- 229910052760 oxygen Inorganic materials 0.000 description 46

- 239000001301 oxygen Substances 0.000 description 46

- 239000010410 layer Substances 0.000 description 44

- 238000010438 heat treatment Methods 0.000 description 40

- 238000005229 chemical vapour deposition Methods 0.000 description 26

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 24

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 24

- 238000000231 atomic layer deposition Methods 0.000 description 24

- 229910052710 silicon Inorganic materials 0.000 description 24

- 239000010703 silicon Substances 0.000 description 24

- 239000008188 pellet Substances 0.000 description 23

- 238000004519 manufacturing process Methods 0.000 description 22

- 125000004429 atom Chemical group 0.000 description 21

- 239000012535 impurity Substances 0.000 description 21

- 229910052782 aluminium Inorganic materials 0.000 description 19

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 19

- 238000000206 photolithography Methods 0.000 description 18

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 17

- 230000003071 parasitic effect Effects 0.000 description 17

- 239000000523 sample Substances 0.000 description 17

- 238000004549 pulsed laser deposition Methods 0.000 description 16

- 238000004544 sputter deposition Methods 0.000 description 16

- 238000001451 molecular beam epitaxy Methods 0.000 description 15

- 239000003990 capacitor Substances 0.000 description 14

- 229910052738 indium Inorganic materials 0.000 description 14

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 14

- 239000000203 mixture Substances 0.000 description 14

- 239000011701 zinc Substances 0.000 description 13

- 230000007547 defect Effects 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- 229910052802 copper Inorganic materials 0.000 description 11

- 239000010949 copper Substances 0.000 description 11

- 239000012212 insulator Substances 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- 239000000463 material Substances 0.000 description 10

- 239000011135 tin Substances 0.000 description 10

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 9

- 229910001195 gallium oxide Inorganic materials 0.000 description 9

- 229910052727 yttrium Inorganic materials 0.000 description 9

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 8

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 8

- 239000004020 conductor Substances 0.000 description 8

- 239000011347 resin Substances 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- 229910052715 tantalum Inorganic materials 0.000 description 8

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 8

- 229910052718 tin Inorganic materials 0.000 description 8

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 8

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 7

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 7

- 230000000903 blocking effect Effects 0.000 description 7

- 229910052733 gallium Inorganic materials 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 239000002159 nanocrystal Substances 0.000 description 7

- 230000008569 process Effects 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 230000001681 protective effect Effects 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 239000010936 titanium Substances 0.000 description 7

- 229910052726 zirconium Inorganic materials 0.000 description 7

- 229910001316 Ag alloy Inorganic materials 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 6

- QRSFFHRCBYCWBS-UHFFFAOYSA-N [O].[O] Chemical compound [O].[O] QRSFFHRCBYCWBS-UHFFFAOYSA-N 0.000 description 6

- 238000004458 analytical method Methods 0.000 description 6

- 238000004040 coloring Methods 0.000 description 6

- 238000004891 communication Methods 0.000 description 6

- 238000010894 electron beam technology Methods 0.000 description 6

- 238000002003 electron diffraction Methods 0.000 description 6

- 238000005530 etching Methods 0.000 description 6

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 6

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 6

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 6

- 150000004767 nitrides Chemical class 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 229910052709 silver Inorganic materials 0.000 description 6

- 239000004332 silver Substances 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- 238000003860 storage Methods 0.000 description 6

- 238000012916 structural analysis Methods 0.000 description 6

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 6

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 5

- 229910052779 Neodymium Inorganic materials 0.000 description 5

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 230000008859 change Effects 0.000 description 5

- 239000003086 colorant Substances 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000005684 electric field Effects 0.000 description 5

- 229910052731 fluorine Inorganic materials 0.000 description 5

- 239000011737 fluorine Substances 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 229910052735 hafnium Inorganic materials 0.000 description 5

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 5

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 5

- 230000001590 oxidative effect Effects 0.000 description 5

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 5

- 229910052725 zinc Inorganic materials 0.000 description 5

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 230000001186 cumulative effect Effects 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 229910052746 lanthanum Inorganic materials 0.000 description 4

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 4

- 229910052749 magnesium Inorganic materials 0.000 description 4

- 239000011777 magnesium Substances 0.000 description 4

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 238000003917 TEM image Methods 0.000 description 3

- 238000005452 bending Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- -1 for example Substances 0.000 description 3

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 239000000395 magnesium oxide Substances 0.000 description 3

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 3

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 238000005121 nitriding Methods 0.000 description 3

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 3

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- 230000037303 wrinkles Effects 0.000 description 3

- 229910001928 zirconium oxide Inorganic materials 0.000 description 3

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 230000004075 alteration Effects 0.000 description 2

- 239000004760 aramid Substances 0.000 description 2

- 229920003235 aromatic polyamide Polymers 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 210000004027 cell Anatomy 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000010893 electron trap Methods 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 230000001151 other effect Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 229910052696 pnictogen Inorganic materials 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- 229910052723 transition metal Inorganic materials 0.000 description 2

- 210000002925 A-like Anatomy 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 235000000177 Indigofera tinctoria Nutrition 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 229910007541 Zn O Inorganic materials 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- FTWRSWRBSVXQPI-UHFFFAOYSA-N alumanylidynearsane;gallanylidynearsane Chemical compound [As]#[Al].[As]#[Ga] FTWRSWRBSVXQPI-UHFFFAOYSA-N 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- 229910052795 boron group element Inorganic materials 0.000 description 1

- 239000011449 brick Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000002524 electron diffraction data Methods 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 229940097275 indigo Drugs 0.000 description 1

- COHYTHOBJLSHDF-UHFFFAOYSA-N indigo powder Natural products N1C2=CC=CC=C2C(=O)C1=C1C(=O)C2=CC=CC=C2N1 COHYTHOBJLSHDF-UHFFFAOYSA-N 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 230000005389 magnetism Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 230000006855 networking Effects 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- KYKLWYKWCAYAJY-UHFFFAOYSA-N oxotin;zinc Chemical compound [Zn].[Sn]=O KYKLWYKWCAYAJY-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920006122 polyamide resin Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 230000009993 protective function Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 238000009736 wetting Methods 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

- H01L2029/42388—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor characterised by the shape of the insulating material

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

本実施の形態では、本発明の一態様である半導体装置、及びその作製方法について図面を参照して説明する。半導体装置の一例としてトランジスタを用いて説明する。

図1(A)、図1(B)及び図1(C)は、本発明の一態様に係るトランジスタ150の上面図及び断面図である。図1(A)は上面図である。図1(B)及び図1(C)は、図1(A)に示す一点鎖線A1−A2、及び一点鎖線B1−B2に対応する断面図である。なお、図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

以下では、酸化物半導体の構造について説明する。

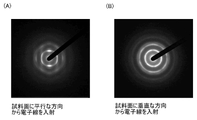

まずは、CAAC−OSについて説明する。

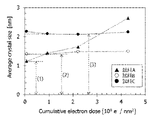

次に、nc−OSについて説明する。

a−like OSは、nc−OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。

以下では、図1に示したトランジスタ150の作製方法について説明する。

以下では、図1などに示したトランジスタ150とは、異なる構造を有するトランジスタ250について説明する。図11(A)、図11(B)及び図11(C)は、本発明の一態様に係るトランジスタ250の上面図及び断面図である。図11(A)は上面図である。図11(B)及び図11(C)は、図11(A)に示す一点鎖線A1−A2、及び一点鎖線B1−B2に対応する断面図である。なお、図11(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

以下では、図11に示したトランジスタ250の作製方法について説明する。

以下では、先に示したトランジスタとは、異なる構造を有するトランジスタ350について説明する。図15(A)、図15(B)及び図15(C)は、本発明の一態様に係るトランジスタ350の上面図及び断面図である。図15(A)は上面図である。図15(B)及び図15(C)は、図15(A)に示す一点鎖線A1−A2、及び一点鎖線B1−B2に対応する断面図である。なお、図15(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

以下では、図15に示したトランジスタ350の作製方法について説明する。

本実施の形態においては、先の実施の形態で例示したトランジスタを有する表示装置の一例について、図18乃至図20を用いて以下説明を行う。

図19及び図20に示す表示装置700は、引き回し配線部711と、画素部702と、ソースドライバ回路部704と、FPC端子部708と、を有する。また、引き回し配線部711は、信号線710を有する。また、画素部702は、トランジスタ750及び容量素子790を有する。また、ソースドライバ回路部704は、トランジスタ752を有する。

図19に示す表示装置700は、液晶素子775を有する。液晶素子775は、導電膜772、導電膜774、及び液晶層776を有する。導電膜774は、第2の基板705側に設けられ、対向電極としての機能を有する。図19に示す表示装置700は、導電膜772と導電膜774に印加される電圧によって、液晶層776の配向状態が変わることによって光の透過、非透過が制御され画像を表示することができる。

図20に示す表示装置700は、発光素子782を有する。発光素子782は、導電膜784、EL層786、及び導電膜788を有する。図20に示す表示装置700は、発光素子782が有するEL層786が発光することによって、画像を表示することができる。

本実施の形態では、本発明の一態様の半導体装置を有する表示装置について、図21を用いて説明を行う。

本実施の形態では、本発明の一態様の半導体装置を有する表示モジュール及び電子機器について、図22及び図23を用いて説明を行う。

101 絶縁膜

102 絶縁膜

102a 絶縁膜

102b 絶縁膜

104 導電膜

106 半導体膜

106a 半導体膜

106b 半導体膜

106c 半導体膜

110a 絶縁膜

110b 絶縁膜

112 絶縁膜

114 導電膜

116a 導電膜

116b 導電膜

150 トランジスタ

208 低抵抗領域

208a 低抵抗領域

208b 低抵抗領域

208c チャネル形成領域

210 絶縁膜

210a 絶縁膜

210b 絶縁膜

250 トランジスタ

310a 絶縁膜

310b 絶縁膜

350 トランジスタ

501 画素回路

502 画素部

504 駆動回路部

504a ゲートドライバ

504b ソースドライバ

506 保護回路

507 端子部

550 トランジスタ

552 トランジスタ

554 トランジスタ

560 容量素子

562 容量素子

570 液晶素子

572 発光素子

700 表示装置

701 基板

702 画素部

704 ソースドライバ回路部

705 基板

706 ゲートドライバ回路部

708 FPC端子部

710 信号線

711 配線部

712 シール材

716 FPC

730 絶縁膜

732 封止膜

734 絶縁膜

736 着色膜

738 遮光膜

750 トランジスタ

752 トランジスタ

760 接続電極

764 絶縁膜

766 絶縁膜

770 平坦化絶縁膜

772 導電膜

774 導電膜

775 液晶素子

776 液晶層

778 構造体

780 異方性導電膜

782 発光素子

784 導電膜

786 EL層

788 導電膜

790 容量素子

5100 ペレット

5120 基板

5161 領域

8000 表示モジュール

8001 上部カバー

8002 下部カバー

8003 FPC

8004 タッチパネル

8005 FPC

8006 表示パネル

8007 バックライトユニット

8008 光源

8009 フレーム

8010 プリント基板

8011 バッテリー

9000 筐体

9001 表示部

9003 スピーカー

9005 操作キー

9006 接続端子

9007 センサ

9008 マイクロフォン

9050 操作ボタン

9051 情報

9052 情報

9053 情報

9054 情報

9055 ヒンジ

9100 携帯情報端末

9101 携帯情報端末

9102 携帯情報端末

9200 携帯情報端末

9201 携帯情報端末

Claims (7)

- 酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、を有し、

前記酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、

前記第1の領域は、前記第1の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第2の領域は、前記第1の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第3の領域は、前記第3の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第4の領域は、前記第2の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第5の領域は、前記第2の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第1の絶縁膜は、前記第1の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第2の絶縁膜は、前記第2の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第3の絶縁膜は、前記第1の絶縁膜上、前記第2の絶縁膜上及び前記酸化物半導体膜上に設けられ、

前記第3の導電膜は、前記酸化物半導体膜と前記第3の絶縁膜を介して、重なる領域を有することを特徴とする半導体装置。 - 酸化物半導体膜と、第1の導電膜と、第2の導電膜と、第3の導電膜と、第4の導電膜と、第1の絶縁膜と、第2の絶縁膜と、第3の絶縁膜と、第4の絶縁膜と、を有し、

前記第4の絶縁膜は、前記第4の導電膜上に設けられ、

前記酸化物半導体膜は、前記第4の絶縁膜上に設けられ、

前記酸化物半導体膜は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、第5の領域と、を有し、

前記第1の領域は、前記第1の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第2の領域は、前記第1の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第3の領域は、前記第3の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第4の領域は、前記第2の絶縁膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第5の領域は、前記第2の導電膜と前記酸化物半導体膜とが互いに接する領域を有し、

前記第1の絶縁膜は、前記第1の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第2の絶縁膜は、前記第2の導電膜上及び前記酸化物半導体膜上に設けられ、

前記第3の絶縁膜は、前記第1の絶縁膜上、前記第2の絶縁膜上及び前記酸化物半導体膜上に設けられ、

前記第3の導電膜は、前記酸化物半導体膜と前記第3の絶縁膜を介して、重なる領域を有することを特徴とする半導体装置。 - 請求項1または請求項2において、

前記第1の絶縁膜及び前記第2の絶縁膜は、水素を有し、

前記第2の領域は、前記第3の領域よりも、抵抗値が低い領域を有し、

前記第4の領域は、前記第3の領域よりも、抵抗値が低い領域を有することを特徴とする半導体装置。 - チャネル形成領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と電気的に接続された、ソース電極と、

前記酸化物半導体膜と電気的に接続された、ドレイン電極と、

前記ソース電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第1の絶縁膜と、

前記ドレイン電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第2の絶縁膜と、

前記酸化物半導体膜、前記第1の絶縁膜及び前記第2の絶縁膜上に設けられた、第3の絶縁膜と、

前記第3の絶縁膜上の、ゲート電極と、を有し、

前記第1の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第2の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第3の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記ゲート電極は、前記第3の絶縁膜及び前記第1の絶縁膜を介して、前記ソース電極と重なる領域を有し、

前記ゲート電極は、前記第3の絶縁膜及び前記第2の絶縁膜を介して、前記ドレイン電極と重なる領域を有することを特徴とする半導体装置。 - 第1のゲート電極と、

前記第1のゲート電極上の、第4の絶縁膜と、

前記第4の絶縁膜上の、チャネル形成領域を有する、酸化物半導体膜と、

前記酸化物半導体膜と電気的に接続された、ソース電極と、

前記酸化物半導体膜と電気的に接続された、ドレイン電極と、

前記ソース電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第1の絶縁膜と、

前記ドレイン電極の上面、及び前記チャネル形成領域側の側面と重なる領域を有する、第2の絶縁膜と、

前記酸化物半導体膜、前記第1の絶縁膜及び前記第2の絶縁膜上に設けられた、第3の絶縁膜と、

前記第3の絶縁膜上の、第2のゲート電極と、を有し、

前記第1の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第2の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第3の絶縁膜は、前記酸化物半導体膜と接する領域を有し、

前記第2のゲート電極は、前記第3の絶縁膜及び前記第1の絶縁膜を介して、前記ソース電極と重なる領域を有し、

前記第2のゲート電極は、前記第3の絶縁膜及び前記第2の絶縁膜を介して、前記ドレイン電極と重なる領域を有することを特徴とする半導体装置。 - 請求項1乃至請求項5のいずれか一において、

前記酸化物半導体膜は、第1の酸化物半導体膜と、前記第1の酸化物半導体膜上の、第2の酸化物半導体膜と、前記第2の酸化物半導体膜上の、第3の酸化物半導体膜と、を有することを特徴とする半導体装置。 - 請求項1乃至請求項5のいずれか一において、

前記酸化物半導体膜は、第1の酸化物半導体膜と、前記第1の酸化物半導体膜上の、第2の酸化物半導体膜と、前記第2の酸化物半導体膜上の、第3の酸化物半導体膜と、を有し、

前記第3の酸化物半導体膜は、前記第1の絶縁膜と前記第3の絶縁膜との間に設けられた領域を有し、かつ前記第2の絶縁膜と前記第3の絶縁膜との間に設けられた領域を有することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015085631A JP6534557B2 (ja) | 2014-04-25 | 2015-04-20 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014091703 | 2014-04-25 | ||

| JP2014091703 | 2014-04-25 | ||

| JP2015085631A JP6534557B2 (ja) | 2014-04-25 | 2015-04-20 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015216367A JP2015216367A (ja) | 2015-12-03 |

| JP2015216367A5 JP2015216367A5 (ja) | 2018-05-31 |

| JP6534557B2 true JP6534557B2 (ja) | 2019-06-26 |

Family

ID=54335552

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015085631A Expired - Fee Related JP6534557B2 (ja) | 2014-04-25 | 2015-04-20 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9780226B2 (ja) |

| JP (1) | JP6534557B2 (ja) |

| KR (1) | KR102344557B1 (ja) |

| TW (1) | TWI655771B (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9882014B2 (en) | 2013-11-29 | 2018-01-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| CN113793872A (zh) | 2014-12-10 | 2021-12-14 | 株式会社半导体能源研究所 | 半导体装置及其制造方法 |

| US9653613B2 (en) * | 2015-02-27 | 2017-05-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP6210105B2 (ja) | 2015-11-04 | 2017-10-11 | トヨタ自動車株式会社 | バッテリ装置 |

| JP6607013B2 (ja) * | 2015-12-08 | 2019-11-20 | 株式会社リコー | 電界効果型トランジスタ、表示素子、画像表示装置、及びシステム |

| JPWO2017125796A1 (ja) * | 2016-01-18 | 2018-11-15 | 株式会社半導体エネルギー研究所 | 金属酸化物膜、半導体装置、及び表示装置 |

| US9905657B2 (en) * | 2016-01-20 | 2018-02-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| US11302717B2 (en) * | 2016-04-08 | 2022-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and method for manufacturing the same |

| US10411003B2 (en) | 2016-10-14 | 2019-09-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| KR102384624B1 (ko) | 2016-10-21 | 2022-04-11 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| WO2018138619A1 (en) | 2017-01-30 | 2018-08-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2019043510A1 (ja) * | 2017-09-01 | 2019-03-07 | 株式会社半導体エネルギー研究所 | 半導体装置、及び表示装置 |

| US11444025B2 (en) * | 2020-06-18 | 2022-09-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Transistor and fabrication method thereof |

Family Cites Families (135)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH03101556U (ja) * | 1990-02-05 | 1991-10-23 | ||

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US20070194379A1 (en) | 2004-03-12 | 2007-08-23 | Japan Science And Technology Agency | Amorphous Oxide And Thin Film Transistor |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| EP2453480A2 (en) | 2004-11-10 | 2012-05-16 | Canon Kabushiki Kaisha | Amorphous oxide and field effect transistor |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7872259B2 (en) | 2004-11-10 | 2011-01-18 | Canon Kabushiki Kaisha | Light-emitting device |

| WO2006051995A1 (en) | 2004-11-10 | 2006-05-18 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI390735B (zh) | 2005-01-28 | 2013-03-21 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI412138B (zh) | 2005-01-28 | 2013-10-11 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| EP1998373A3 (en) | 2005-09-29 | 2012-10-31 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101103374B1 (ko) | 2005-11-15 | 2012-01-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| WO2008133345A1 (en) | 2007-04-25 | 2008-11-06 | Canon Kabushiki Kaisha | Oxynitride semiconductor |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| KR101799265B1 (ko) | 2009-11-13 | 2017-11-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| KR102426613B1 (ko) * | 2009-11-28 | 2022-07-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| WO2011068028A1 (en) | 2009-12-04 | 2011-06-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor element, semiconductor device, and method for manufacturing the same |

| KR20170142998A (ko) | 2009-12-25 | 2017-12-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작 방법 |

| DE112011101410B4 (de) * | 2010-04-23 | 2018-03-01 | Semiconductor Energy Laboratory Co., Ltd. | Verfahren zum Herstellen einer Halbleitervorrichtung |

| KR101809105B1 (ko) | 2010-08-06 | 2017-12-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 집적 회로 |

| US8673426B2 (en) * | 2011-06-29 | 2014-03-18 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, method of manufacturing the driver circuit, and display device including the driver circuit |

| US9048323B2 (en) * | 2012-04-30 | 2015-06-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9059219B2 (en) * | 2012-06-27 | 2015-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| JP6006558B2 (ja) | 2012-07-17 | 2016-10-12 | 株式会社半導体エネルギー研究所 | 半導体装置及びその製造方法 |

| TWI799011B (zh) * | 2012-09-14 | 2023-04-11 | 日商半導體能源研究所股份有限公司 | 半導體裝置及其製造方法 |

| TWI620324B (zh) | 2013-04-12 | 2018-04-01 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| KR20140132878A (ko) * | 2013-05-08 | 2014-11-19 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| TWI809225B (zh) | 2013-05-16 | 2023-07-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| TWI669824B (zh) | 2013-05-16 | 2019-08-21 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| KR20200038333A (ko) | 2013-05-20 | 2020-04-10 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US9293599B2 (en) | 2013-05-20 | 2016-03-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9343579B2 (en) | 2013-05-20 | 2016-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR102537022B1 (ko) | 2013-05-20 | 2023-05-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP6374221B2 (ja) | 2013-06-05 | 2018-08-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI624936B (zh) | 2013-06-05 | 2018-05-21 | 半導體能源研究所股份有限公司 | 顯示裝置 |

| JP6475424B2 (ja) | 2013-06-05 | 2019-02-27 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP6400336B2 (ja) | 2013-06-05 | 2018-10-03 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2015195327A (ja) | 2013-06-05 | 2015-11-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US20140374744A1 (en) | 2013-06-19 | 2014-12-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR102290801B1 (ko) | 2013-06-21 | 2021-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US9006736B2 (en) | 2013-07-12 | 2015-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6322503B2 (ja) | 2013-07-16 | 2018-05-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI632688B (zh) | 2013-07-25 | 2018-08-11 | 半導體能源研究所股份有限公司 | 半導體裝置以及半導體裝置的製造方法 |

| JP2015053477A (ja) | 2013-08-05 | 2015-03-19 | 株式会社半導体エネルギー研究所 | 半導体装置および半導体装置の作製方法 |

| JP6401977B2 (ja) | 2013-09-06 | 2018-10-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9461126B2 (en) | 2013-09-13 | 2016-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, clocked inverter circuit, sequential circuit, and semiconductor device including sequential circuit |

| KR20160132982A (ko) | 2014-03-18 | 2016-11-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치와 그 제작 방법 |

| WO2015145292A1 (en) | 2014-03-28 | 2015-10-01 | Semiconductor Energy Laboratory Co., Ltd. | Transistor and semiconductor device |

-

2015

- 2015-04-14 US US14/685,737 patent/US9780226B2/en active Active

- 2015-04-17 TW TW104112447A patent/TWI655771B/zh not_active IP Right Cessation

- 2015-04-20 KR KR1020150055132A patent/KR102344557B1/ko active IP Right Grant

- 2015-04-20 JP JP2015085631A patent/JP6534557B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW201543673A (zh) | 2015-11-16 |

| KR102344557B1 (ko) | 2021-12-30 |

| US9780226B2 (en) | 2017-10-03 |

| US20150311346A1 (en) | 2015-10-29 |

| JP2015216367A (ja) | 2015-12-03 |

| KR20150123718A (ko) | 2015-11-04 |

| TWI655771B (zh) | 2019-04-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6534557B2 (ja) | 半導体装置 | |

| US11282865B2 (en) | Semiconductor device including indium at insulating film interface | |

| US11862454B2 (en) | Semiconductor device and display device including the same | |

| US10431600B2 (en) | Method for manufacturing a semiconductor device including a metal oxide film | |

| US10438815B2 (en) | Manufacturing method of semiconductor device comprising oxide semiconductor film | |

| US20200321454A1 (en) | Semiconductor device and method for manufacturing the same | |

| US9768315B2 (en) | Semiconductor device and display device having the same | |

| US9496412B2 (en) | Semiconductor device, manufacturing method thereof, and display device including the semiconductor device | |

| US10290656B2 (en) | Semiconductor device with oxide semiconductor film electrical characteristic change of which is inhibited | |

| CN108292684B (zh) | 半导体装置、该半导体装置的制造方法或包括该半导体装置的显示装置 | |

| JP2016027649A (ja) | 半導体装置、該半導体装置を有する表示装置 | |

| US20160111548A1 (en) | Semiconductor device, manufacturing method thereof, display device, and display module | |

| JP2018006732A (ja) | 半導体装置、該半導体装置の作製方法、または該半導体装置を有する表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180403 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180403 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20181227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190529 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6534557 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |