JP6154880B2 - 表示装置の作製方法 - Google Patents

表示装置の作製方法 Download PDFInfo

- Publication number

- JP6154880B2 JP6154880B2 JP2015225539A JP2015225539A JP6154880B2 JP 6154880 B2 JP6154880 B2 JP 6154880B2 JP 2015225539 A JP2015225539 A JP 2015225539A JP 2015225539 A JP2015225539 A JP 2015225539A JP 6154880 B2 JP6154880 B2 JP 6154880B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor film

- substrate

- electrode

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 60

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 239000004065 semiconductor Substances 0.000 claims description 199

- 239000000758 substrate Substances 0.000 claims description 103

- 239000007789 gas Substances 0.000 claims description 76

- 229910052739 hydrogen Inorganic materials 0.000 claims description 42

- 239000001257 hydrogen Substances 0.000 claims description 42

- 230000015572 biosynthetic process Effects 0.000 claims description 40

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 37

- 229910052710 silicon Inorganic materials 0.000 claims description 32

- 239000010703 silicon Substances 0.000 claims description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 28

- 238000005268 plasma chemical vapour deposition Methods 0.000 claims description 26

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 18

- 230000001965 increasing effect Effects 0.000 claims description 17

- 229910052786 argon Inorganic materials 0.000 claims description 9

- 239000001307 helium Substances 0.000 claims description 6

- 229910052734 helium Inorganic materials 0.000 claims description 6

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims description 6

- 230000003247 decreasing effect Effects 0.000 claims description 5

- 238000010438 heat treatment Methods 0.000 claims description 5

- 238000005137 deposition process Methods 0.000 claims 1

- 239000010408 film Substances 0.000 description 347

- 238000006243 chemical reaction Methods 0.000 description 72

- 239000010409 thin film Substances 0.000 description 68

- 239000012535 impurity Substances 0.000 description 36

- 239000004973 liquid crystal related substance Substances 0.000 description 25

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 25

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 24

- 239000010410 layer Substances 0.000 description 23

- 230000008569 process Effects 0.000 description 19

- 238000005530 etching Methods 0.000 description 18

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 17

- 239000001301 oxygen Substances 0.000 description 17

- 229910052760 oxygen Inorganic materials 0.000 description 17

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 16

- 239000011521 glass Substances 0.000 description 16

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 14

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- 239000013078 crystal Substances 0.000 description 11

- 238000000151 deposition Methods 0.000 description 11

- 238000009832 plasma treatment Methods 0.000 description 11

- 229910052990 silicon hydride Inorganic materials 0.000 description 11

- 238000012545 processing Methods 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 9

- 229910021417 amorphous silicon Inorganic materials 0.000 description 9

- 239000007795 chemical reaction product Substances 0.000 description 9

- 238000004140 cleaning Methods 0.000 description 9

- 239000000463 material Substances 0.000 description 9

- 238000002834 transmittance Methods 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 7

- 239000000460 chlorine Substances 0.000 description 7

- 230000008021 deposition Effects 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 229910052750 molybdenum Inorganic materials 0.000 description 6

- 239000011733 molybdenum Substances 0.000 description 6

- 239000012495 reaction gas Substances 0.000 description 6

- 239000000565 sealant Substances 0.000 description 6

- 230000005236 sound signal Effects 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- 239000000203 mixture Substances 0.000 description 5

- 229910000077 silane Inorganic materials 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 4

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 4

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 4

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 4

- 229910052794 bromium Inorganic materials 0.000 description 4

- 229910052801 chlorine Inorganic materials 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 230000001276 controlling effect Effects 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 239000011737 fluorine Substances 0.000 description 4

- 229910052731 fluorine Inorganic materials 0.000 description 4

- 239000011630 iodine Substances 0.000 description 4

- 229910052740 iodine Inorganic materials 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 229920006267 polyester film Polymers 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- 229910000838 Al alloy Inorganic materials 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 239000013081 microcrystal Substances 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 230000006911 nucleation Effects 0.000 description 3

- 238000010899 nucleation Methods 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 239000011148 porous material Substances 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- WXRGABKACDFXMG-UHFFFAOYSA-N trimethylborane Chemical compound CB(C)C WXRGABKACDFXMG-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 238000001237 Raman spectrum Methods 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910000423 chromium oxide Inorganic materials 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 238000007667 floating Methods 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 238000005286 illumination Methods 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- -1 silicon halide Chemical class 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 238000009751 slip forming Methods 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 230000007723 transport mechanism Effects 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910019974 CrSi Inorganic materials 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 238000006124 Pilkington process Methods 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 239000002178 crystalline material Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000005038 ethylene vinyl acetate Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 239000003779 heat-resistant material Substances 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 238000007500 overflow downdraw method Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

Description

及びその作製方法に関する。

て薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタはI

Cや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチン

グ素子として開発が急がれている。薄膜トランジスタには、チャネル領域を形成する半導

体が非晶質シリコンで形成されるものと、多結晶シリコンで形成されるものがある。

FTが知られている(特許文献1及び特許文献2参照)。微結晶シリコンは、非晶質シリ

コンと同様にプラズマCVD法により作製される。例えば、プラズマCVD法による微結

晶シリコン膜の作製方法として、30MHz以上のVHF(Very High Fre

quency)帯の高周波を利用する発明が開示されている(特許文献3参照)。

を形成する場合、ゲート絶縁膜界面には非晶質構造を有する半導体膜が薄く形成され、薄

膜トランジスタの電気特性に影響を及ぼすおそれがある。この問題を解決するため、例え

ば、特許文献4では、半導体膜の成膜速度を異ならせ成膜初期において成長速度を遅くし

、その後成膜速度を高くする方法が提案されている。

加工した後、最終的にテレビやパーソナルコンピュータの画面に合わせた寸法に分断して

製造されている。1枚のマザーガラスから複数枚のパネルを取り出すようにして、パネル

1枚当たりのコストを低減するためである。液晶テレビの市場では、画面サイズ(パネル

サイズ)の大型化と販売価格の低下が急激に進んでいる。大画面化と低価格化に対応して

生産性を向上するために、ここ数年、マザーガラスの大型化が進められている。

mであった。その後、マザーガラスのサイズは、第2世代(400mm×500mm)、

第3世代(550mm×650mm)、第4世代(730mm×920mm)第5世代(

1000mm×1200mm)、第6世代(2450mm×1850mm)、第7世代(

1870mm×2200mm)、第8世代(2000mm×2400mm)、第9世代(

2450mm×3050mm)、第10世代(2850mm×3050mm)と一途に大

型化が図られている。

下により反応室中に存在する酸素(O)等の不純物元素等が成膜される膜中に取り込まれ

やすく、酸素等が取り込まれることによって結晶化が阻害され、そのような微結晶半導体

膜で形成された薄膜トランジスタの電気特性が低下するという問題がある。

形成するためにプラズマCVD装置の電極面積も大型化することとなる。この場合、反応

室の内壁の面積も大きくなるため、微結晶シリコン膜の成膜中に不純物元素が膜中に取り

込まれやすくなる。

大きさが、高周波電源の周波数の波長に近くなってくる。例えば、27MHzの電源周波

数の場合、波長は1100mmであり、60MHzでは500mm、120MHzでは2

50mmとなる。このような場合、表面定在波の影響が顕著に現れるようになり、プラズ

マCVD装置の反応室内のプラズマ密度分布が不均一になり、ガラス基板に形成される薄

膜の膜質や厚さの面内均一性が損なわれるといったことが問題となる。

よい薄膜トランジスタ及び当該薄膜トランジスタを有する表示装置を提供することを課題

とする。

上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて微結晶

半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程とを有し

、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成された

ゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成するものであって、反応室

の圧力を一旦10−5Pa以下とした後、基板の温度を100℃以上200℃以下として

水素及び珪素気体を導入し、ゲート絶縁膜表面に形成される反応生成物に水素プラズマを

作用させてエッチング(除去)を行いながら成膜を行うことによって、微結晶半導体膜を

形成する。

ト電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて

微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程と

を有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成

されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、

反応室の圧力を一旦10−5Pa以下とした後、基板の温度を100℃以上200℃以下

として水素及び希ガスを導入し、ゲート絶縁膜の表面に水素プラズマ及び希ガスプラズマ

を作用させた後、珪素気体を導入し、ゲート絶縁膜表面に形成される反応生成物に水素プ

ラズマを作用させてエッチング(除去)を行いながら成膜を行うことによって、微結晶半

導体膜を形成する。

ト電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて

微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程と

を有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成

されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、

反応室の圧力を一旦10−5Pa以下とした後、基板の温度を100℃以上200℃以下

として水素及び珪素気体を導入し、HF帯(3MHz〜30MHz、代表的には13.5

6MHz)の第1の高周波電力と、VHF帯(30MHz〜300MHz程度まで)の第

2の高周波電力を重畳して印加することによりプラズマの生成を行い、ゲート絶縁膜表面

に形成される反応生成物に水素プラズマを作用させて除去しつつ成膜を行うことによって

、微結晶半導体膜を形成する。

ト電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にプラズマCVD法を用いて

微結晶半導体膜を形成する工程と、微結晶半導体膜上に非晶質半導体膜を形成する工程と

を有し、微結晶半導体膜を形成する工程は、反応室内でプラズマを生成し、基板上に形成

されたゲート絶縁膜上に反応生成物を堆積して微結晶半導体膜を形成する工程であって、

反応室の圧力を一旦10−5Pa以下とした後、基板の温度を100℃以上200℃以下

として水素及び希ガスを導入し、HF帯の第1の高周波電力と、VHF帯の第2の高周波

電力を重畳して印加することによりプラズマの生成を行い、ゲート絶縁膜の表面に水素プ

ラズマ及び希ガスプラズマを作用させた後、珪素気体を導入し、ゲート絶縁膜表面に形成

される反応生成物に水素プラズマを作用させて除去しつつ成膜を行うことによって、微結

晶半導体膜を形成する。

又は希ガスの流量比を低減することを特徴とする。

スの導入を停止又は希ガスの流量比を低減することを特徴とする。

17atoms/cm3以下にすることを特徴とする。

液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される

素子をその範疇に含んでおり、具体的には無機EL(Electro Luminesc

ence)、有機EL等が含まれる。

を含むIC等を実装した状態にあるモジュールとを含む。

を有する表示装置を作製することができる。

様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形

態および詳細を変更し得ることは当業者であれば容易に理解される。従って、本実施の形

態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全

図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返し

の説明は省略する。

本実施の形態では、ボトムゲート型の薄膜トランジスタ(TFT)を有する表示装置の作

製方法に関して図面を参照して説明する。以下の説明では、nチャネル型の薄膜トランジ

スタについて説明する。

膜を形成する(図1(A)、図5(A)参照)。

ノシリケートガラスなど、フュージョン法やフロート法で作製される無アルカリガラス基

板、セラミック基板の他、本作製工程の処理温度に耐えうる耐熱性を有するプラスチック

基板等を用いることができる。また、ステンレス合金などの金属基板の表面に絶縁膜を設

けた基板を適用しても良い。

ウムなどの金属またはその合金を用いて形成する。ゲート電極101は、スパッタリング

法や真空蒸着法で基板100上に導電膜を形成し、当該導電膜上にフォトリソグラフィ技

術またはインクジェット法によりレジストマスクを形成し、当該マスクを用いて導電膜を

エッチングすることで形成することができる。なお、ゲート電極101の密着性向上と下

地への不純物元素の拡散を防ぐバリアメタルとして、上記金属の窒化物膜を、基板100

及びゲート電極101の間に設けてもよい。

膜、酸化窒化珪素膜、または窒化酸化珪素膜で形成することができる。ここでは、ゲート

絶縁膜102として、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化酸化珪

素膜との順に積層して形成する。なお、ゲート絶縁膜を2層とせず、基板側から窒化珪素

膜または窒化酸化珪素膜と、酸化珪素膜または酸化窒化珪素膜と、窒化珪素膜または窒化

酸化珪素膜との順に3層積層して形成してもよい。また、ゲート絶縁膜を、酸化珪素膜、

窒化珪素膜、酸化窒化珪素膜、または窒化酸化珪素膜の単層で形成してもよい。

て、濃度範囲として酸素が55〜65原子%、窒素が1〜20原子%、Siが25〜35

原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。また、窒化酸化珪素膜

とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸

素が15〜30原子%、窒素が20〜35原子%、Siが25〜35原子%、水素が15

〜25原子%の範囲で含まれるものをいう。

晶シリコン膜)を形成する(図1(B)参照)。

成する。以下に、図4を参照して微結晶シリコン膜を成膜する工程の一例に関して説明す

る。なお、図4の説明は反応室を大気圧から真空排気200する段階から示されており、

その後に行われるプレコート201、基板搬入202、下地前処理203、成膜処理20

4、基板搬出205、クリーニング206の各処理が時系列的に示されている。

0−5Pa以下)とし反応室内の酸素(O)等の不純物元素を極力低減する。真空度とし

て10−5Paよりも低い圧力の超高真空排気する場合には、ターボ分子ポンプによる排

気を行い、さらにクライオポンプを使って真空排気する。また、反応室を加熱処理して内

壁からの脱ガス処理を行うことが好ましい。また、基板を加熱するヒータも動作させて温

度を安定化させる。基板の加熱温度は100℃以上300℃以下、好ましくは100℃以

上200℃以下で行う。

くは反応室のクリーニングに使用したエッチングガス)を除去するためにアルゴンなどの

希ガスを導入してプラズマ処理をすることが好ましい。この処理により到達真空度を上げ

ることができる。反応室の内壁を基板上に堆積されるべき膜と同種の膜で被覆する処理が

含まれている。本形態は微結晶シリコン膜を形成する工程を示し、内壁被覆膜としてシリ

コン膜を形成する処理が行われる。プレコート201はシランガスが導入された後、高周

波電力を印加してプラズマを生成する。シランガスは酸素、水分等と反応するので、シラ

ンガスを流し、さらにシランプラズマを生成することで反応室内の酸素、水分を除去する

ことができる。

は、真空排気されたロード室に保管されているので、基板を搬入したとしても真空度が著

しく悪化することはない。

行うことが好ましい。すなわち、ガラス基板上に設けられたゲート絶縁膜の表面上に微結

晶シリコン膜をプラズマCVD法で成膜する場合には、不純物や格子不整合などの要因に

より堆積初期段階において堆積された反応生成物(半導体膜)には非晶質層が形成されて

しまう。この非晶質層の厚さを極力低減し、可能であれば無くすために下地前処理203

を行うことが好ましい。

用により行うことが好ましい。希ガスプラズマ処理としては、アルゴン、クリプトン、キ

セノンなど質量数の大きい希ガス元素を用いることが好ましい。表面に付着した酸素、水

分、有機物、金属元素などをスパッタリングの効果で除去するためである。水素プラズマ

処理は、水素ラジカルにより、表面に吸着した前記不純物の除去と、絶縁膜若しくは非晶

質シリコン膜に対するエッチング作用により清浄表面を形成するのに有効である。また、

希ガスプラズマ処理と水素プラズマ処理を併用することにより微結晶核生成を促進する作

用も実現される。

である。微結晶シリコン膜は、水素及び珪素気体(水素化珪素気体又はハロゲン化珪素気

体)を混合してプラズマにより成膜する。珪素気体は水素で10倍から2000倍に希釈

される。

マを作用させて除去(エッチング)しつつ成膜を行い、微結晶半導体膜を形成する。つま

り、SiH3ラジカルの堆積による膜成長反応と、水素ラジカルによるエッチング反応と

を競争的に起こさせて微結晶構造を含む半導体膜を形成する。

×1017atoms/cm3以下とするように形成を行うことが好ましい。膜中の酸素

濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass S

pectrometry)を用いて測定することができる。

ラズマ処理で除去(エッチング)しつつ成膜を行うことにより、ゲート絶縁膜102上に

形成される結晶核生成を促進させ、当該結晶核を利用して微結晶半導体膜を形成する。そ

のため、不純物や格子不整合などの要因により堆積初期段階において堆積された半導体膜

に非晶質層が形成された場合であっても、この非晶質層の厚さを極力低減し、ゲート絶縁

膜102により近く微結晶半導体膜を形成することが可能となる。

膜を行うので成膜速度が遅くなるが、成膜前に反応室の圧力を一旦超高真空(10−5P

a以下)とし反応室内の水分や酸素(O)等の吸着不純物の不純物元素を低減した後に成

膜を行うことによって、成膜速度を遅くした場合であっても膜中への酸素(O)等の不純

物元素の取り込み(半導体膜の酸化等)を低減し、結晶化の阻害を抑制することができる

。その結果、ゲート絶縁膜102により近く結晶性が高い半導体膜を形成することができ

る。

て行う。例えば、成膜が進につれ、珪素気体の流量に対する水素の流量比が小さくなるよ

うに珪素気体の流量を増加させる。成膜開始時には水素の流量:珪素気体の流量を200

0:1程度にしておき、成膜終了時には50:1程度になるまで徐々に珪素気体の流量を

増加(水素の流量を減少)させ微結晶半導体膜を形成することができる。

り返して行ってもよい。この場合、半導体膜の堆積と半導体膜の除去(エッチング)を繰

り返し行うことによって、ゲート絶縁膜102上に形成される結晶核生成を促進させるこ

とができる。

ゴンなどの希ガスを供給し続ける期間を設けてもよい。成膜の初期段階にゲート絶縁膜1

02表面に堆積される半導体膜に、アルゴンプラズマを作用させて表面の改質を行い、表

面に吸着した水分や不純物の除去を行うことによって、微結晶核の生成を促進させること

ができる。

下で行う。微結晶シリコン膜の成長表面を水素で不活性化し、微結晶シリコンの成長を促

進するためには100℃以上200℃以下で成膜を行うことが好ましい。

、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することがで

きる。

0MHz〜300MHz程度まで)の高周波電力を重畳印加して生成されるプラズマを利

用して成膜やプラズマ処理をしてもよい。表面定在波を引き起こさない第1の高周波電力

を供給してプラズマを生成するとともに、VHF帯に属する第2の高周波電力を供給して

プラズマの高密度化を図ることで長辺が2000mmを超える大面積基板に均質で膜質の

良い薄膜を形成することが可能となる。

中に反応室を構成する金属を不純物として取り込んでしまうのを防ぐことができる。すな

わち、反応室内をシリコンで被覆しておくことで、反応室内がプラズマにより食刻される

のを防ぐことができ、微結晶シリコン膜中に含まれる不純物濃度を低減することができる

。

Vとすべての気体中で最も高いイオン化エネルギーを持ち、そのイオン化エネルギーより

も少し低い、約20eVの準位に準安定状態があるので、放電持続中においては、イオン

化にはその差約4eVしか必要としない。そのため放電開始電圧も全ての気体中最も低い

値を示す。このような特性から、ヘリウムはプラズマを安定的に維持することができる。

また、均一なプラズマを形成することができるので、微結晶シリコン膜を堆積する基板の

面積が大きくなってもプラズマ密度の均一化を図る効果を奏する。

を止めて基板搬出205を行う。引き続き別基板に対して成膜処理を行う場合には、基板

搬入202の段階に戻り同じ処理が行われる。反応室内に付着した被膜や粉末を除去する

には、クリーニング206を行う。

ッチングを行う。また、ClF3のようにプラズマを利用しなくてもエッチングが可能な

ガスを導入して行う。クリーニング206においては基板加熱用のヒータを切って、温度

を下げて行うことが好ましい。エッチングによる反応副生成物の生成を抑えるためである

。クリーニング206の終了後はプレコート201に戻り、以下同様の処理を行えば良い

。

結晶を含む)の中間的な構造の半導体を含む膜である。この半導体は、自由エネルギー的

に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質

なものであり、その粒径を0.5〜20nmとして非単結晶半導体中に分散させて存在せ

しめることが可能である。微結晶半導体の代表例である微結晶シリコンは、そのラマンス

ペクトルが単結晶シリコンを示す520.6cm−1よりも低波数側に、シフトしている

。即ち、481cm−1以上520.6cm−1以下の間に微結晶シリコンのラマンスペ

クトルのピークがある。

p型を付与する不純物元素を、成膜と同時に、或いは成膜後に添加することで、しきい値

制御をすることが可能となる。p型を付与する不純物元素としては、代表的にはホウ素で

あり、トリメチルボロン(CH3)3B、B2H6、BF3などの不純物気体を1ppm

〜1000ppm、好ましくは1〜100ppmの割合で水素化珪素に混入させると良い

。そしてボロンの濃度を、例えば1×1014〜6×1016atoms/cm3とする

と良い。トリメチルボロンは、反応室の内壁等に付着した場合であってもクリーニングに

より容易に除去できるためトリメチルボロンを用いることが好ましい。ボロンの濃度を制

御することによって、i型又はp型の微結晶半導体膜を形成することができる。

く20nm以下で形成する。微結晶半導体膜103は、後に形成される薄膜トランジスタ

のチャネル形成領域として機能する。微結晶半導体膜の厚さを上記の範囲内とすることで

、後に形成される薄膜トランジスタは、完全空乏型とすることができる。

0と遅いため、膜厚を薄くすることでスループットを向上させることができる。

例えば、非晶質シリコン膜)、一導電型を付与する不純物が添加された半導体膜105を

順に形成する(図1(C)参照)。

形成することが好ましい。さらには、ゲート絶縁膜102、微結晶半導体膜103、非晶

質半導体膜104、及び一導電型を付与する不純物が添加された半導体膜105を連続的

に形成することが好ましい。ゲート絶縁膜102、微結晶半導体膜103、及び非晶質半

導体膜104を大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊

する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、薄膜

トランジスタ特性のばらつきを低減することができる。

の流量をさらに制御し、水素を減少、珪素気体を増加させ、珪素気体の流量に対する水素

の流量比を小さくすることで微結晶半導体膜上に連続的に形成してもよい。非晶質半導体

膜104を形成する工程は、より水素の流量を減少させ、珪素気体(水素化珪素気体、又

はハロゲン化珪素気体)のみで行ってもよい。この場合、微結晶半導体膜103の成長表

面を大気に触れさせることなく、微結晶半導体膜103上に非晶質半導体膜104を形成

することができる。

化珪素を用いて、プラズマCVD法により形成することができる。また、上記水素化珪素

に、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元

素で希釈して非晶質半導体を形成することができる。水素化珪素の流量の1倍以上20倍

以下、好ましくは1倍以上10倍以下、更に好ましくは1倍以上5倍以下の流量の水素を

用いて、水素を含む非晶質半導体を形成することができる。また、上記水素化珪素と窒素

またはアンモニアとを用いることで、窒素を含む非晶質半導体を形成することができる。

また、上記水素化珪素と、フッ素、塩素、臭素、またはヨウ素を含む気体(F2、Cl2

、Br2、I2、HF、HCl、HBr、HI等)を用いることで、フッ素、塩素、臭素

、またはヨウ素を含む非晶質半導体を形成することができる。なお、水素化珪素の代わり

に、SiH2Cl2、SiHCl3、SiCl4、SiF4等を用いることができる。

でスパッタリングして非晶質半導体膜を形成することができる。このとき、アンモニア、

窒素、またはN2Oを雰囲気中に含ませることにより、窒素を含む非晶質半導体膜を形成

することができる。また、雰囲気中にフッ素、塩素、臭素、またはヨウ素を含む気体(F

2、Cl2、Br2、I2、HF、HCl、HBr、HI等)を含ませることにより、フ

ッ素、塩素、臭素、またはヨウ素を含む非晶質半導体を形成することができる。

のため、周波数が数十MHz〜数百MHzの高周波プラズマCVD法、またはマイクロ波

プラズマCVD法で形成する場合は、結晶粒を含まない非晶質半導体となるように、成膜

条件を制御することが好ましい。また、非晶質半導体膜104は、n型の電気伝導性を示

す非晶質半導体(例えば、非晶質シリコン膜)で形成してもよい。

部エッチングされる場合があるが、そのときに、非晶質半導体膜104の一部が残存する

厚さで形成することが好ましい。代表的には、100nm以上500nm以下、好ましく

は200nm以上300nm以下の厚さで形成することが好ましい。薄膜トランジスタに

高い電圧(例えば15V程度)を印加する表示装置、代表的には液晶表示装置において、

バッファー層として機能する非晶質半導体膜104の膜厚を上記範囲に示すように厚く形

成すると、耐圧が高くなり、薄膜トランジスタに高い電圧が印加されても、薄膜トランジ

スタが劣化することを回避することができる。非晶質半導体膜104を上記の膜厚の範囲

で形成することにより、非晶質半導体膜104は微結晶半導体膜103より厚く形成され

る。

含む非晶質半導体膜を形成することで、微結晶半導体膜103に含まれる結晶粒の表面の

自然酸化を防止することが可能である。特に、非晶質半導体と微結晶粒が接する領域では

、結晶格子の歪に由来し、亀裂が入りやすい。この亀裂が酸素に触れると結晶粒は酸化さ

れ、酸化珪素が形成される。しかしながら、微結晶半導体膜103の表面にバッファー層

として機能する非晶質半導体膜104を形成することで、微結晶半導体膜103に含まれ

る微結晶粒の酸化を防ぐことができる。また、バッファー層を形成することで、後にソー

ス領域及びドレイン領域を形成する際に発生するエッチング残渣が微結晶半導体に混入す

ることを防ぐことができる。

素、若しくはハロゲンを含む非晶質半導体で形成するため、非晶質半導体のエネルギーギ

ャップが微結晶半導体に比べて大きく(非晶質半導体のエネルギーギャップは1.6〜1

.8eV、微結晶半導体のエネルギーギャップは1.1〜1.5eV)、抵抗が高く、移

動度が低くなる。このため、後に形成される薄膜トランジスタにおいて、ソース領域及び

ドレイン領域と、微結晶半導体膜103との間に形成される非晶質半導体膜104は高抵

抗領域として機能し、微結晶半導体膜103を構成する微結晶半導体がチャネル形成領域

として機能する。

スタを形成する場合には、代表的な不純物元素としてリンを添加すれば良く、水素化珪素

にPH3などの不純物気体を加えれば良い。また、pチャネル型の薄膜トランジスタを形

成する場合には、代表的な不純物元素としてボロンを添加すれば良く、水素化珪素にトリ

メチルボロン(CH3)3B、B2H6などの不純物気体を加えれば良い。一導電型を付

与する不純物が添加された半導体膜105は、微結晶半導体、または非晶質半導体で形成

することができる。一導電型を付与する不純物が添加された半導体膜105は2nm以上

50nm以下の厚さで形成する。一導電型を付与する不純物が添加された半導体膜の膜厚

を、薄くすることでスループットを向上させることができる。

、当該マスク121を用いて微結晶半導体膜103、非晶質半導体膜104及び導電型を

付与する不純物が添加された半導体膜105をエッチングする(図1(D)、図5(B)

参照)。この後、マスク121を除去する。

6を形成し、当該導電膜106上にマスク122を形成する(図2(A)参照)。

ム、モリブデンなどの耐熱性向上元素若しくはヒロック防止元素が添加されたアルミニウ

ム合金の単層または積層で形成することが好ましい。また、半導体膜105と接する側の

膜を、チタン、タンタル、モリブデン、タングステン、またはこれらの元素の窒化物で形

成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。

更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モ

リブデン、タングステン、またはこれらの元素の窒化物で挟んだ積層構造としてもよい。

例えば、導電膜106として、モリブデン膜とアルミニウム膜とモリブデン膜を順に3層

積層した構造とすることができる。また、導電膜106として、チタン膜とアルミニウム

膜とチタン膜を順に3層積層した構造とすることができる。

、金、銅などの導電性ナノペーストを用いてスクリーン印刷法、インクジェット法等を用

いて吐出し焼成して形成しても良い。

104及び半導体膜105をパターニングした後に導電膜106を形成する場合を示して

いるが、図1(C)の工程を省略し、微結晶半導体膜103、非晶質半導体膜104、半

導体膜105及び導電膜106を連続して順に積層させた後にマスク122を形成しても

よい。この場合、マスク121を形成しなくてよいため、工程を簡略化することができる

。

電極106a及びドレイン電極106bを形成する(図2(B)、図5(C)参照)。

ッファー層として機能する非晶質半導体膜104をエッチングして、ソース領域105a

及びドレイン領域105b、ソース電極106a及びドレイン電極106bを形成する(

図2(C)、図6(A)参照)。なお、バッファー層として機能する非晶質半導体膜10

4は一部のみがエッチングされたものであり、微結晶半導体膜103の表面を覆っている

。ここでは、ソース領域105aとドレイン領域105bの間に位置する非晶質半導体膜

104の表面に凹部が形成される。また、このとき、ソース領域105a及びドレイン領

域105bの端部とソース電極106a及びドレイン電極106bの端部はほぼ一致して

いる。

)、図6(B)参照)。

ドレイン電極106bの端部が選択的にエッチングされる。その結果、ソース電極106

a及びドレイン電極106bの端部と、ソース領域105a及びドレイン領域105bの

端部はそれぞれ一致せずずれており、ソース電極106a及びドレイン電極106bの端

部の外側に、ソース領域105a及びドレイン領域105bの端部が形成される。

は、それぞれソース配線またはドレイン配線としても機能する。

106bの端部がそれぞれ一致せずずれた形状となることで、ソース電極106aとドレ

イン電極106bとの端部の距離が離れるため、ソース電極106aとドレイン電極10

6b間のリーク電流やショートを防止することができる。また、ソース領域105aとソ

ース電極106aの端部、ドレイン領域105bとドレイン電極106bの端部がそれぞ

れ一致せずずれた形状となることで、ソース電極106a及びドレイン電極106b、ソ

ース領域105a及びドレイン領域105bの端部に電界が集中せず、ゲート電極101

と、ソース電極106a及びドレイン電極106bとの間でのリーク電流を防止すること

ができる。このため、信頼性が高く、且つ耐圧の高い薄膜トランジスタを作製することが

できる。

。

形成されており、当該凹部以外の領域がソース領域105a及びドレイン領域で覆われる

。即ち、非晶質半導体膜104に形成される凹部123により、ソース領域105a及び

ドレイン領域105bの距離が離れているため、ソース領域105a及びドレイン領域1

05bの間でのリーク電流を低減することができる。また、非晶質半導体膜104の一部

をエッチングすることにより凹部123を形成するため、ソース領域105a及びドレイ

ン領域105bの形成工程において発生するエッチング残渣を除去することができるため

、残渣を介してソース領域105a及びドレイン領域105bにリーク電流(寄生チャネ

ル)が発生することを回避することができる。

領域105bとの間に、バッファー層が形成されている。また、微結晶半導体の表面がバ

ッファー層で覆われている。高抵抗で形成されたバッファー層は、微結晶半導体と、ソー

ス領域105a及びドレイン領域105bとの間にまで延在しているため、薄膜トランジ

スタにリーク電流が発生することを低減することができると共に、高い電圧の印加による

劣化を低減することができる。また、微結晶半導体の表面に水素で表面が終端された非晶

質半導体がバッファー層として形成されているため、微結晶半導体の酸化を防止すること

が可能であると共に、ソース領域105a及びドレイン領域105bの形成工程に発生す

るエッチング残渣が微結晶半導体に混入することを防ぐことができる。

せずずれた形状となることで、ソース電極及びドレイン電極の端部の距離が離れるため、

ソース電極及びドレイン電極間のリーク電流やショートを防止することができる。

領域105b、非晶質半導体膜104及びゲート絶縁膜102上に絶縁膜107を形成す

る(図3(B)参照)。絶縁膜107は、ゲート絶縁膜102と同様に形成することがで

きる。なお、絶縁膜107は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純

物の侵入を防ぐためのものであり、緻密な膜が好ましい。

ン電極106bに接する画素電極108を形成する(図3(C)、図7参照)。

インジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウ

ム錫酸化物、インジウム錫酸化物(以下、ITOと示す)、インジウム亜鉛酸化物、酸化

珪素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができ

る。

成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート

抵抗が10000Ω/□以下、波長550nmにおける透光率が70%以上であることが

好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1Ω・cm以下で

あることが好ましい。

ば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンま

たはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

できる。なお、本実施の形態では、nチャネル型の薄膜トランジスタを形成する場合を示

したが、これに限られず、pチャネル型の薄膜トランジスタも一導電型を付与する不純物

が添加された半導体膜105をp型とすることによって同様に形成することができる。

能である。また、チャネル形成領域として機能する微結晶半導体膜103を微結晶半導体

で構成することにより1〜20cm2/V・secの電界効果移動度を得ることができる

。従って、本実施の形態では、薄膜トランジスタ110を画素部の画素のスイッチング用

素子として適用する例を示したが、これに限られず走査線(ゲート線)側の駆動回路等を

形成する素子として利用することができる。

が可能である。

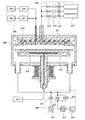

本実施の形態では、上記実施の形態1において微結晶半導体膜の成膜に用いたプラズマC

VD装置の一構成例に関して図11を参照して説明する。具体的に、本実施の形態では、

複数の高周波電力が印加されるプラズマCVD装置の一構成例に関して説明する。

排気できるように構成されている。反応室300には第1の電極301と第2の電極30

2が備えられている。

位が与えられ、基板を載置できるように構成されている。第1の電極301は絶縁材31

6により反応室300の内壁と絶縁分離され、高周波電力が漏洩しないように構成されて

いる。なお、図11では、第1の電極301と第2の電極302について容量結合型(平

行平板型)の構成を示しているが、異なる二以上の高周波電力を印加して反応室300の

内部にプラズマを生成できるものであれば、誘導結合型など他の構成を適用することもで

きる。

それらに対応して第1の整合器306と第2の整合器307が含まれている。第1の高周

波電源304と第2の高周波電源305から出力される高周波電力は、共に第1の電極3

01に供給される。第1の整合器306又は第2の整合器307の出力側には、一方の高

周波電力が流入しないように帯域通過フィルタを設けても良い。

適用され、HF帯である3MHzから30MHz、代表的には13.56MHzの周波数

が適用される。第2の高周波電源305が供給する高周波電力は、VHF帯の周波数であ

り概ね波長が10m未満の高周波が適用され、30MHz〜300MHzの高周波電力が

適用される。

1辺の長さの3倍以上を有し、第2の高周波電源305が供給する高周波電力の波長は、

それよりも短い波長を適用する。表面定在波を引き起こさない高周波電力を第1の電極3

01に供給してプラズマを生成するとともに、VHF帯に属する高周波電力を供給してプ

ラズマの高密度化を図ることで長辺が2000mmを超える大面積基板に均質で膜質の良

い薄膜を形成することが可能となる。

応ガスが充填されるシリンダ310、圧力調整弁311、ストップバルブ312、マスフ

ローコントローラ313などで構成されている。反応室300内において、第1の電極3

01は基板と対抗する面がシャワー板状に加工され、複数の細孔が設けられている。反応

ガスは、第1の電極301の内部の中空構造からこの細孔を通って反応室300に供給さ

れる。

04から高周波電力が供給される第1の電極301aと、第2の高周波電源305から高

周波電力が供給される第1の電極301bに分離されている。第1の電極301aと第1

の電極302bは基板と対抗する面は細孔が設けられると共に、櫛歯状にかみ合うように

構成され、隣接するもの同士は接触しないように絶縁材316で分離されている。図12

に示す構成は、図11で示す第1の電極301と置き換えることが可能であり、同様な効

果を得ることができる。

応室300内を所定の圧力に保持するように制御する機能が含まれている。排気手段30

9の構成としては、バタフライバルブ317、コンダクタンスバルブ318、ターボ分子

ポンプ319、ドライポンプ320などが含まれる。バタフライバルブ317とコンダク

タンスバルブ318を並列に配置する場合には、バタフライバルブ317を閉じてコンダ

クタンスバルブ318を動作させることで、反応ガスの排気速度を制御して反応室300

の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバル

ブ317を開くことで高真空排気が可能となる。

321を併用することが好ましい。その他、到達真空度として超高真空まで排気する場合

には、反応室300の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキン

グ用のヒータを設けても良い。

2に設けられている。基板加熱ヒータ314は第2の電極302内に設けられる場合、熱

伝導加熱方式が採用され、シースヒータなどで構成される。第1の電極301と第2の電

極302の間隔は適宜変更できるように、第2の電極302の高さ調節ができるように可

動式となる構成が含まれる。

ン膜に代表される絶縁膜、微結晶シリコン膜、非晶質シリコン膜に代表される半導体膜、

その他TFT及び光電変換装置などで使用される各種薄膜の形成が可能となる。特に長辺

が2000mmを超える大面積基板に前記薄膜を形成する場合において有用である。

たプラズマCVD装置を用いる場合について説明したが、これに限られず、反応ガスを替

えれば各種薄膜を形成することができる。半導体膜としては、非晶質シリコン膜、非晶質

シリコンゲルマニウム膜、非晶質シリコンカーバイト膜、微結晶シリコンゲルマニウム膜

、微結晶シリコンカーバイト膜などの成膜に本実施の形態で示したプラズマ装置を適用す

ることができる。絶縁膜としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン

膜、窒化酸化シリコン膜などの成膜に本実施の形態で示したプラズマ装置を適用すること

ができる。

が可能である。

本実施の形態では、上記実施の形態2で示される反応室が適用されるプラズマCVD装置

の一例として、複数の膜(ここでは、TFTを構成するゲート絶縁膜及び半導体膜)の成

膜に適した構成の一例に関して、図18を参照して説明する。

の装置は共通室323と、ロード/アンロード室322、第1反応室300a、第2反応

室300b、第3反応室300cを備えた構成となっている。ロード/アンロード室32

2のカセット324に装填される基板は、共通室323の搬送機構326によって各反応

室に搬出入される枚葉式の構成である。共通室323と各室の間にはゲートバルブ325

が備えられ、各反応室で行われる処理が、相互に干渉しないように構成されている。

ゲート絶縁膜などの絶縁膜を成膜し、第2反応室300bはチャネルを形成する微結晶半

導体層を成膜し、第3反応室300cはソース及びドレインを形成する一導電型の不純物

半導体層を成膜する反応室として充当される。勿論、反応室の数はこれに限定されるわけ

ではなく、必要に応じて任意に増減することができる。また、一の反応室で一の膜を成膜

するようにしても良いし、一の反応室で複数の膜を成膜するように構成しても良い。

いる。排気手段はこれらの真空ポンプの組み合わせに限定されるものではなく、概略10

−1Paから10−5Paの真空度にまで排気できるものであれば他の真空ポンプを適用

することができる。また、微結晶半導体膜を形成する第2反応室300bは超高真空まで

真空排気するものとして、クライオポンプ321が連結されている。排気手段と各反応室

との間にはバタフライバルブ317が設けられており、これによって真空排気を遮断させ

ることができ、コンダクタンスバルブ318によって排気速度を制御して、それぞれの反

応室の圧力を調節することができる。

れるシリンダ310、ストップバルブ312、マスフローコントローラ313などで構成

されている。ガス供給手段308gは第1反応室300aに接続され、ゲート絶縁膜を成

膜するためのガスを供給する。ガス供給手段308iは第2反応室300bに接続され、

微結晶半導体膜用のガスを供給する。ガス供給手段308nは第3反応室300cに接続

され、例えば、n型半導体膜用のガスを供給する。ガス供給手段308aはアルゴンを供

給し、ガス供給手段308fは反応室内のクリーニングに用いるエッチングガスを供給す

る系統であり、これらは各反応室共通のラインとして構成されている。

力供給手段303は高周波電源と整合器が含まれる。この場合、実施の形態2と同様に、

第1の高周波電源304と第2の高周波電源305、第1の整合器306と第2の整合器

307で構成することにより、均一性の良い薄膜を形成することができる。プラズマCV

D装置の構成を、各種ガラス基板のサイズ(第1世代と呼ばれる300mm×400mm

、第3世代の550mm×650mm、第4世代の730mm×920mm、第5世代の

1000mm×1200mm、第6世代の24500mm×1850mm、第7世代の1

870mm×2200mm、第8世代の2000mm×2400mm、第9世代の245

0×3050mm、第10世代の2850mm×3050mmなど)に合わせれば、どの

ようなサイズの基板に対しても均一性の良い薄膜を形成することができる。

数の異なる層を大気に触れさせることなく連続して積層することが可能となる。

が可能である。

本実施の形態では、上記実施と異なる薄膜トランジスタを有する表示装置の作製方法に関

して図面を参照して説明する。具体的には、多階調マスクを用いた作製方法に関して説明

する。

結晶半導体膜103、バッファー層として機能する非晶質半導体膜104、一導電型を付

与する不純物が添加された第3の半導体膜105及び導電膜106を順に積層して形成し

た後、導電膜106上にレジスト131を形成する。続いて、多階調マスク132を用い

てレジスト131に光を照射し、当該レジスト131を露光する(図8(A)参照)。

は、ポジ型レジストを用いて示す。

ことが可能なマスクであり、一度の露光及び現像工程により、複数(代表的には二種類)

の厚さの領域を有するレジストマスクを形成することが可能である。このため、多階調マ

スクを用いることで、フォトマスクの枚数を削減することが可能である。

、図15(C)に示すようなハーフトーンマスク132bがある。

及びその上に形成される遮光部134並びに回折格子135で構成される。遮光部134

においては、光の透過率が0%である。一方、回折格子135はスリット、ドット、メッ

シュ等の光透過部の間隔を、露光に用いる光の解像度限界以下の間隔とすることにより、

光の透過量を制御することができる。なお、回折格子135は、周期的なスリット、ドッ

ト、メッシュ、または非周期的なスリット、ドット、メッシュどちらも用いることができ

る。

部134及び回折格子135は、クロムや酸化クロム等の光を吸収する遮光材料を用いて

形成することができる。

部134においては、光透過率136は0%であり、遮光部134及び回折格子135が

設けられていない領域では光透過率136は100%である。また、回折格子135にお

いては、10〜70%の範囲で調整可能である。回折格子135における光の透過量の調

整は、回折格子のスリット、ドット、またはメッシュの間隔及びピッチの調整により可能

である。

及びその上に形成される半透過部137並びに遮光部138で構成される。半透過部13

7は、MoSiN、MoSi、MoSiO、MoSiON、CrSiなどを用いることが

できる。遮光部138は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成す

ることができる。

部138においては、光透過率139は0%であり、遮光部138及び半透過部137が

設けられていない領域では光透過率139は100%である。また、半透過部137にお

いては、10〜70%の範囲で調整可能である。半透過部137に於ける光の透過率の調

整は、半透過部137の材料により調整により可能である。

なる領域を有するレジストマスク141を形成することができる。

る非晶質半導体膜104、一導電型を付与する不純物が添加された第3の半導体膜105

及び導電膜106をエッチングし分離する(図9(A)参照)。

さが薄くなる。このとき、膜厚の薄い領域のレジスト(ゲート電極101の一部と重畳す

る領域)は除去され、図9(B)に示すように、分離されたレジストマスク142を形成

することができる。

105及びバッファー層として機能する非晶質半導体膜104をエッチングして、ソース

領域105a及びドレイン領域105b、ソース電極106a及びドレイン電極106b

を形成する(図9(C)参照)。なお、バッファー層として機能する非晶質半導体膜10

4は一部のみがエッチングされたものであり、微結晶半導体膜103の表面を覆っている

。ここでは、ソース領域105aとドレイン領域105bの間に位置する非晶質半導体膜

104の表面に凹部が形成される。

領域105b、非晶質半導体膜104及びゲート絶縁膜102上に絶縁膜107を形成す

る。続けて、絶縁膜107にコンタクトホールを形成し、当該コンタクトホールにおいて

ドレイン電極106bに接する画素電極108を形成する(図10参照)。

できる。

が可能である。

本実施の形態では、上記実施の形態で示した表示装置の一形態として液晶表示パネルに関

して図16を参照して説明する。図16(A)は、第1の基板4001上に形成された薄

膜トランジスタ4010及び液晶素子4013を第2の基板4006との間にシール材4

005によって封止したパネルの上面図であり、図16(B)は、図16(A)のC−D

における断面を示している。

2と走査線駆動回路4004を囲むようにして、シール材4005が設けられている。ま

た、画素部4002と走査線駆動回路4004の上に第2の基板4006が設けられてい

る。そのため、画素部4002と走査線駆動回路4004は、第1の基板4001とシー

ル材4005と第2の基板4006によって、液晶4008と共に封止されている。

域に、別途用意された基板上に多結晶半導体膜で形成された薄膜トランジスタ4009を

具備する信号線駆動回路4003が実装されている。なお、本実施の形態では、多結晶半

導体膜を用いた薄膜トランジスタ4009を有する信号線駆動回路4003を、第1の基

板4001に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで

信号線駆動回路4003を形成し、貼り合わせるようにしても良い。

トランジスタを複数有しており、図16(B)では、画素部4002に含まれる薄膜トラ

ンジスタ4010を例示している。薄膜トランジスタ4010は、上記実施の形態1、2

で示した薄膜トランジスタに相当する。また、走査線駆動回路4004を構成するトラン

ジスタを薄膜トランジスタ4010と同様の構成で設けることができる。

て液晶素子4013を構成する対向電極4031は、第2の基板4006上に形成されて

いる。画素電極4030と対向電極4031と液晶4008とが重なっている部分が、液

晶素子4013に相当する。

テンレス)、セラミックス、プラスチックを用いることができる。プラスチックとしては

、FRP(Fiberglass−Reinforced Plastics)板、PV

F(ポリビニルフルオライド)フィルム、ポリエステルフィルム、ポリエステルフィルム

またはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVF

フィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

セルギャップ)を制御するために設けられている。なお、球場のスペーサ4035の代わ

りに絶縁膜を選択的にエッチングすることで得られるスペーサを用いていても良い。

4002に与えられる各種信号及び電位は、引き回し配線4014、4015を介して、

FPC4018から供給されている。

ている。また、引き回し配線4014、4015は、薄膜トランジスタ4010のソース

電極及びドレイン電極と同じ導電膜で形成されている。

気的に接続されている。

更にカラーフィルタや遮蔽膜を有していても良い。

ている例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装

しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実

装しても良い。

VA(Vertical Alignment)型又は横電界方式の液晶表示装置とする

ことができる。

VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂

直方向を向く方式である。本実施の形態では、特に画素(ピクセル)をいくつかの領域(

サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されている。これをマル

チドメイン化あるいはマルチドメイン設計という。

階調表現する方式である。この方式によれば、視野角を約180度にまで広げることがで

きる。

る。

本実施の形態では、上記実施の形態で示した表示装置の一形態として発光表示パネルに関

して図17を参照して説明する。図17(A)は、第1の基板4001上に形成された薄

膜トランジスタ4010及び発光素子4011を第2の基板4006との間にシール材4

005によって封止したパネルの上面図であり、図17(B)は、図17(A)のE−F

における断面を示している。

トロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物

であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ば

れている。

2と走査線駆動回路4004を囲むようにして、シール材4005が設けられている。ま

た、画素部4002と走査線駆動回路4004の上に第2の基板4006が設けられてい

る。そのため、画素部4002と走査線駆動回路4004は、第1の基板4001とシー

ル材4005と第2の基板4006によって、充填材4007と共に密封されている。

域に、別途用意された基板上に多結晶半導体膜で形成された薄膜トランジスタ4009を

具備する信号線駆動回路4003が実装されている。なお、本実施の形態では、多結晶半

導体膜を用いた薄膜トランジスタ4009を有する信号線駆動回路4003を、第1の基

板4001に貼り合わせる例について説明するが、単結晶半導体を用いたトランジスタで

信号線駆動回路を形成し、貼り合わせるようにしても良い。

トランジスタを複数有しており、図17(B)では、画素部4002に含まれる薄膜トラ

ンジスタ4010を例示している。薄膜トランジスタ4010は、上記実施の形態1、2

で示した薄膜トランジスタに相当する。また、走査線駆動回路4004を構成するトラン

ジスタを薄膜トランジスタ4010と同様の構成で設けることができる。

極またはドレイン電極と電気的に接続されている。発光素子4011の構成は、発光素子

4011から取り出す光の方向や、薄膜トランジスタ4010の極性などに合わせて、適

宜変えることができる。

4002に与えられる各種信号及び電位は、図17(B)に示す断面図では図示されてい

ないが、引き回し配線4014及び4015を介して、FPC4018から供給されてい

る。

と同じ導電膜から形成されている。また、引き回し配線4014、4015は、薄膜トラ

ンジスタ4010のソース電極及びドレイン電極と同じ導電膜から形成されている。

気的に接続されている。

る。本実施の形態では、第2の基板4006側から光を取り出すため、第2の基板400

6は、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのよう

な透光性を有する材料で形成する。

脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、

ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEV

A(エチレンビニルアセテート)を用いることができる。

位相差板(λ/4板、λ/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよ

い。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により

反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

ている例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別

途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを

別途形成して実装しても良い。

る。

本発明により得られる表示装置等によって、アクティブマトリクス型表示装置モジュール

に用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施

できる。

イ(ゴーグル型ディスプレイ)、カーナビゲーション、プロジェクタ、カーステレオ、パ

ーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍

等)などが挙げられる。それらの一例を図13に示す。

、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付け

られた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面200

3が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えら

れている。このように、テレビジョン装置を完成させることができる。

組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム2004を

介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受

信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもでき

る。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操作機

2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表

示部2007が設けられていても良い。

ネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成に

おいて、主画面2003を視野角の優れた液晶表示パネルで形成し、サブ画面2008を

低消費電力で表示可能な発光表示パネルで形成しても良い。また、低消費電力化を優先さ

せるためには、主画面2003を発光表示パネルで形成し、サブ画面2008を発光表示

パネルで形成し、サブ画面2008は点滅可能とする構成としても良い。

、画素部921が形成されている。信号線駆動回路922と走査線駆動回路923は、表

示パネル900にCOG方式により実装されていても良い。

のうち、映像信号を増幅する映像信号増幅回路925と、そこから出力される信号を赤、

緑、青の各色に対応した色信号に変換する映像信号処理回路926と、その映像信号をド

ライバICの入力仕様に変換するためのコントロール回路927などを有している。コン

トロール回路927は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動す

る場合には、信号線側に信号分割回路928を設け、入力デジタル信号をm個に分割して

供給する構成としても良い。

その出力は音声信号処理回路930を経てスピーカー933に供給される。制御回路93

1は受信局(受信周波数)や音量の制御情報を入力部932から受け、チューナ924や

音声信号処理回路930に信号を送出する。

め、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表

示媒体としても様々な用途に適用することができる。

示部2302、操作部2303などを含んで構成されている。表示部2302においては

、上記実施の形態で説明した表示装置を適用することで、量産性を高めることができる。

含んでいる。表示部2402に、上記実施の形態に示す表示装置を適用することにより、

量産性を高めることができる。

、支柱2504、台2505、電源2506を含む。本発明の発光装置を照明部2501

に用いることにより作製される。なお、照明器具には天井固定型の照明器具または壁掛け

型の照明器具なども含まれる。上記実施の形態に示す表示装置を適用することにより、量

産性を高めることができ、安価な卓上照明器具を提供することができる。

101 ゲート電極

102 ゲート絶縁膜

103 微結晶半導体膜

104 非晶質半導体膜

105 半導体膜

106 導電膜

107 絶縁膜

108 画素電極

110 薄膜トランジスタ

121 マスク

122 マスク

123 凹部

131 レジスト

132 多階調マスク

133 基板

134 遮光部

135 回折格子

136 光透過率

137 半透過部

138 遮光部

139 光透過率

141 レジストマスク

142 レジストマスク

200 真空排気

201 プレコート

202 基板搬入

203 下地前処理

204 成膜処理

205 基板搬出

206 クリーニング

207 破線

300 反応室

301 電極

302 電極

303 高周波電力供給手段

304 高周波電源

305 高周波電源

306 整合器

307 整合器

308 ガス供給手段

309 排気手段

310 シリンダ

311 圧力調整弁

312 ストップバルブ

313 マスフローコントローラ

314 基板加熱ヒータ

315 ヒータコントローラ

316 絶縁材

317 バタフライバルブ

318 コンダクタンスバルブ

319 ターボ分子ポンプ

320 ドライポンプ

321 クライオポンプ

322 ロード/アンロード室

323 共通室

324 カセット

325 ゲートバルブ

326 搬送機構

900 表示パネル

921 画素部

922 信号線駆動回路

923 走査線駆動回路

924 チューナ

925 映像信号増幅回路

926 映像信号処理回路

927 コントロール回路

928 信号分割回路

929 音声信号増幅回路

930 音声信号処理回路

931 制御回路

932 入力部

933 スピーカー

105a ソース領域

105b ドレイン領域

106a ソース電極

106b ドレイン電極

132a グレートーンマスク

132b ハーフトーンマスク

2001 筐体

2002 表示用パネル

2003 主画面

2004 モデム

2005 受信機

2006 リモコン操作機

2007 表示部

2008 サブ画面

2009 スピーカー部

2301 携帯電話機

2302 表示部

2303 操作部

2401 本体

2402 表示部

2501 照明部

2502 傘

2503 可変アーム

2504 支柱

2505 台

2506 電源

300a 反応室

300b 反応室

300c 反応室

301a 電極

301b 電極

302b 電極

308a ガス供給手段

308f ガス供給手段

308g ガス供給手段

308i ガス供給手段

308n ガス供給手段

4001 基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4007 充填材

4008 液晶

4009 薄膜トランジスタ

4010 薄膜トランジスタ

4011 発光素子

4013 液晶素子

4014 配線

4016 接続端子

4017 画素電極

4018 FPC

4019 異方性導電膜

4030 画素電極

4031 対向電極

4035 スペーサ

4041 薄膜トランジスタ

Claims (2)

- 基板上にゲート電極を形成する第1の工程と、

前記ゲート電極上にゲート絶縁膜を形成する第2の工程と、

前記ゲート絶縁膜上にプラズマCVD法を用いて微結晶半導体膜を形成する第3の工程と、を有し、

前記第3の工程は、

真空排気が行なわれた反応室内に前記基板を搬入し、

前記基板を搬入した後に前記微結晶半導体膜を形成することによって行われ、

前記微結晶半導体膜の形成は、珪素気体の流量に対する水素の流量比の増減を繰り返すことによって行われ、

前記微結晶半導体膜の形成は、前記基板の温度を100℃以上300℃以下に加熱して行われ、

前記微結晶半導体膜の成膜処理は、第1の期間と第2の期間を有し、

前記第2の期間は、前記第1の期間の後であり、

前記第1の期間において、アルゴン及びヘリウムが供給され、

前記第2の期間において、アルゴンが供給されず、ヘリウムが供給されることを特徴とする表示装置の作製方法。 - 請求項1において、

前記微結晶半導体膜の形成は、第1の高周波電源と第2の高周波電源とを用いてプラズマを生成し、プラズマCVD法を用いて行われ、

前記第1の高周波電源が供給する第1の高周波電力と、前記第2の高周波電源が供給する第2の高周波電力とは周波数が異なることを特徴とする表示装置の作製方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007212904 | 2007-08-17 | ||

| JP2007212904 | 2007-08-17 | ||

| JP2007212903 | 2007-08-17 | ||

| JP2007212903 | 2007-08-17 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013262465A Division JP2014131036A (ja) | 2007-08-17 | 2013-12-19 | 成膜装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016076715A JP2016076715A (ja) | 2016-05-12 |

| JP6154880B2 true JP6154880B2 (ja) | 2017-06-28 |

Family

ID=40363287

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008202638A Expired - Fee Related JP5478037B2 (ja) | 2007-08-17 | 2008-08-06 | 表示装置の作製方法 |

| JP2013262465A Withdrawn JP2014131036A (ja) | 2007-08-17 | 2013-12-19 | 成膜装置 |

| JP2015225539A Expired - Fee Related JP6154880B2 (ja) | 2007-08-17 | 2015-11-18 | 表示装置の作製方法 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008202638A Expired - Fee Related JP5478037B2 (ja) | 2007-08-17 | 2008-08-06 | 表示装置の作製方法 |

| JP2013262465A Withdrawn JP2014131036A (ja) | 2007-08-17 | 2013-12-19 | 成膜装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7611930B2 (ja) |

| JP (3) | JP5478037B2 (ja) |

| CN (1) | CN101369539B (ja) |

| TW (1) | TWI506677B (ja) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI521292B (zh) | 2007-07-20 | 2016-02-11 | 半導體能源研究所股份有限公司 | 液晶顯示裝置 |

| JP2009071289A (ja) * | 2007-08-17 | 2009-04-02 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| US8101444B2 (en) | 2007-08-17 | 2012-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US20090090915A1 (en) | 2007-10-05 | 2009-04-09 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, display device having thin film transistor, and method for manufacturing the same |

| KR101889287B1 (ko) | 2008-09-19 | 2018-08-20 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 |

| JP5361651B2 (ja) | 2008-10-22 | 2013-12-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN102246310B (zh) * | 2008-12-11 | 2013-11-06 | 株式会社半导体能源研究所 | 薄膜晶体管及显示装置 |

| KR20100067612A (ko) * | 2008-12-11 | 2010-06-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 박막 트랜지스터 및 표시 장치 |

| US8114720B2 (en) | 2008-12-25 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7989325B2 (en) * | 2009-01-13 | 2011-08-02 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing crystalline semiconductor film and method for manufacturing thin film transistor |

| US9312156B2 (en) * | 2009-03-27 | 2016-04-12 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor |

| KR101402294B1 (ko) * | 2009-10-21 | 2014-06-02 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제작방법 |

| JP5698950B2 (ja) | 2009-10-23 | 2015-04-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI535028B (zh) * | 2009-12-21 | 2016-05-21 | 半導體能源研究所股份有限公司 | 薄膜電晶體 |

| US8431496B2 (en) * | 2010-03-05 | 2013-04-30 | Semiconductor Energy Labortory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP5764394B2 (ja) * | 2010-06-18 | 2015-08-19 | 株式会社半導体エネルギー研究所 | 光電変換素子 |

| US8778745B2 (en) * | 2010-06-29 | 2014-07-15 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US8440548B2 (en) | 2010-08-06 | 2013-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of microcrystalline silicon film and manufacturing method of thin film transistor |

| US8704230B2 (en) | 2010-08-26 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US8647919B2 (en) | 2010-09-13 | 2014-02-11 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting display device and method for manufacturing the same |

| US8338240B2 (en) * | 2010-10-01 | 2012-12-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing transistor |

| US8895116B2 (en) | 2010-11-04 | 2014-11-25 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of crystalline semiconductor film and manufacturing method of semiconductor device |

| US8450158B2 (en) * | 2010-11-04 | 2013-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming microcrystalline semiconductor film and method for manufacturing semiconductor device |

| US9048327B2 (en) * | 2011-01-25 | 2015-06-02 | Semiconductor Energy Laboratory Co., Ltd. | Microcrystalline semiconductor film, method for manufacturing the same, and method for manufacturing semiconductor device |

| US9111775B2 (en) | 2011-01-28 | 2015-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Silicon structure and manufacturing methods thereof and of capacitor including silicon structure |

| US8828859B2 (en) * | 2011-02-11 | 2014-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming semiconductor film and method for manufacturing semiconductor device |

| CN102646634B (zh) * | 2011-04-29 | 2013-06-12 | 京东方科技集团股份有限公司 | Tft-lcd阵列基板制造方法 |

| US9660092B2 (en) | 2011-08-31 | 2017-05-23 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor thin film transistor including oxygen release layer |

| WO2015181679A1 (en) * | 2014-05-27 | 2015-12-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| CN104532192B (zh) * | 2014-12-19 | 2018-01-30 | 深圳市华星光电技术有限公司 | 蒸镀装置 |

| JP6861479B2 (ja) * | 2016-06-24 | 2021-04-21 | 東京エレクトロン株式会社 | プラズマ成膜方法およびプラズマ成膜装置 |

| CN107658267B (zh) * | 2017-09-15 | 2020-11-06 | 惠科股份有限公司 | 阵列基板的制造方法 |

| CN108417583B (zh) * | 2018-03-09 | 2021-10-29 | 惠科股份有限公司 | 一种阵列基板的制造方法和阵列基板 |

| KR20200083813A (ko) * | 2018-12-28 | 2020-07-09 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN110634390A (zh) * | 2019-09-20 | 2019-12-31 | 武汉天马微电子有限公司 | 一种显示面板及显示装置 |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5091334A (en) * | 1980-03-03 | 1992-02-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JPS6092475A (ja) * | 1983-10-25 | 1985-05-24 | Anelva Corp | 光化学的薄膜製造方法および装置 |

| US4727044A (en) * | 1984-05-18 | 1988-02-23 | Semiconductor Energy Laboratory Co., Ltd. | Method of making a thin film transistor with laser recrystallized source and drain |

| JP2726414B2 (ja) * | 1987-03-04 | 1998-03-11 | 株式会社東芝 | ケイ素系薄膜の製造方法 |

| JPH01321625A (ja) * | 1988-06-23 | 1989-12-27 | Hitachi Ltd | 薄膜形成方法及び薄膜形成装置 |

| JP2708569B2 (ja) * | 1989-09-20 | 1998-02-04 | 株式会社日立製作所 | 真空装置の脱ガス方法及び脱ガス装置 |

| JPH03278466A (ja) * | 1990-03-27 | 1991-12-10 | Toshiba Corp | 薄膜トランジスタおよびその製造方法 |

| JP2791422B2 (ja) | 1990-12-25 | 1998-08-27 | 株式会社 半導体エネルギー研究所 | 電気光学装置およびその作製方法 |

| US7115902B1 (en) * | 1990-11-20 | 2006-10-03 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JP2561572B2 (ja) * | 1991-05-11 | 1996-12-11 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型電界効果トランジスタの作製方法 |

| JP3255942B2 (ja) * | 1991-06-19 | 2002-02-12 | 株式会社半導体エネルギー研究所 | 逆スタガ薄膜トランジスタの作製方法 |

| JP3025789B2 (ja) * | 1991-06-28 | 2000-03-27 | 東京エレクトロン株式会社 | 排気方法 |

| US5582880A (en) * | 1992-03-27 | 1996-12-10 | Canon Kabushiki Kaisha | Method of manufacturing non-single crystal film and non-single crystal semiconductor device |

| JP3201492B2 (ja) | 1992-03-27 | 2001-08-20 | キヤノン株式会社 | 非晶質シリコン膜の製造方法、非晶質窒化シリコン膜の製造方法、微結晶シリコン膜の製造方法、及び非単結晶半導体装置 |

| JPH05335256A (ja) * | 1992-06-03 | 1993-12-17 | Fujitsu Ltd | 半導体製造装置及びその清掃方法 |

| DE69420474T2 (de) * | 1993-06-30 | 2000-05-18 | Applied Materials Inc | Verfahren zum Spülen und Auspumpen einer Vakuumkammer bis Ultra-Hoch-Vakuum |

| JPH0794749A (ja) | 1993-09-22 | 1995-04-07 | Toshiba Corp | 薄膜トランジスタの製造方法 |

| JP3152829B2 (ja) * | 1994-01-18 | 2001-04-03 | 株式会社東芝 | 半導体装置の製造方法 |

| JPH0897436A (ja) * | 1994-07-27 | 1996-04-12 | Sharp Corp | 薄膜半導体素子とその製造方法 |

| US6699530B2 (en) * | 1995-07-06 | 2004-03-02 | Applied Materials, Inc. | Method for constructing a film on a semiconductor wafer |

| JPH08148690A (ja) * | 1994-11-25 | 1996-06-07 | Sharp Corp | 薄膜トランジスタおよび半導体膜の製造方法 |

| JPH09232235A (ja) * | 1995-02-24 | 1997-09-05 | Mitsui Toatsu Chem Inc | 光電変換素子 |

| JPH10229213A (ja) * | 1996-12-12 | 1998-08-25 | Canon Inc | 半導体薄膜の形成方法 |

| JP3581546B2 (ja) * | 1997-11-27 | 2004-10-27 | キヤノン株式会社 | 微結晶シリコン膜形成方法および光起電力素子の製造方法 |

| JP2002083773A (ja) * | 2000-09-06 | 2002-03-22 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2002329878A (ja) * | 2001-04-27 | 2002-11-15 | Sharp Corp | 薄膜太陽電池および薄膜太陽電池の作製方法 |

| EP1609884B1 (en) * | 2003-03-31 | 2013-08-28 | Konica Minolta Holdings, Inc. | Thin film forming apparatus and method for forming thin film |

| JP4748954B2 (ja) | 2003-07-14 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| TWI368774B (en) * | 2003-07-14 | 2012-07-21 | Semiconductor Energy Lab | Light-emitting device |

| CN101483180B (zh) * | 2003-07-14 | 2011-11-16 | 株式会社半导体能源研究所 | 液晶显示器件 |

| JP4393812B2 (ja) * | 2003-07-18 | 2010-01-06 | 株式会社半導体エネルギー研究所 | 表示装置及び電子機器 |

| JP2005167051A (ja) * | 2003-12-04 | 2005-06-23 | Sony Corp | 薄膜トランジスタおよび薄膜トランジスタの製造方法 |

| JP2007049171A (ja) * | 2006-08-30 | 2007-02-22 | Chi Mei Electronics Corp | 微結晶薄膜トランジスタを用いた画像表示装置 |

-

2008

- 2008-08-05 US US12/186,001 patent/US7611930B2/en not_active Expired - Fee Related

- 2008-08-06 JP JP2008202638A patent/JP5478037B2/ja not_active Expired - Fee Related

- 2008-08-12 TW TW097130667A patent/TWI506677B/zh not_active IP Right Cessation

- 2008-08-15 CN CN2008101456660A patent/CN101369539B/zh not_active Expired - Fee Related

-

2013

- 2013-12-19 JP JP2013262465A patent/JP2014131036A/ja not_active Withdrawn

-

2015

- 2015-11-18 JP JP2015225539A patent/JP6154880B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7611930B2 (en) | 2009-11-03 |

| CN101369539A (zh) | 2009-02-18 |

| CN101369539B (zh) | 2012-10-31 |

| TW200924028A (en) | 2009-06-01 |

| JP2016076715A (ja) | 2016-05-12 |

| JP2014131036A (ja) | 2014-07-10 |

| TWI506677B (zh) | 2015-11-01 |

| US20090047758A1 (en) | 2009-02-19 |

| JP2009071286A (ja) | 2009-04-02 |

| JP5478037B2 (ja) | 2014-04-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6154880B2 (ja) | 表示装置の作製方法 | |

| JP7290769B2 (ja) | 半導体装置 | |

| JP7432052B2 (ja) | 表示装置 | |

| JP5331407B2 (ja) | 半導体装置の作製方法 | |

| US8633485B2 (en) | Display device and manufacturing method thereof | |

| US7910929B2 (en) | Semiconductor device | |

| US8247315B2 (en) | Plasma processing apparatus and method for manufacturing semiconductor device | |

| US20090137103A1 (en) | Method for manufacturing semiconductor device | |

| US20090114917A1 (en) | Thin film transistor and display device having the thin film transistor | |

| JP2009071290A (ja) | 半導体装置の作製方法 | |

| JP2009071288A (ja) | 半導体装置の作製方法 | |

| US8242562B2 (en) | Film deposition apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161115 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170516 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170602 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6154880 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |