JP5952771B2 - メモリ装置及びメモリコントローラ並びにメモリシステム - Google Patents

メモリ装置及びメモリコントローラ並びにメモリシステム Download PDFInfo

- Publication number

- JP5952771B2 JP5952771B2 JP2013091188A JP2013091188A JP5952771B2 JP 5952771 B2 JP5952771 B2 JP 5952771B2 JP 2013091188 A JP2013091188 A JP 2013091188A JP 2013091188 A JP2013091188 A JP 2013091188A JP 5952771 B2 JP5952771 B2 JP 5952771B2

- Authority

- JP

- Japan

- Prior art keywords

- refresh

- address

- row

- cell row

- memory

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000015654 memory Effects 0.000 title claims description 280

- 230000004044 response Effects 0.000 claims description 22

- 238000012546 transfer Methods 0.000 claims description 9

- 239000012189 cellwax Substances 0.000 claims 1

- 238000011084 recovery Methods 0.000 description 50

- 238000010586 diagram Methods 0.000 description 35

- 238000000034 method Methods 0.000 description 31

- 238000004891 communication Methods 0.000 description 13

- 238000003491 array Methods 0.000 description 12

- 239000000872 buffer Substances 0.000 description 12

- 230000003111 delayed effect Effects 0.000 description 7

- 238000004806 packaging method and process Methods 0.000 description 5

- 230000009977 dual effect Effects 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000007704 transition Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 230000001934 delay Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 102100035964 Gastrokine-2 Human genes 0.000 description 2

- 101001075215 Homo sapiens Gastrokine-2 Proteins 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 238000013500 data storage Methods 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 208000023514 Barrett esophagus Diseases 0.000 description 1

- 101100033865 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) RFA1 gene Proteins 0.000 description 1

- 101100524516 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) RFA2 gene Proteins 0.000 description 1

- 101100425597 Solanum lycopersicum Tm-1 gene Proteins 0.000 description 1

- 230000003139 buffering effect Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229920002678 cellulose Polymers 0.000 description 1

- 239000001913 cellulose Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 230000014509 gene expression Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 238000010295 mobile communication Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000002829 reductive effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- CJBPIZBHRWDBGQ-COSFPPCYSA-N rfa-1 Chemical compound C1([C@H]2N[C@H](CC3(N=C4C=5C6=C7O[C@](C6=O)(C)O/C=C/[C@@H]([C@H]([C@@H](OC(C)=O)[C@@H](C)[C@@H](O)[C@H](C)[C@@H](O)[C@@H](C)\C=C\C=C(C)/C(=O)NC(=C4N3)C(=O)C=5C(O)=C7C)C)OC)C2)C=2C=CC=CC=2)=CC=CC=C1 CJBPIZBHRWDBGQ-COSFPPCYSA-N 0.000 description 1

- BINCGEGLXIMJFO-JQSLHUNDSA-N rfa-2 Chemical compound C1([C@H]2N[C@H](CC3(N=C4C=5C6=C7O[C@](C6=O)(C)O/C=C/[C@@H]([C@H]([C@@H](OC(C)=O)[C@@H](C)[C@@H](O)[C@H](C)[C@@H](O)[C@@H](C)\C=C\C=C(C)/C(=O)NC(=C4N3)C(=O)C=5C(O)=C7C)C)OC)C2)C=2C=CC(F)=CC=2)=CC=C(F)C=C1 BINCGEGLXIMJFO-JQSLHUNDSA-N 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003936 working memory Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40615—Internal triggering or timing of refresh, e.g. hidden refresh, self refresh, pseudo-SRAMs

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40611—External triggering or timing of internal or partially internal refresh operations, e.g. auto-refresh or CAS-before-RAS triggered refresh

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40618—Refresh operations over multiple banks or interleaving

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/406—Management or control of the refreshing or charge-regeneration cycles

- G11C11/40622—Partial refresh of memory arrays

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/401—Indexing scheme relating to cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C2211/406—Refreshing of dynamic cells

- G11C2211/4061—Calibration or ate or cycle tuning

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Databases & Information Systems (AREA)

- Dram (AREA)

- Memory System (AREA)

Description

またDRAMの製造工程が微細化されるにつれ、書き込みパス上の抵抗成分の増加によって書き込み動作に困難が発生しているという問題がある。

また、本発明の他の目的は、書き込み特性を向上させることのできるメモリコントローラを提供するにある。

また、本発明の他の目的は、上記メモリ装置を含むメモリシステムを提供するにある。

前記リフレッシュ制御回路は、前記第1時間周期の間、前記第1ウィークセルロウがリフレッシュされなかったと判断された場合、前記リフレッシュ動作のシークエンスにリフレッシュ動作を追加することが好ましい。

前記リフレッシュ制御回路は、前記第1時間周期より長い第2時間周期でノーマルセルロウをリフレッシュすることが好ましい。

前記リフレッシュ制御回路は、第2ロウのスケジュールされたリフレッシュ動作を前記第1ウィークセルロウのリフレッシュ動作に差し替えることが好ましい。

前記リフレッシュ制御回路は、前記第1ウィークセルロウのリフレッシュ動作後、直ちに前記第2ロウのリフレッシュ動作を行うことが好ましい。

前記リフレッシュ制御回路は、第2ロウのリフレッシュ動作と前記第1ウィークセルロウに対するリフレッシュ動作が同時に行われるようにすることが好ましい。

前記リフレッシュ制御回路は、所定の時間内にリフレッシュスケジュールが前記第1ウィークセルロウのリフレッシュ動作を含むか否かを判断するために、前記リフレッシュスケジュールを分析することが好ましい。

前記メモリセルアレイは、対応するウィークセルロウを識別する複数のウィークセルロウアドレスを保存するアドレステーブルをさらに含むことが好ましい。

前記メモリ装置は、前記ウィークセルロウアドレスをメモリコントローラに転送することが好ましい。

前記制御回路は、前記第1アドレスに該当する第1セルロウをリフレッシュする第1リフレッシュコマンドを生成し、前記第1セルロウは、前記第1セルロウに対する書き込み動作後、第1時間周期内にリフレッシュされることが好ましい。

前記制御回路は、第2時間周期内に第2セルロウをリフレッシュする少なくとも一つの第2リフレッシュコマンドを生成し、前記第2時間周期は前記第1時間周期より大きいことが好ましい。

前記制御回路は、前記アドレス比較部に応答して前記テーブルに保存されたウィークセルロウに対する第1書き込みコマンドと、前記テーブルで識別されなかったノーマルセルロウに対する第2書き込みコマンドとを生成することが好ましい。

前記第1書き込みコマンドは、前記メモリ装置が第1時間周期の間、書き込み動作を遂行するようにさせ、前記第2書き込みコマンドは前記メモリ装置が前記第1時間周期より小さい第2時間周期の間、書き込み動作を遂行するようにさせることが好ましい。

前記第1書き込みコマンドのコマンドコードは、前記第2書き込みコマンドのコマンドコードと異なることが好ましい。

前記制御回路は、第1時間インジケータを有する前記第1書き込みコマンドと、第2時間インジケータを有する前記第2書き込みコマンドとを生成し、前記メモリ装置は、前記第1及び第2時間インジケータに応答して前記第1及び第2時間周期の間、それぞれ書き込み動作を行うことが好ましい。

図面上の同一構成要素に対しては同一参照符号を使用し、同一構成要素に対しての重複した説明は省略する。

図1を参照すると、本発明の一実施形態に係る揮発性メモリ装置の動作方法では、先にアドレス情報を保存する(ステップS110)。

このようなアドレス情報は、揮発性メモリ装置のパッケージングの前又は後に、揮発性メモリ装置に含まれるアドレス保存部に保存することができる。揮発性メモリ装置は半導体メモリチップであってもよい。

ここで、ウィークセルは、書き込み性能がノーマルセルより良くないセルを意味する。

M個のリフレッシュロウアドレスは、M個のリフレッシュロウアドレスと関連したメモリセルのリフレッシュ動作の開始以前に生成することができる。

代案としては、M個のリフレッシュロウアドレスはM個のリフレッシュロウアドレスと関連したメモリセルのリフレッシュ動作の開始中に生成することができる。

例えば、パワーアップシークエンスが完了した後、リフレッシュ動作を開始することができる。ある実施形態においては、リフレッシュ動作は、実質的に周期的に認可されるメモリコントローラから受信されたリフレッシュコマンドREFに応答して内部的にリフレッシュロウアドレスを生成し、リフレッシュロウアドレスに対応するメモリセルロウをリフレッシュするオートリフレッシュ動作であるか、又はセルフリフレッシュ進入コマンドSREに応答してセルフリフレッシュモードに進入し、セルフリフレッシュモードでビルトインタイマ(built−in timer)を利用してメモリセルロウを周期的にリフレッシュするセルフリフレッシュ動作であってもよい。

リフレッシュロウアドレスは、メモリコントローラによってメモリ装置に提供することができる。

そこで、Kは自然数であってもよい。M個のリフレッシュロウアドレスのメモリセルロウに対するリフレッシュ動作の間に一つのメモリセルロウに対する書き込み動作が発生する可能性がある。例えば、メモリコントローラのような外部のソースから特定のメモリセルロウに対する書き込みコマンドが受信されることがある。

ここで、所定の時間とは、揮発性メモリ装置のテスト動作の間と同様に予め選択することができる。

所定の時間は、対応するウィークセルロウに保存されたデータが失われることを防止するために選択されてウィークセルロウの保存特性を回復する(例えば、DRAMウィークセル内部のセルキャパシタにチャージを復元する)リフレッシュ動作が遂行されることを許容する。

この場合に各グループのウィークセルロウは、互いに同じ所定の時間を設ける。

図1に示したステップの間では揮発性メモリ装置に対するさまざまな違う動作、例えば書き込み動作及び読み出し動作などを遂行することができる。

代案としては、第(K+1)メモリセルロウに対するリフレッシュ動作は、次のスケジュールのリフレッシュ周期まで遅延されることができる。

また、各メモリセルロウは、同じワードラインに接続されたメモリセルのロウを示し、ウィークセルロウは書き込み特性がノーマルメモリセルに比べて良くないウィークセルを少なくとも一つ以上含むメモリセルロウを表す。

ウィークセルロウは、ウィークセルとノーマルセルを全部含むことができる。

図2を参照すると、ステップS140の後、リフレッシュスケジュールが所定の周期時間の間に、ウィークセルロウに対するリフレッシュ動作を含んでいるか(又は、含むか)を判断するためにリフレッシュスケジュールを分析する(ステップS151)。

そこで、リフレッシュロウアドレスREF_ADDRはリフレッシュ動作に対して現在スケジュールされたロウであり、Xは所定の周期時間の間にリフレッシュ動作がスケジュールされたメモリセルロウの数を表す。

もし、リフレッシュスケジュールが所定の周期時間内でウィークセルロウに対するリフレッシュ動作を含む場合(ステップS151で「はい」)、リフレッシュスケジュールは変動しないで、ステップS150aが完了する(又は、第(K+1)メモリセルロウに対するリフレッシュのような次のスケジュールされたリフレッシュ動作が完了した途端、完了する)。

例えば、ウィークセルロウアドレスに対するリフレッシュ動作をリフレッシュスケジュールを含むテーブルに追加することができる。又は、ウィークセルロウアドレスが次にリフレッシュされるロウとして挿入され、挿入されていなかった場合は、リフレッシュできるようにスケジュールされたロウアドレスを遅延させることができる(例えば、リフレッシュカウンタの出力を「1」リフレッシュサイクル分遅延させてウィークセルロウアドレスが次にリフレッシュをロウとして挿入することができる)。ステップS150aは、ステップS152後に完了する(又は、第(K+1)メモリセルロウに対するリフレッシュのような次のスケジュールされたリフレッシュ動作が完了した途端、完了する)。

図3を参照すると、M個のリフレッシュロウアドレスのうち、リフレッシュロウアドレスREF_ADDRに対応する以前の、「次にスケジュールされた」ロウと比較することにより、「次にスケジュールされた」リフレッシュ周期の間、ウィークセルロウアドレスがリフレッシュされる。例えば、このような以前の、「次にスケジュールされた」ロウアドレスは、リフレッシュが順次に遂行される場合、第(K+1)メモリセルロウであってもよい。

例えば、ウィークセルロウが、直ちにリフレッシュされ、リフレッシュロウアドレスREF_ADDRに対応する以前の「次にスケジュールされた」ロウは、ロウサイクルタイムtRCの後でリフレッシュすることができる。ロウサイクルタイムtRCは、フルサイクルを完了するために必要なクロックサイクルの数に該当する時間であり、一つのロウをプリチャージ実行と活性化実行を含む。

互いに同じである場合に、次のリフレッシュ動作はウィークセルロウに対するリフレッシュ動作であってもよい(従って、追加的なリフレッシュ動作を避けることができる。)。

本発明の実施形態に係る揮発性メモリ装置の動作方法では、このようなフェイルビットの数が増加することを防止するためにウィークセルロウをノーマルセルロウに比べて、最初書き込み後、より早くリフレッシュすることができる。

例えば、ウィークセルロウは、第(K+1)メモリセルロウに対するリフレッシュのような、次のスケジュールされたリフレッシュ動作と同時に、又は順次にリフレッシュされるか、或いは、リフレッシュスケジュールが所定の時間内にウィークセルロウに対するリフレッシュ動作が含まれるように修正できる。

図5を参照すると、揮発性メモリ装置200は、制御ロジック210、アドレスレジスタ220、バンク制御ロジック230、ロウアドレスマルチプレクサ240、カラムアドレスラッチ250、ロウデコーダ、カラムデコーダ、メモリセルアレイ、センスアンプ部、入出力ゲート回路290、データ入出力バッファ295、アドレス保存部225、アドレス比較部(address comparing unit(ACU))300、及びリフレッシュ制御回路(refresh control circuit)400を含む。

図4には4個のバンクを含む揮発性メモリ装置200の例を示すが、実施形態により、揮発性メモリ装置200は任意の数のバンクを含むことができる。

アドレスレジスタ220は、受信されたバンクアドレスBANK_ADDRをバンク制御ロジック230に提供し、受信されたロウアドレスROW_ADDRをロウアドレスマルチプレクサ240に提供し、受信されたカラムアドレスCOL_ADDRをカラムアドレスラッチ250に提供する。

バンク制御信号に応答して、第1〜第4バンクロウデコーダ(260a、260b、260c、260d)の内の、バンクアドレスBANK_ADDRに対応するバンクロウデコーダが活性化され、第1〜第4バンクカラムデコーダ(270a、270b、270c、270d)の内の、バンクアドレスBANK_ADDRに対応するバンクカラムデコーダが活性化される。

ロウアドレスマルチプレクサ240は、ロウアドレスROW_ADDR又はリフレッシュロウアドレスREF_ADDRを選択的に出力することができる。ロウアドレスマルチプレクサ240から出力されたロウアドレスは、第1〜第4バンクロウデコーダ(260a、260b、260c、260d)にそれぞれ印加される。

例えば、活性化されたバンクロウデコーダは、ロウアドレスに対応するワードラインにワードライン駆動電圧を印加する。ワードライン駆動電圧は対応するワードラインに接続されたメモリセルのアクセストランジスタをターンオンさせ、メモリセルのデータがビットラインの対に転送されて感知増幅器によって増幅されることができるようにする。データの感知は知られているようにメモリセルに前記データをリストアしてデータをリフレッシュすることができる。

また、カラムアドレスラッチ250は、バーストモードで、受信されたカラムアドレスCOL_ADDRを徐々に増加させることができる。カラムアドレスラッチ250は、一時的に保存、又は、徐々に増加したカラムアドレスCOL_ADDRを第1〜第4バンクカラムデコーダ(270a、270b、270c、270d)にそれぞれ印加する。

読み出しデータラッチに保存されたデータDQは、データ入出力バッファ295を介してメモリコントローラに提供される。第1〜第4バンクメモリアレイ(280a、280b、280c、280d)の内のいずれか一つのバンクメモリアレイに書き込みされるデータDQは、メモリコントローラからデータ入出力バッファ295に提供される。データ入出力バッファ295に提供されたデータDQは書き込みドライバを介して一つのバンクメモリアレイに書き込みされる。

例えば、制御ロジック210は、揮発性メモリ装置200が書き込み動作又は読み出し動作を遂行するための制御信号を生成する。

制御ロジック210は、メモリコントローラから受信されるコマンドCMDをデコードするコマンドデコーダ211及び揮発性メモリ装置200の動作モードを設定するためのモードレジスタ212を含む。例えば、コマンドデコーダ211は、書き込みイネーブル信号(/WE)、ロウアドレスストローブ信号(/RAS)、カラムアドレスストローブ信号(/CAS)、チップ選択信号(/CS)などをデコードしてコマンドCMDに対応する制御信号を生成する。また、制御ロジック210は、同期方式で揮発性メモリ装置200を駆動するためのクロック信号(CLK)及びクロックイネーブル信号(/CKE)をさらに受信する。また、制御ロジック210はリフレッシュコマンドREFに応答してリフレッシュ制御回路400がオートリフレッシュ動作を遂行するよう制御したり、セルフリフレッシュ進入コマンドSREに応答してリフレッシュ制御回路400がセルフリフレッシュ動作を遂行するよう制御する。

アドレス保存部225に保存されたアドレス情報ADDR_INFOは、メモリセルアレイに含まれたウィークセルロウのロウアドレスである。一実施形態において、アドレス情報ADDR_INFOは揮発性メモリ装置のパッケージング前にアドレス保存部225に保存させることができる。他の実施形態において、アドレス情報ADDR_INFOは揮発性メモリ装置のパッケージング後にアドレス保存部225に保存させることもできる。

実施形態により、アドレス保存部225は電気的プログラマブル・フューズ・メモリ(programmable fuse memory,)、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワンタイム・プログラマブル・メモリ、フラッシュメモリなどのような多様な種類の不揮発性メモリ装置で具現できる。

ウィークセルロウの数は、メモリセルをウィークセルとノーマルセル(従って、ウィークセルロウとノーマルセルロウ)とに区分するメモリセルの最小データ保有時間を決める関数として調節することができる。

ウィークセルロウの数は、ウィークセルロウをスペアメモリセルロウに変えて調節することができる。ウィークセルロウの数はメモリセルロウの少なくとも2%又は少なくとも10%、或いは、20%でもある。

アドレス比較部300は、上記比較の結果に基づいて、第1マッチ信号MATCH1を生成する。例えば、メモリセルロウにデータを書き込むための書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致しない場合、アドレス比較部330は、第1ロジックレベルの第1マッチ信号MATCH1をスイッチ227とリフレッシュ制御回路400に提供する。例えば、メモリセルロウにデータを書き込むための書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致する場合、アドレス比較部330は第2ロジックレベルの第1マッチ信号MATCH1をスイッチ227とリフレッシュ制御回路400に提供する。

例えば、書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致しなくて第1マッチ信号MATCH1が第1ロジックレベルを有する場合、スイッチ227はアドレス情報ADDR_INFOをリフレッシュ制御回路400に提供することができないことがある。例えば、書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致して第1マッチ信号MATCH1が第2ロジックレベルを有する場合、スイッチ227はアドレス情報ADDR_INFOをリフレッシュ制御回路400に提供することができる。

第2ロジックレベルに応答してスイッチ227が閉じられて、マッチングされるロウアドレスがリフレッシュ制御回路400に転送される。第1マッチ信号MATCH1が第1ロジックレベルから第2ロジックレベルへ遷移されると、リフレッシュ制御回路400は転送されたマッチングされるロウアドレスをラッチし、処理する。

例えば、書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致しなくて第1マッチ信号MATCH1が第1ロジックレベルを有する場合、アドレス制御回路400はメモリセルロウを順次にリフレッシュする。例えば、書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスが一致して第1マッチ信号MATCH1が第2ロジックレベルを有する場合、リフレッシュ制御回路400はウィークセルロウのポーズタイム(pause time)が短縮するようにウィークセルロウのリフレッシュを制御する。

図6を参照すると、アドレス保存部225aは、一つ以上のウィークセルロウアドレスWEAK_ADDR_1を保存する第1保存領域227aを含む。

説明の便宜のために、一つのウィークセルロウアドレスWEAK_ADDR_1を表している。実施形態により、アドレス保存部225は電気的プログラマブル・フューズ・メモリ、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワンタイム・プログラマブル・メモリ、フラッシュメモリなどのような多様な種類の不揮発性メモリ装置で具現できる。

アドレス比較部300aはロウアドレスROW_ADDRとウィークセルロウアドレスWEAK_ADDR_1を比較して第1マッチ信号MATCH1を生成する。

第1比較器311aは、ロウアドレスROW_ADDRの第1ビットRA1とウィークセルロウアドレスWEAK_ADDR_1の第1ビットWA1とを比較し、第2比較器312aはリフレッシュロウアドレスROW_ADDRの第2ビットRA2とウィークセルロウアドレスWEAK_ADDR_1の第2ビットWA2とを比較し、第N比較器31NaはロウアドレスROW_ADDRの第NビットRANとウィークセルロウアドレスWEAK_ADDR_1の第NビットWANとを比較し、ANDゲート320aは第1〜第N比較器(311a、312a、31Na)の出力信号にAND演算を遂行して第1マッチ信号MATCH1を生成する。従って、第1マッチ信号MATCH1は書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスとが一致しない場合、第1ロジックレベルを有することができ、書き込みロウアドレスROW_ADDRとアドレス情報ADDR_INFOに含まれるウィークセルロウアドレスとが一致する場合、第2ロジックレベルを有することができる。

図7を参照すると、リフレッシュ制御回路400aは、リフレッシュカウンタ410a、アドレス比較部420a、リフレッシュロウアドレス出力部430a、及びタイマ440aを含んで構成させる。

リフレッシュカウンタ410aは、Nビットカウンタで構成され、Nビットの内部リフレッシュロウアドレスCNT_ADDRを生成する。

例えば、アドレス情報ADDR_INFOに含まれるウィークセルロウアドレスWEAK_ADDR_1とリフレッシュロウアドレスREF_ADDRとが一致しない場合、アドレス比較部420aは第1ロジックレベルの第2マッチ信号MATCH2を提供する。例えば、アドレス情報ADDR_INFOに含まれるウィークセルロウアドレスWEAK_ADDR_1とリフレッシュロウアドレスREF_ADDRとが一致する場合、アドレス比較部420aは第2ロジックレベルの第2マッチ信号MATCH2を提供する。

第1マッチ信号MATCH1の第1ロジックレベルから第2ロジックレベルへの遷移に応答してタイマ440aは動作を始める(即ち、もしタイマ440aがカウンタである場合にはカウントを始める)。所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信すると(これは、リフレッシュロウアドレスREF_ADDRとアドレス情報ADDR_INFOとして提供されるウィークセルロウアドレスWEAK_ADDR_1との間にマッチが発生したことを表す)、タイマ440aはその出力信号であるインサート信号INSERTを第1ロジックレベルに維持する。

所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信しないと、タイマ440aはインサート信号INSERTを第2ロジックレベルに出力する。

第4スイッチ439は、第1マッチ信号MATCH1が第1ロジックレベルを有する場合に接続され、第1マッチ信号MATCHが第2ロジックレベルを有する場合に切断される。即ち、第4スイッチ439はウィークセルロウアドレスWEAK_ADDR_1と書き込みロウアドレスROW_ADDRが一致しない場合、第1ロジックレベルの第1マッチ信号MATCHに応答して接続され、内部リフレッシュロウアドレスCNT_ADDRをリフレッシュロウアドレスREF_ADDRとしてアドレスマルチプレクサ240に提供する。

遅延素子437は、隣接したメモリセルロウのリフレッシュ間隔分の遅延時間を有し、内部リフレッシュロウアドレスCNT_ADDRを遅延させる。

第3スイッチ438は、インサート信号INSERTが第1ロジックレベルを有する場合、第2スイッチ436に接続され、インサート信号INSERTが第2ロジックレベルを有する場合、遅延素子437に接続される。

第1マッチ信号MATCH1が第1ロジックレベルということは、アドレスレジスタ220から受信したロウアドレスとアドレス保存部225に保存されたアドレスとの間にマッチがないということを表す。また、リフレッシュロウアドレス出力部430aは第1マッチ信号MATCH1がインサート信号INSERTによって第2ロジックレベルの場合、ウィークセルロウアドレスWEAK_ADDR_1と内部リフレッシュロウアドレスCNT_ADDRの内の一つを選択してリフレッシュロウアドレスREF_ADDRとしてアドレスマルチプレクサ240とに提供する。この場合、ウィークセルロウアドレスWEAK_ADDR_1に該当する第Kメモリセルロウのワードラインと内部リフレッシュロウアドレスREF_ADDRに該当する第(K+1)メモリセルロウのワードラインが、バンクロウデコーダによって順次に活性化して第Kメモリセルロウと第(K+1)メモリセルロウが順次にリフレッシュされる。

他の実施形態においては、内部リフレッシュロウアドレスCNT_ADDRとウィークセルロウアドレスWEAK_ADDR_1が全部それぞれ異なる信号経路を介してロウアドレスマルチプレクサ240に提供され、ロウアドレスマルチプレクサ240は、このロウアドレスを適切なバンクロウデコーダ(260a、260b、260c、260d)に転送することを制御して、同時に又は順次に各自のリフレッシュ動作を遂行するようにする。

また、リフレッシュロウアドレス出力部430aは、第1マッチ信号MATCH1が第2ロジックレベルであり、インサート信号INSERTが第2ロジックレベルの場合は、遅延された内部的に生成されたリフレッシュロウアドレスが遅延素子437を経由して遅延された後、リフレッシュロウアドレスREF_ADDRとして持続的にアドレスマルチプレクサ240に提供する。

図8を参照すると、リフレッシュ制御回路400bは、リフレッシュカウンタ410b、アドレス比較部420b、リフレッシュロウアドレス出力部430b、及びタイマ440bを含んで構成される。

リフレッシュカウンタ410bは、Nビットカウンタで構成されてNビットの内部リフレッシュロウアドレスCNT_ADDRを生成する。

例えば、アドレス情報ADDR_INFOに含まれるウィークセルロウアドレスWEAK_ADDR_1とリフレッシュロウアドレスREF_ADDRとが一致しない場合、アドレス比較部420bは第1ロジックレベルの第2マッチ信号MATCH2を提供する。例えば、アドレス情報ADDR_INFOに含まれるウィークセルロウアドレスWEAK_ADDR_1とリフレッシュロウアドレスREF_ADDRとが一致する場合、アドレス比較部420bは第2ロジックレベルの第2マッチ信号MATCH2を提供する。

第1マッチ信号MATCH1の第1ロジックレベルから第2ロジックレベルへの遷移に応答してタイマ440bは動作を始める(即ち、タイマ440aがカウンタの場合、カウントを始める)。所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信すると(これは、リフレッシュロウアドレスREF_ADDRとアドレス情報ADDR_INFOとして提供されるウィークセルロウアドレスWEAK_ADDR_1との間にマッチが発生したことを表す)、タイマ440bはその出力信号であるインサート信号INSERTを第1ロジックレベルに維持する。

所定の時間が満了する前に、もし、タイマ440aが第2ロジックレベルの第2マッチ信号MATCH2を受信しない場合、タイマ440aはインサート信号INSERTを第2ロジックレベルに出力する。

第2スイッチ447は、第1マッチ信号MATCH1が第1ロジックレベルを有する場合に接続され、第1マッチ信号MATCHが第2ロジックレベルを有する場合に切断される。即ち、第2スイッチ447はウィークセルロウアドレスWEAK_ADDR_1と書き込みロウアドレスROW_ADDRとが一致しない場合、第1ロジックレベルの第1マッチ信号MATCHに応答して接続され、内部リフレッシュロウアドレスCNT_ADDRをリフレッシュロウアドレスREF_ADDRとしてアドレスマルチプレクサ240に提供する。

遅延素子443は、tRC(active to active)ほどの遅延時間を有し、内部リフレッシュロウアドレスCNT_ADDRの出力を遅延させる(そして、以後には生成された内部リフレッシュロウアドレスCNT_ADDRを遅延させる)。

マルチプレクサ445は、インサート信号INSERTが第1ロジックレベルを有する場合に内部リフレッシュロウアドレスCNT_ADDRを選択し、インサート信号INSERTが第2ロジックレベルを有する場合に遅延素子443の出力を選択する。

また、リフレッシュロウアドレス出力部430bは、第1マッチ信号MATCH1がインサート信号INSERTによって第2ロジックレベルでる場合は、ウィークセルロウアドレスWEAK_ADDR_1と内部リフレッシュロウアドレスCNT_ADDRの内のいずれか一つを選択してリフレッシュロウアドレスREF_ADDRとしてアドレスマルチプレクサ240に提供する。

ここで、記載した信号MATCH1、MATCH2、INSERTと関連した第1ロジックレベル及び第2ロジックレベルと関連して、第1ロジックレベルは必ず互いに同一である必要もなく、第2ロジックレベルは必ず互いに同一である必要はない。

個別的な信号に対して記述された第1ロジックレベルと第2ロジックレベルとは、その信号のロジック状態の違い又は変化を意味するものである。

図9を参照すると、アドレス比較部420aは、複数の比較器(4211、4212、421N)、及び、アンドゲート422を含む。

第1比較器4211は、リフレッシュロウアドレスREF_ADDRの第1ビットRFA1とウィークセルロウアドレスWEAK_ADDR_1の第1ビットWA1とを比較し、第2比較器4212は、リフレッシュロウアドレスROW_ADDRの第2ビットRFA2とウィークセルロウアドレスWEAK_ADDR_1の第2ビットWA2とを比較し、第N比較器421NはロウアドレスROW_ADDRの第NビットRFANとウィークセルロウアドレスWEAK_ADDR_1の第NビットWANとを比較し、ANDゲート422は、第1〜第N比較器(4211、4212、421N)の出力信号にAND演算を遂行して、第2マッチ信号MATCH2を生成する。

図9に示してはしていないが、第1マッチ信号MATCH1は、アンドゲート422に別途の入力端子を介して入力することができ、又は、第1〜第N比較器(4211、4212、421N)の内のいずれか一つ以上をイネーブルさせるのに用いることができる。

図9では図7のアドレス比較部420aに対して説明したが、図8のアドレス比較部420bも図7のアドレス比較部420aと実質的に同じ構成を有することができる。

図10ではウィークセルロウアドレスWEAK_ADDRとリフレッシュロウアドレスREF_ADDRがそれぞれ異なる場合を説明する。

第KメモリセルロウWL_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK_ADDRに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込まれる。

ここでは、ウィークセルロウアドレスWEAK_ADDRとリフレッシュロウアドレスREF_ADDRとが異なるので所定の時間内で第Kリフレッシュロウアドレス以後のリフレッシュロウアドレスの内のいずれか一つである第(K+i)メモリセルロウ(WL_K+i)に対してリフレッシュが遂行される時、同時にウィークセルロウアドレスWEAK_ADDRに該当するウィークセルロウをリフレッシュREFする。

所定の時間は、書き込み命令WRを受信した後に発生するi番のリフレッシュ動作の数に該当する。次に、第(K+i)リフレッシュロウアドレスに連続する第(K+i+1)リフレッシュロウアドレスに対応する第(K+i+1)メモリセルロウ(WL_K+i+1)に対してリフレッシュが遂行される。

図11を参照すると、先ず、第Kリフレッシュロウアドレスによって第KメモリセルロウWL_Kに対してリフレッシュが遂行される。

第KメモリセルロウWL_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK_ADDRに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込まれる。

ここでは、ウィークセルロウアドレスWEAK_ADDRと書き込みコマンドWRが受信された以後から所定の時間の間、リフレッシュロウアドレスREF_ADDRの内のいずれか一つと互いに一致するので、リフレッシュカウンタによって生成されたリフレッシュアドレスCNT_ADDRのリフレッシュシークエンスは変更される必要がなく、ウィークセルロウに対する追加的なリフレッシュが必要ない。

第KメモリセルロウWL_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK_ADDRに該当するウィークセルロウにデータを書き込むための書き込み命令WRを受信してウィークセルロウにデータが書き込みされる。

ここでは、ウィークセルロウアドレスWEAK_ADDRと第KリフレッシュロウアドレスREF_ADDRが所定の時間の間、リフレッシュロウアドレスREF_ADDRの内のいずれか一つと互いに一致しないので、リフレッシュカウンタによって生成されたリフレッシュアドレスCNT_ADDRのリフレッシュシークエンスは、ウィークセルロウに対するリフレッシュ動作を含むように変更される。

ウィークセルロウアドレスに該当するリフレッシュ動作又は第(K+i)メモリセルロウに対するリフレッシュ動作からのリフレッシュインターバルに対応する時間が経過した後、第(K+i)メモリセルロウWL_(K+i)に対するオートリフレッシュ動作が再開される。

リフレッシュインターバルは、ロウサイクルタイムtRCより実質的により大きい。例えば、ロウサイクルタイムtRCより、5倍又は10倍又は100倍大きいこともできる。例えば、リフレッシュインターバルがこの時、3.9マイクロ秒と設定されると、ロウサイクルタイムtRCは、約60ナノ秒と設定され得る。

図13を参照すると、アドレス保存部225bは、ウィークセルロウアドレスWEAK_ADDR_1を保存する第1保存領域227b、及びバンク情報としてバンクアドレスBANK_ADDRを保存する第2保存領域229bを含む。

アドレス比較部300bは、ロウアドレスROW_ADDRとウィークセルロウアドレスWEAK_ADDR_1とを比較した結果に基づいて第1マッチ信号MATCH1をバンク(265a、365d)のうち、バンクアドレスBANK_ADDRに対応するバンクに提供する。

複数の比較器(311b、312b、31Nb)、及びアンドゲート320bは、書き込みロウアドレスROW_ADDRとウィークセルロウアドレスWEAK_ADDR_1とが一致する場合、第2ロジックレベルを有する第1マッチ信号MATCH1をデマルチプレクサ330bに提供する。

デマルチプレクサ330bは、バンクアドレスBANK_ADDRに応答して第1マッチ信号MATCH1を複数のバンクマッチ信号(MATCH1_A〜MATCH1_D)のうち、バンクアドレスBANK_ADDRに対応するバンクマッチ信号として出力する。これにより、複数のバンク(265a〜265d)のうち、バンクアドレスBANK_ADDRに対応するバンクに第1マッチ信号MATCH1が印加される。

図14のフローチャートは、図13のアドレス保存部225bとアドレス比較部300bが図5の揮発性メモリ装置に含まれる場合の揮発性メモリ装置200の動作方法に適用される。

ここで、アドレス情報ADDR_INFOは、少なくとも一つのウィークセルロウを含むウィークセルロウアドレスWEAK_ADDR_1とバンクアドレスBANK_ADDRを含む。

このようなアドレス情報ADDR_INFOは、揮発性メモリ装置200のパッケージングの前又は後にアドレス保存部225bに保存することができる。

次に、リフレッシュロウアドレスを生成する(ステップS420)。

このようなリフレッシュロウアドレス生成によってリフレッシュ動作が開始される。

メモリセルロウに対するリフレッシュが遂行されている途中(即ち、第Kリフレッシュロウアドレスに対応する第Kメモリセルロウをリフレッシュした後、第Kメモリセルロウをリフレッシュする前に第Kメモリセルロウに対する書き込み命令によって第Kメモリセルロウにデータを書き込む場合)、次に揮発性メモリ装置に含まれる複数のメモリセルロウの内のいずれか一つのメモリセルロウにデータを書き込むための書き込みロウアドレスとウィークセルロウアドレスとを比較する(ステップS440)。

上記比較の結果、書き込みロウアドレスとセルロウアドレスとが一致しない場合(ステップS440で「いいえ」)、全てのバンク(380a〜380d)で第Kリフレッシュロウアドレスに連続する第(K+1)リフレッシュロウアドレスに対応する第(K+1)メモリセルロウをリフレッシュする(S450)。

例えば、バンクアドレスBANK_ADDRに対応するバンクのウィークセルロウは、他のバンクで第(K+1)リフレッシュロウアドレスに対応する第(K+1)メモリセルロウがリフレッシュされるのと同時にリフレッシュされる(ステップS460)。

バンクアドレスBANK_ADDRに対応する第(K+1)メモリセルロウはウィークセルロウのリフレッシュに連続して直ちにリフレッシュされる。

バンクアドレスBANK_ADDRに対応する第(K+1)メモリセルロウは、ウィークセルロウのリフレッシュ動作の開始後、ロウサイクルタイムtRC後にリフレッシュ動作を始める。

図15を参照すると、揮発性メモリ装置500は、複数のアドレス保存部(511〜51M)、複数の比較部(521〜52M)及び、OR演算部530を含んで構成される。

実施形態により、複数のアドレス保存部(511〜51M)は、一つの保存装置で具現されるか、又は、複数の保存装置で具現されることができる。例えば、各保存装置は、電気的プログラマブル・フューズ・メモリ、レーザープログラマブル・フューズ・メモリ、アンチフューズ・メモリ、ワンタイム・プログラマブル・メモリ、フラッシュメモリなどのような多様な種類の不揮発性メモリ装置の内のいずれか一つであってもよい。

複数の比較部(521〜52M)は、上記比較の結果に基づいて複数のマッチ信号(MATCH11〜MACTH1M)をそれぞれ生成する。

OR演算部530は、複数の比較部(521〜52M)から受信した複数のマッチ信号(MATCH11〜MACTH1M)に、OR演算を遂行して第1マッチ信号MATCH1を生成する。

図16を参照すると、本発明の一実施形態に係るメモリシステムの制御方法は、メモリシステムのパワーアップシークエンスの間、アドレス情報を揮発性メモリ装置からメモリコントローラに転送する(S510)。

そこで、アドレス情報は、揮発性メモリ装置のアドレス保存部からメモリコントローラのアドレス比較部に転送する。メモリコントローラのアドレス比較部でアドレス情報に含まれるウィークセルロウアドレスと揮発性メモリ装置のメモリセルロウをアクセスするための書き込みロウアドレスを比較する(ステップS520)。

上記比較の結果として、書き込みロウアドレスとウィークセルロウアドレスと一致する場合(ステップS520で「はい」)、メモリコントローラに含まれるコマンドキュー(command queue)がアイドル状態であるか否かに基づいてウィークセルロウのリフレッシュを制御する(ステップS540)。例えば、メモリコントローラは、リフレッシュ動作のスケジュールを修正してコマンドキューのアイドルタイムの間にウィークセルロウに対するリフレッシュ動作が含まれるようにする。

図17を参照すると、書き込みロウアドレスとウィークセルロウアドレスとが一致する場合、メモリコントローラに含まれるコマンドキューがアイドル状態であるか否かに基づいてウィークセルロウのアドレスを制御するために、先ず、メモリコントローラのコマンドキューがアイドル状態か否かの第1判断をする(ステップS541)。

ここで、コマンドキューがアイドル状態というのは、メモリコントローラが揮発性メモリ装置に対しいずれの動作も遂行していないことを意味する。

活性化及びプリチャージ動作は、他のメモリ装置でのリフレッシュ動作と等価又は同一である。

メモリコントローラは、揮発性メモリ装置にウィークセルロウに対してリフレッシュを遂行しないというリフレッシュスキップ情報を転送する(ステップS543)。

もし、ステップS542において、ウィークセルロウがプリチャージされないと決定されると、図17には示していないが、本方法はステップS546に進行することができる。

次に、遂行されたコマンドにリフレッシュコマンドが含まれているか否かの第2判断をする(ステップS545)。

第2判断の結果として、遂行されたコマンドにリフレッシュコマンドが含まれていなくて、リフレッシュが遂行されない場合(ステップS545で「いいえ」)にはステップS541に戻る。

第2判断の結果として、遂行されたコマンドにリフレッシュコマンドが含まれていてリフレッシュが遂行される場合(ステップS545で「はい」)、メモリコントローラは揮発性メモリ装置のアドレス制御回路がウィークセルロウアドレスに対応するウィークセルロウに対してリフレッシュを遂行するように揮発性メモリ装置を制御する(ステップS546)。

図18を参照すると、メモリシステム600は、メモリコントローラ610、及び揮発性メモリ装置650を含んで構成される。

メモリコントローラ610は、揮発性メモリ装置650にコマンドCMD及びアドレスADDRを転送し、メモリコントローラ610と揮発性メモリ装置610はデータDQを交換する。

揮発性メモリ装置650は、アドレス保存部(ASU:address storing unit)660、第1アドレス比較部(ACU1)670、及びリフレッシュ制御回路(RCC:refresh control circuit)680を含んで構成される。

第1アドレス比較部670は、アドレス情報ADDR_INFOとメモリコントローラ610から提供される書き込みロウアドレスROW_ADDRとを比較し、その比較に基づいて第1マッチ信号MATCH1をリフレッシュ制御回路680に提供する。

メモリコントローラ610の第2アドレス比較部640は、アドレス情報ADDR_INFOと揮発性メモリ装置650のメモリセルロウにアクセスするための書き込みロウアドレスROW_ADDRとを比較し、その比較結果に基づいた第3マッチ信号MATCH3を制御ロジック620に転送する。

第3マッチ信号MATCH3が第1ロジックレベルを有する場合、制御ロジック620は、揮発性メモリ装置650のリフレッシュ制御回路680を制御して、リフレッシュ制御回路680において揮発性メモリ装置650によりリフレッシュ制御回路680内のアドレスカウンタによって、又は、リフレッシュ制御回路680内のテーブルを参照して内部的に生成されるリフレッシュロウアドレスによってメモリセルロウがリフレッシュされるようにする。

第3マッチ信号MATCH3が第2ロジックレベルを有する場合、制御ロジック620は、コマンドキュー630がアイドル状態であるか否かをモニタしてコマンドキューがアイドル状態であるか否かによりリフレッシュ制御回路680がウィークセルロウのリフレッシュを制御するようにする。

例えば、メモリコントローラの次のアイドル区間の間又はコマンドキュー630のコマンドの発行を邪魔しないでリフレッシュコマンドを提供することが可能である場合、制御ロジック620は、ウィークセルロウに対するリフレッシュコマンドを提供する。

他の実施形態においては、制御ロジック620はコマンドキューのコマンドの発行をインタラプトしてウィークセルロウに対するリフレッシュコマンドを提供することができる。例えば、ウィークセルロウに対する書き込み動作後の、所定の時間内でウィークセルロウに対するリフレッシュが遂行されるようにできる。

例えば、コマンドキュー630がアイドル状態ではない場合、制御ロジックはコマンドキュー630に保存されたコマンドに伴う動作が遂行されるように揮発性メモリ装置650を制御した後、遂行されたコマンドにリフレッシュコマンドが含まれていると、ウィークセルロウがリフレッシュできるようにリフレッシュ制御回路680を制御する。

他の実施形態においては、リフレッシュスケジュールに対する修正は、メモリコントローラ610のみによって遂行することができる。例えば、アドレス比較部670は揮発性メモリ装置650に含まれないようにもできる。

図19及び図20ではウィークセルロウアドレスと書き込みロウアドレスが一致する場合を説明する。

図19では図18のコマンドキュー630がアイドル状態の場合のメモリシステム600の動作を表す。

第KメモリセルロウWL_Kに対してリフレッシュが遂行された後、ウィークセルロウアドレスWEAK_ADDRに該当するウィークセルロウに書き込み動作をするための書き込み命令WRが受信される。この時、コマンドキュー630がアイドル状態にあるので、制御ロジック620は、ウィークセルロウに対するリフレッシュ動作を挿入するというリフレッシュ情報を転送する。

第(K+i+1)メモリセルロウ(WL_K+i+1)は、第(K+i)メモリセルロウ(WL_K+i)がリフレッシュされた後、直ちにリフレッシュされるか、又は、リフレッシュインターバル(ロウサイクルタイムtRCより少なくても5倍、10倍または、50倍大きいリフレッシュインターバル)ほど遅延してリフレッシュする。

図20を参照すると、第Kリフレッシュロウアドレスによって第KメモリセルロウWL_Kをリフレッシュする。

本動作は、ウィークセルロウと次にリフレッシュされるようスケジュールリングされたロウ(WL_k+i)が同時にリフレッシュされることを除いては図19と同一である。

図21を参照すると、本発明の他の実施形態に係るメモリシステムの制御方法では、メモリシステムのパワーアップシークエンスの間にアドレス情報を揮発性メモリ装置からメモリコントローラに転送する(ステップS610)。

ここで、アドレス情報は、揮発性メモリ装置のアドレス保存部からメモリコントローラのアドレス比較部に転送する。

メモリコントローラのアドレス比較部において、アドレス情報に含まれる一つ以上のウィークセルロウアドレスと揮発性メモリ装置のメモリセルロウをアクセスするための書き込みロウアドレスとを比較する(ステップS620)。

メモリコントローラのトランザクションプロセッサ(transaction processor)は、上記比較の結果により、ノーマルセルロウに対する第1書き込み回復時間に依存する第1タイムウインドウとノーマルセル以外のウィークセルロウに対する第2書き込み回復時間に依存する第2タイムウインドウを含む、それぞれ異なるタイムウインドウで揮発性メモリ装置を制御する(ステップS630、ステップS640)。

上記比較の結果として、書き込みロウアドレスとウィークセルロウアドレスと一致する場合(ステップS620で「はい」)、トランザクションプロセッサは、第2書き込み回復時間が第1書き込み回復時間よりさらに長いように揮発性メモリ装置を制御する(ステップS640)。

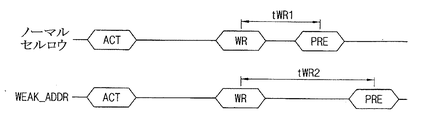

実施形態によっては、ウィークセルロウの第2書き込み回復時間は、ノーマルセルロウの第1書き込み回復時間の少なくとも2倍であってもよい。例えば、標準によりノーマルセルロウに対する書き込み回復時間tWRが15nsである場合、ウィークセルロウの書き込み回復時間は30nsであってもよい。

例えば、同期式DRAMにおいて、書き込み回復時間tWRは、書き込みコマンドとともにデータの最後の部分が入力された直後のデータラッチングクロックのエッジから同期式DRAMによって、プリチャージコマンドが正しく入力されるまでの時間(図24においてT9からTmまでの時間)に該当する。

書き込み回復時間が長くなるほどウィークセルロウに書き込み動作が正しく遂行される時間がさらに多く確保することができる(例えば、DRAMのキャパシタが正しく充電され得る。)

図22を参照すると、メモリシステム700は、メモリコントローラ710及び揮発性メモリ装置750を含む。

メモリコントローラ710は、アドレス比較部(ACU)720、マルチプレクサ730、及びトランザクションプロセッサ740を含む。

揮発性メモリ装置750は、アドレス情報、即ち、ウィークセルロウアドレスWEAK_ADDRを保存するアドレス保存部760を含む。ウィークセルロウアドレスWEAK_ADDRはメモリシステム700のパッケージングの前又は後でアドレス保存部760に保存することができる。

アドレス比較部720は、ウィークセルロウアドレスWEAK_ADDRと揮発性メモリ装置750のメモリセルロウをアクセスするための書き込みロウアドレスROW_ADDRを比較し、上記比較の結果に基づいて、マッチ信号MATCHをマルチプレクサ730に出力する。

マルチプレクサ730は第1ロジックレベルを有するマッチ信号MATCHに応答して第1書き込み回復時間tWR1と第2書き込み回復時間tWR2のうち、第1書き込み回復時間tWR1を選択してトランザクションプロセッサ740に出力する。

トランザクションプロセッサ740は、第1書き込み回復時間tWR1を受信し、揮発性メモリ装置750にコマンド又はトランザクションTRANSを提供して揮発性メモリ装置750のウィークセルロウ以外にノーマルセルロウが第1書き込み回復時間tWR1を利用して動作するように(即ち、第1書き込み回復時間tWR1を利用して書き込むように)揮発性メモリ装置750を制御する。

マルチプレクサ730は第2ロジックレベルを有するマッチ信号MATCHに応答して第1書き込み回復時間tWR1と第2書き込み回復時間tWR2のうち、第2書き込み回復時間tWR2を選択してトランザクションプロセッサ740に出力する。

トランザクションプロセッサ740は、第2書き込み回復時間tWR2を受信し、揮発性メモリ装置750にコマンド又はトランザクションTRANSを提供して揮発性メモリ装置750のウィークセルロウが第2書き込み回復時間tWR2を有するように揮発性メモリ装置750を制御する。

第2書き込み回復時間tWR2は、第1書き込み回復時間tWR1の2倍であってもよい。

本実施形態では、実際の書き込み回復時間はトランザクションプロセッサ740又は揮発性メモリ装置750に提供される必要はなく、それぞれ異なる書き込み回復時間に対応するモードインジケータ及び/又はコマンドを使用することができる。

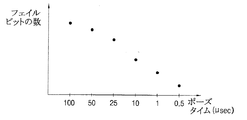

図23を参照すると、書き込み回復時間tWRが増加するほどフェイルビットの数が減少することがわかる。

図23において、符号781は、回復可能なフェイルビットの数を表す。

図24は、DDR3 SDRAMにおいて、クロック書き込みレイテンシ(clock write latency)CWLが「5」クロックであり、バースト(burst)の長さが「8」である場合を説明する。

図24において、最後のデータD7が書き込まれた後、プリチャージコマンドPREが入力される時までの時間T9〜Tmが書き込み回復時間tWRに該当する。

図24に示すように、他のデータに比べて最後のデータD7は受信された後、直ちにワードラインWLが非活性化されるので該当ロウがウィークセルロウの場合にデータD0〜D7は、セルに書き込みされることができる時間が充分でないこともある。従って、書き込み特性とデータ保存が良くなかったり、又は、エラーが発生することがある。

このように書き込み特性が良くなかったり、又は、データ保存能力が良くないセルをウィークセルといい、ウィークセルを少なくとも一つ以上含むメモリセルロウをウィークセルロウという。

図25を参照すると、ノーマルセルロウはアクティブコマンドACTが入力されてワードラインが活性化された後、書き込み命令WRが入力されて書き込み動作が遂行された後から第1書き込み回復時間tWR1後に、プリチャージコマンドPREが入力されてワードラインが非活性化され、ウィークセルロウはアクティブコマンドACTが入力されてワードラインが活性化された後に書き込み命令WRが入力されて、書き込み動作が遂行された後から第2書き込み回復時間tWR2の後にプリチャージコマンドPREが入力されて、ワードラインが非活性化されることによって、書き込み特性が良くないウィークセルを少なくとも一つ以上含むウィークセルロウの書き込み回復時間とノーマルセルロウの書き込み回復時間を別にすることが分かる。

他の実施形態においては、揮発性メモリ装置は受信されたコマンドがウィークセルロウに対して書き込み動作を遂行するというコマンドに該当することを認識し、ウィークセルロウに対する第2書き込み回復時間tWR2を増加させる。

揮発性メモリ装置は、受信されたコマンドが他の実施形態において記述された方式でウィークセルロウに書き込み動作を遂行するというコマンドであることを認識し得る。

図26を参照すると、メモリモジュール800は、複数の揮発性メモリ装置200を含む。

実施形態により、メモリモジュール800は、UDIMM(Unbuffered Dual In−line Memory Module)、RDIMM(Registered Dual In−line Memory Module)、FBDIMM(Fully Buffered Dual In−line Memory Module)、LRDIMM(Load Reduced Dual In−line Memory Module)、又は、他のメモリモジュールであってもよい。

また、バッファ810と揮発性メモリ装置200との間のコマンド/アドレス転送線は、マルチドロップ方式、デイジーチェーン方式、又は、フライ・バイ・デイジーチェーン方式で接続することができる。

バッファ810が、コマンド、アドレス、及びデータを全部バッファリングするので、メモリコントローラは、バッファ810のロードのみを駆動することによってメモリモジュール800とインターフェースすることができる。これにより、メモリモジュール800は、より多くの数のメモリ装置及びメモリランクを含むことができ、メモリシステムはより多くの数のメモリモジュールを含むことができる。

実施形態により、モバイルシステム900は、携帯電話(Mobile Phone)、スマートフォン(Smart Phone)、PDA(Personal Digital Assistant)、 PMP(Portable Multimedia Player)、デジタルカメラ(Digital Camera)、音楽再生機(Music Player)、携帯用ゲームコンソール(Portable Game Console)、ナビゲーション(Navigation)システムなどのような任意のモバイルシステムであることができる。

実施形態により、アプリケーションプロセッサ910は、一つのプロセッサコア(Single Core)を含むか或いは複数のプロセッサコア(Multi−Core)を含むことができる。例えば、アプリケーションプロセッサ910はデュアルコア(Dual−Core)、クアッドコア(Quad−Core)、ヘキサコア(Hexa−Core)などのマルチコア(Multi−Core)を含むことができる。また、実施形態により、アプリケーションプロセッサ910は、内部又は外部に位置したキャッシュメモリ(Cache Memory)をさらに含むことができる。

例えば、通信部920は、イーサネット(登録商標)(Ethernet(登録商標))通信、NFC(Near Field Communication)、RFID(Radio Frequency Identification)通信、移動通信(Mobile Telecommunication)、メモリカード通信、USB(Universal Serial Bus)通信などを遂行できる。例えば、通信部1420は、ベースバンドチップセット(Baseband Chipset)を含むことができ、GSM(登録商標)、GPRS、WCDMA(登録商標)、HSxPAなどの通信を支援することができる。

例えば、揮発性メモリ装置950は、DDR SDRAM、LPDDR SDRAM、GDDR SDRAM、RDRAMなどのような動的ランダムアクセスメモリ、又は、リフレッシュ動作が必要な任意の揮発性メモリ装置であってもよい。揮発性メモリ装置950はウィークセルロウアドレスをリフレッシュロウアドレスと比較して、その比較結果により、ウィークセルロウアドレスのリフレッシュを制御することによってウィークセルロウのポーズタイム増加による書き込み特性が悪くなることを防止できる。

パワーサプライ960は、モバイルシステム900の動作電圧を供給する。

また、実施形態により、モバイルシステム900は、CIS(Camera Image Processor)をさらに包含でき、メモリカード(Memory Card)、SSD(Solid State Drive)、HDD(Hard Disk Drive)、CD−ROMなどのような保存装置をさらに含むことができる。

図28を参照すると、コンピューティングシステム1100は、プロセッサ1110、入出力ハブ1120、入出力コントローラハブ1130、少なくとも一つのメモリモジュール1140、及びグラフィックカード1150を含む。

実施形態により、プロセッサ1110は一つのプロセッサコア(Single Core)を含むか、又は、複数のプロセッサコア(Multi−Core)を含むことができる。例えば、プロセッサ1510はデュアルコア(Dual−Core)、クアッドコア(Quad−Core)、ヘキサコア(Hexa−Core)などのマルチコア(Multi−Core)を含むことができる。

また、図28には一つのプロセッサ1110を含むコンピューティングシステム1100を示しているが、実施形態により、コンピューティングシステム1100は、複数のプロセッサを含むことができる。また、実施形態により、プロセッサ1110は、内部又は外部に位置したキャッシュメモリ(Cache Memory)をさらに含むことができる。

プロセッサ1110に含まれたメモリコントローラ1111は、IMC(Integrated Memory Controller)と呼ばれる。

メモリコントローラ1111は上述した一つ以上の実施形態の構造を含むか、又は、制御方法を遂行できる。メモリコントローラ1111とメモリモジュール1140との間のメモリインターフェースは、複数の信号線を含む一つのチャネルで具現されるか、又は、複数のチャネルで具現されることができる。また、各チャネルには一つ以上のメモリモジュール1140が接続されることができる。実施形態により、メモリコントローラ1111は、入出力ハブ1120内に位置することができる。メモリコントローラ1111を含む入出力ハブ1120は、MCH(Memory Controller Hub)と呼ばれる。

揮発性メモリ装置は、リフレッシュ動作の遂行途中でメモリコントローラから書き込みコマンドが入力される場合、リフレッシュロウアドレスとウィークセルロウアドレスとを比較し、比較結果により、ウィークセルロウアドレスのリフレッシュを制御することによってウィークセルロウのポーズタイム増加による書き込み特性が悪くなることを防止することができる。

代案的な、及び/または、追加的な実施形態において、メモリコントローラは、個別的なウィークセルロウベイシス(basis)よりは、メモリセルグループをウィークセルロウグループで処理することができる。例えば、メモリモジュールのうちいずれか一つのメモリチップのうちいずれか一つのバンクがウィークセルバンクとして考慮され、ウィークセルバンクは他のバンクよりさらに短いリフレッシュサイクル、及び/又は、さらに長い書き込み時間(書き込み回復時間)を有する。

入出力ハブ1120は、多様な方式のインターフェースを介してプロセッサ1110に接続され得る。例えば、入出力ハブ1120とプロセッサ1110は、FSB(Front Side Bus )、システムバス(System Bus)、ハイパートランスポート(HyperTransport)、LDT(Lightning Data Transport)、QPI(QuickPath Interconnect)、CSI(Common System Interface)などの多様な標準インターフェースで接続され得る。図28には一つの入出力ハブ1120を含むコンピューティングシステム1100を示したが、実施形態によって、コンピューティングシステム1100は複数の入出力ハブを含むことができる。

グラフィックカード1150は、画像を表示するためのディスプレイ装置(図示せず)を制御する。グラフィックカード1150は、イメージデータ処理のための内部プロセッサ及び内部半導体メモリ装置を含むことができる。実施形態により、入出力ハブ1120は、入出力ハブ1120の外部に位置したグラフィックカード1150とともに、又は、グラフィックカード1150の代わりに入出力ハブ1120の内部にグラフィック装置を含むことができる。

入出力ハブ1120に含まれたグラフィック装置は、集積グラフィック(Integrated Graphics)と呼ばれる。また、メモリコントローラ及びグラフィック装置を含む入出力ハブ1120は、GMCH(Graphics and Memory Controller Hub)と呼ばれる。

本発明の概念はまた、不揮発性メモリ装置にも適用できる。例えば、不揮発性メモリ装置において読み出しディスターバンスエラー(disturbance errors)は、メモリの特定ロウで頻繁に発生する可能性があり、このようなロウは、より速いコピーバックサイクルタイム(copy−back cycle times)を必要とする。

このようなより速いコピーバックサイクルタイムは、ここに記載した実施形態の、修正済みのリフレッシュサイクルタイムと類似方式で遂行されるか、或いは具現することができる。

また、不揮発性メモリ装置もさらに長い書き込み時間を必要とするメモリセルロウを含むことができ、ノーマルセルロウよりさらに長い書き込み回復時間の提供を受けることができるが、このような長い書き込み回復時間は、ここに記載した実施形態の、修正済みの書き込み回復時間と類似方式で遂行されるか、或いは具現することができる。

210 制御ロジック

220 アドレスレジスタ

225 アドレス保存部

230 バンク制御ロジック

240 ロウアドレスマルチプレクサ

250 カラムアドレスラッチ

260a、260b、260c、260d (第1〜第4)バンクロウデコーダ

270a、270b、270c、270d (第1〜第4)バンクカラムデコーダ

280a、280b、280c、280d (第1〜第4)バンクメモリアレイ

290 入出力ゲート回路

295 データ入出力バッファ

300 アドレス比較部

400 リフレッシュ制御回路

Claims (21)

- ウィークセルロウ(weak cell row)とノーマルセルロウ(normal cell row)とを含む複数の揮発性メモリセルのロウ(row)を備えるメモリセルアレイと、

コマンドを受信するコマンドデコーダと、

対応するウィークセルロウを識別する複数のウィークセルロウアドレスを保存するアドレステーブルと、

前記メモリセルアレイの動作を制御して前記複数の揮発性メモリセルのロウを周期的にリフレッシュするリフレッシュ制御回路とを有し、

前記リフレッシュ制御回路は、前記コマンドデコーダが、前記アドレステーブルに保存されたウィークセルロウアドレスによって第1ウィークセルロウが識別された時、前記第1ウィークセルロウに書き込むための書き込みコマンドを受信することに応答して前記第1ウィークセルロウのリフレッシュ動作を行うことを特徴とするメモリ装置。 - 前記リフレッシュ制御回路は、前記第1ウィークセルロウに書き込むための前記書き込みコマンドを受信した後、第1時間周期の間、リフレッシュ動作のシークエンスをモニタすることを特徴とする請求項1に記載のメモリ装置。

- 前記リフレッシュ制御回路は、前記第1時間周期の間、前記第1ウィークセルロウがリフレッシュされなかったと判断された場合、前記リフレッシュ動作のシークエンスにリフレッシュ動作を追加することを特徴とする請求項2に記載のメモリ装置。

- 前記リフレッシュ制御回路は、前記第1時間周期より長い第2時間周期でノーマルセルロウをリフレッシュすることを特徴とする請求項3に記載のメモリ装置。

- 前記リフレッシュ制御回路は、第2ロウのスケジュールされたリフレッシュ動作を前記第1ウィークセルロウのリフレッシュ動作に差し替えることを特徴とする請求項1に記載のメモリ装置。

- 前記リフレッシュ制御回路は、前記第1ウィークセルロウのリフレッシュ動作後、直ちに前記第2ロウのリフレッシュ動作を行うことを特徴とする請求項5に記載のメモリ装置。

- 前記リフレッシュ制御回路は、第2ロウのリフレッシュ動作と前記第1ウィークセルロウに対するリフレッシュ動作が同時に行われるようにすることを特徴とする請求項1に記載のメモリ装置。

- 前記リフレッシュ制御回路は、所定の時間内にリフレッシュスケジュールが前記第1ウィークセルロウのリフレッシュ動作を含むか否かを判断するために、前記リフレッシュスケジュールを分析することを特徴とする請求項1に記載のメモリ装置。

- メモリ装置であって、

ウィークセルロウ(weak cell row)とノーマルセルロウ(normal cell row)とを含む複数の揮発性メモリセルのロウ(row)を備えるメモリセルアレイと、

第1タイムウインドウでの第1書き込み動作を示す第1書き込みコマンドと、第2タイムウインドウでの第2書き込み動作を示す第2書き込みコマンドを受信し、前記第1書き込みコマンドと前記第2書き込みコマンドは、それぞれ異なるコマンドコードを含み、前記第1書き込みコマンドと前記第2書き込みコマンドは、前記メモリ装置に対し外部のソースから受信するコマンドデコーダと、

前記第1タイムウインドウでウィークセルロウに対する前記第1書き込み動作を遂行し、前記第1タイムウインドウより小さい前記第2タイムウインドウでノーマルセルロウに対する第2書き込み動作を遂行するロウデコーダとを有することを特徴とするメモリ装置。 - 前記コマンドデコーダは、前記第1及び第2書き込みコマンドのそれぞれを受信すると共に、書き込み動作が遂行されるロウを識別するそれぞれのアドレスと、前記識別されたロウに書き込む時に用いられる書き込みタイムを識別するそれぞれのコードとを受信することを特徴とする請求項9に記載のメモリ装置。

- 前記メモリセルアレイは、対応するウィークセルロウを識別する複数のウィークセルロウアドレスを保存するアドレステーブルをさらに含むことを特徴とする請求項9に記載のメモリ装置。

- 前記メモリ装置は、前記ウィークセルロウアドレスをメモリコントローラに転送することを特徴とする請求項11に記載のメモリ装置。

- メモリコントローラであって、

メモリ装置に転送されるリフレッシュコマンドと書き込みコマンドとを含む複数のコマンドを生成する制御回路と、

前記メモリ装置の複数のウィークセルロウアドレスを保存するテーブルと、

前記メモリ装置に転送される第1書き込みコマンドと関連した第1アドレスが前記複数のウィークセルロウアドレスの内のいずれか一つに該当するか否かを判断するアドレス比較部とを有し、

前記制御回路は、前記アドレス比較部の前記判断に応答して前記第1アドレスと関連したリフレッシュ動作を含むようにリフレッシュスケジュールを調整することを特徴とするメモリコントローラ。 - 前記メモリコントローラは、前記メモリ装置から前記複数のウィークセルロウアドレスを受信し、前記受信された複数のウィークセルロウアドレスを前記テーブルに保存することを特徴とする請求項13に記載のメモリコントローラ。

- 前記制御回路は、前記第1アドレスに該当する第1セルロウをリフレッシュする第1リフレッシュコマンドを生成し、

前記第1セルロウは、前記第1セルロウに対する書き込み動作後、第1時間周期内にリフレッシュされることを特徴とする請求項13に記載のメモリコントローラ。 - 前記制御回路は、第2時間周期内に第2セルロウをリフレッシュする少なくとも一つの第2リフレッシュコマンドを生成し、

前記第2時間周期は前記第1時間周期より大きいことを特徴とする請求項15に記載のメモリコントローラ。 - 前記制御回路は、前記アドレス比較部に応答して前記テーブルに保存されたウィークセルロウに対する第1書き込みコマンドと、前記テーブルで識別されなかったノーマルセルロウに対する第2書き込みコマンドとを生成することを特徴とする請求項13に記載のメモリコントローラ。

- 前記第1書き込みコマンドは、前記メモリ装置が第1時間周期の間、書き込み動作を遂行するようにさせ、前記第2書き込みコマンドは前記メモリ装置が前記第1時間周期より小さい第2時間周期の間、書き込み動作を遂行するようにさせることを特徴とする請求項17に記載のメモリコントローラ。

- 前記第1書き込みコマンドのコマンドコードは、前記第2書き込みコマンドのコマンドコードと異なることを特徴とする請求項18に記載のメモリコントローラ。

- 前記制御回路は、第1時間インジケータを有する前記第1書き込みコマンドと、第2時間インジケータを有する前記第2書き込みコマンドとを生成し、

前記メモリ装置は、前記第1及び第2時間インジケータに応答して前記第1及び第2時間周期の間、それぞれ書き込み動作を行うことを特徴とする請求項18に記載のメモリコントローラ。 - 請求項1に記載のメモリ装置と、

前記メモリ装置と通信して前記メモリ装置にコマンドを発行するメモリコントローラとを備えることを特徴とするメモリシステム。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2012-0042411 | 2012-04-24 | ||

| KR1020120042411A KR101966858B1 (ko) | 2012-04-24 | 2012-04-24 | 휘발성 메모리 장치의 동작 방법, 휘발성 메모리 장치 및 메모리 시스템의 제어 방법 |

| US13/720,998 | 2012-12-19 | ||

| US13/720,998 US9165637B2 (en) | 2012-04-24 | 2012-12-19 | Volatile memory device and a memory controller |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013229096A JP2013229096A (ja) | 2013-11-07 |

| JP2013229096A5 JP2013229096A5 (ja) | 2015-12-10 |

| JP5952771B2 true JP5952771B2 (ja) | 2016-07-13 |

Family

ID=49381238

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013091188A Active JP5952771B2 (ja) | 2012-04-24 | 2013-04-24 | メモリ装置及びメモリコントローラ並びにメモリシステム |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US9165637B2 (ja) |

| JP (1) | JP5952771B2 (ja) |

| KR (1) | KR101966858B1 (ja) |

| CN (1) | CN103377158B (ja) |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101977665B1 (ko) * | 2012-07-12 | 2019-08-28 | 삼성전자주식회사 | 리프레쉬 주기를 조절하는 반도체 메모리 장치, 메모리 시스템 및 그 동작방법 |

| KR102048407B1 (ko) * | 2012-10-19 | 2019-11-25 | 삼성전자주식회사 | 리프레쉬 어드레스 생성기 및 휘발성 메모리 장치 |

| KR102125230B1 (ko) * | 2013-03-13 | 2020-06-22 | 삼성전자주식회사 | 디램 및 리프레시 제어방법 |

| US9349433B2 (en) * | 2013-03-13 | 2016-05-24 | Inphi Corporation | Hidden refresh of weak memory storage cells in semiconductor memory |

| KR20140113191A (ko) * | 2013-03-15 | 2014-09-24 | 삼성전자주식회사 | 반도체 메모리 장치 및 이의 리프레쉬 방법 |

| CN105339917A (zh) * | 2013-05-30 | 2016-02-17 | 惠普发展公司,有限责任合伙企业 | 访问存储器中数据的分离的存储器控制器 |

| US9685217B2 (en) * | 2013-07-22 | 2017-06-20 | Taiwan Semiconductor Manufacturing Company Ltd. | Memory device with over-refresh and method thereof |

| JP2015076110A (ja) * | 2013-10-08 | 2015-04-20 | マイクロン テクノロジー, インク. | 半導体装置及びこれを備えるデータ処理システム |

| US10020045B2 (en) * | 2013-11-26 | 2018-07-10 | Micron Technology, Inc. | Partial access mode for dynamic random access memory |

| US9230634B2 (en) | 2013-12-09 | 2016-01-05 | Qualcomm Incorporated | Refresh scheme for memory cells with next bit table |

| KR102285994B1 (ko) * | 2014-05-13 | 2021-08-06 | 삼성전자주식회사 | 불휘발성 메모리 시스템 및 메모리 컨트롤러의 동작 방법 |

| CN105280215B (zh) * | 2014-06-09 | 2018-01-23 | 华为技术有限公司 | 动态随机存取存储器dram的刷新方法、设备以及系统 |

| WO2016014399A1 (en) * | 2014-07-21 | 2016-01-28 | Rensselaer Polytechnic Institute | Error tolerant memory system |

| JP6180450B2 (ja) * | 2015-02-02 | 2017-08-16 | キヤノン株式会社 | 制御装置、制御装置の制御方法及びプログラム |

| US9384820B1 (en) * | 2015-06-12 | 2016-07-05 | Apple Inc. | Aligning calibration segments for increased availability of memory subsystem |

| CN105632546A (zh) * | 2015-07-21 | 2016-06-01 | 上海磁宇信息科技有限公司 | 一种mram芯片及其自刷新操作方法 |

| KR102432701B1 (ko) * | 2015-11-18 | 2022-08-16 | 에스케이하이닉스 주식회사 | 리프레시 액티브 제어회로 및 이를 포함하는 메모리 장치 |

| KR102501651B1 (ko) * | 2016-03-02 | 2023-02-21 | 에스케이하이닉스 주식회사 | 리프레쉬 제어 장치 |

| KR20170118484A (ko) * | 2016-04-15 | 2017-10-25 | 에스케이하이닉스 주식회사 | 리프레쉬 제어 장치 |

| KR102439671B1 (ko) * | 2016-04-25 | 2022-09-02 | 에스케이하이닉스 주식회사 | 메모리 장치 |

| KR102517700B1 (ko) * | 2016-06-10 | 2023-04-05 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그의 동작 방법 |

| KR102558044B1 (ko) * | 2016-06-14 | 2023-07-20 | 에스케이하이닉스 주식회사 | 비교회로 및 반도체장치 |

| KR102553181B1 (ko) * | 2016-07-12 | 2023-07-10 | 에스케이하이닉스 주식회사 | 메모리 장치 및 메모리 장치의 동작 방법 |

| US10318187B2 (en) * | 2016-08-11 | 2019-06-11 | SK Hynix Inc. | Memory controller and memory system including the same |

| US10372566B2 (en) * | 2016-09-16 | 2019-08-06 | Micron Technology, Inc. | Storing memory array operational information in nonvolatile subarrays |

| KR20180114712A (ko) * | 2017-04-11 | 2018-10-19 | 에스케이하이닉스 주식회사 | 리프레쉬 컨트롤러 및 그를 포함하는 반도체 메모리 장치 |

| CN108959106B (zh) * | 2017-05-18 | 2020-12-18 | 华为技术有限公司 | 内存访问方法和装置 |

| US10109339B1 (en) | 2017-07-28 | 2018-10-23 | Micron Technology, Inc. | Memory devices with selective page-based refresh |

| KR20190047451A (ko) * | 2017-10-27 | 2019-05-08 | 에스케이하이닉스 주식회사 | 저항 변화 메모리 장치를 구비한 반도체 메모리 시스템 및 그 구동 방법 |

| KR20190054812A (ko) * | 2017-11-14 | 2019-05-22 | 삼성전자주식회사 | 메모리 장치의 구동 방법 및 이를 수행하는 메모리 장치 |

| KR102408867B1 (ko) * | 2017-12-20 | 2022-06-14 | 삼성전자주식회사 | 반도체 메모리 장치, 메모리 시스템 및 반도체 메모리 장치의 동작 방법 |

| US10503670B2 (en) * | 2017-12-21 | 2019-12-10 | Advanced Micro Devices, Inc. | Dynamic per-bank and all-bank refresh |

| US20190243720A1 (en) * | 2018-02-08 | 2019-08-08 | Micron Technology, Inc. | Backup operations from volatile to non-volatile memory |

| KR20190123990A (ko) * | 2018-04-25 | 2019-11-04 | 에스케이하이닉스 주식회사 | 메모리 컨트롤러 및 그 동작 방법 |

| KR102573270B1 (ko) * | 2018-10-08 | 2023-08-31 | 삼성전자주식회사 | 반도체 메모리 장치 및 이의 구동 방법 |

| US10483978B1 (en) | 2018-10-16 | 2019-11-19 | Micron Technology, Inc. | Memory device processing |

| US10824573B1 (en) | 2019-04-19 | 2020-11-03 | Micron Technology, Inc. | Refresh and access modes for memory |

| KR102406449B1 (ko) * | 2020-06-25 | 2022-06-08 | 에스케이하이닉스 주식회사 | 스토리지 장치 및 그 동작 방법 |

| KR20220028718A (ko) * | 2020-08-31 | 2022-03-08 | 에스케이하이닉스 주식회사 | 래치 회로 및 이를 포함하는 메모리 장치 |

| US11520661B1 (en) | 2021-07-12 | 2022-12-06 | Apple Inc. | Scheduling of data refresh in a memory based on decoding latencies |

| US20230359558A1 (en) * | 2022-05-09 | 2023-11-09 | Advanced Micro Devices, Inc. | Approach for skipping near-memory processing commands |

| CN117672290B (zh) * | 2024-02-01 | 2024-05-17 | 长鑫存储技术(西安)有限公司 | 存储器结构、刷新方法及存储器 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1139861A (ja) * | 1997-07-16 | 1999-02-12 | Toshiba Corp | ダイナミック型半導体記憶装置 |

| US5909404A (en) | 1998-03-27 | 1999-06-01 | Lsi Logic Corporation | Refresh sampling built-in self test and repair circuit |

| US6058069A (en) | 1999-04-12 | 2000-05-02 | Etron Technology, Inc. | Protection circuit to ensure DRAM signal in write cycle |

| US6556482B2 (en) | 1999-06-24 | 2003-04-29 | Nec Electronics Corporation | Semiconductor memory device |

| US6275437B1 (en) * | 2000-06-30 | 2001-08-14 | Samsung Electronics Co., Ltd. | Refresh-type memory with zero write recovery time and no maximum cycle time |

| US7095669B2 (en) * | 2003-11-07 | 2006-08-22 | Infineon Technologies Ag | Refresh for dynamic cells with weak retention |

| JP4322694B2 (ja) * | 2004-02-04 | 2009-09-02 | エルピーダメモリ株式会社 | 半導体記憶装置および半導体記憶装置のリフレッシュ方法 |

| US7099221B2 (en) | 2004-05-06 | 2006-08-29 | Micron Technology, Inc. | Memory controller method and system compensating for memory cell data losses |

| US7193920B2 (en) | 2004-11-15 | 2007-03-20 | Hynix Semiconductor Inc. | Semiconductor memory device |

| KR100689708B1 (ko) * | 2005-01-05 | 2007-03-08 | 삼성전자주식회사 | 반도체 장치 |

| JP2006344345A (ja) * | 2005-05-12 | 2006-12-21 | Nec Electronics Corp | 揮発性半導体記憶装置 |

| US7283395B2 (en) * | 2005-06-24 | 2007-10-16 | Infineon Technologies Flash Gmbh & Co. Kg | Memory device and method for operating the memory device |

| US7734866B2 (en) * | 2005-08-04 | 2010-06-08 | Rambus Inc. | Memory with address-differentiated refresh rate to accommodate low-retention storage rows |

| US8086461B2 (en) | 2007-06-13 | 2011-12-27 | At&T Intellectual Property Ii, L.P. | System and method for tracking persons of interest via voiceprint |

| US8949520B2 (en) * | 2009-01-22 | 2015-02-03 | Rambus Inc. | Maintenance operations in a DRAM |

| US7990795B2 (en) * | 2009-02-19 | 2011-08-02 | Freescale Semiconductor, Inc. | Dynamic random access memory (DRAM) refresh |

| US7872929B2 (en) * | 2009-04-28 | 2011-01-18 | Lsi Corporation | Accessing memory cells in a memory circuit |

| KR101879442B1 (ko) * | 2011-05-25 | 2018-07-18 | 삼성전자주식회사 | 휘발성 메모리 장치의 리프레쉬 방법, 리프레쉬 어드레스 생성기 및 휘발성 메모리 장치 |

| KR101893895B1 (ko) * | 2011-12-16 | 2018-09-03 | 삼성전자주식회사 | 메모리 시스템 및 그 동작 제어 방법 |

| KR20130117198A (ko) * | 2012-04-18 | 2013-10-25 | 삼성전자주식회사 | 메모리 셀의 리프레쉬 방법 및 이를 이용한 반도체 메모리 장치 |

| KR102050473B1 (ko) * | 2012-09-24 | 2019-11-29 | 삼성전자주식회사 | 리프레쉬 주기를 조절하는 반도체 메모리 장치 및 메모리 시스템 |

| KR20140076735A (ko) * | 2012-12-13 | 2014-06-23 | 삼성전자주식회사 | 휘발성 메모리 장치 및 메모리 시스템 |

-

2012

- 2012-04-24 KR KR1020120042411A patent/KR101966858B1/ko active IP Right Grant

- 2012-12-19 US US13/720,998 patent/US9165637B2/en active Active

-

2013

- 2013-04-19 CN CN201310136956.XA patent/CN103377158B/zh active Active

- 2013-04-24 JP JP2013091188A patent/JP5952771B2/ja active Active

-

2015

- 2015-09-18 US US14/858,140 patent/US9653141B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR101966858B1 (ko) | 2019-04-08 |

| KR20130119544A (ko) | 2013-11-01 |

| US20130282973A1 (en) | 2013-10-24 |

| CN103377158A (zh) | 2013-10-30 |

| JP2013229096A (ja) | 2013-11-07 |

| US9653141B2 (en) | 2017-05-16 |

| CN103377158B (zh) | 2018-04-20 |

| US9165637B2 (en) | 2015-10-20 |

| US20160012880A1 (en) | 2016-01-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5952771B2 (ja) | メモリ装置及びメモリコントローラ並びにメモリシステム | |

| US9685218B2 (en) | Memory device and memory system having the same | |

| US9418723B2 (en) | Techniques to reduce memory cell refreshes for a memory device | |

| US9767050B2 (en) | Memory systems that adjust an auto-refresh operation responsive to a self-refresh operation history | |

| US9336851B2 (en) | Memory device and method of refreshing in a memory device | |

| US9293188B2 (en) | Memory and memory controller for high reliability operation and method | |

| US9767882B2 (en) | Method of refreshing memory device | |

| US9361967B2 (en) | Semiconductor memory device | |

| US9147461B1 (en) | Semiconductor memory device performing a refresh operation, and memory system including the same | |

| US9042194B2 (en) | Refresh method, refresh address generator, volatile memory device including the same | |

| KR20170057704A (ko) | 액세스 동작과 리프레쉬 동작의 충돌을 제어하는 메모리 장치 및 이를 포함하는 메모리 시스템 | |

| KR20140076735A (ko) | 휘발성 메모리 장치 및 메모리 시스템 | |

| KR20160056056A (ko) | 반도체 메모리 장치 및 이를 포함하는 메모리 시스템 | |

| KR20160094767A (ko) | 아이들 구간에서 정보 전달 기능을 수행하는 메모리 장치 및 방법 | |

| US20140237177A1 (en) | Memory module and memory system having the same | |

| US9449673B2 (en) | Memory device and memory system having the same | |

| KR20150100184A (ko) | 메모리 모듈 및 이를 포함하는 메모리 시스템 | |

| CN114115715A (zh) | 执行存储器的低时延存取的设备和方法 | |

| KR102048217B1 (ko) | 메모리 장치 및 이를 갖는 메모리 시스템 | |

| KR20180060091A (ko) | 메모리 장치의 구동 방법 및 메모리 시스템의 구동 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150911 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150911 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20150911 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20151001 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151021 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20151021 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20151027 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160210 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160517 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160610 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5952771 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |