JP5695813B2 - 表示装置、表示モジュール、及び電子機器 - Google Patents

表示装置、表示モジュール、及び電子機器 Download PDFInfo

- Publication number

- JP5695813B2 JP5695813B2 JP2006216902A JP2006216902A JP5695813B2 JP 5695813 B2 JP5695813 B2 JP 5695813B2 JP 2006216902 A JP2006216902 A JP 2006216902A JP 2006216902 A JP2006216902 A JP 2006216902A JP 5695813 B2 JP5695813 B2 JP 5695813B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- switch

- current

- terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000011368 organic material Substances 0.000 claims description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 6

- 239000002041 carbon nanotube Substances 0.000 claims description 6

- 229910021393 carbon nanotube Inorganic materials 0.000 claims description 6

- 229910010272 inorganic material Inorganic materials 0.000 claims description 6

- 239000011147 inorganic material Substances 0.000 claims description 4

- 239000010408 film Substances 0.000 description 206

- 239000010410 layer Substances 0.000 description 182

- 239000003990 capacitor Substances 0.000 description 165

- 239000000758 substrate Substances 0.000 description 165

- 239000004065 semiconductor Substances 0.000 description 141

- 108091006146 Channels Proteins 0.000 description 93

- 239000000463 material Substances 0.000 description 90

- 238000010586 diagram Methods 0.000 description 67

- 230000006870 function Effects 0.000 description 57

- 239000012212 insulator Substances 0.000 description 57

- 239000011229 interlayer Substances 0.000 description 34

- 239000002585 base Substances 0.000 description 31

- 239000011521 glass Substances 0.000 description 30

- 239000012535 impurity Substances 0.000 description 30

- 150000002894 organic compounds Chemical class 0.000 description 28

- 230000002093 peripheral effect Effects 0.000 description 27

- 238000012545 processing Methods 0.000 description 24

- 229910021417 amorphous silicon Inorganic materials 0.000 description 23

- 229910052751 metal Inorganic materials 0.000 description 23

- 239000002184 metal Substances 0.000 description 23

- 230000015572 biosynthetic process Effects 0.000 description 22

- 238000000034 method Methods 0.000 description 22

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 22

- 238000004519 manufacturing process Methods 0.000 description 20

- 230000008859 change Effects 0.000 description 19

- 238000002347 injection Methods 0.000 description 19

- 239000007924 injection Substances 0.000 description 19

- 238000007789 sealing Methods 0.000 description 19

- 229910052782 aluminium Inorganic materials 0.000 description 16

- 239000010409 thin film Substances 0.000 description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 230000009467 reduction Effects 0.000 description 13

- 229910052710 silicon Inorganic materials 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- 229910052814 silicon oxide Inorganic materials 0.000 description 13

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 12

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 12

- 230000007547 defect Effects 0.000 description 12

- 239000011575 calcium Substances 0.000 description 11

- 230000005525 hole transport Effects 0.000 description 11

- 239000011159 matrix material Substances 0.000 description 11

- 230000003071 parasitic effect Effects 0.000 description 11

- 230000005540 biological transmission Effects 0.000 description 10

- 150000001875 compounds Chemical class 0.000 description 10

- 239000004973 liquid crystal related substance Substances 0.000 description 9

- 239000004033 plastic Substances 0.000 description 9

- 229920003023 plastic Polymers 0.000 description 9

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 9

- 239000010453 quartz Substances 0.000 description 9

- 239000003566 sealing material Substances 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 8

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 8

- 229910045601 alloy Inorganic materials 0.000 description 7

- 239000000956 alloy Substances 0.000 description 7

- 239000000919 ceramic Substances 0.000 description 7

- 229910052744 lithium Inorganic materials 0.000 description 7

- 239000000565 sealant Substances 0.000 description 7

- 230000005236 sound signal Effects 0.000 description 7

- 229910017073 AlLi Inorganic materials 0.000 description 6

- 229910017911 MgIn Inorganic materials 0.000 description 6

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 239000010949 copper Substances 0.000 description 6

- 239000012788 optical film Substances 0.000 description 6

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 6

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 5

- 229910004261 CaF 2 Inorganic materials 0.000 description 5

- 239000004642 Polyimide Substances 0.000 description 5

- 229910004298 SiO 2 Inorganic materials 0.000 description 5

- 229910052791 calcium Inorganic materials 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 5

- 229920001721 polyimide Polymers 0.000 description 5

- 239000011347 resin Substances 0.000 description 5

- 229920005989 resin Polymers 0.000 description 5

- 230000002441 reversible effect Effects 0.000 description 5

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 5

- 229910052709 silver Inorganic materials 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- 239000004925 Acrylic resin Substances 0.000 description 4

- 229920000178 Acrylic resin Polymers 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 238000002425 crystallisation Methods 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- -1 porphyrin compounds Chemical class 0.000 description 4

- 238000005070 sampling Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 239000011701 zinc Substances 0.000 description 4

- UOCMXZLNHQBBOS-UHFFFAOYSA-N 2-(1,3-benzoxazol-2-yl)phenol zinc Chemical compound [Zn].Oc1ccccc1-c1nc2ccccc2o1.Oc1ccccc1-c1nc2ccccc2o1 UOCMXZLNHQBBOS-UHFFFAOYSA-N 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- UHOVQNZJYSORNB-UHFFFAOYSA-N Benzene Chemical group C1=CC=CC=C1 UHOVQNZJYSORNB-UHFFFAOYSA-N 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000000872 buffer Substances 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 150000004696 coordination complex Chemical class 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- IYZMXHQDXZKNCY-UHFFFAOYSA-N 1-n,1-n-diphenyl-4-n,4-n-bis[4-(n-phenylanilino)phenyl]benzene-1,4-diamine Chemical compound C1=CC=CC=C1N(C=1C=CC(=CC=1)N(C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 IYZMXHQDXZKNCY-UHFFFAOYSA-N 0.000 description 2

- DHDHJYNTEFLIHY-UHFFFAOYSA-N 4,7-diphenyl-1,10-phenanthroline Chemical compound C1=CC=CC=C1C1=CC=NC2=C1C=CC1=C(C=3C=CC=CC=3)C=CN=C21 DHDHJYNTEFLIHY-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 2

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 239000007983 Tris buffer Substances 0.000 description 2

- 150000001408 amides Chemical class 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- UFVXQDWNSAGPHN-UHFFFAOYSA-K bis[(2-methylquinolin-8-yl)oxy]-(4-phenylphenoxy)alumane Chemical compound [Al+3].C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC=C([O-])C2=NC(C)=CC=C21.C1=CC([O-])=CC=C1C1=CC=CC=C1 UFVXQDWNSAGPHN-UHFFFAOYSA-K 0.000 description 2

- XJHCXCQVJFPJIK-UHFFFAOYSA-M caesium fluoride Chemical compound [F-].[Cs+] XJHCXCQVJFPJIK-UHFFFAOYSA-M 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 239000007850 fluorescent dye Substances 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 150000002484 inorganic compounds Chemical class 0.000 description 2

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 2

- IBHBKWKFFTZAHE-UHFFFAOYSA-N n-[4-[4-(n-naphthalen-1-ylanilino)phenyl]phenyl]-n-phenylnaphthalen-1-amine Chemical group C1=CC=CC=C1N(C=1C2=CC=CC=C2C=CC=1)C1=CC=C(C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C3=CC=CC=C3C=CC=2)C=C1 IBHBKWKFFTZAHE-UHFFFAOYSA-N 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 230000001052 transient effect Effects 0.000 description 2

- POILWHVDKZOXJZ-ARJAWSKDSA-M (z)-4-oxopent-2-en-2-olate Chemical compound C\C([O-])=C\C(C)=O POILWHVDKZOXJZ-ARJAWSKDSA-M 0.000 description 1

- UHXOHPVVEHBKKT-UHFFFAOYSA-N 1-(2,2-diphenylethenyl)-4-[4-(2,2-diphenylethenyl)phenyl]benzene Chemical group C=1C=C(C=2C=CC(C=C(C=3C=CC=CC=3)C=3C=CC=CC=3)=CC=2)C=CC=1C=C(C=1C=CC=CC=1)C1=CC=CC=C1 UHXOHPVVEHBKKT-UHFFFAOYSA-N 0.000 description 1

- VFMUXPQZKOKPOF-UHFFFAOYSA-N 2,3,7,8,12,13,17,18-octaethyl-21,23-dihydroporphyrin platinum Chemical compound [Pt].CCc1c(CC)c2cc3[nH]c(cc4nc(cc5[nH]c(cc1n2)c(CC)c5CC)c(CC)c4CC)c(CC)c3CC VFMUXPQZKOKPOF-UHFFFAOYSA-N 0.000 description 1

- SNTWKPAKVQFCCF-UHFFFAOYSA-N 2,3-dihydro-1h-triazole Chemical compound N1NC=CN1 SNTWKPAKVQFCCF-UHFFFAOYSA-N 0.000 description 1

- FQJQNLKWTRGIEB-UHFFFAOYSA-N 2-(4-tert-butylphenyl)-5-[3-[5-(4-tert-butylphenyl)-1,3,4-oxadiazol-2-yl]phenyl]-1,3,4-oxadiazole Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=C(C=CC=2)C=2OC(=NN=2)C=2C=CC(=CC=2)C(C)(C)C)O1 FQJQNLKWTRGIEB-UHFFFAOYSA-N 0.000 description 1

- YLYPIBBGWLKELC-RMKNXTFCSA-N 2-[2-[(e)-2-[4-(dimethylamino)phenyl]ethenyl]-6-methylpyran-4-ylidene]propanedinitrile Chemical compound C1=CC(N(C)C)=CC=C1\C=C\C1=CC(=C(C#N)C#N)C=C(C)O1 YLYPIBBGWLKELC-RMKNXTFCSA-N 0.000 description 1

- OGGKVJMNFFSDEV-UHFFFAOYSA-N 3-methyl-n-[4-[4-(n-(3-methylphenyl)anilino)phenyl]phenyl]-n-phenylaniline Chemical group CC1=CC=CC(N(C=2C=CC=CC=2)C=2C=CC(=CC=2)C=2C=CC(=CC=2)N(C=2C=CC=CC=2)C=2C=C(C)C=CC=2)=C1 OGGKVJMNFFSDEV-UHFFFAOYSA-N 0.000 description 1

- 125000004860 4-ethylphenyl group Chemical group [H]C1=C([H])C(=C([H])C([H])=C1*)C([H])([H])C([H])([H])[H] 0.000 description 1

- 229920002799 BoPET Polymers 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- 229920000298 Cellophane Polymers 0.000 description 1

- 241000284156 Clerodendrum quadriloculare Species 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 239000005041 Mylar™ Substances 0.000 description 1

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 1

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 1

- ZCQWOFVYLHDMMC-UHFFFAOYSA-N Oxazole Chemical compound C1=COC=N1 ZCQWOFVYLHDMMC-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- FZWLAAWBMGSTSO-UHFFFAOYSA-N Thiazole Chemical compound C1=CSC=N1 FZWLAAWBMGSTSO-UHFFFAOYSA-N 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- CUJRVFIICFDLGR-UHFFFAOYSA-N acetylacetonate Chemical compound CC(=O)[CH-]C(C)=O CUJRVFIICFDLGR-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 229910000272 alkali metal oxide Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 150000004982 aromatic amines Chemical class 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- WZJYKHNJTSNBHV-UHFFFAOYSA-N benzo[h]quinoline Chemical group C1=CN=C2C3=CC=CC=C3C=CC2=C1 WZJYKHNJTSNBHV-UHFFFAOYSA-N 0.000 description 1

- GQVWHWAWLPCBHB-UHFFFAOYSA-L beryllium;benzo[h]quinolin-10-olate Chemical compound [Be+2].C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21.C1=CC=NC2=C3C([O-])=CC=CC3=CC=C21 GQVWHWAWLPCBHB-UHFFFAOYSA-L 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- XZCJVWCMJYNSQO-UHFFFAOYSA-N butyl pbd Chemical compound C1=CC(C(C)(C)C)=CC=C1C1=NN=C(C=2C=CC(=CC=2)C=2C=CC=CC=2)O1 XZCJVWCMJYNSQO-UHFFFAOYSA-N 0.000 description 1

- WUKWITHWXAAZEY-UHFFFAOYSA-L calcium difluoride Chemical compound [F-].[F-].[Ca+2] WUKWITHWXAAZEY-UHFFFAOYSA-L 0.000 description 1

- 229910001634 calcium fluoride Inorganic materials 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- XCJYREBRNVKWGJ-UHFFFAOYSA-N copper(II) phthalocyanine Chemical compound [Cu+2].C12=CC=CC=C2C(N=C2[N-]C(C3=CC=CC=C32)=N2)=NC1=NC([C]1C=CC=CC1=1)=NC=1N=C1[C]3C=CC=CC3=C2[N-]1 XCJYREBRNVKWGJ-UHFFFAOYSA-N 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 230000005281 excited state Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- RBTKNAXYKSUFRK-UHFFFAOYSA-N heliogen blue Chemical compound [Cu].[N-]1C2=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=NC([N-]1)=C(C=CC=C3)C3=C1N=C([N-]1)C3=CC=CC=C3C1=N2 RBTKNAXYKSUFRK-UHFFFAOYSA-N 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- UEEXRMUCXBPYOV-UHFFFAOYSA-N iridium;2-phenylpyridine Chemical compound [Ir].C1=CC=CC=C1C1=CC=CC=N1.C1=CC=CC=C1C1=CC=CC=N1.C1=CC=CC=C1C1=CC=CC=N1 UEEXRMUCXBPYOV-UHFFFAOYSA-N 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 239000002346 layers by function Substances 0.000 description 1

- 239000003446 ligand Substances 0.000 description 1

- FUJCRWPEOMXPAD-UHFFFAOYSA-N lithium oxide Chemical compound [Li+].[Li+].[O-2] FUJCRWPEOMXPAD-UHFFFAOYSA-N 0.000 description 1

- 229910001947 lithium oxide Inorganic materials 0.000 description 1

- 125000000040 m-tolyl group Chemical group [H]C1=C([H])C(*)=C([H])C(=C1[H])C([H])([H])[H] 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- DCZNSJVFOQPSRV-UHFFFAOYSA-N n,n-diphenyl-4-[4-(n-phenylanilino)phenyl]aniline Chemical group C1=CC=CC=C1N(C=1C=CC(=CC=1)C=1C=CC(=CC=1)N(C=1C=CC=CC=1)C=1C=CC=CC=1)C1=CC=CC=C1 DCZNSJVFOQPSRV-UHFFFAOYSA-N 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 150000004866 oxadiazoles Chemical class 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 150000005041 phenanthrolines Chemical class 0.000 description 1

- IEQIEDJGQAUEQZ-UHFFFAOYSA-N phthalocyanine Chemical compound N1C(N=C2C3=CC=CC=C3C(N=C3C4=CC=CC=C4C(=N4)N3)=N2)=C(C=CC=C2)C2=C1N=C1C2=CC=CC=C2C4=N1 IEQIEDJGQAUEQZ-UHFFFAOYSA-N 0.000 description 1

- 229920000172 poly(styrenesulfonic acid) Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229940005642 polystyrene sulfonic acid Drugs 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 125000002943 quinolinyl group Chemical group N1=C(C=CC2=CC=CC=C12)* 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 150000003377 silicon compounds Chemical class 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000005549 size reduction Methods 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000004575 stone Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- GWDUZCIBPDVBJM-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzothiazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)SC2=CC=CC=C2N1 GWDUZCIBPDVBJM-UHFFFAOYSA-L 0.000 description 1

- QEPMORHSGFRDLW-UHFFFAOYSA-L zinc;2-(2-hydroxyphenyl)-3h-1,3-benzoxazole-2-carboxylate Chemical compound [Zn+2].OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1.OC1=CC=CC=C1C1(C([O-])=O)OC2=CC=CC=C2N1 QEPMORHSGFRDLW-UHFFFAOYSA-L 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

- G09G3/325—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror the data current flowing through the driving transistor during a setting phase, e.g. by using a switch for connecting the driving transistor to the data driver

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

- G09G2300/0866—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes by means of changes in the pixel supply voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0248—Precharge or discharge of column electrodes before or after applying exact column voltages

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0223—Compensation for problems related to R-C delay and attenuation in electrodes of matrix panels, e.g. in gate electrodes or on-substrate video signal electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0252—Improving the response speed

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/302—Details of OLEDs of OLED structures

- H10K2102/3023—Direction of light emission

- H10K2102/3026—Top emission

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/805—Electrodes

- H10K50/82—Cathodes

- H10K50/824—Cathodes combined with auxiliary electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/805—Electrodes

- H10K59/8052—Cathodes

- H10K59/80522—Cathodes combined with auxiliary electrodes

Description

T.Shirasaki et al,SID’04 Digest P1516〜1519 (2004)

また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

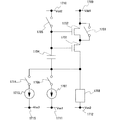

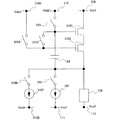

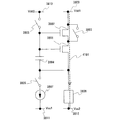

本発明は、EL素子を有する画素だけでなく、電流源を有する様々なアナログ回路に適用することが出来る。そこでまず、本実施の形態では、本発明の基本原理について述べる。

本実施の形態においては実施の形態1で述べた図1のアナログ回路とは別の構成について述べる。

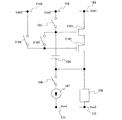

本実施の形態においては上記実施の形態で述べたアナログ回路とは別の構成について述べる。

本実施の形態においては上記実施の形態で述べたアナログ回路とは別の構成について述べる。

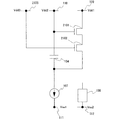

本実施の形態においては上記実施の形態で述べたアナログ回路とは別の構成について述べる。

本実施の形態においては上記実施の形態で述べたアナログ回路とは別の構成について述べる。

102 切り替えトランジスタ

103 スイッチ

104 容量素子

105 スイッチ

106 スイッチ

107 電流源

108 負荷

109 配線

110 配線

111 配線

112 配線

201 破線矢印

202 スイッチングトランジスタ

301 破線矢印

604 容量素子

701 スイッチ

702 配線

801 破線矢印

901 破線矢印

1101 切り替えトランジスタ

1102 スイッチ

1201 電流源トランジスタ

1202 切り替えトランジスタ

1203 スイッチ

1204 容量素子

1205 スイッチ

1207 電流源

1208 負荷

1209 配線

1210 配線

1211 配線

1212 配線

1301 破線矢印

1401 破線矢印

1404 容量素子

1601 切り替えトランジスタ

1602 スイッチ

1701 電流源トランジスタ

1702 切り替えトランジスタ

1703 スイッチ

1704 容量素子

1705 スイッチ

1706 スイッチ

1707 電流源

1708 負荷

1709 配線

1710 配線

1711 配線

1712 配線

1713 電流源

1714 スイッチ

1715 配線

1801 破線矢印

1901 破線矢印

2001 破線矢印

2101 電流源トランジスタ

2102 切り替えトランジスタ

2103 スイッチ

2104 スイッチ

2105 配線

2201 破線矢印

2301 破線矢印

2701 電流源トランジスタ

2702 切り替えトランジスタ

2807 電流源

2809 配線

2810 配線

2811 配線

2812 配線

2815 配線

2901 破線矢印

3001 破線矢印

3101 電流源トランジスタ

3102 切り替えトランジスタ

3103 スイッチ

3104 スイッチ

3105 配線

3106 スイッチ

3107 電流源

3108 配線

3201 破線矢印

3301 破線矢印

3401 破線矢印

3507 信号分割回路

3801 電流源トランジスタ

3802 切り替えトランジスタ

3803 スイッチ

3804 容量素子

3805 スイッチ

3806 スイッチ

3807 電流源

3808 負荷

3809 配線

3810 配線

3901 破線矢印

4001 破線矢印

4101 破線矢印

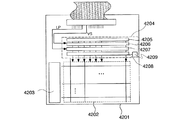

4201 表示装置

4202 画素領域

4203 ゲート線駆動回路

4204 信号線駆動回路

4205 シフトレジスタ

4206 第1ラッチ回路

4207 第2ラッチ回路

4208 デジタル・アナログ変換回路

4209 リファレンス用電流源回路

4301 リファレンス用電流源回路

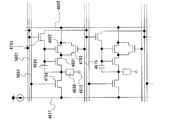

4400 電流源回路

4401 電流源トランジスタ

4402 切り替えトランジスタ

4403 スイッチ用トランジスタ

4404 容量素子

4405 スイッチ用トランジスタ

4406 スイッチ用トランジスタ

4407 電流源

4408 負荷

4409 配線

4410 配線

4411 配線

4413 配線

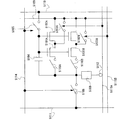

4601 電流源トランジスタ

4602 切り替えトランジスタ

4603 スイッチ

4604 容量素子

4605 スイッチ

4606 スイッチ

4608 表示素子

4609 配線

4610 配線

4611 配線

4612 対向電極

4614 配線

4615 配線

4703 スイッチングトランジスタ

4705 スイッチングトランジスタ

4706 スイッチングトランジスタ

4714 配線

4801 電流源

4812 配線

4901 信号線駆動回路

4902 走査線駆動回路

4903 画素部

4904 画素

5001 配線A

5002 配線B

5103 スイッチ

5104 容量素子

5105 スイッチ

5106 スイッチ

5108 表示素子

5109 配線

5110 配線

5111 配線

5112 対向電極

5114 配線

5201 電流源

5212 配線

5501 スイッチ

5502 スイッチ

5503 プリチャージ用電流源

5504 配線

5505 配線

5601 電流源トランジスタ

5602 切り替えトランジスタ

5603 スイッチングトランジスタ

5604 容量素子

5605 スイッチングトランジスタ

5606 スイッチングトランジスタ

5608 表示素子

5609 配線

5610 配線

5611 配線

5612 対向電極

5614 配線

5615 配線

5701 電流源

5712 配線

5803 スイッチングトランジスタ

5805 スイッチングトランジスタ

5806 スイッチングトランジスタ

6201 マルチゲートトランジスタ

6501 スイッチ

6502 配線

6601 整流素子

6602 配線

6701 信号線駆動回路

6702 画素部

6703 走査線駆動回路

6704 封止基板

6705 シール材

6706 走査線駆動回路

6707 空間

6708 配線

6709 FPC

6710 基板

6711 TFT

6712 TFT

6713 電極

6714 絶縁物

6716 層

6717 電極

6718 発光素子

6719 ICチップ

6720 Nチャネル型TFT

6721 Nチャネル型TFT

6740 基板

6800 基板

6801 信号線駆動回路

6802 画素部

6803 走査線駆動回路

6804 走査線駆動回路

6805 FPC

6806 ICチップ

6807 ICチップ

6808 封止基板

6809 シール材

6810 基板

6811 信号線駆動回路

6812 画素部

6813 走査線駆動回路

6814 走査線駆動回路

6815 第FPC

6816 ICチップ

6817 ICチップ

6818 封止基板

6819 シール材

6900 基板

6901 周辺駆動回路

6902 画素部

6904 第FPC

6905 ICチップ

6906 ICチップ

6907 封止基板

6908 シール材

6910 基板

6911 周辺駆動回路

6912 画素部

6913 FPC

6914 FPC

7001 基板

7002 陽極

7003 正孔注入層

7004 正孔輸送層

7005 発光層

7006 電子輸送層

7007 電子注入層

7008 陰極

7011 基板

7012 陽極

7013 正孔注入層

7014 正孔輸送層

7015 発光層

7016 電子輸送層

7017 電子注入層

7018 陰極

7100 基板

7101 駆動用TFT

7102 電極

7103 層

7104 電極

7200 基板

7201 駆動用TFT

7202 下地膜

7203 電極

7204 層

7205 電極

7501 基板

7502 下地膜

7503 ゲート電極

7504 電極

7505 ゲート絶縁膜

7506 チャネル形成領域

7507 LDD領域

7508 不純物領域

7509 チャネル形成領域

7510 LDD領域

7511 不純物領域

7512 層間絶縁物

7513 配線

7514 電極

7515 開口部

7516 層間絶縁物

7517 画素電極

7518 絶縁物

7519 層

7520 対向電極

7521 発光素子

7522 駆動トランジスタ

7523 容量素子

7524 電極

7525 容量素子

7601 基板

7602 下地膜

7603 画素電極

7604 電極

7605 配線

7606 配線

7607 N型半導体層

7608 N型半導体層

7609 半導体層

7610 ゲート絶縁膜

7611 絶縁膜

7612 ゲート電極

7613 電極

7614 層間絶縁物

7615 層

7616 対向電極

7617 発光素子

7618 駆動トランジスタ

7619 容量素子

7620 電極

7701 基板

7702 下地膜

7703 ゲート電極

7704 電極

7705 ゲート絶縁膜

7706 半導体層

7707 半導体層

7708 N型半導体層

7710 N型半導体層

7711 配線

7713 導電層

7714 画素電極

7715 絶縁物

7716 層

7717 対向電極

7718 発光素子

7719 駆動トランジスタ

7720 容量素子

7721 電極

7722 容量素子

7801 絶縁物

7802 絶縁物

7901 表示パネル

7902 画素部

7903 走査線駆動回路

7904 信号線駆動回路

7911 回路基板

7912 コントロール回路

7913 信号分割回路

7914 接続配線

8001 チューナ

8002 映像波増幅回路

8003 映像信号処理回路

8004 信号線駆動回路

8005 音声波増幅回路

8006 音声信号処理回路

8007 スピーカー

8008 制御回路

8009 入力部

8010 表示パネル

8011 走査線駆動回路

8012 コントロール回路

8013 信号分割回路

8102 表示画面

8103 スピーカー

8104 操作スイッチ

8110 充電器

8112 筐体

8113 表示部

8116 操作キー

8117 スピーカー部

8201 表示パネル

8202 プリント配線基板

8203 画素部

8204 走査線駆動回路

8205 走査線駆動回路

8206 信号線駆動回路

8207 コントローラ

8208 CPU

8209 メモリ

8210 電源回路

8211 音声処理回路

8212 送受信回路

8213 フレキシブル配線基板

8214 インターフェイス部

8215 アンテナ用ポート

8216 VRAM

8217 DRAM

8218 フラッシュメモリ

8219 インターフェース

8220 制御信号生成回路

8221 デコーダ

8222 レジスタ

8223 演算回路

8224 RAM

8225 入力手段

8226 マイク

8227 スピーカー

8228 アンテナ

8301 表示パネル

8313 FPC

8330 ハウジング

8331 プリント基板

8332 スピーカー

8333 マイクロフォン

8334 送受信回路

8335 信号処理回路

8336 入力手段

8337 バッテリー

8339 筐体

8501 スイッチ

8502 配線

8601 スイッチ

8602 配線

8603 ノード

8701 基板

8702 下地膜

8703 チャネル形成領域

8704 不純物領域

8705 低濃度不純物領域

8706 ゲート絶縁膜

8707 ゲート電極

8708 層間絶縁物

8709 電極

8710 層間絶縁物

8711 画素電極

8712 絶縁物

8713 層

8714 対向電極

8715 トランジスタ

8716 発光素子

8717 接合部

8718 無機絶縁膜

8719 配線

8720 電極

8721 電極

8722 サイドウォール

8723 トランジスタ

8724 電極

8901 信号線駆動回路

8902 走査線駆動回路

8903 画素部

8904 画素

8905 走査線駆動回路

8906 パルス出力回路

8907 パルス出力回路

8908 スイッチ

8909 スイッチ

9201 電流源トランジスタ

9202 切り替えトランジスタ

9203 スイッチ

9204 容量素子

9205 スイッチ

9206 スイッチ

9207 電流源

9208 負荷

9209 配線

9211 配線

9212 配線

9213 スイッチ

9301 電流源トランジスタ

9302 切り替えトランジスタ

9303 スイッチ

9304 容量素子

9305 スイッチ

9308 負荷

9309 配線

9312 配線

9313 スイッチ

9601 電流源トランジスタ

9603 切り替えスイッチ

9604 容量素子

9605 スイッチ

9606 スイッチ

9607 電流源

9608 負荷

9609 配線

9611 配線

9612 配線

9701 電車車両本体

9702 表示パネル

9703 表示パネル

9704 表示パネル

9801 電柱

9802 表示パネル

9803 移動体

9901 車体

9902 表示パネル

10001 ユニットバス

10002 表示パネル

10101 飛行機車体

10102 表示パネル

10103 ヒンジ部

26101 基板

26102 下地膜

26103 チャネル形成領域

26105 不純物領域

26106 チャネル形成領域

26107 LDD領域

26108 不純物領域

26109 ゲート絶縁膜

26110 ゲート電極

26111 上部電極

26112 層間絶縁物

26113 配線

26114 画素電極

26115 層間絶縁物

26116 層

26117 対向電極

26118 駆動トランジスタ

26119 容量素子

26120 発光素子

26202 領域

26301 上部電極

26302 容量素子

27101 基板

27102 下地膜

27103 チャネル形成領域

27105 不純物領域

27106 ゲート絶縁膜

27107 ゲート電極

27108 電極

27109 層間絶縁物

27110 配線

27111 電極

27112 層間絶縁物

27113 画素電極

27114 電極

27115 層間絶縁物

27116 層

27117 対向電極

27118 駆動トランジスタ

27119 容量素子

27120 発光素子

4501A 電流源

4502A 電流源回路

4503A スイッチ

4902A 走査線駆動回路

4902B 走査線駆動回路

5101A 電流源トランジスタ

5101B 電流源トランジスタ

5102A 切り替えトランジスタ

5102B 切り替えトランジスタ

5103A スイッチA

5103B スイッチB

5105A 配線A

5105B 配線B

5115A 配線A

5115B 配線B

5116A スイッチA

5116B スイッチB

7206B カラーフィルター

7206G カラーフィルター

7206R カラーフィルター

84101 筐体

84102 支持台

84103 表示部

84201 本体

84202 表示部

84203 受像部

84204 操作キー

84205 外部接続ポート

84206 シャッター

84301 本体

84302 筐体

84303 表示部

84304 キーボード

84305 外部接続ポート

84306 ポインティングマウス

84401 本体

84402 表示部

84403 スイッチ

84404 操作キー

84405 赤外線ポート

84501 本体

84502 筐体

84503 表示部A

84504 表示部B

84505 部

84506 操作キー

84507 スピーカー部

84601 本体

84602 表示部

84603 イヤホン

84604 支持部

84701 筐体

84702 表示部

84703 スピーカー部

84704 操作キー

84705 記憶媒体挿入部

84801 本体

84802 表示部

84803 操作キー

84804 スピーカー

84805 シャッター

84806 受像部

84807 アンテナ

9306A スイッチ

9307A 電流源

9311A 配線

Claims (8)

- 第1及び第2のスイッチと、第1及び第2のトランジスタと、を有する表示装置であって、

前記第1のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第1の配線と接続され、

前記第1のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のスイッチの第1端子と接続され、

前記第1のスイッチの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第2の配線と接続され、

前記第2のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のトランジスタの第2端子と接続され、

前記第2のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のスイッチの第1端子と接続され、

前記第2のトランジスタの第2端子は、インダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、表示素子の第1の端子と接続され、

前記第2のトランジスタの第2の端子は、スイッチ又はトランジスタを介さずに前記表示素子の第1の端子と接続され、

前記表示素子の第2の端子は、スイッチ又はトランジスタを介さずに第4の配線と接続され、

前記第2のトランジスタの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のスイッチの第1端子と接続され、

前記第2のスイッチの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第3の配線と接続され、

前記第2の配線は、一定の電位を供給することができる機能を有し、

前記一定の電位は、前記第1の配線が供給することができる電位の大きさと、前記第4の配線が供給することができる電位の大きさとの間の大きさの電位であり、

前記第3の配線は、電流を供給することができる機能を有し、

前記電流が前記第2のスイッチを介して供給されているときに、前記表示素子に前記電流が供給されない期間を有し、

前記第1のトランジスタの第1端子と前記第1のトランジスタの第2端子との間、または、前記第2のトランジスタの第1端子と前記第2のトランジスタの第2端子との間を、短絡状態にする手段を有し、

前記表示素子は、有機材料を含むEL素子、有機材料及び無機材料を含むEL素子、電子放出素子、又はカーボンナノチューブを有することを特徴とする表示装置。 - 第1乃至第3のスイッチと、第1及び第2のトランジスタと、を有する表示装置であって、

前記第1のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第1の配線と接続され、

前記第1のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のスイッチの第1端子と接続され、

前記第1のスイッチの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第2の配線と接続され、

前記第2のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のトランジスタの第2端子と接続され、

前記第2のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のスイッチの第1端子と接続され、

前記第2のトランジスタの第2端子は、インダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、表示素子の第1の端子と接続され、

前記第2のトランジスタの第2の端子は、スイッチ又はトランジスタを介さずに前記表示素子の第1の端子と接続され、

前記表示素子の第2の端子は、スイッチ又はトランジスタを介さずに第4の配線と接続され、

前記第2のトランジスタの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のスイッチの第1端子と接続され、

前記第2のスイッチの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第3の配線と接続され、

前記第2の配線は、一定の電位を供給することができる機能を有し、

前記一定の電位は、前記第1の配線が供給することができる電位の大きさと、前記第4の配線が供給することができる電位の大きさとの間の大きさの電位であり、

前記第3の配線は、電流を供給することができる機能を有し、

前記電流が前記第2のスイッチを介して供給されているときに、前記表示素子に前記電流が供給されない期間を有し、

前記第3のスイッチの第1の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のトランジスタの第1端子と接続され、

前記第3のスイッチの第2の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のトランジスタの第1端子、又は、前記第2のトランジスタの第2端子と接続されており、

前記表示素子は、有機材料を含むEL素子、有機材料及び無機材料を含むEL素子、電子放出素子、又はカーボンナノチューブを有することを特徴とする表示装置。 - 請求項1又は2において、

前記第1のスイッチ及び前記第2のスイッチはトランジスタであることを特徴とする表示装置。 - 第1乃至第5のトランジスタを有する表示装置であって、

前記第1のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第1の配線と接続され、

前記第1のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第3のトランジスタの第1端子と接続され、

前記第3のトランジスタの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第2の配線と接続され、

前記第2のトランジスタの第1端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のトランジスタの第2端子と接続され、

前記第2のトランジスタのゲートは、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第3のトランジスタの第1端子と接続され、

前記第2のトランジスタの第2端子は、インダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、表示素子の第1の端子と接続され、

前記第2のトランジスタの第2の端子は、スイッチ又はトランジスタを介さずに前記表示素子の第1の端子と接続され、

前記表示素子の第2の端子は、スイッチ又はトランジスタを介さずに第4の配線と接続され、

前記第2のトランジスタの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第4のトランジスタの第1端子と接続され、

前記第4のトランジスタの第2端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、第3の配線と接続され、

前記第2の配線は、一定の電位を供給することができる機能を有し、

前記一定の電位は、前記第1の配線が供給することができる電位の大きさと、前記第4の配線が供給することができる電位の大きさとの間の大きさの電位であり、

前記第3の配線は、電流を供給することができる機能を有し、

前記電流が前記第4のトランジスタを介して供給されているときに、前記表示素子に前記電流が供給されない期間を有し、

前記第5のトランジスタの第1の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のトランジスタの第1端子と接続され、

前記第5のトランジスタの第2の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第1のトランジスタの第1端子、又は、前記第2のトランジスタの第2端子と接続されており、

前記表示素子は、有機材料を含むEL素子、有機材料及び無機材料を含むEL素子、電子放出素子、又はカーボンナノチューブを有することを特徴とする表示装置。 - 請求項1乃至請求項4のいずれか一項において、

容量素子を有し、

前記容量素子の一方の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のトランジスタのゲートと接続され、

前記容量素子の他方の端子は、スイッチとトランジスタとインダクタと抵抗素子とダイオードとのうちの少なくとも一つを介して、又は、介さずに、前記第2のトランジスタの第2端子と接続されることを特徴とする表示装置。 - 請求項1乃至請求項5のいずれか一項において、

前記第1のトランジスタ及び前記第2のトランジスタは同じ導電型であることを特徴とする表示装置。 - ハウジング、又は、FPCと、

請求項1乃至請求項6のいずれか一項に記載の表示装置と、

を有する表示モジュール。 - アンテナ、操作キー、又は、スピーカと、

請求項1乃至請求項6のいずれか一項に記載の表示装置、又は、請求項7に記載の表示モジュールと、

を有する電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006216902A JP5695813B2 (ja) | 2005-08-12 | 2006-08-09 | 表示装置、表示モジュール、及び電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005234007 | 2005-08-12 | ||

| JP2005234007 | 2005-08-12 | ||

| JP2006216902A JP5695813B2 (ja) | 2005-08-12 | 2006-08-09 | 表示装置、表示モジュール、及び電子機器 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012022917A Division JP2012133381A (ja) | 2005-08-12 | 2012-02-06 | 半導体装置、表示装置、表示モジュール、及び電子機器 |

| JP2013090275A Division JP2013140407A (ja) | 2005-08-12 | 2013-04-23 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007072453A JP2007072453A (ja) | 2007-03-22 |

| JP2007072453A5 JP2007072453A5 (ja) | 2009-09-17 |

| JP5695813B2 true JP5695813B2 (ja) | 2015-04-08 |

Family

ID=37721896

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006216902A Expired - Fee Related JP5695813B2 (ja) | 2005-08-12 | 2006-08-09 | 表示装置、表示モジュール、及び電子機器 |

| JP2012022917A Withdrawn JP2012133381A (ja) | 2005-08-12 | 2012-02-06 | 半導体装置、表示装置、表示モジュール、及び電子機器 |

| JP2013090275A Withdrawn JP2013140407A (ja) | 2005-08-12 | 2013-04-23 | 半導体装置 |

| JP2014159301A Expired - Fee Related JP5933648B2 (ja) | 2005-08-12 | 2014-08-05 | 表示装置、表示モジュール、電子機器 |

| JP2016040154A Withdrawn JP2016145986A (ja) | 2005-08-12 | 2016-03-02 | 表示装置、表示モジュール、及び電子機器 |

Family Applications After (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012022917A Withdrawn JP2012133381A (ja) | 2005-08-12 | 2012-02-06 | 半導体装置、表示装置、表示モジュール、及び電子機器 |

| JP2013090275A Withdrawn JP2013140407A (ja) | 2005-08-12 | 2013-04-23 | 半導体装置 |

| JP2014159301A Expired - Fee Related JP5933648B2 (ja) | 2005-08-12 | 2014-08-05 | 表示装置、表示モジュール、電子機器 |

| JP2016040154A Withdrawn JP2016145986A (ja) | 2005-08-12 | 2016-03-02 | 表示装置、表示モジュール、及び電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7859488B2 (ja) |

| JP (5) | JP5695813B2 (ja) |

| KR (3) | KR101228971B1 (ja) |

| CN (2) | CN102148008B (ja) |

| TW (2) | TWI485681B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015014795A (ja) * | 2005-08-12 | 2015-01-22 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Families Citing this family (92)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1544842B1 (en) * | 2003-12-18 | 2018-08-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| US7592975B2 (en) * | 2004-08-27 | 2009-09-22 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof |

| JP2008009277A (ja) * | 2006-06-30 | 2008-01-17 | Canon Inc | 電圧電流変換方法、電圧電流変換回路、及びアクティブマトリクス型表示装置 |

| TWI324406B (en) * | 2006-12-18 | 2010-05-01 | Ind Tech Res Inst | Printed circuit unit based on organic transistor |

| US7738050B2 (en) * | 2007-07-06 | 2010-06-15 | Semiconductor Energy Laboratory Co., Ltd | Liquid crystal display device |

| US20090091264A1 (en) * | 2007-10-04 | 2009-04-09 | Himax Technologies Limited | Pixel circuit |

| GB2456005B (en) * | 2007-12-28 | 2013-03-06 | Wolfson Ltd | Amplifier circuit |

| JP2009300866A (ja) * | 2008-06-16 | 2009-12-24 | Nec Electronics Corp | 駆動回路および表示装置 |

| JP5442234B2 (ja) * | 2008-10-24 | 2014-03-12 | 株式会社半導体エネルギー研究所 | 半導体装置及び表示装置 |

| KR101772639B1 (ko) * | 2009-10-16 | 2017-08-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US9899329B2 (en) | 2010-11-23 | 2018-02-20 | X-Celeprint Limited | Interconnection structures and methods for transfer-printed integrated circuit elements with improved interconnection alignment tolerance |

| TWI424413B (zh) * | 2010-12-28 | 2014-01-21 | Au Optronics Corp | 主動矩陣有機發光二極體顯示器之像素電路 |

| US9886899B2 (en) * | 2011-05-17 | 2018-02-06 | Ignis Innovation Inc. | Pixel Circuits for AMOLED displays |

| JP5686043B2 (ja) * | 2011-06-02 | 2015-03-18 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| US8889485B2 (en) | 2011-06-08 | 2014-11-18 | Semprius, Inc. | Methods for surface attachment of flipped active componenets |

| WO2013018597A1 (ja) | 2011-08-02 | 2013-02-07 | シャープ株式会社 | 表示装置およびその駆動方法 |

| KR102549647B1 (ko) | 2011-10-18 | 2023-07-03 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 발광 장치 |

| US10043794B2 (en) | 2012-03-22 | 2018-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| JP6031954B2 (ja) * | 2012-11-14 | 2016-11-24 | ソニー株式会社 | 発光素子、表示装置及び電子機器 |

| CN103021306B (zh) * | 2012-12-05 | 2016-12-21 | 昆山维信诺科技有限公司 | 一种屏体老炼引线布线结构及其制备方法 |

| CA2894717A1 (en) | 2015-06-19 | 2016-12-19 | Ignis Innovation Inc. | Optoelectronic device characterization in array with shared sense line |

| CN104122805B (zh) * | 2013-04-26 | 2016-12-28 | 立锜科技股份有限公司 | 数字卫星设备控制信号产生电路及相关的信号产生方法 |

| US9735671B2 (en) | 2013-05-17 | 2017-08-15 | Cirrus Logic, Inc. | Charge pump-based drive circuitry for bipolar junction transistor (BJT)-based power supply |

| WO2014186765A1 (en) | 2013-05-17 | 2014-11-20 | Cirrus Logic, Inc. | Single pin control of bipolar junction transistor (bjt)-based power stage |

| US9496855B2 (en) | 2013-07-29 | 2016-11-15 | Cirrus Logic, Inc. | Two terminal drive of bipolar junction transistor (BJT) of a light emitting diode (LED)-based bulb |

| US9504106B2 (en) | 2013-07-29 | 2016-11-22 | Cirrus Logic, Inc. | Compensating for a reverse recovery time period of a bipolar junction transistor (BJT) in switch-mode operation of a light-emitting diode (LED)-based bulb |

| KR102117988B1 (ko) * | 2013-10-08 | 2020-06-10 | 삼성디스플레이 주식회사 | 평판 표시장치 및 그의 구동방법 |

| TWI656620B (zh) | 2014-06-18 | 2019-04-11 | 愛爾蘭商艾克斯瑟樂普林特有限公司 | 微組裝發光二極體顯示器及照明元件 |

| KR102275615B1 (ko) | 2014-08-26 | 2021-07-09 | 엑스-셀레프린트 리미티드 | 마이크로 어셈블링된 하이브리드 디스플레이들 및 조명 엘리먼트들 |

| KR102388997B1 (ko) | 2014-08-29 | 2022-04-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 및 전자 기기 |

| KR102441803B1 (ko) | 2014-09-02 | 2022-09-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 및 전자 기기 |

| US9537069B1 (en) | 2014-09-25 | 2017-01-03 | X-Celeprint Limited | Inorganic light-emitting diode with encapsulating reflector |

| US9991163B2 (en) | 2014-09-25 | 2018-06-05 | X-Celeprint Limited | Small-aperture-ratio display with electrical component |

| US9799719B2 (en) | 2014-09-25 | 2017-10-24 | X-Celeprint Limited | Active-matrix touchscreen |

| US9818725B2 (en) | 2015-06-01 | 2017-11-14 | X-Celeprint Limited | Inorganic-light-emitter display with integrated black matrix |

| US9799261B2 (en) | 2014-09-25 | 2017-10-24 | X-Celeprint Limited | Self-compensating circuit for faulty display pixels |

| TWI556681B (zh) * | 2014-11-12 | 2016-11-01 | Light emitting diode switch circuit | |

| US9504118B2 (en) | 2015-02-17 | 2016-11-22 | Cirrus Logic, Inc. | Resistance measurement of a resistor in a bipolar junction transistor (BJT)-based power stage |

| US9603206B2 (en) | 2015-02-27 | 2017-03-21 | Cirrus Logic, Inc. | Detection and control mechanism for tail current in a bipolar junction transistor (BJT)-based power stage |

| US9609701B2 (en) | 2015-02-27 | 2017-03-28 | Cirrus Logic, Inc. | Switch-mode drive sensing of reverse recovery in bipolar junction transistor (BJT)-based power converters |

| US9871345B2 (en) | 2015-06-09 | 2018-01-16 | X-Celeprint Limited | Crystalline color-conversion device |

| US10133426B2 (en) | 2015-06-18 | 2018-11-20 | X-Celeprint Limited | Display with micro-LED front light |

| US11061276B2 (en) | 2015-06-18 | 2021-07-13 | X Display Company Technology Limited | Laser array display |

| US10255834B2 (en) | 2015-07-23 | 2019-04-09 | X-Celeprint Limited | Parallel redundant chiplet system for controlling display pixels |

| US9640108B2 (en) | 2015-08-25 | 2017-05-02 | X-Celeprint Limited | Bit-plane pulse width modulated digital display system |

| US10380930B2 (en) | 2015-08-24 | 2019-08-13 | X-Celeprint Limited | Heterogeneous light emitter display system |

| US10230048B2 (en) | 2015-09-29 | 2019-03-12 | X-Celeprint Limited | OLEDs for micro transfer printing |

| US10066819B2 (en) | 2015-12-09 | 2018-09-04 | X-Celeprint Limited | Micro-light-emitting diode backlight system |

| US9930277B2 (en) | 2015-12-23 | 2018-03-27 | X-Celeprint Limited | Serial row-select matrix-addressed system |

| US10091446B2 (en) | 2015-12-23 | 2018-10-02 | X-Celeprint Limited | Active-matrix displays with common pixel control |

| US9786646B2 (en) | 2015-12-23 | 2017-10-10 | X-Celeprint Limited | Matrix addressed device repair |

| US9928771B2 (en) | 2015-12-24 | 2018-03-27 | X-Celeprint Limited | Distributed pulse width modulation control |

| US10200013B2 (en) | 2016-02-18 | 2019-02-05 | X-Celeprint Limited | Micro-transfer-printed acoustic wave filter device |

| US10361677B2 (en) | 2016-02-18 | 2019-07-23 | X-Celeprint Limited | Transverse bulk acoustic wave filter |

| US10109753B2 (en) | 2016-02-19 | 2018-10-23 | X-Celeprint Limited | Compound micro-transfer-printed optical filter device |

| EP3420582A1 (en) | 2016-02-25 | 2019-01-02 | X-Celeprint Limited | Efficiently micro-transfer printing micro-scale devices onto large-format substrates |

| US10150326B2 (en) | 2016-02-29 | 2018-12-11 | X-Celeprint Limited | Hybrid document with variable state |

| US10150325B2 (en) | 2016-02-29 | 2018-12-11 | X-Celeprint Limited | Hybrid banknote with electronic indicia |

| US10193025B2 (en) | 2016-02-29 | 2019-01-29 | X-Celeprint Limited | Inorganic LED pixel structure |

| US10153256B2 (en) | 2016-03-03 | 2018-12-11 | X-Celeprint Limited | Micro-transfer printable electronic component |

| US10153257B2 (en) | 2016-03-03 | 2018-12-11 | X-Celeprint Limited | Micro-printed display |

| US10008483B2 (en) | 2016-04-05 | 2018-06-26 | X-Celeprint Limited | Micro-transfer printed LED and color filter structure |

| US10199546B2 (en) | 2016-04-05 | 2019-02-05 | X-Celeprint Limited | Color-filter device |

| US10198890B2 (en) | 2016-04-19 | 2019-02-05 | X-Celeprint Limited | Hybrid banknote with electronic indicia using near-field-communications |

| US9997102B2 (en) | 2016-04-19 | 2018-06-12 | X-Celeprint Limited | Wirelessly powered display and system |

| US10360846B2 (en) | 2016-05-10 | 2019-07-23 | X-Celeprint Limited | Distributed pulse-width modulation system with multi-bit digital storage and output device |

| US9997501B2 (en) | 2016-06-01 | 2018-06-12 | X-Celeprint Limited | Micro-transfer-printed light-emitting diode device |

| US10453826B2 (en) | 2016-06-03 | 2019-10-22 | X-Celeprint Limited | Voltage-balanced serial iLED pixel and display |

| US11137641B2 (en) | 2016-06-10 | 2021-10-05 | X Display Company Technology Limited | LED structure with polarized light emission |

| JP6725173B2 (ja) * | 2016-08-12 | 2020-07-15 | アズビル株式会社 | インタフェース回路 |

| CN107799072B (zh) * | 2016-09-07 | 2020-08-11 | 元太科技工业股份有限公司 | 电子纸显示器装置 |

| US9980341B2 (en) | 2016-09-22 | 2018-05-22 | X-Celeprint Limited | Multi-LED components |

| US10782002B2 (en) | 2016-10-28 | 2020-09-22 | X Display Company Technology Limited | LED optical components |

| US10347168B2 (en) | 2016-11-10 | 2019-07-09 | X-Celeprint Limited | Spatially dithered high-resolution |

| US10600671B2 (en) | 2016-11-15 | 2020-03-24 | X-Celeprint Limited | Micro-transfer-printable flip-chip structures and methods |

| US10395966B2 (en) | 2016-11-15 | 2019-08-27 | X-Celeprint Limited | Micro-transfer-printable flip-chip structures and methods |

| WO2018091459A1 (en) | 2016-11-15 | 2018-05-24 | X-Celeprint Limited | Micro-transfer-printable flip-chip structures and methods |

| US10438859B2 (en) | 2016-12-19 | 2019-10-08 | X-Celeprint Limited | Transfer printed device repair |

| US10832609B2 (en) | 2017-01-10 | 2020-11-10 | X Display Company Technology Limited | Digital-drive pulse-width-modulated output system |

| US10396137B2 (en) | 2017-03-10 | 2019-08-27 | X-Celeprint Limited | Testing transfer-print micro-devices on wafer |

| JP6841099B2 (ja) * | 2017-03-15 | 2021-03-10 | セイコーエプソン株式会社 | 半導体装置、発光制御回路、及び、電子機器 |

| CN106782340B (zh) * | 2017-03-16 | 2018-09-07 | 深圳市华星光电技术有限公司 | 一种像素驱动电路及oled显示装置 |

| US11024608B2 (en) | 2017-03-28 | 2021-06-01 | X Display Company Technology Limited | Structures and methods for electrical connection of micro-devices and substrates |

| JP6512259B1 (ja) * | 2017-10-30 | 2019-05-15 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP7225112B2 (ja) * | 2017-11-09 | 2023-02-20 | 株式会社半導体エネルギー研究所 | 表示装置、電子機器 |

| US10690920B2 (en) | 2018-02-28 | 2020-06-23 | X Display Company Technology Limited | Displays with transparent bezels |

| US11189605B2 (en) | 2018-02-28 | 2021-11-30 | X Display Company Technology Limited | Displays with transparent bezels |

| CN108377147B (zh) * | 2018-04-27 | 2023-11-28 | 张家港乐达汽车电器有限公司 | 一种具有按键防护功能的brt快速控制开关 |

| US10910355B2 (en) | 2018-04-30 | 2021-02-02 | X Display Company Technology Limited | Bezel-free displays |

| TWI669815B (zh) * | 2018-06-26 | 2019-08-21 | 智晶光電股份有限公司 | 柔性基板側向薄膜封裝 |

| TWI707325B (zh) * | 2019-07-01 | 2020-10-11 | 友達光電股份有限公司 | 發光二極體驅動電路 |

| CN114495843B (zh) * | 2022-01-25 | 2023-09-08 | 江西兴泰科技股份有限公司 | 一种像素tft充放电面板电路结构 |

Family Cites Families (79)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5216531A (en) | 1990-08-28 | 1993-06-01 | Asahi Glass Company Ltd. | Projection type active matrix polymer dispersed liquid crystal display apparatus with particles of liquid crystal material randomly oriented |

| JP3672586B2 (ja) * | 1994-03-24 | 2005-07-20 | 株式会社半導体エネルギー研究所 | 補正システムおよびその動作方法 |

| US5942773A (en) | 1996-06-04 | 1999-08-24 | Fujitsu Limited | Field effect transistor with reduced delay variation |

| US6229506B1 (en) | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| FR2772501B1 (fr) | 1997-12-15 | 2000-01-21 | Thomson Lcd | Dispositif de commande matriciel |

| GB9812742D0 (en) * | 1998-06-12 | 1998-08-12 | Philips Electronics Nv | Active matrix electroluminescent display devices |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000056286A (ja) | 1998-08-07 | 2000-02-25 | Dainippon Printing Co Ltd | 可逆表示媒体の書換装置 |

| JP2000105350A (ja) | 1998-09-30 | 2000-04-11 | Sony Corp | 三次元立体像表示方法および三次元立体像表示装置および三次元立体像表示システムおよび三次元像表示方法および三次元像表示装置 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP4229513B2 (ja) * | 1999-03-10 | 2009-02-25 | 三洋電機株式会社 | アクティブ型el表示装置 |

| US6346730B1 (en) | 1999-04-06 | 2002-02-12 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device having a pixel TFT formed in a display region and a drive circuit formed in the periphery of the display region on the same substrate |

| US6630977B1 (en) | 1999-05-20 | 2003-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with capacitor formed around contact hole |

| JP2001166252A (ja) | 1999-12-03 | 2001-06-22 | Sony Corp | 画像表示装置 |

| JP2001189520A (ja) | 1999-12-28 | 2001-07-10 | Sony Corp | 光源装置およびそれを用いた投射型表示装置 |

| JP2001318627A (ja) * | 2000-02-29 | 2001-11-16 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| KR100327374B1 (ko) * | 2000-03-06 | 2002-03-06 | 구자홍 | 액티브 구동 회로 |

| TW531901B (en) * | 2000-04-27 | 2003-05-11 | Semiconductor Energy Lab | Light emitting device |

| CN1658266A (zh) * | 2000-07-07 | 2005-08-24 | 精工爱普生株式会社 | 驱动电流驱动元件的驱动电路及其方法 |

| US6828950B2 (en) | 2000-08-10 | 2004-12-07 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method of driving the same |

| JP4352598B2 (ja) | 2000-08-24 | 2009-10-28 | ソニー株式会社 | 液晶表示装置および携帯端末 |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| JP3736399B2 (ja) | 2000-09-20 | 2006-01-18 | セイコーエプソン株式会社 | アクティブマトリクス型表示装置の駆動回路及び電子機器及び電気光学装置の駆動方法及び電気光学装置 |

| US6864863B2 (en) | 2000-10-12 | 2005-03-08 | Seiko Epson Corporation | Driving circuit including organic electroluminescent element, electronic equipment, and electro-optical device |

| JP4092541B2 (ja) | 2000-12-08 | 2008-05-28 | ソニー株式会社 | 半導体薄膜の形成方法及び半導体装置の製造方法 |

| TWI313059B (ja) | 2000-12-08 | 2009-08-01 | Sony Corporatio | |

| JP2002198311A (ja) | 2000-12-25 | 2002-07-12 | Sony Corp | 多結晶性半導体薄膜の形成方法及び半導体装置の製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| JP2002231628A (ja) | 2001-02-01 | 2002-08-16 | Sony Corp | 半導体薄膜の形成方法及び半導体装置の製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| JP2002246310A (ja) | 2001-02-14 | 2002-08-30 | Sony Corp | 半導体薄膜の形成方法及び半導体装置の製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| JP2002246311A (ja) | 2001-02-19 | 2002-08-30 | Sony Corp | 多結晶性半導体薄膜及びその形成方法、半導体装置及びその製造方法、これらの方法の実施に使用する装置、並びに電気光学装置 |

| WO2002075709A1 (fr) | 2001-03-21 | 2002-09-26 | Canon Kabushiki Kaisha | Circuit permettant d'actionner un element electroluminescent a matrice active |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP2002350749A (ja) | 2001-05-23 | 2002-12-04 | Sony Corp | 光変調素子駆動システム及びその駆動装置、並びに投映システム |

| JP2003005710A (ja) | 2001-06-25 | 2003-01-08 | Nec Corp | 電流駆動回路及び画像表示装置 |

| JP4650601B2 (ja) * | 2001-09-05 | 2011-03-16 | 日本電気株式会社 | 電流駆動素子の駆動回路及び駆動方法ならびに画像表示装置 |

| JP2004054200A (ja) * | 2001-09-21 | 2004-02-19 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US20040222089A1 (en) * | 2001-09-27 | 2004-11-11 | Kazuyoshi Inoue | Sputtering target and transparent electroconductive film |

| WO2003040441A1 (en) | 2001-11-05 | 2003-05-15 | Japan Science And Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| KR100940342B1 (ko) | 2001-11-13 | 2010-02-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 그 구동방법 |

| JP4074502B2 (ja) | 2001-12-12 | 2008-04-09 | セイコーエプソン株式会社 | 表示装置用電源回路、表示装置及び電子機器 |

| JP2003195810A (ja) | 2001-12-28 | 2003-07-09 | Casio Comput Co Ltd | 駆動回路、駆動装置及び光学要素の駆動方法 |

| EP1331627B1 (en) | 2002-01-24 | 2012-04-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of driving the semiconductor device |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US6885146B2 (en) | 2002-03-14 | 2005-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Display device comprising substrates, contrast medium and barrier layers between contrast medium and each of substrates |

| JP4610843B2 (ja) * | 2002-06-20 | 2011-01-12 | カシオ計算機株式会社 | 表示装置及び表示装置の駆動方法 |

| JP4103500B2 (ja) | 2002-08-26 | 2008-06-18 | カシオ計算機株式会社 | 表示装置及び表示パネルの駆動方法 |

| JP2004101777A (ja) | 2002-09-09 | 2004-04-02 | Sony Corp | 画像形成方法及びその画像形成装置 |

| JP4515082B2 (ja) | 2002-12-03 | 2010-07-28 | 株式会社半導体エネルギー研究所 | アナログ回路並びにアナログ回路を用いた表示装置及び電子機器 |