JP4352598B2 - 液晶表示装置および携帯端末 - Google Patents

液晶表示装置および携帯端末 Download PDFInfo

- Publication number

- JP4352598B2 JP4352598B2 JP2000254335A JP2000254335A JP4352598B2 JP 4352598 B2 JP4352598 B2 JP 4352598B2 JP 2000254335 A JP2000254335 A JP 2000254335A JP 2000254335 A JP2000254335 A JP 2000254335A JP 4352598 B2 JP4352598 B2 JP 4352598B2

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- crystal display

- substrate

- display device

- semiconductor chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Mathematical Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Liquid Crystal (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

【発明の属する技術分野】

本発明は、液晶表示装置およびこれを用いた携帯端末に関し、特に薄型化、小面積化、狭額縁化が要求される携帯端末に使用される液晶表示装置およびこれを表示部として用いる携帯端末に関する。

【0002】

【従来の技術】

テレビジョン受像機、コンピュータあるいは携帯端末などの表示装置として、近年、薄型で低消費電力のパネルディスプレイが多用されるようになってきている。

このパネルディスプレイとしては、ガラス基板などの透明絶縁基板(パネル)上に、スイッチング素子として、例えばTFT(Thin Film Transistor;薄膜トランジスタ)を用いた画素を行列状に多数配列し、液晶などの電気光学的効果を有する物質と組み合わせたアクティブマトリックス型表示装置が知られている。

【0003】

このアクティブマトリクス型表示装置として、特開平4−242724号公報では、画素部を駆動するために基板上に形成される周辺回路の一部を、画素に接続されたアクティブ素子と同様の相補型のTFTで構成し、残りの周辺回路を半導体チップで構成した液晶表示装置を提供している。

【0004】

図12(a)に上記の従来の液晶表示装置の概略構成図を、図12(b)に図12(a)におけるA−A線の断面図を示す。

図12(a)および(b)に示す液晶表示装置では、TFTにより形成された一部の周辺回路(例えば水平ドライバ14、垂直ドライバ13など)が形成された透明絶縁基板16と、これと対向配置された透明絶縁性基板(対向基板)62との間に液晶層63を保持してなる液晶表示装置において、半導体チップで構成した残りの周辺回路(例えばタイミングコントローラ23、基準電圧発生回路24、およびDC−DCコンバータ25など)、すなわちICチップ(23〜25)を透明絶縁基板16における周辺回路(13,14)が形成されている面とは、反対側の面に取り付け、フレキシブルケーブル8を用いて周辺回路(13,14)との間の電気的接続をなす構成を採っている。

【0005】

あるいは、図13に示すように、TFTにより形成された一部の周辺回路(例えば水平ドライバ14、垂直ドライバ13など)が形成された透明絶縁基板16の同一面に、残りの半導体チップで構成した周辺回路(例えばタイミングコントローラ23、基準電圧発生回路24、およびDC−DCコンバータ25など)、すなわちICチップ(23〜25)を取り付け、周辺回路(13,14)との間の電気的接続をなす構成を採っている。

【0006】

【発明が解決しようとする課題】

しかしながら、図12に示す液晶表示装置では、図12(b)に示すように、少なくともICチップ(23〜25)およびフレキシブルケーブル8の厚みta(例えば、1mm程度)の分だけ液晶表示装置全体の厚みtbが厚くなってしまう。

従って、当該液晶表示装置を表示部として用いる機器の厚みも厚くなってしまう。特に、携帯端末、例えば携帯電話機では、装置本体の薄型化が進められており、この携帯電話機の表示部として用いられる液晶表示装置の厚さtbが厚いと、携帯電話機本体の薄型化の妨げとなる。

【0007】

また、図13に示す液晶表示装置では、TFTにより形成された一部の周辺回路(13,14)と、残りのICチップ(23〜25)の合算された面積が、周辺部(額縁)の面積となり、コンパクト化が損なわれるという不利益がある。また、液晶表示装置に占める有効表示面積(液晶表示部)の割合が小さくなってしまうという不利益もある。

【0008】

本発明は上記の事情に鑑みてなされたものであり、従って、本発明は、液晶表示装置の薄型化、小面積化、狭額縁化を実現できる液晶表示装置およびこれを用いた携帯端末を提供することを目的とする。

【0009】

【課題を解決するための手段】

上記の目的を達成するため、本発明の液晶表示装置は、複数の画素が行列状に配置されており、スイッチング素子として薄膜トランジスタを有する画素部が形成された第1の基板と、前記第1の基板に対向して配置された第2の基板と、前記第1の基板と前記第2の基板との間に保持された液晶組成物を有する液晶表示装置であって、前記画素部に対して画素信号を書き込むための周辺回路のうち少なくとも一部の周辺回路が、前記第1の基板上に薄膜トランジスタで構成され、前記周辺回路のうち残りの部分の周辺回路が、半導体チップで構成されており、前記半導体チップの少なくとも一部が、前記薄膜トランジスタで構成された前記周辺回路領域と重なるように、前記半導体チップが前記第1の基板上に配置されている。

そして、この液晶表示装置は、携帯電話機などの携帯端末において、その表示部として用いられる。

【0010】

例えば、前記周辺回路として、前記画素部に画素信号を書き込むために前記画素部に接続されたマトリクス配線に接続されている駆動部が薄膜トランジスタで構成されている。

また、前記駆動部のうち、水平あるいは垂直方向の走査を行うシフトレジスタ回路が半導体チップで構成されていてもよい。

【0011】

前記周辺回路として、タイミング波形を制御するタイミングコントローラ、あるいは、基準電圧を出力する基準電圧発生部、あるいは入力電圧よりも高い電圧を2種類以上発生し他の周辺回路に電源を与えるDC−DCコンバータのいずれかが前記半導体チップで構成されている。

【0012】

前記半導体チップの少なくとも一部が、COG法によって前記薄膜トランジスタで構成された前記周辺回路領域と重なるように、前記半導体チップが前記第1の基板上に実装されており、前記薄膜トランジスタで構成された前記周辺回路の周辺部分に、前記COG法によって前記半導体チップを接続するための接続部が形成されている。

【0013】

例えば、前記周辺回路として、低速駆動する一部の周辺回路を前記薄膜トランジスタで構成し、前記一部の周辺回路よりも高速駆動する周辺回路を前記半導体チップで構成する。

【0014】

上記の本発明の液晶表示装置によれば、例えば第1の基板上に形成された薄膜トランジスタで構成される一部の周辺回路領域に重なるように、半導体チップで構成される残りの周辺回路の少なくとも一部を第1の基板上に配置することで、各周辺回路を並列的に第1の基板上に配置するのと比較して、液晶表示装置の額縁部分の削減を図ることができる。

また、半導体チップの厚さが液晶表示装置全体の厚さに比して、小さくすることで、液晶表示装置の厚さが半導体チップの厚さに依存することなく、液晶表示装置の薄型化を図ることができる。

従って、液晶表示装置全体の狭額縁化および薄型化、ひいてはこれを表示部として用いる携帯端末の狭額縁化および薄型化を図ることが可能となる。

【0015】

【発明の実施の形態】

以下に、本発明の実施の形態について、図面を参照して説明する。

【0016】

第1実施形態

本実施形態は、アナログ点順次駆動方式のアクティブマトリクス型液晶表示装置に本発明を適用したものである。

図1(a)は本実施形態の液晶表示装置の各回路部の概略配置図であり、図1(b)は図1(a)におけるB−B線の断面図である。

また、図2は、本実施形態の液晶表示装置を構成する各回路部の電気的接続関係を表した概略構成図である。

【0017】

図1(a)および図2に示すように、本実施形態に係るアクティブマトリクス型液晶表示装置では、画素11が行列状に多数配列されてなる液晶表示部12、液晶表示部12の各画素11を行単位で順次選択する垂直ドライバ13、行単位で選択された各画素11に画素信号を書き込む水平ドライバ14および当該垂直および水平ドライバ(13,14)をコントロールする制御部15が透明絶縁基板16上に実装された構成となっている。

【0018】

透明絶縁基板16上には、液晶表示部12において、m行分のゲートライン(垂直選択ライン)17−1〜17−mと、n列分の信号ライン(ソースライン)18−1〜18−nとがマトリクス状に配線されるとともに、所定の間隔をもって対向配置された他方の透明絶縁基板62との間に液晶層63が保持された構造となっている。そして、ゲートライン(17−1〜17−m)と信号ライン(18−1〜18−n)との各交差部分に画素11が配されている。

【0019】

画素11の各々は、ゲート電極がゲートライン(17−1〜17−m)に接続され、ソース電極が信号ライン(18−1〜18−n)に接続されたスイッチング素子であるポリシリコンTFT(Thin Film Transistor;薄膜トランジスタ)19と、このTFT19のドレイン電極に画素電極が接続された液晶セル(液晶容量)20と、TFT19のドレイン電極に一方の電極が接続された補助容量21とから構成されている。

【0020】

上記の画素構造において、液晶セル20の対向電極は、補助容量21の他方の電極と共に、コモン線22に接続されている。

コモン線22には、所定の直流電圧がコモン電圧VCOMとして与えられる。

【0021】

液晶表示部12のスイッチング素子としてのトランジスタおよび駆動部(垂直ドライバ13、水平ドライバ14)を構成するトランジスタとして用いられるポリシリコンTFTには、ゲート電極がゲート絶縁膜の下に配置されるボトムゲート構造のものと、ゲート電極がゲート絶縁膜の上に配置されるトップゲート構造のものとがある。

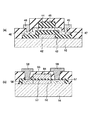

図3(a)にボトムゲート構造のポリシリコンTFT、(b)にトップゲート構造のポリシリコンTFTの断面図を示す。

【0022】

図3(a)に示すボトムゲート構造のTFTでは、透明絶縁基板(ガラス基板)16の上にゲート電極42が形成され、当該ゲ−ト電極42の上にゲート絶縁膜43を介してポリシリコン(Poly−Si)層44が形成され、さらに、当該ポリシリコン層44を被覆して層間絶縁膜45が形成されている。

また、ゲ−ト電極42の側方のゲート絶縁膜43上には、n+ 拡散層からなるソース領域46およびドレイン領域47が形成され、当該ソース・ドレイン領域(46,47)にはソース電極48およびドレイン電極49がそれぞれ接続されている。

【0023】

図3(b)に示すトップゲート構造のTFTでは、透明絶縁基板(ガラス基板)16の上にポリシリコン層52が形成され、当該ポリシリコン層52の上にゲート絶縁膜53を介してゲ−ト電極54が形成され、さらにゲ−ト電極54を被覆して層間絶縁膜55が形成されている。

また、ポリシリコン層52の側方の透明絶縁基板16上には、n+ 拡散層からなるソース領域56およびドレイン領域57が形成され、当該ソース・ドレイン領域(56,57)にはソース電極58およびドレイン電極59がそれぞれ接続されている。

【0024】

制御部15において、タイミングコントローラ(TC)23には、例えば、不図示の外部の電源部から電源電圧VDDが、不図示の外部のCPUからデジタル画像データdataが、不図示の外部のクロック発生器からクロックCLKがそれぞれ不図示のTCP(Tape Carrier Package) を通して入力される。

【0025】

タイミングコントローラ23は、タイミング制御しつつ、垂直スタートパルスVST、垂直クロックVCKなどのクロック信号および各種のコントロール信号を垂直ドライバ13に、水平スタートパルスHST、水平クロックHCKなどのクロック信号、各種のコントロール信号およびデジタル画像データdataを水平ドライバ14にそれぞれ供給する。

【0026】

基準電圧発生回路(REF)24は、互いに電圧値の異なる複数の基準電圧を発生し、これら複数の基準電圧を水平ドライバ14の後述する基準電圧選択型D/Aコンバータ37に対してその基準電圧として与える。

【0027】

DC−DCコンバータ(DDC)25は、低い電圧の直流電圧(低電圧)を2種類以上の高い直流電圧(高電圧)に変換して垂直ドライバ13、水平ドライバ14、基準電圧発生回路24などの各回路部に与える。

【0028】

本実施形態では、高速駆動する回路部分、もしくは特性バラツキが小さい回路部分として、例えば、上記の制御部15のタイミングコントローラ23、基準電圧発生回路24およびDC−DCコンバータ25が、単結晶シリコンのチップで形成(IC化)されている。

そして、このシリコンIC(23〜25)は、図1(b)に示すように、垂直ドライバ13上に、例えばCOG(Chip on Glass)法によって実装されている。この単結晶シリコンによって形成されたシリコンIC(23〜25)は、100MHzでも駆動することが可能である。

【0029】

一方、低速駆動で特性バラツキが大きい回路部分として、例えば垂直ドライバ13および水平ドライバ14に関しては、上述したようにポリシリコンTFTを用いて形成する。

【0030】

垂直ドライバ13は、例えば図4に示すように、シフトレジスタ31、レベルシフタ32およびゲートバッファ33を有する構成となっている。

【0031】

シフトレジスタ31は、垂直スタートパルスVSTが入力されると、当該垂直スタートパルスVSTを垂直クロックVCKに同期して、順次転送することによって各転送段からシフトパルスとして順次出力する。

レベルシフタ32は、シフトレジスタ31の各転送段から出力されるシフトパルスを昇圧してゲートバッファ33に供給する。

ゲートバッファ33は、レベルシフタ32で昇圧されたシフトパルスを垂直走査パルスとして液晶表示部12のゲートライン(17−1〜17−m)に順次印加し、液晶表示部12の各画素11を行単位で選択駆動することによって垂直走査を行う。

【0032】

水平ドライバ14は、例えば図5に示すように、シフトレジスタ34、レベルシフタ35、データラッチ回路36、D/Aコンバータ37およびバッファ38を有する構成となっている。

【0033】

シフトレジスタ34は、水平スタートパルスHSTが入力されると、この水平スタートパルスHSTを水平クロックHCKに同期して順次転送することによって、各転送段からシフトパルスとして順次出力し、水平走査を行う。

レベルシフタ35は、シフトレジスタ34の各転送段から出力されるシフトパルスを昇圧して、データラッチ回路36に供給する。

データラッチ回路36は、レベルシフタ35を通してシフトレジスタ34から与えられるシフトパルスに応答して、入力される所定ビットのデジタル画像データdataを順次ラッチする。

D/Aコンバータ37は、例えば基準電圧選択型の構成をとり、データラッチ回路36にラッチされたデジタル画像データをアナログ画像信号に変換し、バッファ38を通して液晶表示部12の信号ライン(18−1〜18−n)に与える。

【0034】

図6(a)にシリコンIC(23〜25)で形成された制御部15と、ポリシリコンTFTで形成された垂直ドライバ13の接続方法の説明図を示す。また、図6(b)に、接続部分における断面図を示す。

【0035】

図6(a)に示すように、シリコンIC(23〜25)の配置を可能にするために、垂直ドライバ13には、駆動回路領域13aが形成されており、当該駆動回路領域13aが複数のパッド13bに接続された構成となっている。

一方、シリコンIC(23〜25)側も、図6(a)に示すように、シリコン基板250上に制御回路領域251が形成され、当該制御回路領域251が複数の不図示のパッドを介してバンプ252に電気的に接続された構成となっている。なお、図6(a)において、制御回路領域251およびバンプ252は、紙面上、裏面に形成されている。

【0036】

そして、図6(b)に示すように、当該垂直ドライバ13の駆動回路領域13aとシリコンIC(23〜25)側の制御回路領域251が対向するようにして、シリコンIC(23〜25)側のバンプ252を導電粒子材66を介して、垂直ドライバ13側のパッド13b上に実装することにより、制御回路と駆動回路との電気的接続が達成される。

また、パッド13bは、透明絶縁基板16上に設けられた不図示のアルミ配線に接続されており、当該アルミ配線によって、図2に示すようなICチップ(23〜25)間の電気的接続、およびICチップ(23〜25)と水平・垂直ドライバ(13,14)との電気的接続を達成している。

なお、図6(b)には、駆動回路領域13aが、相補型のTFTにより構成されている例を示した。従って、一方のTFTのn+ 拡散層からなるドレイン領域47と、他方のTFTのp+ 拡散層からなるソース領域46a(あるいはドレイン領域47a)とが、例えばアルミ配線60によって電気的に接続されている。また、当該相補型のTFTを被覆してパッシベーション膜61が形成されている。

【0037】

上記構成の液晶表示装置の動作について説明する。

例えば、外部のCPUからタイミングコントローラ23に画像データdataが入力されて、画像データdataが水平ドライバ14のシフトレジスタ34に供給される。

また、基準電圧発生回路24において、水平ドライバ14のD/Aコンバータ37で用いられる複数の基準電圧が発生され、D/Aコンバータ37の不図示の基準電圧線に供給される。

【0038】

そして、水平クロックHCKおよび水平スタートパルスHSTが水平ドライバ14のシフトレジスタ34に入力される。

シフトレジスタ34においては、水平スタートパルスHSTが入力されると、この水平スタートパルスHSTが水平クロックHCKに同期して順次転送され、各転送段からシフトパルスとして順次レベルシフタ35に出力される。

レベルシフタ35において、シフトレジスタの各転送段から出力されるシフトパルスが昇圧され、データラッチ回路36に供給される。

データラッチ回路36においては、レベルシフタ35を通してシフトレジスタ34から与えられるシフトパルスに応答して、タイミングコントローラ23から入力される所定ビットのデジタル画像データdataを順次ラッチする。

【0039】

データラッチ回路36にラッチされた画像データは、基準電圧選択型のD/Aコンバータ37に供給される。

D/Aコンバータ37においては、対応する基準電圧が選択され、デジタル画像データがアナログ画像信号に変換され、バッファ38を通して液晶表示部12の信号ライン(18−1〜18−n)に、アナログ信号として供給される。

【0040】

また、垂直ドライバ13において、垂直スタートパルスVSTがシフトレジスタ31に入力されると、この垂直スタートパルスVSTが垂直クロックVCKに同期して順次転送され、各転送段からシフトパルスとして順次レベルシフタ32に出力される。

次に、レベルシフタ32において、シフトレジスタ31の各転送段から出力されるシフトパルスが昇圧され、ゲートバッファ33に供給される。

そして、ゲートバッファ33において、レベルシフタ32で昇圧されたシフトパルスが垂直走査パルスとして、ゲートライン(17−1〜17−m)に順次印加され、液晶表示部12の各画素11が行単位で選択駆動される。

これにより、画像データがn個の画素に対して並列に書き込まれることになる。

【0041】

本実施形態に係る液晶表示装置によれば、低速駆動で特性バラツキが大きい回路部分として、例えば垂直ドライバ13および水平ドライバ14に関してポリシリコンTFTを用いて形成する一方、高速駆動する回路部分、もしくは特性バラツキが小さい回路部分として、例えば制御部15のタイミングコントローラ23、基準電圧発生回路24、およびDC−DCコンバータ25に関しては単結晶シリコンでIC化し、当該IC化した各回路部分を垂直ドライバ13などの駆動回路部分上に例えばCOG法によって、実装することにより、液晶表示装置の額縁部分の削減を図ることができる。

【0042】

また、図1(b)に示すように、垂直ドライバ13とICチップ(23〜25)を合わせた厚さt1が、対向側の透明絶縁基板62および液晶層63を合わせた厚さt3以下になるようにすることで、液晶表示装置全体の厚さt2がICチップ(23〜25)の厚さに依存することがないため、液晶表示装置の薄型化が図れる。

すなわち、透明絶縁基板16、透明絶縁基板62および液晶層63のトータルの厚さt2が液晶表示装置自体の厚さとなる。

【0043】

さらに、周辺回路をIC化し、このICチップを透明絶縁基板16上に実装することにより、透明絶縁基板16上における外部回路との電気的に接続する箇所を少なくすることができるため、液晶表示装置の機械振動などに対する信頼性を向上することができるとともに、製造工程での電気的な接続不良の発生を抑止することができる。

【0044】

なお、ICチップ(23〜25)を透明絶縁基板16上に実装した場合、ICチップ自体については、IC作製時に保護層がシリコンICに形成されるため、信頼性の面で問題になることはない。

【0045】

第2実施形態

本実施形態は、時分割駆動方式(セレクタ方式)のアクティブマトリクス型液晶表示装置に本発明を適用したものである。

図7は、本発明が適用された時分割駆動方式のアクティブマトリクス型液晶表示装置の各回路部の概略配置図である。

図8は、図7に示す液晶表示装置の各回路部の電気的接続関係を表した概略構成図である。

【0046】

図7および図8において、本実施形態に係る液晶表示装置は、画素11が行列状に多数配列されてなる液晶表示部12、液晶表示部12の各画素11を行単位で順次選択する垂直ドライバ13、行単位で選択された各画素11に画素信号を書き込む水平ドライバ74、時分割駆動のための時分割スイッチ部75、垂直、水平ドライバ(13,74)や時分割スイッチ部75をコントロールする制御部15が透明絶縁基板16上に実装された構成となっている。

【0047】

画素11の各々は、ゲート電極がゲートライン(17−1〜17−m)に接続され、ソース電極が信号ライン(18−1〜18−n)に接続されたポリシリコンTFT19と、当該TFT19のドレイン電極に画素電極が接続された液晶セル20と、TFT19のドレイン電極に一方の電極が接続された補助容量21とから構成されている。

上記構成の画素11の各々において、液晶セル20の対向電極は、補助容量21の他方の電極と共にコモン線22に接続されている。コモン線22には、所定の直流電圧がコモン電圧VCOMとして与えられる。

【0048】

垂直ドライバ13、水平ドライバ74および時分割スイッチ部75を制御する制御部15は、タイミングコントローラ(TC)23、基準電圧発生回路(REF)24、DC−DCコンバータ(DDC)25などを有する。

タイミングコントローラ23には、例えば、不図示の外部の電源部から電源電圧VDDが、不図示の外部のCPUからデジタル画像データdataが、不図示の外部のクロック発生器からクロックCLKがそれぞれ不図示のTCPを通して入力される。

【0049】

タイミングコントローラ23は、タイミング制御しつつ、垂直スタートパルスVST、垂直クロックVCKなどのクロック信号および各種のコントロール信号を垂直ドライバに、水平スタートパルスHST、水平クロックHCKなどのクロック信号、各種のコントロール信号およびデジタル画像データdataを水平ドライバ74に、ゲート選択信号(S1〜S3,XS1〜XS3)を時分割スイッチ部75にそれぞれ供給する。

【0050】

基準電圧発生回路24は、互いに電圧値の異なる複数の基準電圧を発生し、これら複数の基準電圧を水平ドライバ74の後述する基準電圧選択型D/Aコンバータ88に対してその基準電圧として与える。

DC−DCコンバータ25は、低い電圧の直流電圧(低電圧)を2種類以上の高い直流電圧(高電圧)に変換して垂直ドライバ13、水平ドライバ74、基準電圧発生回路24などの各回路部に与える。

【0051】

上記構成の時分割駆動方式のアクティブマトリクス型液晶表示装置において、垂直ドライバ13を構成するトランジスタ、時分割スイッチ部75を構成する各アナログスイッチは、TFT、特に液晶表示部12のスイッチング素子であるトランジスタ19と同じポリシリコンTFTにより、液晶表示部12と同じ透明絶縁基板16上に形成されている。

【0052】

一方、水平ドライバ74、制御部15のタイミングコントローラ23、基準電圧発生回路24、DC−DCコンバータ25は、単結晶シリコンによってIC化されている。

そして、当該シリコンICで形成された水平ドライバ74は時分割選択スイッチ部75上に、シリコンICで形成された基準電圧発生回路24、およびDC−DCコンバータ25は、垂直ドライバ13上に、例えばCOG法によって実装されている。

【0053】

ここで、時分割駆動法について、本実施形態の液晶表示の動作とともに説明する。

時分割駆動法とは、液晶表示部12の互いに隣り合う複数本の信号ラインを1単位(ブロック)として分割し、この1分割ブロック内の複数本の信号ラインに与える信号電圧を時系列で水平ドライバ74の各出力端子から出力する一方、複数本の信号ラインを1単位として時分割スイッチ部75を設け、この時分割スイッチ部75によって水平ドライバ74から出力される時系列の信号電圧を時分割でサンプリングして複数本の信号ラインに順次与える駆動方法である。

【0054】

この時分割駆動法を実現するために、水平ドライバ74は、複数本の信号ラインを1単位とし、これら複数本の信号ラインに与える信号電圧を時系列で出力する構成となっている。

図9に、上記の水平ドライバ74の構成例を示す。

【0055】

図9に示す水平ドライバ74は、シフトレジスタ84、サンプリングスイッチ群85、レベルシフタ86、データラッチ回路87およびD/Aコンバータ88を有し、本実施形態では、例えば5ビットのディジタル画像データ(data1〜data5)や電源電圧Vdd、Vssをシフトレジスタ84のシフト方向における両側から取り込む構成となっている。

【0056】

上記構成の水平ドライバ74において、シフトレジスタ84は、水平スタートパルスHSTが入力されると、この水平スタートパルスHSTを水平クロックHCKに同期して順次転送することによって各転送段からシフトパルスとして順次出力し、水平走査を行う。

サンプリングスイッチ群85におけるサンプリングスイッチの各々は、シフトレジスタ84から順次出力されるシフトパルス(サンプリングパルス)に応答して、入力されるデジタル画像データ(data1〜data5)を順次サンプリングする。

【0057】

レベルシフタ86は、サンプリングスイッチ群85でサンプリングされた例えば5Vのデジタルデータを液晶駆動電圧のデジタルデータに昇圧する。

データラッチ回路87は、レベルシフタ86で昇圧されたデジタルデータを1H分蓄積するメモリである。

D/Aコンバータ88は、例えば基準電圧選択型の構成をとり、データラッチ回路87から出力される1H分のデジタル画像データをアナログ画像信号に変換して出力する。

【0058】

そして、水平ドライバ74として、いわゆるカラム反転駆動方式のものを用いる。

当該水平ドライバ74は、カラム反転駆動を実現するために、各出力端子の奇数、偶数ごとに電位が反転する信号電圧を出力し、かつその信号電圧の極性を1フィールドごとに反転する。ここで、カラム反転駆動方式とは、水平方向に隣接する画素間では同極性となり、しかもこの画素極性の状態を1フィールドごとに反転させる駆動方式である。

【0059】

一方、時分割スイッチ部75は、水平ドライバ74から出力される時系列の信号電圧を時分割でサンプリングするアナログスイッチ(トランスミッションスイッチ)によって構成されている。

図10に、時分割スイッチ部75の具体的な構成例を示す。

図10に示す時分割スイッチ部75は、水平ドライバ74の各出力に対して1個ずつ設けられるものである。また、ここでは、R(赤)、G(緑)、B(青)に対応して3時分割駆動を行う場合を例にとって示している。

【0060】

この時分割スイッチ部75は、pチャネルMOSトランジスタおよびnチャネルMOSトランジスタが並列に接続されてなるCMOS構成のアナログスイッチ(75−1,75−2,75−3)によって構成されている。

なお、本実施形態では、アナログスイッチ(75−1,75−2,75−3)として、CMOS構成のものを用いるとしたが、pチャネルMOSトランジスタあるいはnチャネルMOSトランジスタ構成のものを用いることも可能である。

【0061】

上記の時分割スイッチ部75において、3個のアナログスイッチ(75−1,75−2,75−3)の各入力端が共通に接続され、各出力端が3本の信号ライン(18−1,18−2,18−3)の各一端にそれぞれ接続されている。

そして、これらのアナログスイッチ(75−1,75−2,75−3)の各入力端には、水平ドライバ74から時系列で出力される信号電位が与えられる。

【0062】

また、1個のアナログスイッチにつき2本ずつ、合計6本の制御ライン(89−1〜89−6)が配線されている。そして、アナログスイッチ75−1の2つの制御入力端(すなわち、CMOSトランジスタの各ゲート)が制御ライン(89−1,89−2)に、アナログスイッチ75−2の2つの制御入力端が制御ライン(89−3,89−4)に、アナログスイッチ75−3の2つの制御入力端が制御ライン(89−5,89−6)にそれぞれ接続されている。

【0063】

6本の制御ライン(89−1〜89−6)に対して、3個のアナログスイッチ(75−1,75−2,75−3)を順に選択するためのゲート選択信号(S1〜S3,XS1〜XS3)がタイミングコントローラ(TC)23(図8参照)から与えられる。ここで、ゲート選択信号(XS1〜XS3)は、ゲート選択信号(S1〜S3)の反転信号である。

【0064】

ゲート選択信号(S1〜S3,XS1〜XS3)は、水平ドライバ74から出力される時系列の信号電位に同期して、3個のアナログスイッチ(75−1,75−2,75−3)を順次オンさせる。

これにより、アナログスイッチ(75−1,75−2,75−3)は、水平ドライバ74から出力される時系列の信号電位を、1H期間に3時分割でサンプリングしつつ、対応する信号ライン(18−1,18−2,18−3)にそれぞれ供給する。

【0065】

本実施形態に係る液晶表示装置では、低速駆動で特性バラツキが大きい回路部分として、例えば垂直ドライバ13および時分割スイッチ部75に関してポリシリコンTFTを用いて形成する一方、高速駆動する回路部分、もしくは特性バラツキが小さい回路部分として、例えば水平ドライバ74や、制御部15のタイミングコントローラ23、基準電圧発生回路24、およびDC−DCコンバータ25に関しては単結晶シリコンでIC化し、当該IC化した各回路部分を垂直ドライバ13や時分割スイッチ部75上に例えばCOG法によって、実装することにより、第1実施形態と同様の効果を得ることができる。

【0066】

なお、本発明に係る液晶表示装置は、パーソナルコンピュータ、ワードプロセッサ等のOA機器やテレビジョン受像機などのディスプレイとして用いられる他、特に、装置本体の薄型化が進められている携帯電話器やPDA(Personal Digital Asistants)などの携帯端末の表示部として用いるのに好適なものである。

【0067】

図11は、本発明が適用される携帯端末、例えばPDAの構成の概略を示す斜視図である。

【0068】

本例に係るPDAは、装置筐体91の前面側に、表示部92、スピーカ部93、操作部94および電源部95などが配置された構成となっている。

なお、図11に示すPDAでは、例えば、表示部92上から、ペン96などにより入力可能となっている。

かかる構成のPDAの表示部92において、本発明の液晶表示装置が使用される。

【0069】

このように、PDAや携帯電話機などの携帯端末において、本発明に係る液晶表示装置を表示部92として用いることにより、当該液晶表示装置は、薄型化および狭額縁化を達成できる構成となっていることから、携帯端末の装置本体の薄型化、狭額縁化に大きく寄与できる利点がある。

【0070】

本発明は、上記の実施形態の説明に限定されない。

例えば、本実施形態では、CPU、画像データを格納するメモリあるいはクロック発生器を液晶表示部の外部に設けるとしたが、それらの少なくとも1つを制御部の一部として液晶表示部上に実装することも可能である。

また、本実施形態では、垂直ドライバ上にIC化された制御部をCOG法によって実装する例を示したが、これに限られるものではなく、例えば、TAB(Tape Automated bonding) 法などにより実装することも、また、水平ドライバ上に実装することも可能である。

その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0071】

【発明の効果】

以上説明したように、本発明によれば、液晶表示装置の薄型化、小面積化、狭額縁化を実現でき、ひいてはこれを表示部として用いる携帯端末の薄型化、小面積化、狭額縁化を実現できる。

【図面の簡単な説明】

【図1】図1(a)は第1実施形態の液晶表示装置の各回路部の概略配置図であり、図1(b)は図1(a)におけるB−B線の断面図である。

【図2】図2は、第1実施形態の液晶表示装置を構成する各回路部の電気的接続関係を表した概略構成図である。

【図3】図3は、ポリシリコンTFTの断面構造を示す断面図であり、図3(a)は、ボトムゲート構造のポリシリコンTFT、(b)はトップゲート構造のポリシリコンTFTを示したものである。

【図4】図4は、アナログ点順次駆動方式のアクティブマトリクス型液晶表示装置における垂直ドライバの構成の一例を示すブロック図である。

【図5】図5は、アナログ点順次駆動方式のアクティブマトリクス型液晶表示装置における水平ドライバの構成の一例を示すブロック図である。

【図6】図6(a)は、シリコンICで形成された制御部と、ポリシリコンTFTで形成された垂直ドライバの接続方法の説明図であり、図6(b)は、接続部分おける断面図である。

【図7】図7は、第2実施形態における液晶表示装置の各回路部の概略配置図である。

【図8】図8は、図7に示す液晶表示装置の各回路部の電気的接続関係を表した概略構成図である。

【図9】図9は、第2実施形態の時分割駆動方式のアクティブマトリクス型液晶表示装置における水平ドライバの構成の一例を示すブロック図である。

【図10】図10は、時分割スイッチ部の構成の一例を示す回路図である。

【図11】図11は、本発明が適用される携帯端末として、例えばPDAの構成の概略を示す斜視図である。

【図12】図12(a)は、従来例1の液晶表示装置の概略構成図、図12(b)は図12(a)におけるA−A線の断面図を示したものである。

【図13】図13は、従来例2の液晶表示装置の概略構成図を示したものである。

【符号の説明】

11…画素、12…液晶表示部、13…垂直ドライバ、14,74…水平ドライバ、15…制御部、16…透明絶縁基板、19…ポリシリコンTFT、20…液晶セル、23…タイミングコントローラ、24…基準電圧発生回路、25…DC−DCコンバータ。

Claims (10)

- 複数の画素が行列状に配置されており、スイッチング素子として薄膜トランジスタを有する画素部が形成された第1の基板と、前記第1の基板に対向して配置された第2の基板と、前記第1の基板と前記第2の基板との間に保持された液晶組成物を有する液晶表示装置であって、

前記画素部に対して画素信号を書き込むための周辺回路のうち少なくとも一部の周辺回路が、前記第1の基板上に薄膜トランジスタで構成され、

前記周辺回路のうち残りの部分の周辺回路が、半導体チップで構成されており、

前記半導体チップの少なくとも一部が、前記薄膜トランジスタで構成された前記周辺回路領域と重なるように、前記半導体チップが前記第1の基板上に配置されている

液晶表示装置。 - 前記周辺回路として、前記画素部に画素信号を書き込むために前記画素部に接続されたマトリクス配線に接続されている駆動部が薄膜トランジスタで構成されている

請求項1記載の液晶表示装置。 - 前記駆動部のうち、水平あるいは垂直方向の走査を行うシフトレジスタ回路が半導体チップで構成されている

請求項2記載の液晶表示装置。 - 前記周辺回路として、タイミング波形を制御するタイミングコントローラが前記半導体チップで構成されている

請求項1記載の液晶表示装置。 - 前記周辺回路として、基準電圧を出力する基準電圧発生部が前記半導体チップで構成されている

請求項1記載の液晶表示装置。 - 前記周辺回路として、入力電圧よりも高い電圧を2種類以上発生し、他の周辺回路に電源を与えるDC−DCコンバータが前記半導体チップで構成されている

請求項1記載の液晶表示装置。 - 前記半導体チップの少なくとも一部が、COG法によって前記薄膜トランジスタで構成された前記周辺回路領域と重なるように、前記半導体チップが前記第1の基板上に実装されている

請求項1記載の液晶表示装置。 - 前記薄膜トランジスタで構成された前記周辺回路の周辺部分に、前記COG法によって前記半導体チップを接続するための接続部が形成されている

請求項7記載の液晶表示装置。 - 前記周辺回路として、低速駆動する一部の周辺回路を前記薄膜トランジスタで構成し、前記一部の周辺回路よりも高速駆動する周辺回路を前記半導体チップで構成する

請求項1記載の液晶表示装置。 - 複数の画素が行列状に配置されており、スイッチング素子として薄膜トランジスタを有する画素部が形成された第1の基板と、前記第1の基板に対向して配置された第2の基板と、前記第1の基板と前記第2の基板との間に保持された液晶組成物を有し、

前記画素部に対して画素信号を書き込むための周辺回路のうち少なくとも一部の周辺回路が、前記第1の基板上に薄膜トランジスタで構成され、

前記周辺回路のうち残りの部分の周辺回路が、半導体チップで構成されており、

前記半導体チップの少なくとも一部が、前記薄膜トランジスタで構成された前記周辺回路領域と重なるように、前記半導体チップが前記第1の基板上に配置されている液晶表示装置を表示部として有する

携帯端末。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000254335A JP4352598B2 (ja) | 2000-08-24 | 2000-08-24 | 液晶表示装置および携帯端末 |

| PCT/JP2001/007204 WO2002017007A1 (fr) | 2000-08-24 | 2001-08-23 | Afficheur à cristaux liquides et appareil électronique pourvu de cet afficheur |

| CNB018032737A CN1174280C (zh) | 2000-08-24 | 2001-08-23 | 液晶显示装置及使用它的电子装置 |

| EP01958417A EP1243965A4 (en) | 2000-08-24 | 2001-08-23 | LIQUID CRYSTAL DISPLAY AND ELECTRONIC APPARATUS PROVIDED WITH SAID DISPLAY |

| US10/111,207 US6897841B2 (en) | 2000-08-24 | 2001-08-23 | Liquid crystal display device and electronic apparatus comprising it |

| KR1020027004833A KR100829066B1 (ko) | 2000-08-24 | 2001-08-23 | 액정 표시 장치 및 이것을 사용한 전자 장치 |

| NO20021807A NO20021807L (no) | 2000-08-24 | 2002-04-17 | Flytende krystallskjerminnretning og elektronisk innretning som bruker den samme |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000254335A JP4352598B2 (ja) | 2000-08-24 | 2000-08-24 | 液晶表示装置および携帯端末 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002072233A JP2002072233A (ja) | 2002-03-12 |

| JP2002072233A5 JP2002072233A5 (ja) | 2007-05-24 |

| JP4352598B2 true JP4352598B2 (ja) | 2009-10-28 |

Family

ID=18743300

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000254335A Expired - Fee Related JP4352598B2 (ja) | 2000-08-24 | 2000-08-24 | 液晶表示装置および携帯端末 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6897841B2 (ja) |

| EP (1) | EP1243965A4 (ja) |

| JP (1) | JP4352598B2 (ja) |

| KR (1) | KR100829066B1 (ja) |

| CN (1) | CN1174280C (ja) |

| NO (1) | NO20021807L (ja) |

| WO (1) | WO2002017007A1 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2001073743A1 (fr) * | 2000-03-28 | 2001-10-04 | Seiko Epson Corporation | Afficheur a cristaux liquides, procede et dispositif de commande d'un afficheur a cristaux liquides, dispositif electronique |

| JP2004247373A (ja) * | 2003-02-12 | 2004-09-02 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP4393812B2 (ja) * | 2003-07-18 | 2010-01-06 | 株式会社半導体エネルギー研究所 | 表示装置及び電子機器 |

| JP4480968B2 (ja) * | 2003-07-18 | 2010-06-16 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP4424946B2 (ja) * | 2003-09-03 | 2010-03-03 | 三菱電機株式会社 | 表示装置 |

| JP2005300920A (ja) * | 2004-04-12 | 2005-10-27 | Nec Corp | 表示装置及び液晶表示装置 |

| KR100675636B1 (ko) * | 2004-05-31 | 2007-02-02 | 엘지.필립스 엘시디 주식회사 | Goldd구조 및 ldd구조의 tft를 동시에포함하는 구동회로부 일체형 액정표시장치 |

| KR101082909B1 (ko) * | 2005-02-05 | 2011-11-11 | 삼성전자주식회사 | 게이트 구동 방법 및 그 장치와 이를 갖는 표시장치 |

| US20060232579A1 (en) * | 2005-04-14 | 2006-10-19 | Himax Technologies, Inc. | WOA panel architecture |

| TWI485681B (zh) * | 2005-08-12 | 2015-05-21 | Semiconductor Energy Lab | 顯示裝置 |

| CN100437236C (zh) * | 2005-10-28 | 2008-11-26 | 友达光电股份有限公司 | 液晶显示面板与其上的线路布局 |

| JP5084134B2 (ja) | 2005-11-21 | 2012-11-28 | 日本電気株式会社 | 表示装置及びこれらを用いた機器 |

| JP5057321B2 (ja) * | 2006-03-14 | 2012-10-24 | 株式会社ジャパンディスプレイウェスト | 表示装置の製造方法 |

| TWI361416B (en) * | 2007-03-23 | 2012-04-01 | Chimei Innolux Corp | Driving circuit board riving system and driving method for flat panel display apparatus |

| US9013672B2 (en) * | 2007-05-04 | 2015-04-21 | Asml Netherlands B.V. | Cleaning device, a lithographic apparatus and a lithographic apparatus cleaning method |

| JP5137690B2 (ja) * | 2008-05-27 | 2013-02-06 | 株式会社ジャパンディスプレイウェスト | 電気光学装置、およびこれを搭載した電子機器 |

| JP5222229B2 (ja) * | 2009-05-29 | 2013-06-26 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| KR101987094B1 (ko) | 2012-06-15 | 2019-10-01 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 제조 방법 |

| TWI469119B (zh) * | 2012-08-06 | 2015-01-11 | Au Optronics Corp | 顯示器及其閘極驅動器 |

| KR101989001B1 (ko) | 2012-09-07 | 2019-06-14 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN103941507B (zh) * | 2014-04-02 | 2017-01-11 | 上海天马微电子有限公司 | 一种阵列基板、显示面板及显示装置 |

| CN105976778B (zh) * | 2016-07-04 | 2019-01-11 | 深圳市华星光电技术有限公司 | 液晶显示面板的数据驱动系统 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5849601A (en) * | 1990-12-25 | 1998-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| JP2791422B2 (ja) | 1990-12-25 | 1998-08-27 | 株式会社 半導体エネルギー研究所 | 電気光学装置およびその作製方法 |

| JP2997737B2 (ja) * | 1990-12-25 | 2000-01-11 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US5479319A (en) * | 1992-12-30 | 1995-12-26 | Interconnect Systems, Inc. | Multi-level assemblies for interconnecting integrated circuits |

| WO1995009438A1 (en) * | 1993-09-30 | 1995-04-06 | Kopin Corporation | Three-dimensional processor using transferred thin film circuits |

| JPH07209672A (ja) * | 1993-12-03 | 1995-08-11 | Semiconductor Energy Lab Co Ltd | 非発光型ディスプレーを有する電子装置 |

| JP3778964B2 (ja) * | 1995-02-15 | 2006-05-24 | 株式会社半導体エネルギー研究所 | アクティブマトリクス表示装置 |

| TW520816U (en) * | 1995-04-24 | 2003-02-11 | Matsushita Electric Ind Co Ltd | Semiconductor device |

| JP3133248B2 (ja) * | 1996-01-27 | 2001-02-05 | 株式会社半導体エネルギー研究所 | 電気光学装置 |

| JPH1184425A (ja) * | 1997-09-05 | 1999-03-26 | Semiconductor Energy Lab Co Ltd | 電気光学装置 |

| JPH1165471A (ja) * | 1997-08-20 | 1999-03-05 | Semiconductor Energy Lab Co Ltd | 電気光学装置 |

| JP3436478B2 (ja) * | 1998-01-12 | 2003-08-11 | 株式会社日立製作所 | 液晶表示装置および計算機システム |

| JPH11352516A (ja) * | 1998-06-09 | 1999-12-24 | Matsushita Electric Ind Co Ltd | アクティブマトリックス型液晶表示パネル |

| JP2000267590A (ja) * | 1999-03-19 | 2000-09-29 | Sharp Corp | 画像表示装置 |

| JP2000276068A (ja) | 1999-03-26 | 2000-10-06 | Seiko Epson Corp | 表示装置及び電子機器 |

| JP3339456B2 (ja) * | 1999-03-26 | 2002-10-28 | 日本電気株式会社 | 液晶表示装置 |

| JP4783890B2 (ja) * | 2000-02-18 | 2011-09-28 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| JP4185678B2 (ja) * | 2001-06-08 | 2008-11-26 | 株式会社日立製作所 | 液晶表示装置 |

-

2000

- 2000-08-24 JP JP2000254335A patent/JP4352598B2/ja not_active Expired - Fee Related

-

2001

- 2001-08-23 EP EP01958417A patent/EP1243965A4/en not_active Withdrawn

- 2001-08-23 CN CNB018032737A patent/CN1174280C/zh not_active Expired - Fee Related

- 2001-08-23 US US10/111,207 patent/US6897841B2/en not_active Expired - Fee Related

- 2001-08-23 KR KR1020027004833A patent/KR100829066B1/ko not_active IP Right Cessation

- 2001-08-23 WO PCT/JP2001/007204 patent/WO2002017007A1/ja active Application Filing

-

2002

- 2002-04-17 NO NO20021807A patent/NO20021807L/no not_active Application Discontinuation

Also Published As

| Publication number | Publication date |

|---|---|

| WO2002017007A1 (fr) | 2002-02-28 |

| KR20020040879A (ko) | 2002-05-30 |

| KR100829066B1 (ko) | 2008-05-16 |

| EP1243965A4 (en) | 2005-06-22 |

| NO20021807D0 (no) | 2002-04-17 |

| JP2002072233A (ja) | 2002-03-12 |

| US6897841B2 (en) | 2005-05-24 |

| US20030057853A1 (en) | 2003-03-27 |

| CN1174280C (zh) | 2004-11-03 |

| NO20021807L (no) | 2002-04-17 |

| CN1394293A (zh) | 2003-01-29 |

| EP1243965A1 (en) | 2002-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4352598B2 (ja) | 液晶表示装置および携帯端末 | |

| EP3477626B1 (en) | Oled display panel and oled display device | |

| JP4649706B2 (ja) | 表示装置およびこれを用いた携帯端末 | |

| US7561150B2 (en) | Liquid crystal driving circuit and liquid crystal display device | |

| US9489879B2 (en) | Display device | |

| JP4102309B2 (ja) | 表示駆動制御システム | |

| WO2011104945A1 (ja) | 表示装置 | |

| US20080150859A1 (en) | Liquid crystal display device and method of driving the same | |

| US7151523B2 (en) | Bi-directional shift register and display device using same | |

| JP2008033297A (ja) | 液晶装置、および電子機器 | |

| JP2007094262A (ja) | 電気光学装置及び電子機器 | |

| JPH08234237A (ja) | 液晶表示装置 | |

| JP2002287653A (ja) | 表示装置およびその製造方法、ならびに携帯端末およびその製造方法 | |

| KR20020045539A (ko) | 액티브 매트릭스형 표시 장치 | |

| JP2000075840A (ja) | 液晶表示装置 | |

| WO2004107030A1 (ja) | 平面表示装置用アレイ基板 | |

| JP4877413B2 (ja) | 表示装置およびこれを用いた携帯端末 | |

| JP3730220B2 (ja) | 液晶表示装置 | |

| JPH10274762A (ja) | 駆動回路内蔵型液晶表示装置 | |

| KR20240104961A (ko) | GIP(Gate In Panel)회로 및 이를 포함하는 표시장치 | |

| JPH11311804A (ja) | 液晶表示装置 | |

| JP4062877B2 (ja) | アクティブマトリクス型表示装置およびこれを用いた携帯端末 | |

| US7986292B2 (en) | Liquid crystal display device employing an analog interface to which a gradation voltage is input from outside | |

| JP2005275430A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070112 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070327 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090421 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090609 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090707 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090720 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120807 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |