JP5011881B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5011881B2 JP5011881B2 JP2006219477A JP2006219477A JP5011881B2 JP 5011881 B2 JP5011881 B2 JP 5011881B2 JP 2006219477 A JP2006219477 A JP 2006219477A JP 2006219477 A JP2006219477 A JP 2006219477A JP 5011881 B2 JP5011881 B2 JP 5011881B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- type layer

- layer

- substrate

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

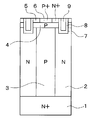

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0297—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the gate electrodes, e.g. to form trench gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/665—Vertical DMOS [VDMOS] FETs having edge termination structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/01—Manufacture or treatment

- H10D62/051—Forming charge compensation regions, e.g. superjunctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/109—Reduced surface field [RESURF] PN junction structures

- H10D62/111—Multiple RESURF structures, e.g. double RESURF or 3D-RESURF structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/017—Manufacturing their source or drain regions, e.g. silicided source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0195—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices the components including vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/101—Integrated devices comprising main components and built-in components, e.g. IGBT having built-in freewheel diode

- H10D84/141—VDMOS having built-in components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

- H10D62/116—Dielectric isolations, e.g. air gaps adjoining the input or output regions of field-effect devices, e.g. adjoining source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/977—Thinning or removal of substrate

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thyristors (AREA)

- Junction Field-Effect Transistors (AREA)

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006219477A JP5011881B2 (ja) | 2006-08-11 | 2006-08-11 | 半導体装置の製造方法 |

| US11/889,075 US7635622B2 (en) | 2006-08-11 | 2007-08-09 | Method for manufacturing a vertical transistor that includes a super junction structure |

| US12/614,632 US7858475B2 (en) | 2006-08-11 | 2009-11-09 | Method for manufacturing a vertical transistor that includes a super junction structure |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006219477A JP5011881B2 (ja) | 2006-08-11 | 2006-08-11 | 半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012091786A Division JP2012160753A (ja) | 2012-04-13 | 2012-04-13 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008047602A JP2008047602A (ja) | 2008-02-28 |

| JP2008047602A5 JP2008047602A5 (enExample) | 2010-01-07 |

| JP5011881B2 true JP5011881B2 (ja) | 2012-08-29 |

Family

ID=39051298

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006219477A Expired - Fee Related JP5011881B2 (ja) | 2006-08-11 | 2006-08-11 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7635622B2 (enExample) |

| JP (1) | JP5011881B2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10510879B2 (en) | 2018-03-22 | 2019-12-17 | Kabushiki Kaisha Toshiba | Semiconductor device |

Families Citing this family (39)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7229872B2 (en) * | 2000-04-04 | 2007-06-12 | International Rectifier Corporation | Low voltage power MOSFET device and process for its manufacture |

| US7790549B2 (en) * | 2008-08-20 | 2010-09-07 | Alpha & Omega Semiconductor, Ltd | Configurations and methods for manufacturing charge balanced devices |

| JP5135759B2 (ja) * | 2006-10-19 | 2013-02-06 | 富士電機株式会社 | 超接合半導体装置の製造方法 |

| US20090166722A1 (en) * | 2007-12-28 | 2009-07-02 | Alpha & Omega Semiconductor, Ltd: | High voltage structures and methods for vertical power devices with improved manufacturability |

| US7893488B2 (en) * | 2008-08-20 | 2011-02-22 | Alpha & Omega Semiconductor, Inc. | Charged balanced devices with shielded gate trench |

| US20120273916A1 (en) | 2011-04-27 | 2012-11-01 | Yedinak Joseph A | Superjunction Structures for Power Devices and Methods of Manufacture |

| US9508805B2 (en) | 2008-12-31 | 2016-11-29 | Alpha And Omega Semiconductor Incorporated | Termination design for nanotube MOSFET |

| US7943989B2 (en) * | 2008-12-31 | 2011-05-17 | Alpha And Omega Semiconductor Incorporated | Nano-tube MOSFET technology and devices |

| US7910486B2 (en) * | 2009-06-12 | 2011-03-22 | Alpha & Omega Semiconductor, Inc. | Method for forming nanotube semiconductor devices |

| US8299494B2 (en) | 2009-06-12 | 2012-10-30 | Alpha & Omega Semiconductor, Inc. | Nanotube semiconductor devices |

| JP5218326B2 (ja) * | 2009-08-11 | 2013-06-26 | 信越半導体株式会社 | 並列pn接合構造を有する半導体基板の製造方法 |

| JP5532758B2 (ja) * | 2009-08-31 | 2014-06-25 | 富士電機株式会社 | 半導体装置の製造方法および半導体装置 |

| US20110049638A1 (en) * | 2009-09-01 | 2011-03-03 | Stmicroelectronics S.R.L. | Structure for high voltage device and corresponding integration process |

| US7892924B1 (en) * | 2009-12-02 | 2011-02-22 | Alpha And Omega Semiconductor, Inc. | Method for making a charge balanced multi-nano shell drift region for superjunction semiconductor device |

| JP5729331B2 (ja) * | 2011-04-12 | 2015-06-03 | 株式会社デンソー | 半導体装置の製造方法及び半導体装置 |

| KR101930381B1 (ko) * | 2011-04-27 | 2018-12-19 | 페어차일드 세미컨덕터 코포레이션 | 전력 소자들을 위한 슈퍼정션 구조물 및 제조방법들 |

| TWI470699B (zh) * | 2011-12-16 | 2015-01-21 | 茂達電子股份有限公司 | 具有超級介面之溝槽型功率電晶體元件及其製作方法 |

| TWI487110B (zh) * | 2012-01-05 | 2015-06-01 | 世界先進積體電路股份有限公司 | 半導體裝置及其製造方法 |

| JP2013175655A (ja) | 2012-02-27 | 2013-09-05 | Toshiba Corp | 電力用半導体装置及びその製造方法 |

| JP2013219163A (ja) * | 2012-04-09 | 2013-10-24 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置およびその製造方法 |

| JP2013219207A (ja) * | 2012-04-10 | 2013-10-24 | Sumitomo Electric Ind Ltd | 電力用半導体装置およびその製造方法 |

| US20130320429A1 (en) * | 2012-05-31 | 2013-12-05 | Asm Ip Holding B.V. | Processes and structures for dopant profile control in epitaxial trench fill |

| US20130320512A1 (en) | 2012-06-05 | 2013-12-05 | Infineon Technologies Austria Ag | Semiconductor Device and Method of Manufacturing a Semiconductor Device |

| JP5812029B2 (ja) | 2012-06-13 | 2015-11-11 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| KR101420528B1 (ko) * | 2012-12-07 | 2014-07-16 | 삼성전기주식회사 | 전력 반도체 소자 |

| TWI470701B (zh) * | 2012-12-13 | 2015-01-21 | Pfc Device Holdings Ltd | 用於半導體元件之超接面結構及其製程 |

| CN104637821B (zh) * | 2015-01-19 | 2018-10-26 | 上海华虹宏力半导体制造有限公司 | 超级结器件的制造方法 |

| DE102015116040A1 (de) | 2015-09-23 | 2017-03-23 | Infineon Technologies Austria Ag | Halbleiterbauelemente und ein Verfahren zum Bilden von Halbleiterbauelementen |

| JP6817895B2 (ja) * | 2017-05-24 | 2021-01-20 | 株式会社東芝 | 半導体装置 |

| CN112514037A (zh) * | 2018-07-27 | 2021-03-16 | 日产自动车株式会社 | 半导体装置及其制造方法 |

| CN113628968B (zh) * | 2020-05-06 | 2022-06-24 | 苏州东微半导体股份有限公司 | 半导体超结器件的制造方法 |

| CN111785656B (zh) * | 2020-07-28 | 2023-08-15 | 哈尔滨工业大学 | 电子器件氧化层中固定负电荷陷阱的检测方法 |

| JP7339935B2 (ja) * | 2020-09-18 | 2023-09-06 | 株式会社東芝 | 半導体部材の製造方法及び半導体装置の製造方法 |

| CN115566039A (zh) * | 2021-07-01 | 2023-01-03 | 深圳尚阳通科技有限公司 | 超结器件及其制造方法 |

| US12324173B2 (en) | 2021-11-12 | 2025-06-03 | Shanghai Supersemiconductor Technology Co., Ltd. | Ultra-thin super junction IGBT device and manufacturing method thereof |

| CN114300528A (zh) * | 2021-12-28 | 2022-04-08 | 深圳市千屹芯科技有限公司 | 低关断损耗的超级结绝缘栅双极型晶体管及其制作方法 |

| CN114823532A (zh) * | 2022-06-24 | 2022-07-29 | 北京芯可鉴科技有限公司 | 超级结器件的制造方法、超级结器件、芯片和电路 |

| JP7702923B2 (ja) * | 2022-08-09 | 2025-07-04 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| CN115332104B (zh) * | 2022-08-30 | 2025-06-13 | 电子科技大学 | 评估超结电荷平衡的介质超结mis结构及测试方法 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3851744B2 (ja) * | 1999-06-28 | 2006-11-29 | 株式会社東芝 | 半導体装置の製造方法 |

| US6475864B1 (en) | 1999-10-21 | 2002-11-05 | Fuji Electric Co., Ltd. | Method of manufacturing a super-junction semiconductor device with an conductivity type layer |

| JP4127751B2 (ja) | 2000-06-29 | 2008-07-30 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP4635304B2 (ja) * | 2000-07-12 | 2011-02-23 | 富士電機システムズ株式会社 | 双方向超接合半導体素子およびその製造方法 |

| WO2002084745A2 (en) * | 2001-04-11 | 2002-10-24 | Silicon Wireless Corporation | Power semiconductor devices and methods of forming same |

| JP2003086800A (ja) * | 2001-09-12 | 2003-03-20 | Toshiba Corp | 半導体装置及びその製造方法 |

| US6555873B2 (en) * | 2001-09-07 | 2003-04-29 | Power Integrations, Inc. | High-voltage lateral transistor with a multi-layered extended drain structure |

| JP4109009B2 (ja) | 2002-04-09 | 2008-06-25 | 株式会社東芝 | 半導体素子及びその製造方法 |

| JP2004311673A (ja) | 2003-04-07 | 2004-11-04 | Denso Corp | 半導体装置の製造方法 |

| JP2004342660A (ja) | 2003-05-13 | 2004-12-02 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP4999464B2 (ja) * | 2003-12-19 | 2012-08-15 | サード ディメンジョン (スリーディ) セミコンダクタ インコーポレイテッド | 広いメサを備えた超接合ディバイスの製造方法 |

| US7368777B2 (en) * | 2003-12-30 | 2008-05-06 | Fairchild Semiconductor Corporation | Accumulation device with charge balance structure and method of forming the same |

| JP4773716B2 (ja) | 2004-03-31 | 2011-09-14 | 株式会社デンソー | 半導体基板の製造方法 |

| JP3961503B2 (ja) | 2004-04-05 | 2007-08-22 | 株式会社Sumco | 半導体ウェーハの製造方法 |

| JP2005317828A (ja) | 2004-04-30 | 2005-11-10 | Sumitomo Electric Ind Ltd | 高電圧車載電力変換用半導体装置の製造方法と高電圧車載電力変換用半導体装置 |

| JP4755439B2 (ja) | 2005-04-13 | 2011-08-24 | 新電元工業株式会社 | 半導体装置およびその製造方法 |

| JP5147163B2 (ja) | 2005-07-01 | 2013-02-20 | 株式会社デンソー | 半導体装置 |

| US7399673B2 (en) * | 2005-07-08 | 2008-07-15 | Infineon Technologies Ag | Method of forming a charge-trapping memory device |

| US20080017897A1 (en) * | 2006-01-30 | 2008-01-24 | Kabushiki Kaisha Toshiba | Semiconductor device and method of manufacturing same |

| US7595241B2 (en) * | 2006-08-23 | 2009-09-29 | General Electric Company | Method for fabricating silicon carbide vertical MOSFET devices |

-

2006

- 2006-08-11 JP JP2006219477A patent/JP5011881B2/ja not_active Expired - Fee Related

-

2007

- 2007-08-09 US US11/889,075 patent/US7635622B2/en active Active

-

2009

- 2009-11-09 US US12/614,632 patent/US7858475B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10510879B2 (en) | 2018-03-22 | 2019-12-17 | Kabushiki Kaisha Toshiba | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US7635622B2 (en) | 2009-12-22 |

| US20100112765A1 (en) | 2010-05-06 |

| US20080038850A1 (en) | 2008-02-14 |

| US7858475B2 (en) | 2010-12-28 |

| JP2008047602A (ja) | 2008-02-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5011881B2 (ja) | 半導体装置の製造方法 | |

| US9722070B2 (en) | Methods of manufacturing trench semiconductor devices with edge termination structures | |

| US7655974B2 (en) | Semiconductor device | |

| US7915155B2 (en) | Double trench for isolation of semiconductor devices | |

| US8237221B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| EP1211734A1 (en) | Vertical semiconductor device and method for producing the same | |

| JP2006066421A (ja) | 半導体装置およびその製造方法 | |

| JP2007189192A (ja) | 半導体装置 | |

| JP2004342660A (ja) | 半導体装置及びその製造方法 | |

| CN102386124A (zh) | 直接接触的沟槽结构 | |

| JP2009200300A (ja) | 半導体装置およびその製造方法 | |

| US7205587B2 (en) | Semiconductor device and method of producing the same | |

| CN210723039U (zh) | 双极晶体管 | |

| JP5766462B2 (ja) | 半導体装置およびその製造方法 | |

| US7132344B1 (en) | Super self-aligned BJT with base shorted field plate and method of fabricating | |

| KR101798241B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR101960547B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US7091578B2 (en) | Bipolar junction transistors and methods of manufacturing the same | |

| JP2012160753A (ja) | 半導体装置の製造方法 | |

| JP2005026391A (ja) | Mos型半導体装置 | |

| US7368361B2 (en) | Bipolar junction transistors and method of manufacturing the same | |

| JPH06318602A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2004311673A (ja) | 半導体装置の製造方法 | |

| JP2009043952A (ja) | 半導体装置の製造方法 | |

| JPH11297709A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080922 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120413 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120521 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150615 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5011881 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150615 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |