JP4358998B2 - 薄膜トランジスタ装置およびその製造方法 - Google Patents

薄膜トランジスタ装置およびその製造方法 Download PDFInfo

- Publication number

- JP4358998B2 JP4358998B2 JP2001025531A JP2001025531A JP4358998B2 JP 4358998 B2 JP4358998 B2 JP 4358998B2 JP 2001025531 A JP2001025531 A JP 2001025531A JP 2001025531 A JP2001025531 A JP 2001025531A JP 4358998 B2 JP4358998 B2 JP 4358998B2

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- polycrystalline

- composition ratio

- transistor

- crystal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010409 thin film Substances 0.000 title claims description 112

- 238000004519 manufacturing process Methods 0.000 title claims description 10

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 63

- 239000013078 crystal Substances 0.000 claims description 57

- 239000000203 mixture Substances 0.000 claims description 44

- 239000000758 substrate Substances 0.000 claims description 44

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 19

- 239000012212 insulator Substances 0.000 claims description 17

- 238000000034 method Methods 0.000 claims description 14

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 11

- 238000010438 heat treatment Methods 0.000 claims description 6

- 230000003746 surface roughness Effects 0.000 claims description 4

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims description 2

- 239000010408 film Substances 0.000 description 19

- 238000010586 diagram Methods 0.000 description 15

- 239000011521 glass Substances 0.000 description 12

- 230000002093 peripheral effect Effects 0.000 description 9

- 238000005224 laser annealing Methods 0.000 description 8

- 238000000137 annealing Methods 0.000 description 7

- 239000000969 carrier Substances 0.000 description 7

- 238000000089 atomic force micrograph Methods 0.000 description 6

- 239000000463 material Substances 0.000 description 6

- 238000001878 scanning electron micrograph Methods 0.000 description 6

- 238000002425 crystallisation Methods 0.000 description 5

- 238000005516 engineering process Methods 0.000 description 5

- 238000005191 phase separation Methods 0.000 description 5

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 230000008025 crystallization Effects 0.000 description 4

- 230000005669 field effect Effects 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 239000002245 particle Substances 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 238000007711 solidification Methods 0.000 description 3

- 230000008023 solidification Effects 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 239000000523 sample Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 108091006149 Electron carriers Proteins 0.000 description 1

- 229910008045 Si-Si Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910008310 Si—Ge Inorganic materials 0.000 description 1

- 229910006411 Si—Si Inorganic materials 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000000921 elemental analysis Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 229910000078 germane Inorganic materials 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 235000015067 sauces Nutrition 0.000 description 1

- 238000005204 segregation Methods 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78675—Polycrystalline or microcrystalline silicon transistor with normal-type structure, e.g. with top gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78684—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising semiconductor materials of Group IV not being silicon, or alloys including an element of the group IV, e.g. Ge, SiN alloys, SiC alloys

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/933—Germanium or silicon or Ge-Si on III-V

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Recrystallisation Techniques (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

Description

【発明の属する技術分野】

本発明は、薄膜トランジスタ装置およびその製造方法に係り、特に多結晶シリコン(poly-Si)薄膜を用いたトランジスタに好適な薄膜トランジスタ装置およびその製造方法に関する。

【0002】

【従来の技術】

薄膜トランジスタ装置は、例えば液晶表示装置(LCD)やプラズマ表示装置(PDP)等の主として画像表示装置に、画素もしくは周辺回路駆動用薄膜トランジスタ(TFT)として用いられている。

【0003】

従来の薄膜トランジスタが形成される母体薄膜には、主として高温多結晶Siが用いられてきた。これは絶縁体基板である石英基板上に、900℃前後の高温熱処理によって多結晶Si(poly-Si)薄膜を形成したもので、比較的大きな粒径(例えば500〜600nm)の多結晶Siが形成される。

【0004】

この高温多結晶Si(以下、高温poly-Siと言う)薄膜上に形成されたTFTは、粒界密度が低く結晶性のよいSi薄膜をチャネルとして利用するために、電界効果移動度が100〜150[cm2/Vs]とSi基板上の従来型Si-LSiのそれ(〜500[cm2/Vs],文献 S. M. Sze, Physics of Semiconductor Devices, p.29, Second Edition, Wiley)に近い値を得ることができる。

【0005】

しかし、この高温poly-Siは、高温プロセスに耐えられるよう絶縁体基板として高価な石英基板を使用する必要があるため、基板コストが原因となって半導体装置全体のコスト低減が困難でTFTの普及が制限されていた。

【0006】

近年、これに代わるものとして低温多結晶Si(以下、低温poly-Siと言う)が盛んに研究されてきた。これは、低コストのガラス基板あるいはプラスティック基板上にプラズマCVD法等のプロセスで形成した非晶質Siを、エキシマレーザーアニールなどの溶融再結晶化法を用いて結晶化した多結晶Siである。この手法を用いると、多結晶Si薄膜を低温(〜150℃)で形成可能のため、非常に廉価なTFTを形成できるという利点がある。

【0007】

しかし、これまでの低温poly-Siは、高温poly-Siと比べて結晶粒径が小さく(〜100nm)、かつ表面凹凸の大きな(〜50nm)多結晶Siしか形成することができなかった。

【0008】

結晶粒径が小さいと、キャリア経路に存在する粒界密度が大きくなり、粒界散乱を通してキャリア移動度を低下させてしまうという欠点がある。

また、表面凹凸が大きいと、ゲートリーク電流を抑えるためにその分ゲート絶縁膜を厚く(〜100nm)する必要が生じ、そのため同じゲート電圧によってチャネルに誘起されるキャリア数が小さくなるために、やはりキャリア移動度を低下させてしまう。

【0009】

このため従来の低温poly-Siを素子材とした製品ベースのTFTでは電界効果移動度が電子キャリアの場合で〜150[cm2/Vs]、正孔キャリアの場合で〜50[cm2/Vs]程度に抑えられていた。このような小さな移動度では必要とされる素子速度に到達できないために、同一のガラス(あるいはプラスティック)基板上に形成できる素子の種類が制限されるという問題が起こる。

【0010】

例えば画像表示装置の場合では、比較的要求性能が低い画素回路部はガラス(あるいはプラスティック)上に形成できるがその他の要求性能が高いソースドライバ、ゲートドライバ、シフトレジスタ、周辺コントローラなどの回路は、同一基板上に形成できないため、従来のSi-LSI技術を用いた半導体チップとしてプリント基板上に集積し、これをガラス基板と接続して用いなければならない。

【0011】

このような方法では、周辺回路部を実装する面積によって画面サイズが小さく(4インチ〜10インチ)なる上に、画像表示装置全体のコストが非常に高くなってしまうという問題があった。さらに、将来の市場が有望視される省電力画像表示装置ではTFTのCMOS(相補型MOS)化が必須であるが、そのためには正孔キャリアの電界効果移動度に対する要求性能はさらに大きくなると予測される。

【0012】

このような問題を改善するためには、低温poly-Siの粒界散乱を抑制し、かつ表面凹凸を小さくできるような多結晶薄膜を実現することでTFTを高性能化する技術が必要である。これまで低温poly-Siを、このように高機能化するために以下に例示するように様々な技術が提案されてきた。

【0013】

それらは例えば、絶縁体基板上に形成された非晶質Si膜に選択的に結晶化を助長する金属元素を導入し、基板に平行方向に結晶成長を行わせることにより、キャリア移動方向に[111]軸を持った多結晶Siを形成する技術(例えば特開平7-321339号公報);熱処理用ビームの形状と照射位置移動量を精密に制御して基板垂直方向に<100>軸、ビーム走査方向に平行(または45°の角度)の{220}面を持った矩形状多結晶Siを形成する技術(例えば特開平10-41234号公報);基板上に第1の多結晶Si層を形成し、異方性エッチングで特定面({100}、{110}、{111})のいずれかを持った種結晶を形成、その上に第2の多結晶Si層を形成することにより、面方位の揃った柱状の多結晶Si層を形成する技術(例えば特開平8-55808号公報)などである。

しかし、これら数多くの試みにもかかわらず、十分高移動度のTFTを得るにはいたっていない。

【0014】

【発明が解決しようとする課題】

上記従来の低温poly-Si薄膜の結晶化法はいずれも十分に完成した技術とは言えず、到達できる最大粒径、表面凹凸のいずれをとっても、例えば周辺回路集積型の液晶表示パネルに要求されるTFTの要求性能には及んでいない。このためこれらの技術では既存の低機能の薄膜トランジスタ装置を十分に置き換えるにはいたっていない。従って高性能で大面積の画像表示装置を低コストで実現すると言う技術課題は極めて重要である。

【0015】

そこで、本発明の第一の目的はTFTの素子材となる低温poly-Siにおいて、結晶粒界でのキャリア散乱を抑制し、表面凹凸を小さくして、正孔キャリアについても高移動度が実現できるような結晶構造を持つ多結晶薄膜を実現して、従来技術では得られない特性の優れた薄膜トランジスタ装置を提供することにあり、第二の目的はこの薄膜トランジスタ装置を容易に得ることのできる製造方法を提供することにあり、第三の目的はこの薄膜トランジスタ装置を用いた画像表示装置を提供することにある。

【0016】

【課題を解決するための手段】

上記目的を達成するために、本発明者等はTFTを形成するための低温poly-Siについて種々実験検討の結果、poly-Si薄膜中にGeを導入し、結晶化に伴う相分離で結晶粒内と結晶粒界との間にGe組成比を異ならせることで(詳しくは結晶粒界のGe組成比を結晶粒内でGe組成が最小となる部分よりも大きくする)、結晶粒界におけるキャリア散乱要因を抑制し、かつ結晶の体積差を利用して表面凹凸を抑制することにより高移動度TFTを実現することができると言う重要な知見を得た。

【0017】

本発明は、このような知見に基づいてなされたもので、上記第一の目的は、絶縁体基板と、前記絶縁体基板上に形成された多結晶薄膜と、前記多結晶薄膜上に形成されたソース、ドレイン、チャネル及びゲートからなるトランジスタとを有し、前記トランジスタのチャネル部における前記多結晶薄膜は、シリコンゲルマニウム多結晶Si1-xGexからなり、ただし、Siに対するGeの組成比xは0<x<1であり、かつ前記多結晶薄膜中のGeの組成比xは、結晶粒内でGe組成が最小となる部分よりも粒界においてより大きいことを特徴とする薄膜トランジスタ装置により、達成される。

【0018】

そして好ましくは、前記多結晶薄膜の厚さが10〜100nmであり、前記多結晶薄膜を構成する結晶粒の中心部におけるGeの組成比xが0<x≦0.3、粒界におけるGeの組成比xが0.1≦x<1.0であって、前記Geの組成比xは常に結晶粒内でGe組成が最小となる部分よりも粒界においてより大きいことである。

【0019】

さらに好ましい本発明薄膜トランジスタ装置の特徴点を以下に列挙する。

上記薄膜トランジスタ装置において、多結晶Si1-xGex薄膜は、粒界における表面凹凸が30nm以下であることを特徴とする。

【0020】

上記薄膜トランジスタ装置において、 前記トランジスタのチャネル部を流れる主キャリアが正孔であることを特徴とする。

【0021】

上記薄膜トランジスタ装置は、絶縁体基板と、前記絶縁体基板上に形成された多結晶薄膜と、前記多結晶薄膜上に形成されたソース、ドレイン、チャネル及びゲートからなるトランジスタとを有し、前記トランジスタのチャネル部における前記結晶薄膜は、基板に平行な{110}結晶面を有し、粒界における平均格子定数が結晶粒内部における平均格子定数より大きいことを特徴とする。

【0022】

上記薄膜トランジスタ装置は、絶縁体基板と、前記絶縁体基板上に形成された多結晶Si1-xGex薄膜、ただし、Siに対するGeの組成比xは0<x<1と、前記多結晶Si1-xGex薄膜上に形成されたソース、ドレイン、チャネル及びゲートからなるトランジスタを複数個集積して構成した回路部とを保持し、前記回路部はpタイプのトランジスタ及びnタイプのトランジスタの両者を混在させたCMOS型トランジスタを含むことを特徴とする。

【0023】

そして上記薄膜トランジスタ装置は、前記回路部を構成するpタイプのトランジスタのGe組成比xが、nタイプのトランジスタのGe組成比より大きいことを特徴とする。

【0024】

上記第二の目的は、絶縁体基板上に、膜厚10〜100nmの非晶質Si1-xGex層、ただし、Siに対するGeの組成比xは0<x<1、を形成する工程と、前記非晶質Si1-xGex層をエネルギー密度200〜300mJ/cm2、パルス数1〜50個のエキシマレーザーにより結晶化する熱処理工程とを有することを特徴とする薄膜トランジスタ装置の製造方法により、達成される。

【0025】

そして好ましくは、上記薄膜トランジスタ装置の製造方法において、前記熱処理工程は、前記非晶質Si1-xGex層の膜厚がTnmのときエネルギー密度を(180+T)〜(200+T)mJ/cm2として、膜厚に対応して変化させることを特徴とする。

【0026】

上記第三の目的は、画像表示部と、前記画像表示部の表示を制御し、少なくともデータドライバ、ゲートドライバ及びバッファアンプを含む画像表示回路と、前記画像表示回路の周辺に位置して前記画像表示回路を制御する周辺回路部とを有する画像表示装置であって、前記画像表示回路及び前記周辺回路部は、前記画像表示部を構成する基板と同一の基板上に集積されると共に、前記画像表示回路及び前記周辺回路部は、絶縁体基板と、前記絶縁体基板上に形成された多結晶Si1-xGex薄膜、ただし、Siに対するGeの組成比xは0<x<1と、前記多結晶Si1-xGex薄膜上に形成されたソース、ドレイン、チャネル及びゲートからなるトランジスタを複数個集積して構成した回路部とを保持し、前記回路部はpタイプのトランジスタもしくはnタイプのトランジスタのいずれか一方、もしくは両者を混在させたCMOS型トランジスタを含むことを特徴とする画像表示装置により、達成される。

【0027】

そして好ましくは、上記画像表示装置において、前記回路部を構成するpタイプトランジスタのGe組成比xが、nタイプトランジスタのGe組成比より大きいことを特徴とする。

【0028】

更に好ましくは、前記回路部に前記pタイプトランジスタ、前記nタイプトランジスタ及び前記CMOS型トランジスタのいずれかの種類を区別するために、これら回路近傍に設けられた位置合わせマークを保持することを特徴とする。

【0029】

【発明の実施の形態】

以下、図6〜図12を用い従来技術との対比において、本発明の特徴であるSiGeの結晶成長特性について詳細に説明する。なお、本明細書では結晶面方位(110)、(101)、(011)のように結晶学的に等価な面方位群をまとめて{110}のように表記している。

【0030】

図6は、従来TFTの母材であるエキシマレーザーアニールにより形成した多結晶Si薄膜の表面SEM(走査電子顕微鏡)像である。

なお、この多結晶Si薄膜は、ガラス基板上に周知のプラズマCVD法によって膜厚50nmに成膜し、それをエキシマレーザーにより、エネルギー密度340mJ/cm2の条件でアニールしたものである。

【0031】

この低温poly-Siの平均粒径は50〜100nmと比較的小さめの例を挙げたが、現在到達できる最大粒径は200〜300nm程度である。しかし、粒径が大きくなるにしたがい粒径ばらつきも増大し、その結果TFT移動度に大きなばらつきが生じることが問題となっている。

【0032】

このため実用的な結晶粒径としては図に挙げた50〜100nmが典型例である。各結晶粒の粒界は暗いコントラストとなっているが、それに隣接した部分においてところどころ明るいコントラストの領域が見られる。このようなコントラストの違いは表面凹凸に相当する。

【0033】

エキシマレーザーアニールなどの熱処理法では溶融から固化する過程でSi結晶の体積膨張を伴う。このため各結晶粒がぶつかり合う粒界付近では膨張した体積分を逃がすために基板に垂直な上方向へ膜を持ち上げる力が働く。結晶粒界の3重点付近ではこの力がさらに大きくなり表面凹凸の原因となっている。膜厚50nmのSi多結晶に対し平均的表面凹凸は50nmにも達する。

【0034】

図7は、本発明の低温多結晶Si1-xGex薄膜の表面SEM像(左図)および平面TEM(透過電子顕微鏡)像である。Ge組成比はx=0.3、KrFエキシマレーザーエネルギー密度240mJ/cm2、30回照射により形成したものである。

【0035】

なお、この場合も多結晶Si薄膜は、ガラス基板上に周知のプラズマCVD法によって膜厚50nmに成膜したが、その際にCVDガス中にソースとしてGeをSiに対して30mol%導入し、Si0.7Ge0.3薄膜(以下、単にSiGe薄膜と略記)とした。それをエキシマレーザーにより、エネルギー密度240mJ/cm2の条件でアニールしたものである。

【0036】

図7の左図を見ると、結晶粒径は図6の多結晶Si薄膜のそれとほとんど同じであるが、粒内と粒界のコントラスト関係が反転していることがわかる。これは図6の場合とは逆に、粒界の方が粒内より上に凸となっていることが原因である。元素分析の結果、この粒界には粒内よりはるかに高濃度のGeが検出され、その高濃度領域と本図における明るいコントラスト領域とはほぼ一致した。

【0037】

この多結晶Si0.7Ge0.3薄膜の平面TEMの暗視野像(図7の右図)を見ると結晶構造の詳細を知ることができる。本図(図7の右図)では基板面に平行な{110}面が明るく表示されるような条件で測定されている。図を見るとほとんどの結晶粒は同じ明るさに揃っており、若干数の黒い粒が間に存在することがわかる。結晶粒内にはスタッキングフォールトか双晶と思われる直線上の模様がところどころ見えるがそれ意外はほぼきれいな単結晶となっていることがわかる。

【0038】

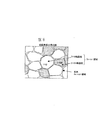

図8は、図7に示した本発明の低温多結晶SiGe薄膜の結晶構造模式図である。大部分の結晶粒が基板に平行な{110}面を持って揃っており、若干数の面方位の異なる粒が間に存在している。これら面方位の異なる粒は条件を変えたTEM観察によって、{110}面が基板平行面から1〜10度傾いたものであることがわかっている。このため本発明の多結晶SiGe薄膜は基本的に{110}面方位を持った多結晶であることがわかる。各粒内はアニール前に導入していたGe組成比よりSi-richであり、粒界ではそれに対しGe組成比の大きな結晶となっている。

【0039】

このような相分離(Ge組成比が結晶粒内と粒界とで異なる)が起こる原因は、Si中におけるGeの拡散係数とSi対Geの結合エネルギーに起因している。非晶質Si中のGe拡散係数は比較的大きく600℃でもD=8.0×10-20[m2/s]である(文献S. M. Prokes and F. Spaepen, Appl. Phys. Lett., vol 47, p234 (1985)参照)。

【0040】

このような移動条件のもと結晶が安定な格子を組むためには、各原子間の結合エネルギーを最小化した方がよい。Si-Si、Si-Ge、Ge-Ge間の結合エネルギーはそれぞれ3.73eV、3.65eV、3.56eVである(文献K. Nakagawa, N. Sugii, S. Yamaguchi, and M. Miyao, J. Cryst. Growth, vol 210, p560, (1999)参照)。

【0041】

このためGeはSiと結合するよりGe同士で結合する方がエネルギー的に安定となる。アニール前にSiの方がGeより多い条件に設定しておくと、結晶化の初期段階である任意の場所にSi結晶核ができ、それが成長する過程においてGeを周辺に追い出しながらSiを多く内包した結晶粒が成長する。このような結晶粒がいたるところ成長することにより、上述のような結晶構造を持つ多結晶SiGeが形成されると思われる。

【0042】

このような複数種からなる元素間の相分離自体は従来から知られている。相分離した元素それぞれをp型/n型に切り分けることで多結晶薄膜を熱電変換材料に利用した例もある(例えば特開平2000-261043号公報)。しかし、本発明の多結晶SiGe薄膜のように粒界構造のいたるところできれいにGe-richとなり、以下で述べるように粒界における表面凹凸を抑制できTFTに応用できる多結晶SiGe薄膜はこれまで知られていない。

【0043】

また、このようにGe-richな相ができると特に正孔移動度にとって有利な構造となる。材料自体の性質として単結晶Ge(電子移動度〜3000cm2/Vs、正孔移動度〜1500cm2/Vs)は、単結晶Si(電子移動度〜1500cm2/Vs、正孔移動度〜500cm2/Vs)より大きな移動度を持っている(文献M. V. Fischetti and S. E. Laux, J. Appl. Phys. Vol 80, p2234, (1996)参照)。

【0044】

従来問題視されてきたGe/酸化膜界面安定性の問題も熱酸化膜ではなく堆積酸化膜であればそれほど問題ではないこともわかっている。このような潜在能力の高いGeがTFTで用いられていない理由は形成できる多結晶Geの粒径が極めて小さく粒界散乱が大きくて実用にならないからである。しかし本発明のような多結晶SiGe薄膜構造であれば粒径は多結晶Si薄膜のそれに匹敵し、散乱の大きい粒界付近に高移動度のGe-rich相が存在することにより全体として高移動度を実現できるという利点がある。

【0045】

図9は、従来の多結晶Si薄膜のSEM像(左図)の四角領域におけるAFM(原子間力顕微鏡)像(右図)である。このAFM像は表面凹凸をそのまま直接コントラスト比で表示している。多結晶Si薄膜における結晶粒の3重点付近でいたるところ明るい凸部が見られる。これら凸部の頂点と凹部の底との高低差は上述したように約50nmと非常に大きい。これは体積膨張によって働く上向きの力が3重点で極めて大きいためである。

【0046】

一方、図10は、本発明の多結晶SiGe薄膜のSEM像(左図)、およびその四角領域におけるAFM像(右図)である。AFM像を見れば明らかなように粒界に相当する部分でまんべんなく明るく、凸部が形成されていることがわかる。

【0047】

図11の左図は、上記図10の右図と同様のAFM像であるが、右図はその直線部分における高低差分布を示す図である。この図から明るい部分が凸部、暗い部分が凹部に相当することがはっきりわかる。この凸部の頂点と凹部の底との高低差は最大で20nm程度と上述の図7に示した多結晶Si薄膜の50nmと比較して大幅に抑制されていることがわかる。

【0048】

これは主としてSi、Ge間で体積膨張係数や弾性係数が異なることが原因と考えられる。つまり、アニール前には非晶質SiGe混晶としての格子定数(>非晶質Si)で薄膜が形成されていたが、固化する際の相分離によって比較的硬いSi結晶の周りに柔らかいGe-rich相が形成されることで体積膨張分を粒界で緩和でき、その結果表面凹凸を抑制できていると考えられる。いずれにしても本発明の多結晶SiGe薄膜は、従来の多結晶Si薄膜より非常に小さな表面凹凸しか持たないことがわかる。

【0049】

図12は、本発明の多結晶SiGe薄膜を形成するために必要なレーザーアニール条件を、Ge組成比x=0.3の場合を例に示したものである。横軸は、エキシマ(KrF)レーザーのエネルギー密度[mJ/cm2]、縦軸は多結晶SiGe薄膜の膜厚(nm)であり、照射回数はすべて30回である。エネルギー密度を最低の140[mJ/cm2]から徐々に増大させていくと、表面凸部を示す明るいコントラスト領域がしだいに増していく。

【0050】

このうち膜厚50nmおよび30nmの場合だけ、それぞれ240[mJ/cm2]、220[mJ/cm2]で特異的に凸部が結晶粒界構造に一致することがわかる。このような構造は他のGe組成比(たとえばx=0.1など)でも見ることができるが、いずれの場合も極めて狭いアニール条件においてしか実現できないことがわかっている。この原因は、アニール前に導入したGe濃度が固化過程でちょうど偏析できる条件がそれほど広くないことによるためと思われるが、本発明ではこれら特異的なアニール処理条件で実現する多結晶SiGe薄膜を有効利用する。

以上で本発明の特徴である多結晶SiGe薄膜の結晶成長特性についての説明を終わる。以下では本発明の実施例に関する説明を行。

【0051】

【実施例】

以下、図1〜図5を用いて本発明の実施例を具体的に説明する。

(実施例1)

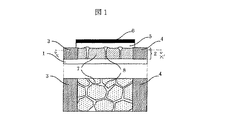

図1は、本発明の第1の実施例に係わる薄膜tランジスタ装置の展開図である。上段が縦断面図、その下段はチャネル部分を横(X−X‘方向)に切断した平面図である。ガラス板からなる絶縁体基板1上に、下記のプラズマCVDによる成膜条件、及びレーザーアニール条件で多結晶Si1-xGex薄膜2を形成した。

【0052】

すなわち、原料ガスとして、シラン及びゲルマンを用い、Si対Geの流量比が0.7対0.3になるようにガス量を調整しながら、合計膜厚が50nmとなるようプラズマCVDにより非晶質Si1-xGex薄膜を形成した。

【0053】

次に、成膜した表面に対し、レーザーアニール条件としてエネルギー密度240[mJ/cm2]、パルス数30回、パルス周波数100Hzでエキシマレーザーを照射し、多結晶Si1-xGex薄膜2を形成した。

【0054】

この多結晶Si1-xGex薄膜には、ソース3、ドレイン4、およびチャネル上にゲート絶縁膜5、ゲート6が形成されている。チャネルのうち、特にゲート絶縁膜5直下の領域は電界効果トランジスタの活性領域であり電流密度が最も大きい。その部分の平面図が図1の下段の図に描かれているが、本実施例ではこの平面上における多結晶Si1-xGex薄膜の結晶粒7内部のGe組成比xを0<x≦0.1、結晶粒界8におけるGe組成比xを0.3≦x<1とした。

【0055】

このような格子構造をとると、上述したように結晶粒界8の表面(凸部)と結晶粒7の表面(凹部)との高低差が20nm程度と大幅に抑制されて、ゲート絶縁膜5を比較的薄く(〜50nm)することができる。このため比較的小さなゲート電圧で多くのキャリアをチャネルに誘起することができ高移動度を実現できる。

【0056】

また、結晶粒7の大半が基板1に平行な{110}面に揃っていることで結晶粒界8の格子整合が比較的整いキャリアの粒界散乱を抑制できる効果も持つ。さらに、粒界8に高移動度のGe-rich相が形成されていることで膜全体の移動度が向上されるという利点も持つことが本実施例の特徴である。

【0057】

なお、多結晶Si1-xGex薄膜中のSiに対するGe組成比xの測定は、以下の方法で行った。

透過型電子顕微鏡(TEM)内に備えたX線微量分析計のプローブ用の電子ビームを小さく(約100nm)絞って試料表面に照射し、照射された領域から放出される特性X線の波長と強度を測定することにより、SiとGeとの濃度を測定する。

次に、このSiとGeとの濃度の測定結果から計算により、Siに対するGe組成比xを求める。

【0058】

また、結晶粒の組成比の測定は、ビーム照射領域が結晶粒内部に納まるように行う。粒界の組成比の測定は、ビーム照射領域が粒界を含むように行う。ここで、ビーム照射領域が粒界からはみ出して結晶粒にまたがっても良い。

(実施例2)

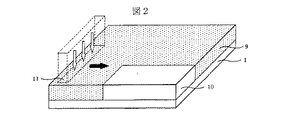

図2〜図4は、本発明の第2の実施例に係わる薄膜半導体装置とその製造過程を模式的に示したものである。本実施例では多結晶Si1-xGex薄膜を部分的に導入してトランジスタをCMOS(相補型MOS)化するものである。

【0059】

まず、図2に示したように、絶縁体基板(ガラス板)1上に非晶質Si薄膜9を形成する。その一部を通常のフォトプロセスでエッチング除去し、埋め込み型のGe組成比増加領域10を設ける。このようにして得た薄膜表面をKrFエキシマレーザーで照射しつつ、基板1を保持したステージを順次移動させることでレーザービーム照射領域11を走査させる。このとき予めステージ移動領域をプログラム制御することで、後にトランジスタ領域となる部分だけを選択的に結晶化する。

【0060】

このようにして、図3に示したように非晶質Si薄膜9の必要領域にのみ、純粋Si多結晶12および多結晶Si1-xGex薄膜2領域が形成される。

【0061】

次に、図4に示したように、結晶化した薄膜にAsイオンを注入することでn型領域14を、また、Bイオンを注入することでp型領域13を、それぞれ注入用マスクを使用して順序よくかつ領域選択的に形成する。この後窒素雰囲気中で600℃1時間程度の炉アニールを行いn型領域14およびp型領域13のキャリア活性化を行い、その上にゲート絶縁膜5、ゲート6を設けてトランジスタを形成する。

【0062】

こうすることでp型領域13には、多結晶Si薄膜12からなるnタイプトランジスタが、また、n型領域14には、多結晶Si1-xGex薄膜2からなるpタイプトランジスタがそれぞれでき、低消費電力と高移動度を両立させたCMOS型トランジスタが形成されるという利点がある。

(実施例3)

図5は、本発明の薄膜半導体装置を利用した画像表示装置の分解組み立て図の例を示す。絶縁体基板(ガラス板)1上に多結晶Si薄膜と多結晶Si1-xGex薄膜を選択的に形成し、その上に画素ドライバ領域17、バッファアンプ領域18、ゲートドライバ領域19、シフトレジスタ領域20、データドライバ領域21などからなる回路が集積されており、それらが一体となって、画素16を持つ画像表示パネル15に接続されて機能する。

【0063】

これらの回路を構成するトランジスタには要求される性能がそれぞれ異なるため、本発明の実施例1〜3のトランジスタが選択的かつ複合的に組み合わされて利用されている。このような構成では、大面積のガラス基板上に主要な回路を集積することができ、従来の周辺回路のほとんどを集積した画像表示装置を形成することができる。さらに低コストのガラス基板を用いて数少ない工程により製造できるという利点がある。

【0064】

【発明の効果】

本発明によれば、Si中にGeを導入し結晶化に伴う相分離で結晶粒内と結晶粒界との間にGe組成比を異ならせることで、結晶粒界におけるキャリア散乱要因を抑制し、かつ結晶の体積差を利用して表面凹凸を抑制することにより高移動度TFTを実現する。これにより、同一ガラス基板上に、画素部、周辺回路を集約的に形成することが可能となるため、大面積(例えば15インチ以上)画像表示装置を高集積化することができる。

【図面の簡単な説明】

【図1】本発明の第1の実施例に係わる薄膜トランジスタ装置の展開図である。上段が縦断面図、その下段はチャネル部分を横に切断した平面図である。

【図2】本発明の第2の実施例に係わる薄膜トランジスタ装置とその製造過程を模式的に示したものである。

【図3】同じく本発明の第2の実施例に係わる薄膜トランジスタ装置とその製造過程を模式的に示したものである。

【図4】同じく本発明の第2の実施例に係わる薄膜トランジスタ装置とその製造過程を模式的に示したものである。

【図5】本発明の薄膜トランジスタ装置を利用した画像表示装置の例を示したものである。

【図6】従来TFTの母材であるエキシマレーザーアニールにより形成した多結晶Si薄膜の表面SEM(走査電子顕微鏡)像である。

【図7】本発明の多結晶SiGe薄膜の表面SEM像(左図)および平面TEM(透過電子顕微鏡)像である。

【図8】本発明の多結晶SiGe薄膜の結晶構造模式図である。

【図9】従来多結晶Si薄膜のSEM像(左図)とその四角領域におけるAFM(原子間力顕微鏡)像(右図)である。

【図10】本発明の多結晶SiGe薄膜のSEM像(左図)とその四角領域におけるAFM像(右図)である。

【図11】上記図10のAFM像(左図)と、その直線部分における高低差分布を示す図(右図)である。

【図12】本発明の多結晶Si1-xGex薄膜を形成するために必要なレーザーアニール条件を、Ge組成比x=0.3の場合で示したものである。

【符号の説明】

1…絶縁体基板、

2…多結晶Si1-xGex薄膜、

3…ソース、

4…ドレイン、

5…ゲート絶縁膜、

6…ゲート、

7…結晶粒、

8…結晶粒界、

9…非晶質Si薄膜、

10…Ge組成比増加領域、

11…レーザービーム照射領域、

12…純粋Si多結晶、

13…p型領域、

14…n型領域、

15…画像表示パネル、

16…画素、

17…画素ドライバ領域、

18…バッファアンプ領域、

19…ゲートドライバ領域、

20…シフトレジスタ領域、

21…データドライバ領域。

Claims (4)

- 絶縁体基板と、前記絶縁体基板上に形成された多結晶薄膜と、前記多結晶薄膜上に形成されたソース、ドレイン、チャネル及びゲートからなるトランジスタとを有し、前記トランジスタのチャネル部における前記多結晶薄膜は、シリコンゲルマニウム多結晶Si1−xGexからなり、ただし、Siに対するGeの組成比xは0<x<1であり、かつ前記多結晶薄膜中のGeの組成比xは、結晶粒内でGe組成が最小となる部分よりも粒界において大きく、前記多結晶Si 1−x Ge x 薄膜は、粒界における表面凹凸が30nm以下であることを特徴とする薄膜トランジスタ装置。

- 前記多結晶薄膜の厚さが10〜100nmであり、前記多結晶薄膜を構成する結晶粒内でGe組成が最小となる部分におけるGeの組成比xが0<x≦0.1、粒界におけるGeの組成比xが0.3≦x<1.0であって、前記Geの組成比xは常に結晶粒の中心部よりも粒界において大きいことを特徴とする請求項1記載の薄膜トランジスタ装置。

- 前記トランジスタのチャネル部を流れる主キャリアが正孔であることを特徴とする請求項1記載の薄膜トランジスタ装置。

- 絶縁体基板上に、膜厚10〜100nmの非晶質Si1-xGex層、ただし、Siに対するGeの組成比xは0<x<1、を形成する工程と、前記非晶質Si1-xGex層をエネルギー密度200〜300mJ/cm2、パルス数1〜50個のエキシマレーザーにより結晶化する熱処理工程とを有し、非晶質Si1-xGex層を多結晶Si1-xGexにGeの組成比xを0<x<1で変化させ、前記多結晶薄膜中のGeの組成比xを、結晶粒内でGe組成が最小となる部分よりも粒界において大きくなるようにしたことを特徴とする薄膜トランジスタ装置の製造方法。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001025531A JP4358998B2 (ja) | 2001-02-01 | 2001-02-01 | 薄膜トランジスタ装置およびその製造方法 |

| TW090103950A TW478171B (en) | 2001-02-01 | 2001-02-21 | Thin film semiconductor device and method for producing thereof |

| US09/790,545 US6521909B2 (en) | 2001-02-01 | 2001-02-23 | Thin film semiconductor device containing polycrystalline Si-Ge alloy and method for producing thereof |

| KR1020010009646A KR100761619B1 (ko) | 2001-02-01 | 2001-02-26 | 박막 반도체 장치 및 그 제조 방법 |

| US10/277,140 US6716726B2 (en) | 2001-02-01 | 2002-10-22 | Thin film semiconductor device containing polycrystalline Si—Ge alloy and method for producing thereof |

| US10/274,995 US6690064B2 (en) | 2001-02-01 | 2002-10-22 | Thin-film semiconductor device containing poly-crystalline Si-Ge alloy and method for producing thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001025531A JP4358998B2 (ja) | 2001-02-01 | 2001-02-01 | 薄膜トランジスタ装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002231958A JP2002231958A (ja) | 2002-08-16 |

| JP2002231958A5 JP2002231958A5 (ja) | 2006-03-30 |

| JP4358998B2 true JP4358998B2 (ja) | 2009-11-04 |

Family

ID=18890502

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001025531A Expired - Fee Related JP4358998B2 (ja) | 2001-02-01 | 2001-02-01 | 薄膜トランジスタ装置およびその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US6521909B2 (ja) |

| JP (1) | JP4358998B2 (ja) |

| KR (1) | KR100761619B1 (ja) |

| TW (1) | TW478171B (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3980159B2 (ja) * | 1998-03-05 | 2007-09-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3737914B2 (ja) * | 1999-09-02 | 2006-01-25 | 松下電器産業株式会社 | 半導体装置及びその製造方法 |

| US6882012B2 (en) * | 2000-02-28 | 2005-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and a method of manufacturing the same |

| JP3559962B2 (ja) * | 2000-09-04 | 2004-09-02 | 日本航空電子工業株式会社 | 熱電変換材料及びその製造方法 |

| US6746942B2 (en) * | 2000-09-05 | 2004-06-08 | Sony Corporation | Semiconductor thin film and method of fabricating semiconductor thin film, apparatus for fabricating single crystal semiconductor thin film, and method of fabricating single crystal thin film, single crystal thin film substrate, and semiconductor device |

| JP2003332350A (ja) * | 2002-05-17 | 2003-11-21 | Hitachi Ltd | 薄膜半導体装置 |

| JP3904512B2 (ja) * | 2002-12-24 | 2007-04-11 | シャープ株式会社 | 半導体装置およびその製造方法、並びに半導体装置を備えた電子機器 |

| JP2004207616A (ja) * | 2002-12-26 | 2004-07-22 | Hitachi Displays Ltd | 表示装置 |

| KR100975523B1 (ko) * | 2003-12-30 | 2010-08-13 | 삼성전자주식회사 | 조절된 이동도를 가지는 반도체 소자 및 이를 적용한 tft |

| JP4567984B2 (ja) * | 2004-01-30 | 2010-10-27 | 株式会社 日立ディスプレイズ | 平面表示装置の製造装置 |

| KR100623689B1 (ko) * | 2004-06-23 | 2006-09-19 | 삼성에스디아이 주식회사 | 박막트랜지스터 및 그의 제조 방법 |

| JP5152827B2 (ja) | 2007-03-22 | 2013-02-27 | 株式会社日立製作所 | 薄膜トランジスタ及びそれを用いた有機el表示装置 |

| JP5648252B2 (ja) * | 2010-08-27 | 2015-01-07 | 学校法人東北学院 | 半導体装置 |

| KR101983157B1 (ko) * | 2013-11-19 | 2019-05-28 | 삼성전기주식회사 | 인쇄회로기판 및 그 제조방법 |

| NZ723384A (en) | 2014-03-12 | 2019-11-29 | Hexion Inc | Polymers, composites, and methods for making polymers and composites |

| WO2017019064A1 (en) | 2015-07-29 | 2017-02-02 | Schober Robert C | Complementary current field-effect transistor devices and amplifiers |

| US10514716B2 (en) | 2015-07-30 | 2019-12-24 | Circuit Seed, Llc | Reference generator and current source transistor based on complementary current field-effect transistor devices |

| CN108141181A (zh) | 2015-07-30 | 2018-06-08 | 电路种子有限责任公司 | 多级式且前馈补偿的互补电流场效应晶体管放大器 |

| CN108141180A (zh) | 2015-07-30 | 2018-06-08 | 电路种子有限责任公司 | 基于互补电流场效应晶体管装置的低噪声跨阻抗放大器 |

| CN108140613B (zh) * | 2015-12-14 | 2020-07-28 | 电路种子有限责任公司 | 过饱和电流场效应晶体管和跨阻抗mos装置 |

| CN107359203A (zh) | 2017-05-12 | 2017-11-17 | 惠科股份有限公司 | 显示面板和显示装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR940010378A (ko) * | 1992-10-19 | 1994-05-26 | 김광호 | 다결정 실리콘 박막의 제조방법 |

| JP2791858B2 (ja) | 1993-06-25 | 1998-08-27 | 株式会社半導体エネルギー研究所 | 半導体装置作製方法 |

| JPH0823160A (ja) * | 1994-05-06 | 1996-01-23 | Seiko Epson Corp | プリント配線板と電子部品の接続方法 |

| JPH07321323A (ja) * | 1994-05-24 | 1995-12-08 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタおよびその製造方法 |

| JP3294439B2 (ja) | 1994-08-17 | 2002-06-24 | 沖電気工業株式会社 | 多結晶シリコン薄膜の形成方法 |

| JP4026191B2 (ja) | 1996-05-22 | 2007-12-26 | ソニー株式会社 | シリコン単結晶粒子群の形成方法及びフラッシュメモリセルの製造方法 |

| JP3642546B2 (ja) * | 1997-08-12 | 2005-04-27 | 株式会社東芝 | 多結晶半導体薄膜の製造方法 |

| TW454260B (en) * | 1998-06-30 | 2001-09-11 | Matsushita Electric Ind Co Ltd | Thin film transistor and manufacturing method thereof |

| JP2000174282A (ja) * | 1998-12-03 | 2000-06-23 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2000243854A (ja) * | 1999-02-22 | 2000-09-08 | Toshiba Corp | 半導体装置及びその製造方法 |

| US6426245B1 (en) * | 1999-07-09 | 2002-07-30 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

-

2001

- 2001-02-01 JP JP2001025531A patent/JP4358998B2/ja not_active Expired - Fee Related

- 2001-02-21 TW TW090103950A patent/TW478171B/zh not_active IP Right Cessation

- 2001-02-23 US US09/790,545 patent/US6521909B2/en not_active Expired - Lifetime

- 2001-02-26 KR KR1020010009646A patent/KR100761619B1/ko not_active IP Right Cessation

-

2002

- 2002-10-22 US US10/274,995 patent/US6690064B2/en not_active Expired - Lifetime

- 2002-10-22 US US10/277,140 patent/US6716726B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20030049892A1 (en) | 2003-03-13 |

| KR20020064620A (ko) | 2002-08-09 |

| US20020102823A1 (en) | 2002-08-01 |

| US20030054593A1 (en) | 2003-03-20 |

| JP2002231958A (ja) | 2002-08-16 |

| US6521909B2 (en) | 2003-02-18 |

| TW478171B (en) | 2002-03-01 |

| KR100761619B1 (ko) | 2007-09-27 |

| US6690064B2 (en) | 2004-02-10 |

| US6716726B2 (en) | 2004-04-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4358998B2 (ja) | 薄膜トランジスタ装置およびその製造方法 | |

| JP4732599B2 (ja) | 薄膜トランジスタ装置 | |

| US20050179086A1 (en) | Structures with seeded single-crystal domains | |

| Howell et al. | Poly-Si thin-film transistors on steel substrates | |

| US20060113596A1 (en) | Single crystal substrate and method of fabricating the same | |

| Tsai et al. | High-performance top and bottom double-gate low-temperature poly-silicon thin film transistors fabricated by excimer laser crystallization | |

| Rana et al. | Dependence of single-crystalline Si TFT characteristics on the channel position inside a location-controlled grain | |

| TWI266371B (en) | Thin-film semiconductor device, manufacturing method of the same and image display apparatus | |

| US6593215B2 (en) | Method of manufacturing crystalline semiconductor material and method of manufacturing semiconductor device | |

| US20060084246A1 (en) | Manufacturing method for crystalline semiconductor material and manufacturing method for semiconductor device | |

| US7109075B2 (en) | Method for fabrication of polycrystallin silicon thin film transistors | |

| Choi et al. | Giant-grain silicon (GGS) and its application to stable thin-film transistor | |

| US7662678B2 (en) | Method of forming a more highly-oriented silicon layer and substrate having the same | |

| JP2001345451A (ja) | 薄膜半導体集積回路装置、それを用いた画像表示装置、及びその製造方法 | |

| JP5232360B2 (ja) | 半導体装置及びその製造方法 | |

| Sugawara et al. | Crystallization of double-layered silicon thin films by solid green laser annealing for high-performance thin-film transistors | |

| JP3203652B2 (ja) | 半導体薄膜の製造方法 | |

| JP4701467B2 (ja) | 多結晶膜の製造方法および半導体装置の製造方法 | |

| Noguchi | Prospective crystallization of amorphous Si films for new Si TFTs | |

| JP2867402B2 (ja) | 半導体装置の製造方法 | |

| Yamaguchi et al. | Novel high-performance TFTs fabricated by selectively enlarging laser x'tallization (SELAX) technology | |

| Wang et al. | High-performance polycrystalline silicon thin-film transistors with two-dimensional location control of the grain boundary via excimer laser crystallization | |

| KR101333797B1 (ko) | 실리사이드 씨드 유도 측면 결정화를 이용한 비정질 실리콘 박막의 결정화 방법 및 이를 이용한 다결정 박막 트랜지스터의 제조방법 | |

| KR0128522B1 (ko) | 저온 다결정질 실리콘 박막 구조 및 그 제조방법, 저온 다결정질 실리콘 박막 트랜지스터 및 그 제조 방법 | |

| Song et al. | A study on the Pd/a-Si/Ni seed layer for metal-induced lateral crystallization and poly-Si TFTs |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060214 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060214 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060214 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090113 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090721 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090807 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4358998 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S631 | Written request for registration of reclamation of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313631 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 Free format text: JAPANESE INTERMEDIATE CODE: R313121 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120814 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130814 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |