JP3595745B2 - 画像処理装置 - Google Patents

画像処理装置 Download PDFInfo

- Publication number

- JP3595745B2 JP3595745B2 JP31078599A JP31078599A JP3595745B2 JP 3595745 B2 JP3595745 B2 JP 3595745B2 JP 31078599 A JP31078599 A JP 31078599A JP 31078599 A JP31078599 A JP 31078599A JP 3595745 B2 JP3595745 B2 JP 3595745B2

- Authority

- JP

- Japan

- Prior art keywords

- image

- input

- signal

- synchronization signal

- clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

- H04L12/40052—High-speed IEEE 1394 serial bus

- H04L12/40117—Interconnection of audio or video/imaging devices

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/43—Processing of content or additional data, e.g. demultiplexing additional data from a digital video stream; Elementary client operations, e.g. monitoring of home network or synchronising decoder's clock; Client middleware

- H04N21/4302—Content synchronisation processes, e.g. decoder synchronisation

- H04N21/4305—Synchronising client clock from received content stream, e.g. locking decoder clock with encoder clock, extraction of the PCR packets

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/43—Processing of content or additional data, e.g. demultiplexing additional data from a digital video stream; Elementary client operations, e.g. monitoring of home network or synchronising decoder's clock; Client middleware

- H04N21/431—Generation of visual interfaces for content selection or interaction; Content or additional data rendering

- H04N21/4312—Generation of visual interfaces for content selection or interaction; Content or additional data rendering involving specific graphical features, e.g. screen layout, special fonts or colors, blinking icons, highlights or animations

- H04N21/4316—Generation of visual interfaces for content selection or interaction; Content or additional data rendering involving specific graphical features, e.g. screen layout, special fonts or colors, blinking icons, highlights or animations for displaying supplemental content in a region of the screen, e.g. an advertisement in a separate window

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/43—Processing of content or additional data, e.g. demultiplexing additional data from a digital video stream; Elementary client operations, e.g. monitoring of home network or synchronising decoder's clock; Client middleware

- H04N21/436—Interfacing a local distribution network, e.g. communicating with another STB or one or more peripheral devices inside the home

- H04N21/4363—Adapting the video stream to a specific local network, e.g. a Bluetooth® network

- H04N21/43632—Adapting the video stream to a specific local network, e.g. a Bluetooth® network involving a wired protocol, e.g. IEEE 1394

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/14—Picture signal circuitry for video frequency region

- H04N5/20—Circuitry for controlling amplitude response

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/44—Receiver circuitry for the reception of television signals according to analogue transmission standards

- H04N5/445—Receiver circuitry for the reception of television signals according to analogue transmission standards for displaying additional information

- H04N5/45—Picture in picture, e.g. displaying simultaneously another television channel in a region of the screen

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Computer Networks & Wireless Communication (AREA)

- Business, Economics & Management (AREA)

- Marketing (AREA)

- Controls And Circuits For Display Device (AREA)

- Liquid Crystal Display Device Control (AREA)

- Transforming Electric Information Into Light Information (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Picture Signal Circuits (AREA)

- Control Of Gas Discharge Display Tubes (AREA)

- Facsimile Image Signal Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、様々なフォーマットを有する画像信号を所望のフォーマットの画像信号に変換したり、合成したりする画像処理装置に関する。

【0002】

【従来の技術】

近年のマルチメディア化に伴い、ディスプレイも多様な画像信号フォーマットのものを表示する機会が増えている。特に、以前はTVセットとパーソナルコンピュータ(PC)のディスプレイは全くの別物であったが、相互の融合化が進み、PCの画像を表示できるTVや、TVの信号を入力できるPCのディスプレイが現れてきた。また、デジタルテレビやMPEGなどの新しいデジタルフォーマットの映像ソースの出現や3次元グラフィックスの高度化が進み、PC用ディスプレイといえども、動画を表示する割合が増加してきている。

【0003】

図6に従来のこうしたディスプレイのブロック図を示す。同図において、1−1はアナログの画像信号の入力端子であり、1−2は入力信号の水平同期信号(IHD)入力端子であり、1−3は入力信号の垂直同期信号(IVD)入力端子である。2はADコンバータであり、入力端子1−1に入力されるアナログの画像信号をnビットのデジタル信号に変換する。3は入力系画像処理部、4はメモリ制御部、5は画像データを格納するメモリ部、6は出力系画像処理部であり、7は画像表示部である。20−1、20−2、20−3、20−4は各部へnビットのデジタル信号を伝送するデータバスである。21はメモリの制御線およびアドレス線から構成される制御バスであり、22はメモリのデータバスである。

【0004】

また、8はPLL(Phase Locked Loop)回路であり、ICKは入力IHDに同期した入力系クロックである。12は発振回路であり、出力系クロックOCKを発生する。11はHおよびVカウンタ回路であり、出力系クロックOCKから出力系水平同期信号OHDおよび垂直同期信号OVDを作成する。9はマイクロコンピュータ(μCOM)部であり、19は各部を制御するm本の制御バスである。

【0005】

デジタル画像信号はメモリ部5に格納される前に入力系画像処理部3で画質の調整や画像の縮小変換等の処理を行なわれ、メモリ制御部4に転送される。メモリ制御部4では入力同期信号(IHD、IVD)と入力系クロックICKに対応したタイミングでメモリ部5に画像データを格納するとともに、出力系のクロックOCK、水平同期信号OHDおよび垂直同期信号OVDのタイミングで画像データをメモリ部5から読み出し出力系画像処理部6にデータを転送する。画像処理部6では、画質の調整や、画像の拡大変換などが行なわれる。これにより、入力系の様々なフォーマットの入力画像をメモリを介在して画像表示部7に適したフォーマットの画像信号に変換している。

【0006】

さらに、最近、ワイド対応のテレビやプラズマディスプレイ、リア型プロジェクションTVや投射型のプロジェクターなどの大画面の表示装置において、映画やTV、ホームビデオ、プレゼンテーション、TV会議、各種資料の表示などのさまざまな映像ソースをオフィスや家庭で利用する場面が増加している。さらに、このような形態のなかで、1つの画面内に複数の異なる入力ソースの画像を画面内に分割して表示を行なうマルチ画面表示の表示装置がある。

【0007】

図13に従来こうした場面で用いられるディスプレイの例として、1系統はデジタルのコンピュータ画像信号の入力であり、もう1系統はアナログのコンピュータ画像信号の入力である2系統のPC入力を有し、フレームメモリの出力を制御して合成を行ない、1系統の画像表示部に2画面のマルチ画面表示を行なう画像表示装置の画像処理部のブロック図を示す。

【0008】

図13において、1−1aは1系統目(PC1)のqビットのデジタルのコンピュータ画像信号(IDATA1)の入力端子である。ここでは、本来、赤、青、緑(RGB)の3系統あるはずであるが、構成の説明を簡単にするため、1系統で示している(以下同様)。1−1bは入力信号の水平同期信号(IHD1)入力端子であり、1−1cは入力信号の垂直同期信号(IVD1)入力端子である。1−1dは画像信号のクロック(ICK1)入力端子であり、1−1eは、DDC(DDC1)入出力端子である。20−1a−1、20−1a−2は各部へqビットのデジタルの画像信号を伝送するデータバスである。また、20−1b、20−1c、20−1d、20−1eは、それぞれ、IHD1、IVD1、ICK1、DDC1の信号線である。

DDCとは、標準化団体であるVESA(Video ElectronicStandard Association)が勧告した、コンピュータが表示装置を認識および制御するための通信手段の標準である。

【0009】

1−2aは、2系統目(PC2)のアナログのコンピュータ画像信号(IDATA2)の入力端子である。1−2bは入力信号の水平同期信号(IHD2)入力端子であり、1−2cは入力信号の垂直同期信号(IVD2)入力端子である。1−2eはDDC(DDC2)入出力端子である。

2はADコンバータであり、アナログの画像信号(IDATA2)をnビットのデジタル信号に変換する。また、8はPLL回路であり、端子1−2bから入力した水平同期信号(IHD2)に同期したPC2側の入力系のクロック(ICK2)を発生する。

【0010】

20−2a−0はアナログの信号線であり、20−2a−1、20−2a−2はnビットのデジタルの信号線である。また、20−2b、20−2c、20−2d、20−2eは、それぞれ、IHD2、IVD2、ICK2、DDC2の信号線である。

【0011】

3−1はPC1の入力系の画像処理部であり、3−2はPC2の入力系の画像処理部である。4は2系統の入力画像処理部から入力された画像信号を、一旦メモリに記憶し、マルチ画面として出力するために、画像を合成して出力系の画像処理部に出力する制御を行うメモリ制御部である。5−1、5−2は入力系PC1、PC2にそれぞれ対応したフレームメモリ(メモリA、メモリB)である。21−1、21−2はそれぞれメモリA、Bの制御バスであり、22−1、22−2はそれぞれメモリA、Bのデータバスである。

【0012】

9は、システムを制御するマイコン部であり、19−1および19−2はマイコンから各部への制御線およびデータ線からなるマイコンバス(MB)である。

12は発振回路であり、出力系のクロック(OCK)を発生する。

11はH、Vカウンタ回路であり、出力系のクロック(OCK)をカウントして、出力系の水平同期信号(OHD)と垂直同期信号(OVD)を作成する。

【0013】

また、6は出力系の画像処理部であり、7は液晶やプラズマディスプレイ、CRTなどの画像表示部である。

1−fは画像表示用デジタルデータ(ODATA)の画像表示部の入力端子であり、1−gは出力信号の水平同期信号(OHD)の画像表示部の入力端子であり、1−hは出力信号の垂直同期信号(OVD)の画像表示部の入力端子である。1−iは、出力画像信号のクロック(OCK)の画像表示部の入力端子であり、1−jは、マイコンバス(MB)の画像表示部の入力端子である。

【0014】

また、20−f−1、20−f−2、20−f−3はkビットのODATAの信号線である。20−g−1、20−g−2はOHDの信号線である。20−h−1、20−h−2はOVDの信号線である。20−i−1、20−i−2はOCKの信号線である。

【0015】

画像の入力端子1−1aから入力したデジタル画像信号は、5−1のメモリ部Aに格納される前に3−1の入力系画像処理部1で画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。

また、画像の入力端子1−2aから入力したアナログ画像信号は、PLL回路8で作成されたクロックに同期して、ADコンバータ2でデジタルデータに変換される。こうして得られたデジタル画像信号は、5−2のメモリ部Bに格納される前に3−2の入力系画像処理部2で画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。

【0016】

メモリ制御部4では、IDATA1を処理した信号に基づき、入力同期信号(IHD1、IVD1)と入力系クロックICK1に対応したタイミングで5−1のメモリ部Aに画像データを格納するとともに、IDATA2からデジタルに変換された信号を、入力同期信号(IHD2、IVD2)と入力系クロックICK2に対応したタイミングで5−2のメモリ部Bに画像データとして格納する。さらに、出力系のクロックOCK、水平同期信号OHD、垂直同期信号OVDに同期した所定の画像の大きさ、表示位置の関係に合ったタイミングで2つの画像データをメモリ部5−1と5−2から読み出して、出力系画像部6にデータを転送する。画像処理部6では、画質の調整や、画像の拡大変換などが行なわれる。これにより、入力系の様々なフォーマットの入力画像をメモリを介在して画像表示部7に適したフォーマットの画像信号に変換するとともに、2入力から入力された画像データを1画面上に合成してマルチ画面表示を行なう。

【0017】

図7に、図6および図13のディスプレイにおいて、画像表示部7の解像度がXGA(横1024画素×縦768画素)、表示垂直周波数が75Hzである場合に、入力信号(図6の入力信号または図13のPC1入力もしくはPC2入力)として▲1▼VGA(横640画素×縦480画素)100Hz、および▲2▼SVGA(横800画素×縦600画素)60Hzの画像信号が入力された場合の動作タイミングの例を示した。図7の説明上、図13の装置に関してはPC1入力の系統もPC2入力の系統も同様の動作のため、同じこととして説明する。

【0018】

図7において、30、31および32は入力がVGA100Hzの時の入力系の垂直同期信号IVD(IVD、IVD1またはIVD2)、水平同期信号IHD(IHD、IHD1またはIHD2)およびクロックICK(ICK、ICK1またはICK2)を示す。IVDは1周期が1/100secであり、かつブランキング期間の分α1を含んだ、IHDの(480+α1)本分の期間である。また、IHDの1周期は、ブランキング期間の分β1を含んだ、ICKの(640+β1)CLK分の期間である。

【0019】

33、34および35は入力がSVGA60Hzの時のIVD(IVD、IVD1またはIVD2)、IHD(IHD、IHD1またはIHD2)およびICK(ICK、ICK1またはICK2)を示す。IVDは1周期が1/60secであり、かつブランキング期間の分α2を含んだ、IHDの(600+α2)本分の期間である。また、IHDの1周期は、ブランキング期間の分β2を含んだ、ICKの(800+β2)CLK分の期間である。

【0020】

36、37および38は出力がXGA75Hzの時の出力系の垂直同期信号OVD、水平同期信号OHDおよびクロックOCKを示す。OVDは1周期が1/75secであり、かつブランキング期間の分α3を含んだ、OHDの(768+α3)本分の期間である。また、OHDは1周期がブランキング期間の分β3を含んだ、OCKの(1024+β3)CLK分の期間である。

【0021】

このように、入力系の水平同期信号、垂直同期信号および入力クロックは解像度によって異なる周期を持つ。図6の装置において、マイコン部9はこのIHD、IVDなどから解像度やフォーマットを判別してPLL回路8の分周比を設定し、それぞれのフォーマットに相当したICKを発生させる。一方、出力系は入力系の信号とは非同期で、出力クロックOCKからカウンタ回路11で一定のカウンタ値で作成されたOHD、OVDで動作する。このようにして、入力系と出力系の垂直周波数つまり、画面の更新周波数(フレームレート)の変換が行なわれる。

【0022】

図13の装置においては、入力系1(PC1入力)の場合、IHD1、IVD1、ICK1に同期させて、入力の信号処理系を動作させ、メモリAに記録する。入力系2(PC1入力)の場合は、まず、マイコン部9が、このIHD2、IVD2やDDC2でやりとりする情報により解像度やフォーマットを判別して、PLL回路8により、それぞれのフォーマットに相当したICK2を発生させる。次に、IHD2、IVD2、ICK2に同期させて、入力の信号処理系を動作させて、メモリBに画像の記録を行う。

【0023】

一方、出力系は入力系の信号とは非同期で、出力クロックOCKからカウンタ回路で一定のカウンタ値でOHD、OVDの作成を行ない、メモリAおよびメモリBからOCK、OHD、OVDに同期したタイミングで2系統の画像が読み出されるとともに、合成され、出力系の画像処理部および画像表示部に送られる。このようにして、入力系と出力系の解像度変換および垂直周波数つまり、画面の更新周波数(フレームレート)の変換が行なわれる。

【0024】

【発明が解決しようとする課題】

しかしながら、このフレームレート変換においては、図8に具体例を示すような動画像の画質劣化の問題点が存在する。図8の説明においても図13に関しては、PC1入力の系統もPC2入力の系統も同様の動作のため、同じ現象が生じる。ここでは、入力の垂直周波数と出力の垂直周波数の比が5:4の場合(例えば100Hzと80Hzなど)を例として示す。図8において、41は入力される連続した5枚(a〜e)のフレーム画像、42は同じ期間に表示装置に出力される連続した4枚(f〜1)のフレーム画像である。矢印が画面左から右方向へ移動する動画を表示している。

【0025】

同じメモリ領域に1画面を書き込みながら読み出しているため、(a)と(f)、(e)と(i)のようにたまたま1画面を書き換えるタイミングと読み出すタイミングが近い時は画面上に変化は現れないが、(g)、(h)のように画面を読み出している途中で画面が書き変わるタイミングになると、1画面の途中で前後の画面が切り替わり、動いている画像が画面の上下でずれてみえてしまう。これは“画像の追い越し”とよばれ、動画を表示する場合の画像の品位が落ちてしまう現象である。これは、逆に出力の垂直周波数が入力の垂直周波数より速い場合も同様の現象として現れる。

【0026】

この現象は、比較的画面に対して大きめな幾何学的な物体が水平に平行移動している時に目立ちやすいが、自然画などではあまり目立ちにくく、また、従来のPCはワープロ、表計算、描画といった静止画の用途が多いため、大きな問題にはならなかった。しかしながら、前述したようにPCといえども最近は動画を表示する機会が多くなり、また、幾何学的なグラフィックの移動する画面も多くなってきたため動画に対する要求も高くなってきている。

【0027】

このような問題の対策として、ダブルバッファリングという方法がある。これは、メモリ領域を1画面分ではなく、2画面分用意して1画面おきに交互にメモリ領域を切り換えて書き込むとともに、読み出しは画面の追い越しが起きないように、必ず読み出しているメモリ領域の走査が、そのメモリ領域の書込みの走査より先行する関係となるようにメモリ領域を選択するように制御する方法である。

【0028】

例えば、XGA(1024×768)の画素数のデータを格納する場合、図9のメモリマップに示すようにアドレス00000h〜BFFFFhの第1のメモリ領域にm、m+2、m+4・・・フィールドといった偶数番目のフィールドの入力画像を格納し、C0000h〜17FFFFhの第2のメモリ領域にm+1、m+3、m+5・・・フィールドといった奇数番目のフィールドの入力画像を格納する。図10にこの時のメモリの書込みと読み出しの動作のタイミングチャートを示す。61に入力の垂直同期信号(IVD)を、64に出力の垂直同期信号(OVD)を示す。ここでの説明も図13に関してはPC1入力とPC2入力に共通するので、IVDはIVD1またはIVD2(もしくは両方)を示し、また第1のメモリ領域と第2のメモリ領域はメモリAまたはメモリB(もしくは両方)にそれぞれ設けられると仮定する。

【0029】

IVD61が入る度にm、m+1、m+2・・・というように入力フィールドが更新され、またOVD64が入る度にn、n+1、n+2・・・というように出力フィールドが更新される。62に第1のメモリ領域の書込みが行なわれることを示す信号(WE1)を、63に第2のメモリ領域の書込みが行なわれることを示す信号(WE2)を、65に第1のメモリ領域の読み出しが行なわれることを示す信号(RE1)を、63に第2のメモリ領域の読み出しが行なわれることを示す信号(RE2)を示す。ここでは、アクティブHighで示す。

【0030】

書込みは前述したように、入力フィールドの偶数番目と奇数番目で交互に第1と第2のメモリ領域に書き込まれるが、読み出しは書込み途中が表示されないフィールドを選択して読み出されている。ここでは、入力に対して出力側が垂直周波数が高いので出力VDがHighになった時の入力フィールドが第1のメモリ領域を書き込んでいる場合、第2のメモリ領域を読み出し、第2のメモリ領域を書き込んでいる場合、第1のメモリ領域を読み出すように制御して、追い越し現象が現れないようにしている。出力側の垂直周波数が低い場合は、入力のVD(IVD)と出力のVD(OVD)の関係をみながら、追い越しが起きないように制御する必要がある。いずれにしても、第1のメモリと第2のメモリの読み出しタイミングは入力と出力の周波数や、同期信号間の関係にあわせて、必ず読み出しているメモリ領域の走査が、そのメモリ領域の書込みの走査より先行する関係となるようにメモリ領域を切り換えるように設定される。

【0031】

しかしながら、このダブルバッファリング方式においても、以下に示すような動画上の問題点がある。

ダブルバッファリングの場合、現在書込み途中のメモリ領域を表示しないように、もう一方のメモリ領域を選択することから、例えば図11のように、入力画面71(a)〜(d)の、人が片手をまわしているような連続した動きの画面がある場合に、72(e)〜(i)のようにフレームレートを変換された出力のうち(e)と(f)のように、同じ画像が2フィールド連続する“フレームの二重化”や、図12のように、入力画面81(a)〜(d)のような画面がある場合に、82(e)〜(g)のようにフレームレートを変換された出力のうち(c)のように、相当するフィールドがなくなる“フレームの欠落”が生じてしまう。

【0032】

また、ダブルバッファリングとは別の方法で動画質を改善する方法としては、入力の垂直周波数と出力の垂直周波数を同期させる方法がある。XGA(1024×768画素)の表示部の場合、VGA(640×480)やSVGA(800×600)などの50Hzの入力信号が入ってきた場合はXGA50Hzに変換して表示を行ない、また、100Hzの入力信号が入ってきた場合はXGA100Hzに変換して表示を行なう方法である。

【0033】

こうした場合、メモリの書込みと読み出しの周期が一致するため、動きの問題点は発生しない。ところが、入力の信号源が50Hzなど低い周波数の場合は、液晶のようにフィールド毎に極性を反転して表示している装置などの場合、同じ極性でみるとさらに半分の周波数となるため、画面の書き換え周期が遅くなり、面全体がちらついてみえるフリッカ現象となってしまう画質上の問題がある。また、100Hzのように速い周波数になると、VGAのように画素数が低い場合には大した速度でなくても、XGAの画素数の出力に変換すると入力の2.6倍程度のスピードが要求されるため、出力系全体の動作速度を高くしなくてはならない問題点がある。例えば、XGAの60Hzでは65MHz程度のクロックレートのものが、XGA100Hzでは108MHz程度となり、100MHzを越えてしまう。解決のためには、高い動作速度の部品の採用や新規な部品の開発、動作系統を分割して速度を下げるなどの回路構成にする必要などがあり、コストの上昇や回路規模の増大につながってしまう。

【0034】

上記の問題に加えて、入力が2系統以上であることゆえの問題点も存在する。図13の例で示したように、入力系はそれぞれの入力信号と同期して動作するため、PC1入力とPC2入力は基本的に非同期である一方で、出力系は同一のタイミングで2系統の画像を1画面に合成して出力するために、入力と出力の垂直周波数を同期させる方法はどちらか1系統に対しては実施できるが、同時に2系統に対しては適用できない。この問題は、入力系統が増加し、それぞれの動画の画質を重視するマルチ画面用途に対して大きな問題になる。

【0035】

さらに、複数の画像入力に対しては、動画の画質同様に、色や明るさ、コントラストなど、様々な画質特性面でマルチ画面特有の、いずれか1系統の入力系にしか最適化できないか、もしくは最適化する場合回路規模が増大する問題が発生する。

【0036】

ここで、画像のコントラストやブライト、ガンマ特性など画質の階調性に関わる問題の例を図13の回路で示す。

図14は、図13などの画像処理装置に入力する映像信号の1つとして水平方向に階調が8段階に変化するグレースケール信号を示す。14−1はグレースケールでの表示画面であり、14−2はこの時の信号である。14−2において、横軸は1水平走査期間の時間であり、縦軸は信号レベルである。14−3はこのときの入力信号の水平同期信号である。ここでは、1水平期間に、0%から100%までを8段階に等分に変化している。

【0037】

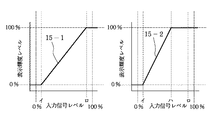

また、図15に、図13の画像表示部7における入力信号に対する表示画面の輝度特性を示す。この特性は、例えば透過型の液晶であれば、入力電圧に対する光の透過率特性であり、反射型のデバイスであれば、入力電圧に対する光の反射率特性である。この特性は、図13の画像表示部7によって適した特性が異なる。ここでは、15−1、15−2の2種類の特性を例に挙げて説明する。15−1、15−2において、横軸は画面表示部の入力信号のレベル、縦軸は表示輝度のレベルであり、イ、ロ、ハはそれぞれ入力信号のあるレベルを示している。

【0038】

ここで、図13のPC1、PC2の2系統の入力IDATA1、IDATA2に対して、それぞれ図16に示す16−1A、16−1Bのように信号レベルの異なる入力信号が入力されたとする。

また、図16には図15に15−1で示す特性の画像表示部を用いた場合の2系統の信号での表示輝度レベル16−4Aおよび16−4Bを示す。16−4A、16−4Bに示すように、同様の階調数の入力信号でもIDATA2の16−4Bが白100%黒0%がつぶれているものの、ほぼ輝度レベルとしては0%から100%まで出ているのに対して、もう一方の16−4Aは黒が60%程度まで白側にシフトし白く浮いた画像になっている。このため、同一の表示装置に2つの画面を同時表示すると、異なる黒レベルで、かつ、コントラストの異なる2つの画面が混在するため、非常に見づらい画面表示になる。

【0039】

ここで、図13の入力系画像処理部1(3−1)および入力系画像処理部2(3−2)にAGC(Auto−Gain−Control)回路を持たせた場合は、入力信号の直流レベルと振幅の異なる信号に対しては補正が行なわれる。しかし、ここで、画像表示部が図15の15−2の特性を有する表示部に交換された場合、この特性の変化に対しては信号の補正が行われない。

【0040】

図17および図18に、表示部の特性が図15の15−1の場合と15−2の場合の入力信号と輝度レベルを示す。図17および図18において、2系統の入力IDATA1およびIDATA2に入力する入力信号16−1A、16−1Bと、入力系画像処理部1(3−1)および入力系画像処理部2(3−2)のAGC回路通過後の各信号レベル16−2A、16−2B、およびこの信号を入力したときの表示部の輝度レベル16−4A、16−4Bを示す。図17の16−4A、16−4Bに示すように、15−1の入出力特性ではAGCにより階調は0%から100%まで出ている。

しかし、図18の16−4A、16−4Bに示すように、15−2の入出力特性では階調は0%から60%までしかでていなく、白側数段階が白つぶれ画像になってしまう。

【0041】

このような、画像表示部の特性の交換に対しては、図13の出力系画像処理部6に、画像表示部の特性に対する補正特性を持たせることが考えられる。図19に、表示部の特性が図15の15−2の場合の入力信号と輝度レベルを示す。2系統の入力IDATA1およびIDATA2に入力する入力信号16−1A、16−1Bと、入力系画像処理部1(3−1)および入力系画像処理部2(3−2)のAGC回路通過後の各信号レベル16−2A、16−2Bに加えて、出力系画像処理部通過後の各信号レベルを16−3A、16−3Bに、この信号を入力したときの表示部7の輝度レベルを16−4A、16−4Bに示す。

【0042】

このように、各信号の入力系画像処理部に入力信号の補正特性を持ち、出力系画像処理部に表示部の補正特性を持たせることにより、各入力信号のレベル差や、表示部の特性ばらつきの影響の少ないマルチ画面表示が実現される。補正特性としては、明るさ(ブライト)、明暗(コントラスト)、ガンマ特性、およびそれらの各色の系での差から生じるホワイトバランスなどがある。

【0043】

しかしながら、このように、入力系と出力系の両方に画像信号の補正特性を設けることは、同様の回路を複数用意することになり、回路規模、調整項目数が増加し、コストの増大を招く。これは、特に入力数が多い構成において問題になる。

さらに、こうした構成は、特性補正のためのデジタル処理系を2回以上通すことにより、画像の劣化も招く。図20に、この説明のための概念図を示す。図20において、x軸は入力信号のレベルを、y軸は出力信号の入力レベルを示す。この図では8ビット256段階のデジタル処理系での、▲1▼y=xの入出力特性に対して、▲2▼y=x2 の特性1のテーブルと▲3▼y=x1/2の特性2のテーブルを通過させた後の▲4▼y=[x2 ]*[x1/2]≒xの入出力特性を示している。本来であれば、▲4▼と▲1▼は一致するはずであるが、▲2▼の特性1と▲3▼の特性2の演算通過の各段階で出力は8ビットに規格化されるため、その度に演算誤差が発生して、合成後の▲4▼では、0から50程度のxに対してのyのビット誤差が大きくなっている。

【0044】

こうしたことを、従来例に当てはめて考えると、入力系で▲2▼のような特性変換を与えて、出力系で▲3▼のような特性変換を与えることに相当し、この場合、出力画像の黒レベルの階調性が劣化し、画像に疑似輪郭のような画質劣化が生じることになる。

この現象を避けるために、演算ビットを増加させる方法もあるが、コストや処理系の規模の増大を招く。

【0045】

このように、従来、複数の入力信号源の画像を同じ表示部に表示するマルチ画面表示において、表示部の特性の変化に対して、異なる入力画像の特性を同じ表示特性に変換する構成は規模が大きくなりコストが増大する問題があった。また、回路構成上ビット誤差の大きな回路となり、画質劣化を招く問題を有していた。このため、容易に各入力系統の明るさやコントラスト、階調性、色などを揃えられなかった。

【0046】

また、AGC回路を入力画像処理装置に持たせた場合は、信号のダイナミックレンジは確保できるが、自動で補正をするため、本来表示すべき信号レベルまでも補正を行い、信号送出側の意図を無視してしまう問題も存在した。

【0047】

本発明の目的は、安価かつ簡単な回路構成で動画像の画質を改善した画像処理装置を実現することにある。また、複数の入力信号源に対しても、柔軟に動画質に対して適した処理を行なえる画像処理装置を実現することにある。

【0050】

【課題を解決するための手段および作用】

上記の目的を達成するため本発明に係る第1の画像処理装置は、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、第1のクロックと第1の画像同期信号により、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部とからなる画像処理装置において、前記同期制御部は、第2のクロックを分周して、第1の画像同期信号とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号を同期化して作成した第4の画像同期信号を作成するとともに、前記第3の画像同期信号と前記第4の画像同期信号を切り換えて、前記第2の画像同期信号として出力することを特徴とする。これらの第3の画像同期信号と前記第4の画像同期信号の切り換えは、出力する画像の使用目的に応じて選択される。

【0051】

本発明は、複数の入力系信号処理部を有し、そこに入力される画像信号を適宜合成して表示する場合にも適用可能である。本発明に係る第2の画像処理装置は、第1の画像同期信号に同期する第4の画像同期信号として、複数の第1の画像同期信号のそれぞれに同期する複数の第4の画像同期信号を作成し、作成した複数の第4の画像同期信号と第1の画像同期信号とは非同期の第3の画像同期信号の中から1つの画像同期信号を選択し、前記第2の画像同期信号として出力する。第2の画像同期信号となる画像同期信号は、出力する画像の使用目的、または前記複数の入力系信号処理部に入力する信号の動画の有無や割合、あるいは前記複数の入力系信号の用途や種類に応じて、前記第3の画像同期信号と前記第4の画像同期信号群の中の1つを選択する。この第2の局面においては、さらに、前記複数の入力系信号処理部に入力する信号源に対して、入力する画像信号を設定、あるいは再設定する要求を出力する手段を設け、前記第3の画像同期信号と前記第4の画像同期信号群の中から選択して出力する第2の画像同期信号に同期していない任意の入力信号源に対して、第2の画像同期信号に同期する要求を出力する構成とすることが好ましい。 本発明に係る第3の画像処理装置は、複数の入力系信号処理部と、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、前記複数の入力系信号処理部に入力される複数の入力信号に同期した複数の第1のクロック群と第1の画像同期信号群を用いて、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部からなる画像処理装置において、前記同期制御部は、第2のクロックから分周され、第1の画像同期信号群とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号群をそれぞれ同期化して作成した第4の画像同期信号群を作成するとともに、前記第3の画像同期信号と前記第4の画像同期信号群の中から一つの画像同期信号を選択して、前記第2の画像同期信号として出力し、前記画像処理装置は、前記複数の入力系信号処理部に入力する信号源に対して、入力する画像信号を設定、あるいは再設定する要求を出力するとともに、前記第3の画像同期信号と前記第4の画像同期信号群の中から選択して出力する第2の画像同期信号に同期していない任意の入力信号源に対して、第2の画像同期信号に同期する要求を出力する手段を有することを特徴とする。

【0052】

本発明は、CRTをはじめ透過型、反射型の表示装置、液晶表示装置、PDP(プラズマディスプレイ)や電荷放出型表示装置などの画像表示装置、CCDやCMOS型の2次元撮像素子、およびビデオ信号のキャプチャーボード等のデジタル画像処理を伴なうあらゆる画像処理装置に適用可能である。

【0057】

【実施例】

以下、本発明の実施例について、図面を用いて説明する。

(実施例1)

本発明の第1の実施例の説明のためのブロック図を図1に示す。同図において、1−1はアナログの画像信号の入力端子であり、1−2は入力信号の水平同期信号(IHD)入力端子であり、1−3は入力信号の垂直同期信号(IVD)入力端子である。2はADコンバータであり、入力されたアナログ画像信号をnビットのデジタル信号に変換する。3は入力系画像処理部、4はメモリ制御部、5は画像データを格納するメモリ部、6は出力系画像処理部であり、7は画像表示部である。20−1、20−2、20−3、20−4は各部へnビットのデジタル信号を伝送するデータバスである。21はメモリの制御線とアドレス線から構成される制御バスであり、22はメモリのデータバスである。

【0058】

また、8はPLL回路であり、ICKは入力水平同期信号IHDに同期したクロックである。12は発振回路であり、出力系クロックOCKを発生する。9はマイクロコンピュータ(μCOM)部であり、19はm本の、各部を制御する制御バスである。

【0059】

デジタル画像信号はメモリ部5に格納される前に入力系画像処理部3で画質の調整や画像の縮小変換等の処理を行なわれ、メモリ制御部4に転送される。メモリ制御部4では入力同期信号(IHD、IVD)と入力系クロックICKに対応したタイミングでメモリ部5に画像データを格納するとともに、出力系クロックOCK、水平同期信号OHD、垂直同期信号OVDのタイミングで画像データをメモリ部5から読み出し、出力系画像処理部6にデータを転送する。画像処理部6では、画質の調整や、画像の拡大変換などが行なわれるのは図6の従来例と同様である。

【0060】

図1においては、10が同期制御部であり、出力のフレームレートを決定するブロックである。ここには、入力の同期信号IHD、IVDと出力系クロックOCKが入力し、出力系の水平同期信号OHD、垂直同期信号OVDと書込みフィールド制御信号WEと読み出しフィールド制御信号REを出力する。また、これらの制御をマイコンのバス19によりコントロールする。

【0061】

図2にこの同期制御部10の回路構成例を示す。

図2において、901はOCKをカウントするHカウンタであり、902はOHDをカウントする第1のVカウンタであり、904はIHDをカウントする第2のVカウンタであり、905、906、907はカウンタ901、902、904それぞれの出力をデコードして任意のパルスを作成する第1、第2、第3のデコーダである。903と910はD入力フリップフロップ(D−FF)である。また、908および909は入力のパルスを切り換えて出力する第1および第2のスイッチ(SW1およびSW2)である。また、911は論理を反転するインバータである。また、912がIHDの、913がIVDの、914がOCKの入力端子であり、915がOHDの、916がOVDの、917がREの、918がWEの出力端子である。また、919、920がマイコンの制御バスのうち、各SWを切り換える信号線の入力端子であり、921、922、923は第1〜第3のデコーダの値を設定するためのマイコンの制御バスの入力端子である。

【0062】

925、926、927は各カウンタのクロック入力端子であり、930、931、932は各カウンタのクロックのイネーブル端子であり、934、935、936は各カウンタの出力端子である。950はHカウンタのリセット端子である。また、出力端子934、935、936、937は各デコーダの入力端子にも接続しており、938、939、940は各デコーダの出力端子である。

【0063】

928、929は各D−FF903、910のクロック端子であり、933はクロックのイネーブル端子、941、942はD−FFの入力端子である。また、943、944はD−FFの非反転出力端子であり、952は反転出力端子である。

【0064】

947、948は第1のスイッチ908の入力端子IN1、IN2であり、949は出力端子である。940、945、946は第2のスイッチ909の入力端子IN3、IN4、IN5であり、951は出力端子である。

【0065】

ここで、Hカウンタ901とデコーダ905でOCKをカウントおよびデコードしてOHDを作成し、915から出力するとともに、作成したOHDを第1のVカウンタ902とデコーダ906でカウントおよびデコードして第1のスイッチの入力端子947に結果を出力する。一方、入力したIVDはD−FF903を通過し、第1のスイッチ908の入力端子948に入力する。入力端子947と948に入力した信号は、端子919に入力されるマイコンからの制御信号により動作モードによって選択、切り換えされて、どちらか一方が端子916にOVDとして出力される。

【0066】

また、D−FF903の出力はD−FF910のイネーブル端子933にも入力し、端子933にIVDが入力する度に極性が反転するメモリ書き込み信号WEを端子918に出力する。また、このメモリ書き込み信号WEとその反転論理信号とが、メモリ読み出し信号の候補信号として第2のスイッチ909の入力端子945、946に入力する。さらにIHDのカウンタ904とOHDのカウンタ902との両者の出力結果をデコーダ907でデコードして、両者の関係で定まる信号もメモリ読み出し信号の候補信号として第2のスイッチ909の入力端子940に入力し、端子920へのマイコンからの制御信号にしたがって、動作モードによってこの3入力の1つが選択されて、メモリ読み出し信号REとして端子917から出力される。

【0067】

この実施例における、入力信号の周波数に対する動作モードと第1および第2のスイッチの切り換えて出力される信号との対応表を表1に、またその時のタイミングチャートを図3に示す。

【0068】

【表1】

【0069】

表1には、入力信号の垂直周波数の範囲に対して、出力の垂直周波数が入力信号に同期しているかどうかと、ダブルバッファリングするかどうか、およびその動作を実現するための図2におけるSW1、SW2の切換出力する信号を示している。

【0070】

また、図3においてA1、A2、A3、A4、A5はそれぞれ入力垂直周波数が100Hz、80Hz、75Hz、60Hz、50Hzのときの入力垂直同期信号IVDであり、A6、A7は入力周波数が80Hzのときの出力垂直同期信号と出力水平同期信号である。A8、A9は入力周波数が75Hzのときの出力垂直同期信号と出力水平同期信号である。A10、A11は入力周波数が60Hzのときの出力垂直同期信号と出力水平同期信号である。A12、A13は入力周波数が50Hzのときと100Hzのときの出力垂直同期信号と出力水平同期信号である。

【0071】

本実施例では、使用頻度の高い60Hzから80Hzまでの垂直周波数の入力信号に対応して出力の垂直同期信号OVDを入力の垂直同期信号IVDに同期させるモードを、それ以外の入力信号については、入力の垂直同期信号には無関係に出力の垂直同期信号を発生させるモードを選択する構成をとっている。

【0072】

このため、60Hzから80Hzまでの垂直周波数の入力信号に対応しては、ダブルバッファリングを用いず(用いてもかまわない)、入力の垂直同期と同期させる方法で動画に対して追い越し、フレームの二重化、および欠落のない画質を実現している。このとき、第1のスイッチはIN2側、第2のスイッチはIN5(IN4でも可)を選択する。

【0073】

また、60Hz未満の場合は、フリッカ防止のため、SW1をIN1側としてダブルバッファリングによる動画質の改善を行ない、入力に対しては非同期とする。入力の垂直周波数が出力の周波数より低い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとすればメモリ読み出し走査を書込み走査が追い越すことはないので、SW2をIN4側としている。

【0074】

一方、80Hz以上では出力系の動作スピードを抑えるために、SW1をIN1側としてダブルバッファリングによる動画質の改善を行ない、入力に対しては非同期とする。入力の垂直周波数が出力の周波数より高い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとしても、メモリ読み出し走査を書込み走査が追い越すことがあるので、SW2をIN3側として、入力のIHDと出力のOHDの関係から追い越しが生じないタイミングでメモリ読み出し信号を出力している。

【0075】

このとき、図1の発振器(OSC)12の周波数は、出力系の最高垂直周波数であるXGA80Hzの時のクロック周波数にあわせて設計される。すなわち、1フィールド=1V期間=1S/80=12.5mSであるから、例えば、1V=(768+α)H=808Hとして1H期間=15.5μS、1H=(1024+α)CLK=1344CLKとして1CLK=11.5nSとなり、発振器12の周波数は、1/11.5nS=87MHzとなる。図3において、A2の80HzのIVDが入力した場合、その出力OVD=IVDとなり、OVDの1周期間のIHDは768+α=808個に設定される。

【0076】

また、A3、A4の75Hz、60HzのIHDが入力した場合、対応するOHDであるA8、A9はIHDと同周期になり、また、OVDの1周期間のOCKおよびOHDの周期は一定に保たれるため、OVD1周期間のOHD数が比例して増加する。この768+α=808本を越える分の期間についてはブランキング期間が増加すると考えて表示部を駆動している。

【0077】

一方、入力IHDが100HzのA1や50HzのA5の場合は、入力と非同期に出力の垂直周波数を設定するため、A12のOVD、A13のOHDに示すように80Hzの時と同じOVD、OHD周期でかつ、入力と非同期に自走させている。60〜80Hzという周波数は、現行のPCやWS(ワークステーション)やDTV(デジタルテレビ)等、最も広く普及している周波数帯である一方、TVからの動画の映像ソースもNTSCが60Hzのため、この範囲に入ってくるため使用頻度が非常に高く動画を最優先させる意味は高い。

【0078】

一方、50Hzなど、低い周波数のフリッカ現象は、動画、静止画に関らず非常に見づらい画質劣化となる点から、ダブルバッファリングのような簡易的に動画に強い方式をとる方法で、フリッカ防止と動画画質向上を両立させている。

【0079】

また、100Hzのように高い垂直周波数の信号に関しては、100MHzを超える動作速度が回路的な負担が大きいことを重視し、ダブルバッファリングのような簡易的に動画に強い方式をとる方法で、コスト削減と安定動作を動画画質向上と両立させている。特に液晶やPDPなどの表示素子は駆動電圧が10数Vから数十Vという高電圧が必要とされるため、1画素あたりの速度が高速化すると、映像信号系やドライバ回路が非常に高い動作帯域やスルーレートが必要とされる。現状においても、こうした高い速度の駆動に対しては追従できない部分を、複数に分割駆動しているが、さらなる出力系の高速化は高速な部品ヘの変更、新規部品の開発、分割数の変更などの回路変更によるコストアップばかりでなく回路の動作マージンを狭くし、安定的な動作を困難にする要因となる。また、この問題はSXGAやUXGAといった、現状よりもさらに数倍画素数の多い表示素子などを駆動する場合に、特に重要になる。将来の高画素化のためにも、コスト削減と安定動作が動画画質向上と両立できる点が重要になってくる。

【0080】

本実施例のような構成をとることで、システムの全体の動作として、動画に強い構成をとり、特に使用頻度の高い垂直周波数帯で動画の問題のない動作を実現し、また、その他の垂直周波数帯では簡易的に動画に強い動作を行なうことで回路構成の簡素化、安価化を実現している。

【0081】

ここでは、使用頻度の高い垂直周波数帯域以外の周波数をダブルバッファリングさせたが、ダブルバッファリングは、メモリ領域を倍必要とすること、またそのための制御回路部分が必要となるため、機能として省くことも考えられる。特定の垂直周波数帯域は入力の垂直周波数に同期させる一方で、その帯域以外の使用頻度は低いと判断し、製品として動作はするが、動画質は改善しない単なる非同期な動作に切り換えることも安価な製品を提供する意味で本発明のひとつの実施の形態である。

【0082】

また、本実施例では、入力信号の垂直周波数により、出力系を入力系と同期させるか非同期とするかを選択したが、本発明の第1の実施形態は出力系を入力系と同期させるか非同期とするかを選択する回路を有することが特徴であり、切り換える基準は入力信号の垂直周波数以外にも、入力信号のフォーマットのほかの項目であったり、システムの動作モードであったり、ユーザー設定などによる場合も含んでいる。実施例2は、このような基準として、動画か静止画かを選択の基準にした例を示す。

【0083】

(実施例2)

実施例1では、入力信号の垂直周波数によって出力系のV同期を入力同期信号に同期させるか非同期にするかを切り換える例を示したが、実施例2では、動作目的や用途で入力の同期信号に同期させるか非同期にするかを切り換える例を示す。図4に実施例2のブロック図を示す。

【0084】

ここでは、入力系が2系統になり、メモリ制御部で合成している。これは、図5に示すように、例えば画面全体(C1)にPCのグラフや表などの出力画面を表示して、子画面部(C2)にTV電話の画像などの動画を出力するなどの、異なる入力源の合成画面を想定した回路構成である。こうした場合、両者の信号には一般的に同期関係がない。また、動画か静止画かは接続される入力源によって多種多様な組み合わせとなる。

【0085】

図4において3−1は入力A系統の画像処理部であり、1−4はqビットのデジタルの画像信号の入力端子であり、1−5は入力信号の水平同期信号(IHD1)入力端子であり、1−6は入力信号の垂直同期信号(IVD1)入力端子、l−7は入力信号の同期クロック(ICK1)入力端子である。また、3−2は入力B系統の画像処理部であり、1−8はアナログの画像信号の入力端子であり、1−9は入力信号の水平同期信号(IHD2)入力端子であり、1−10は入力信号の垂直同期信号(IVD2)入力端子である。2はADコンバータであり、B系統のアナログ信号をnビットのデジタル信号に変換する。4−2はメモリ制御部、5は画像データを格納するメモリ部、6は出力系画像処理部であり、7は画像表示部である。20−5、20−6はqビットのデジタル信号のデータバスであり、20−7、20−8はnビットのデジタル信号を伝送するデータバスである。また、20−9、20−10はrビットのデジタル信号を伝送するデータバスである。21はメモリの制御線とアドレス線から構成される制御バスであり、22はメモリのデータバスである。

【0086】

さらに、1−11、1−12はそれぞれ入力A系統、B系統のDDC(Display Data Cannel)端子であり、ディスプレイの情報を入力信号源に伝える端子である。なお、DDCは、VESA(Video Electronics Standards Association)により規格化されたコンピュータ用ディスプレイとホストシステム間の通信の標準である。

【0087】

また、8はPLL回路であり、ICK2は入力B系の水平同期信号IHD2に同期したクロックである。12は発振回路であり、出力系クロックOCKを発生する。9はマイクロコンピュータ(μCOM)部であり、19はm本の、各部を制御する制御バスである。

【0088】

デジタル画像信号はメモリ部5に格納される前に入力系画像処理部3−1、3−2で画質の調整や画像の縮小変換等の処理を行なわれ、メモリ制御部4−2に転送される。また、入力系画像処理部3−1、3−2では動き検出も行ない、その結果をマイコンのバス19を介してマイコン9に送る。メモリ制御部4では入力同期信号(IHD1、IHD2、IVD1、IVD2)と入力系クロックICK1、ICK2に対応したタイミングでメモリ部5に画像データを格納するとともに、出力系クロックOCK、水平同期信号OHD、垂直同期信号OVDのタイミングで画像データをメモリ部5から読み出し、出力系画像処理部6にデータを転送する。画像処理部6においては、図6の従来例と同様に、画質の調整や、画像の拡大変換などが行なわれる。

【0089】

図4において、10が同期制御部であり、出力のフレームレートを決定するブロックである。ここには、2系統の入力系同期信号IHD1、IVD1、IHD2、IVD2と出力系クロックOCK18が入力し、出力系の水平同期信号OHDおよび垂直同期信号OVDと、書込みフィールドの制御信号WEと、読み出しフィールド制御信号REとを出力する。また、これらの制御をマイコンのバス19によりコントロールする。

【0090】

ここで、同期制御部10の動作例を表2に示す。実施例1同様、出力の垂直同期信号をスイッチを用いて、入力に同期か非同期かを切り換える。実施例1と異なるのは、入力が2系統になった点と、周波数によって同期関係を切り換えるほかに、入力源2系統の動画と静止画の状態によって同期関係を切り換える点である。

【0091】

【表2】

【0092】

前述の入力の画像処理部3−1、3−2の動き検出の結果を受けて、マイコン部9からの制御信号により、表2のように動作モードを切り換える。一方が動画で一方が静止画の場合は、動画のほうの入力垂直同期信号にOVDを同期させる。また、2系統とも動画の場合には、IVD1とIVD2を比較し速い周期の垂直同期信号にOVDを同期させる。また、据置のTV会議システムなど、A系統がPCでB系統がTV出力などのように用途が固定している場合には、マニュアル設定でA系統のIVD1に同期させるか、B系統のIVD2に同期させるか、A、Bとも非同期にOVDを発生させるかを決定できるようにしてある。

【0093】

さらに、本実施例では、DDCなどのディスプレイ側の情報をPCなどの入力信号源に伝える制御線を用いて、以下に述べる制御も行なう。すなわち、最初の状態で、一方のみが動作し、一方が接続されていない場合、例えばB系統のみが接続、動作しているとすると、同期制御部10は実施例1同様、IVD2に対してOVDを表1のような動作に設定する。

【0094】

次に、後から1系統が接続される場合に(この場合A系統)、マイコンは現在のOVD周期と同じ垂直周波数の信号をA系統のDDC端子1−11を介し入力信号源に対して要求する。これを受けたA系統の入力信号源は、要求された垂直周波数の信号に設定を行ない、結果として入力の2系統とも同じ周波数となり、両方の画像が動画に対して強い出力設定にすることが可能にできる。

【0095】

また、新規のA系統がDDCを受け付けない場合は、マイコン部が判断を行ない、後に接続されたA系統のIVD1に同期した設定に出力同期OVDを再設定する一方、このOVD周期と同じ垂直周波数の信号をB系統のDDC端子1−12を介してB系統の入力信号源に対して要求する。これを受けたB系統の入力信号源は、要求された垂直周波数の信号に再設定を行ない、入力の2系統が同じ周波数に設定される。

【0096】

このような構成をとることで、複数の異なる周期の入力信号が混在するシステムにおいても、出力系の構成は1系統のクロックで動作させながら、動画に強い構成を簡単で安価な回路構成で実現することができる。

【0097】

(実施例3)

図21は本発明を適用したディスプレイの第3の実施例として、1系統はデジタルのコンピュータ画像信号の入力であり、もう1系統はアナログのコンピュータ画像信号の入力である2系統のPC入力を有し、フレームメモリの出力を制御して合成を行ない、1系統の画像表示部に2画面のマルチ画面表示を行なう画像表示装置の画像処理部のブロック図を示す。

【0098】

同図において、1−1aは1系統めのqビットのデジタルのコンピュータ画像信号(IDATA1)の入力端子である。ここでは、本来、赤、青、緑(RGB)の3系統あるはずであるが、構成の説明を簡単にするため、1系統で示している(以下同様)。1−1bは入力信号の水平同期信号(IHD1)入力端子であり、1−1cは入力信号の垂直同期信号(IVD1)入力端子である。1−1dは画像信号のクロック(ICK1)入力端子であり、1−1eはDDC信号(DDC1)の入出力端子である。20−1a−1、20−1a−2は各部へqビットのデジタルの画像信号を伝送するデータバスである。また、20−1b、20−1c、20−1d、20−1eは、それぞれ、IHD1、IVD1、ICK1、DDC1の信号線である。

【0099】

1−2aは2系統めのアナログのコンピュータ画像信号(IDATA2)の入力端子である。1−2bは入力信号の水平同期信号(IHD2)入力端子であり、1−2cは入力信号の垂直同期信号(IVD2)入力端子である。1−2eはDDC信号(DDC2)の入出力端子である。

【0100】

2はADコンバータであり、アナログの画像信号(IDATA2)をnビットのデジタル信号に変換する。また、8はPLL(Phase Locked Loop)回路であり、1−2bから入力した水平同期信号(IHD2)に同期したPC2側の入力系のクロック(ICK2)を発生する。

【0101】

20−2a−0はアナログの信号線であり、20−2a−1、20−2a−2はnビットのデジタルの信号線である。また、20−2b、20−2c、20−2d、20−2eは、それぞれ、IHD2、IVD2、ICK2、DDC2の信号線である。

【0102】

3−1はPC1の入力系の画像処理部1であり、3−2はPC2の入力系の画像処理部2処理部である。

10−3が画像比較部であり、20−REF−1、20−REF−2が、入力系画像処理部1および入力系画像処理部2から出力される画像信号から比較用に抽出された比較信号の信号線である。

【0103】

4は2系統の入力画像処理部から入力された画像信号を、一旦メモリに記憶し、マルチ画面として出力するために画像を合成して、出力系の画像処理部に出力する制御を行なうメモリ制御部である。5−1、5−2は入力系PC1、PC2にそれぞれ対応したフレームメモリ(メモリA、メモリB)である。21−1、21−2はそれぞれメモリA、Bの制御バスであり、22−1、22−2はそれぞれメモリA、Bのデータバスである。

6は出力系の画像処理部であり、また、7は液晶やプラズマディスプレイ、CRTなどの画像表示部である。

【0104】

1−fは画像表示部のデジタルデータ(ODATA)の画像表示部の入力端子であり、1−gは出力信号の水平同期信号(OHD)の画像表示部の入力端子であり、1−hは出力信号の垂直同期信号(OVD)の画像表示部の入力端子である。1−iは、出力画像信号のクロック(OCK)の画像表示部の入力端子であり、1−jは、マイコンバス(MB)の画像表示部の入力端子である。また、1−sは、画像表示部に対するDDC信号(DDC3)の入出力端子であり、20−s−1、20−s−2はこのDDC3の信号線である。20−f−1、20−f−2、20−f−3はkビットのデジタルの画像データ(ODATA)の信号線である。

【0105】

12は発振回路であり、出力系のクロック(OCK)を発生する。20−i−1、20−i−2はOCKの信号線である。

【0106】

10−2が同期制御部であり、20−WE−1はメモリAの書込みフィールドの制御信号WE―A、20−RE−1はメモリAの読み出しフィールド制御信号RE−A、20−WE−2はメモリBの書込みフィールドの制御信号WE―B、20−RE−2はメモリBの読み出しフィールド制御信号RE−Bである。また、20−g−1、20−g−2は出力系の水平同期信号(OHD)の信号線である。20−h−1、20−h−2は出力系の垂直同期信号(OVD)の信号線である。

【0107】

9はシステムを制御するマイコン部であり、19−1および19−2はマイコンから各部への制御線およびデータ線からなるマイコンバス(MB)である。

【0108】

画像の入力端子1−1aから入力したデジタル画像信号は、5−1のメモリ部Aに格納される前に3−1の入力系画像処理部1で画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。また、入力系画像処理部1から画質を比較するための信号が、マイコンで選択されて画像比較部に送出される。

【0109】

また、画像の入力端子1−2aから入力したアナログ画像信号は、PLL回路8で作成されたクロックに同期して、ADコンバータ2でデジタルデータに変換される。こうして得られたデジタル画像信号は、5−2のメモリ部Bに格納される前に3−2の入力系画像処理部2で画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。

また、入力系画像処理部2から画質を比較するための信号が、マイコンで選択されて画像比較部に送出される。

【0110】

4のメモリ制御部では、IDATA1からの信号を、入力同期信号(IHD1、IVD1)と入力系クロックICK1に対応したタイミングで5−1のメモリ部Aに画像データを格納するとともに、IDATA2からデジタルに変換された信号を、入力同期信号(IHD2、IVD2)と入力系クロックICK2に対応したタイミングで5−2のメモリ部Bに画像データを格納する。

【0111】

本実施例では、このメモリ部A、メモリ部Bの双方ともダブルバッファリング可能なメモリ領域を確保し、同期制御部のメモリ書き込み信号と読み出し信号(20−WE−1、20−WE−2、20−RE−1、20−RE−2)で書き込みメモリ領域および読み出しメモリ領域を切替え制御する。

【0112】

さらに、出力系のクロックOCKと同期制御部からの水平同期信号OHD、垂直同期信号OVDに同期して所定の画像の大きさ、表示位置の関係に合ったタイミングで2つの画像データを5−1と5−2のメモリ部から読み出して、6の出力系画像部にデータを転送する。

【0113】

6の画像処理部では、画質の調整や、画像の拡大変換などが行なわれる。最後に画像表示部にこれらの画像データと同期信号、クロックが伝送され画像表示が行なわれる。

【0114】

本実施例においては、10−2の同期制御部において、出力として選択されたフレームレートにあわせて、出力の同期信号とメモリ制御信号を作成、選択切替えを行なう。ここには、入力の同期信号IHD1、IHD2およびIVD1、IVD2と出力系のクロックOCKが入力し、出力系の水平同期信号OHD(20−g−1)、垂直同期信号OVD(20−h−1)とメモリAの書込みフィールドの制御信号WE―A(20−WE−1)と読み出しフィールド制御信号RE―A(20−RE−1)およびメモリBの書込みフィールドの制御信号WE―B(20−WE−2)と読み出しフィールド制御信号RE―B(20−RE−2)を出力する。また、これらの制御をマイコンのバス19−1によりコントロールする。

【0115】

また、本実施例においては、10−3の画像比較部において、各入力系の画質の比較を行ない、マイコンが出力系と各入力系の画質制御を行なうための情報の出力を行なう。入力系画像処理部1および入力系画像処理部2から出力される画像信号から比較用に抽出された比較信号20−REF−1、20−REF−2から得られた比較情報の演算結果がマイコンバス19−1を経由してマイコンに伝達される。

【0116】

本実施例において、マイコン部では各入力系の同期信号IHD1、IHD2、IVD1、IVD2が入力され、同期信号による各入力信号の動作タイミングの比較を行なうことに加えて、DDC3やほかの通信経路、初期情報で与えられる表示部の特性や条件とも加味した比較を行ない、システムの動作タイミングを決定して同期制御部を制御するとともに、DDC1、DDC2を介して入力信号源の動作タイミングの制御も行なう。また、画質については、画像比較部から得られる各入力系の画質特性の比較結果に加えて、DDC3や他の通信経路、初期情報等で与えられる表示部の特性や条件との比較を行ない、内部の各画像処理部(入力系画像処理部1、入力系画像処理部2、出力系画像処理部)を制御するとともに、DDC1、DDC2を介して入力信号源の画質制御を行なう。

【0117】

これにより、複数の入力系の様々なフォーマットと画質特性の入力画像を1画面上に合成してマルチ画面表示を行なう際に、各入力系と出力表示部の画質や動画の特性に応じて、システム全体の動作タイミングと画質が最適化される。

【0118】

図22にこの同期制御部10−2の回路構成例を示す。

図22において、901はOCKをカウントするHカウンタであり、902はOHDをカウントする第1のVカウンタであり、904−1はIHD1をカウントする第2のVカウンタである。904−2はIHD2をカウントする第3のVカウンタである。

【0119】

903−1、903−2と910−1、910−2、957−1、957−2はD入力フリップフロップ(DFF)であり、905、906、907−1、907−2はそれぞれのカウンタ出力をデコードして任意のパルスを作成する第1、第2、第3、第4のデコーダである。また、908、909−1、909−2は入力のパルスを切り換えて出力する第1(SW1)、第2(SW2−1)、第3(SW2−2)のスイッチである。また、911−1、911−2は論理を反転するインバータである。

【0120】

また、912−1、912−2がIHD1、IHD2の、913−1、913−2がIVD1、IVD2の、914がOCKの入力端子であり、915がOHDの、916がOVDの、917−1、917−2がRE−A、RE−Bの、918−1、918−2がWE−A、WE−Bの出力端子である。また、919、920−1、920−2がマイコンの制御バスのうち、第1〜第3の各SWを切り換える信号線の入力端子であり、921、922、923−1、923−2は第1〜第4のデコーダの値を設定するためのマイコンの制御バスの入力端子である。

【0121】

また、925、926、927−1、927−2は各カウンタのクロック入力端子であり、930、931、932−1、932−2は各カウンタのクロックのイネーブル端子であり、934、935、936−1、936−2は各カウンタの出力端子である。950はHカウンタのリセット端子である。また、各カウンタの出力端子934、935、936−1、936−2は各デコーダの入力端子953、954、955−1、955−2、956−1、956−2、937−1、937−2にも接続しており、938、939、940−1、940−2は各デコーダの出力端子である。

【0122】

また、928−1、928−2、929−1、929−2、958−1、958−2は各DFFのクロック端子であり、933−1、933−2、959−1、959−2はクロックのイネーブル端子、941−1、941−2、942−1、942−2、960−1、960−2はD入力端子である。また、943−1、943−2、944−1、944−2、961−1、961−2はDFFの出力端子であり、952−1、952−2は反転出力端子である。

【0123】

947、948−1、948−2は第1のスイッチ908の入力端子IN1、IN2−1、IN2−2であり、949は出力端子である。962−1、945−1、946−1は第2のスイッチ(SW2−1)909−1の入力端子IN3−1、IN4−1、IN5−1であり、951−1は出力端子である。962−2、945−2、946−2は第3のスイッチ(SW2−2)909−2の入力端子IN3−2、IN4−2、IN5−2であり、951−2は出力端子である。

【0124】

Hカウンタ901とデコーダ905でOCKをカウント、デコードしてOHDを作成し、端子915から出力するとともに、作成したOHDを第1のVカウンタ902とデコーダ906でカウント、デコードして第1のスイッチの入力端子947に結果を出力する。

【0125】

一方、入力したIVD1はDFF903−1を通過し、第1のスイッチの入力端子948−1に入力する。また、入力したIVD2はDFF903−2を通過し、第1のスイッチの入力端子948−2に入力する。入力端子947と948−1、948−2に入力した信号は、端子919のマイコンからの制御信号により動作モードによって選択、切り換えられて、どれか一つが端子916にOVDとして出力される。

【0126】

また、DFF903−1の出力はDFF910−1のイネーブル端子933−1にも入力し、端子933−1にIVD1が入力する度に極性が反転するメモリ書き込み信号WE―Aを端子918−1に出力する。また、DFF903−2の出力はDFF910−2のイネーブル端子933−2にも入力し、端子933−2にIVD2が入力する度に極性が反転するメモリ書き込み信号WE―Bを端子918−2に出力する。

【0127】

また、このメモリ書き込み信号WE―Aとその反転論理信号とが、メモリ読み出し信号の候補信号として第2のスイッチ(SW2−1)909−1の入力端子945−1、946−1に入力する。さらにIHD1のカウンタ904−1出力とIHD2のカウンタ904−2出力とOHDのカウンタ902出力の3者の値を、マイコンからの制御信号923−1で定まる関係でデコードしたデコーダ907−1の出力端子940−1からの信号も、メモリ読み出し信号の候補信号として第2のスイッチ(SW2−1)909−1の入力端子962−1に入力し、端子920−1のマイコンからの制御信号にしたがって、動作モードによってこの3入力のうち一つが選択される。この結果をOVDのタイミングでDFF957−1でラッチを行ない、メモリ読み出し信号RE―Aとして端子917−1から出力する。

【0128】

さらに、メモリ書き込み信号WE―Bとその反転論理信号とが、メモリ読み出し信号の候補信号として第3のスイッチ(SW2−2)909−2の入力端子945−2、946−2に入力する。さらにIHD1のカウンタ904−1出力とIHD2のカウンタ904−2出力とOHDのカウンタ902の3者の値を、マイコンからの制御信号923−2で定まる関係でデコードしたデコーダ907−2の出力端子940−2からの信号も、メモリ読み出し信号の候補信号として第3のスイッチ(SW2−2)909−2の入力端子962−2に入力し、端子920−2のマイコンからの制御信号にしたがって、動作モードによってこの3入力のうち一つが選択される。この結果をOVDのタイミングでDFF957−2でラッチを行ない、メモリ読み出し信号RE―Bとして端子917−2から出力する。

【0129】

この実施例における、入力信号の周波数に対する動作モードと各スイッチを切り換えて出力される信号との対応表を表3に示す。またその時のタイミングチャートは、前掲の図3と同様になる。

【0130】

【表3】

【0131】

表3には、2系統の入力信号の垂直同期信号(IVD1、IVD2)の周波数fIN1、fIN2の範囲に対して、出力の垂直周波数をいずれの入力信号に同期させるかどうかと、ダブルバッファリングするかどうか、およびその動作を実現するための図21におけるSW1、SW2−1、SW2−2の切換出力する信号を示している。

【0132】

また、図3においてA1、A2、A3、A4、A5はそれぞれ入力垂直周波数が100Hz、80Hz、75Hz、60Hz、50Hzのときの入力垂直同期信号IVD(IVD1やIVD2)であり、A6、A7は入力周波数が80Hzのときの出力垂直同期信号(OVD)と出力水平同期信号(OHD)である。A8、A9は入力周波数が75Hzのときの出力垂直同期信号(OVD)と出力水平同期信号(OHD)である。A10、A11は入力周波数が60Hzのときの出力垂直同期信号(OVD)と出力水平同期信号(OHD)である。A12、A13は入力周波数が50Hzのときと100Hzのときの出力垂直同期信号(OVD)と出力水平同期信号(OHD)である。

【0133】

本実施例では、使用頻度の高い60Hzから80Hzまでの垂直周波数の入力信号に対しては、出力の垂直同期信号OVDを入力の垂直同期信号IVD1やIVD2に同期させるモードとして、動画に強い画像を表示させる。また、IVD1とIVD2がともに使用頻度の高い60Hzから80Hzまでの垂直周波数の場合は、入力画像の性質をマイコンで判断したり(例えば、動画、静止画判別を、図21の10−3の画像比較部で行なう)、ユーザーの設定で選択したり、表示画面上での各入力画像の表示面積の割合に応じたり、画面上に複数のウインドウ画面が開いているときに、最も前面側の画面を選択するなどで、2系統のうちいずれの入力を優先して同期を合わせるかを選択している。

【0134】

したがって、60Hzから80Hzまでの垂直周波数の入力信号に対応しては、ダブルバッファリングを用いる必要はなく(用いてもかまわない)、入力の垂直同期と同期させる方法で動画に対して追い越し、フレームの二重化、欠落のない画質を実現している。IVD1と同期を取る場合(表3の(4)、(5)、(6)、(9))、SW1はIN2−1側、同期を合わせる系統のスイッチSW2−1はIN5−1を選択する。IVD2と同期を取る場合(表3の(2)、(7)、(8)、(11))、SW1はIN2−2側、同期を合わせる系統のスイッチSW2−2はIN5−2を選択する。

【0135】

また、入力の垂直周波数が60Hz未満の場合(IVD1にとっては表3の(1)〜(3)、IVD2にとっては(1)、(4)、(10))は、フリッカ防止のため、SW1をIN1側としてダブルバッファリングによる動画質の改善を行ない、出力は80Hz一定で出力して、入力に対しては非同期とする。入力の垂直周波数が出力の周波数より低い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとすればメモリ読み出し走査を書込み走査が追い越すことはないので、SW2(SW2−1もしくはSW2−2)をIN4(IN4−1もしくはIN4−2)側としている。

【0136】

一方、入力の垂直周波数IVD(IVD1、IVD2)が80Hz以上(IVD1にとっては表3の(10)〜(12)、IVD2にとっては(3)、(9)、(12))では、出力系の動作スピードを抑えるために、SW1をIN1側としてダブルバッファリングによる動画質の改善を行ない、出力は80Hz一定で出力して、入力に対しては非同期とする。入力の垂直周波数が出力の周波数より高い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとしても、メモリ読み出し走査を書込み走査が追い越すことがあるので、SW2(SW2−1もしくはSW2−2)をIN3(IN3−1もしくはIN3−2)側として、入力のIVD1、IVD2と出力のOVDの関係から追い越しが生じないタイミングでメモリ読み出し信号を出力する。

【0137】

また、IVD1とIVD2がともに使用頻度の高い60Hzから80Hzまでの垂直周波数の場合に、出力と同期しないモードに選択された系では、出力系と比べて入力の垂直周波数が低い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとすればメモリ読み出し走査を書込み走査が追い越すことはないので、SW2(SW2−1もしくはSW2−2)をIN4(IN4−1もしくはIN4−2)側とする。逆に、出力系と比べて入力の垂直周波数が高い場合は、書込みメモリ領域と反対のメモリ領域を読み出しフィールドとしてもメモリ読み出し走査を書込み走査が追い越すことがあるので、SW2(SW2−1もしくはSW2−2)をIN3(IN3−1もしくはIN3−2)側として、入力のIVD1、IVD2と出力のOVDの関係から追い越しが生じないタイミングでメモリ読み出し信号を出力する。

【0138】

このとき、図21の発振器OSC12の周波数は、出力系の最高垂直周波数であるXGA80Hzの時のクロック周波数にあわせて設計される(例えば87MHz、1フィールド=1V期間=12.5mS、1V=(768+α)H=808Hとして1H期間=15.5μS、1H=(1024+α)CLK=1344CLKとして1CLK=11.5nS)。

【0139】

図3において、A2の80HzのIVDが入力した場合、その出力OVD=IVDとなり、その間のIHDは768+α=808本に設定される。

【0140】

また、A3、A4の75Hz、60HzのIHDが入力した場合、対応するOHDであるA8、A9はIHDと同周期になり、また、その間のOCKおよびOHDの周期は一定に保たれるため、OVD間のOHD数が比例して増加する。この768+α=808本を越える分の期間についてはブランキング期間が増加すると考えて表示部7を駆動している。

【0141】

一方、入力IHDが100HzのA1や50HzのA5の場合は、入力と非同期に出力の垂直周波数を設定するため、A12のOVD、A13のOHDに示すように80Hzの時と同じOVD、OHD周期でかつ、入力と非同期に自走させている。

【0142】

図23〜図26を用いて、具体的な動作例を示す。図23〜図26において、(a)は入力系統1の垂直同期信号IVD1であり、(b)は図22の回路で作成したメモリAの書き込み信号WE−Aであり、(c)は入力系統2の垂直同期信号IVD2であり、(d)は図22の回路で作成したメモリBの書き込み信号WE−Bであり、(e)は図22の回路で作成した出力の垂直同期信号OVDであり、(f)は図22の回路で作成したメモリAの読み出し信号RE−Aであり、(g)は図22の回路で作成したメモリBの読み出し信号RE−Bである。また、Ta1からTa9は出力の垂直同期信号のLOWレベルからHIGHレベルへの立ち上がりのタイミングを示しており、図22の回路はこのタイミングでWE−AおよびWE−Bの信号極性を保持することで、RE−AおよびRE−Bの信号極性を決定している。

【0143】

まず、図23は本実施例での最適化が行なわれる前の状態を示している。例えば、電源投入時や入力系統1と2(PC1入力とPC2入力)からの信号が伝送される直前である。まず、本画像表示装置の画像表示部として動作範囲が50Hzから85Hzの範囲にあり、かつ推奨される動作タイミングが75Hzの垂直周波数の表示部を接続したとすると、出力としてOVDは、まず75Hzに設定されている。また、この直後に、IVD1として、50Hzの垂直周波数の信号とIVD2として60Hzの垂直周波数の信号がそれぞれ入力されたときを示している。この状態では、まだ本回路で最適化は行なわれておらず、それぞれの周波数に応じてメモリが駆動されて、ダブルバッファによる表示が行なわれている。

【0144】

次に、図24は第一段階として入力系統2の60Hzを動画表示上優先すると判断した場合の動作を示している。この選択としては、例えば図21のマイコンに入力する同期信号IHD1、IHD2、IVD1、IVD2からマイコン部が2系統の入力信号の同期判別を行ない、解像度と垂直周波数を判定した結果を表3のように、マイコン部内に持つテーブルを参照して表3の(2)の動作を選択する。あるいは、図21の画像比較部10−3において、IVD2の系統がNTSCなどのTV系のインターレース信号をPC用にノンインターレース化した動画であり、IVD1の系統が静止画であるという判別を行なった場合も同様の決定がされる。図22のSW1、SW2−1、SW2−2はそれぞれIN2−2、IN4−1、IN5−2が選択される。これにより、図24の(e)に示すように、出力の垂直同期信号OVDはIVD2と同期が合わせ込まれる。これにより、IVD2の系の動画質は確保され、ダブルバッファリングの欠点であるフレームの二重化やフレームの抜けが発生しないスムーズな画面が実現される。また、IVD1の系は50Hzから60Hzに変換されるため表示部においてフリッカによる画質劣化を避けることができている。

【0145】

さらに、図25に第二段階として、IVD1の入力系統も動画の映像ソースを送出してきたことを図21の画像比較部10−3で検出して、マイコン部がIVD1の入力系の動画質を改善すべきと判断した場合や、システムの設定で常に動画質を各系統とも最善の状態に設定するようにマイコン部のソフトウエアが設計されている場合の例を示す。図21のマイコン部9はDDC1を介してIVD1の入力信号源に対して、垂直周波数を50Hzから60Hzに変更するよう要求し、IVD1の入力信号源は垂直周波数を60Hzに設定を変更する。これにより、IVD1はIVD2やOVDとは位相は一致していないが、周波数は一致するため、ダブルバッファリングをしていても、フレームの二重化やフレームの抜けが発生しないスムーズな画面が実現される。これにより、2系統とも動画質の最適化された表示装置が実現される。

【0146】

さらに、図26に第三段階として、画像表示部を変更した場合を示す。例えば、従来リア型のプロジェクションディスプレイを用いていたシステムをプラズマディスプレイに置き換えたり、古い型のディスプレイを新しい型に置き換えたりして、動作範囲が50Hzから85Hzまで可変できるタイプのディスプレイから、動作範囲が70Hzから100Hzのディスプレイに変更した場合が考えられる。

【0147】

このとき、図21のシステムのマイコン部はDDC3を介して新たに接続されたディスプレイの動作範囲から、60Hzでは動作しないものであることを検知して、出力系の動作周波数を70Hz以上に変更しようとする。また、マイコン部は、DDCや入力画質の情報から、特にIVD1の系よりもIVD2の系の動画質を優先させるべきと判断する。そこで、本実施例のマイコン部は、もとのIVD2の垂直周波数の周期(画面の更新周期)に近く、また周期の比が整数対整数の比になるような新しい垂直周波数の候補を出力可能な周波数の範囲から選択するとともに(例えば、75Hzを選択する。もとの60Hzとの周期の比はT(60Hz):T(75Hz)=5:4)、IVD2系のDDC通信を介してIVD2の系が60Hzの次に最適な周波数としてその垂直周波数で動作可能かを調べる。IVD2側が動作可能であれば、新しく選択された垂直周波数75HzにIVD2の系の動作周波数が設定されるとともに、画像表示部の垂直周波数も、IVD2の垂直同期信号に同期した75Hzに設定される。再び、図22のSW1、SW2−1、SW2−2はそれぞれIN2−2、IN4−1、IN5−2が選択される。これにより、図26に示すように、出力の垂直同期信号OVDはIVD2と同期が合わせ込まれる。また、これに伴ない、IVD1の系も動画質を良くするために、DDC1を介して75Hzに動作周波数を設定し直される。これにより、入力系、出力系ともに75Hzに動作を変更される。

【0148】

実施例の中で述べたように、60〜80Hzという周波数は、現行のPCやWS(ワークステーション)やDTV(デジタルテレビ)等、最も広く普及している周波数帯である一方、TVからの動画の映像ソースもNTSCが60Hzのため、この範囲に入ってくるので使用頻度が非常に高く、動画を最優先させる意味は高い。

【0149】

一方、50Hzなど、低い周波数のフリッカ現象は、動画、静止画に関らず非常に見づらい画質劣化となる点から、ダブルバッファリングのような簡易的に動画に強い方式をとる方法で、フリッカ防止と動画画質向上を両立させている。

【0150】

また、100Hzのように高い垂直周波数の信号に関しては、100MHzを超える動作速度が回路的な負担が大きいことを重視し、ダブルバッファリングのような簡易的に動画に強い方式をとる方法で、コスト削減と安定動作を動画画質向上と両立させている。特に液晶やPDPなどの表示素子は駆動電圧が10数Vから数十Vという高電圧が必要とされるため、1画素あたりの速度が高速化すると、映像信号系やドライバ回路が非常に高い帯域やスルーレートが必要とされる。現状においても、こうした高い速度の駆動に対しては追従できない部分を、複数に分割駆動しているが、更なる出力系の高速化は高速な部品への変更、新規部品の開発、分割数の変更などの回路変更によるコストアップばかりでなく、回路の動作マージンを狭くし、安定的な動作を困難にする要因となる。また、この問題はSXGAやUXGAといった、現状よりも更に数倍画素数の多い表示素子などを駆動する場合に、特に重要になる。将来の高画素化のためにも、コスト削減と安定動作が動画画質向上と両立できる点が重要になってくる。

【0151】

さらに、このような垂直周波数の最適化を図る際に、出力の垂直同期が完全に一致できるのは、複数の系統のうち一つしかないため、複数系統の入力画像のどれを優先して垂直同期を一致させて動画質を確保するかの選択を可能にしたことで、複数系統のなかで動画質を重視する入力系統が、アプリケーションソフトや番組などにより変化した場合も、安価でありながら、柔軟に対応できるシステムが構築できる。

【0152】

また、選択された出力同期周波数に対して、同期していない入力系統に対して、DDC等を介して入力信号源に対して入力周波数の変更を要求し、出力周波数と一致した周波数に変更することにより、複数画面の入力系とも動画質が最適に表示されるため、デジタルTVやPCのグラフィックゲームソフト、デジタルビデオ等、さまざまな動画ソースが表示されるマルチ画面の表示装置において、安価でありながら、動画質を十分満たせる機器を提供できる。

【0153】

また、画像表示部が異なるタイプのディスプレイに変わったことにより(例えばリア型のプロジェクションディスプレイからプラズマディスプレイなど)、対応可能な動作周波数の帯域が変化した場合も、DDCやその他の通信を介して得られる画像表示部の特性の情報を受けて、内部の出力周波数の選択範囲や選択方法を変更するのに加えて、DDCを介して複数の入力信号系に要求する内容も変更をかける構成にしたことで、安価でありながら、将来的なシステムの変更やシステムの拡張に対しても柔軟で、かつ動画質の最適な機器が実現できる。

【0154】

本実施例では、複数の入力に接続される機器からの通信手段として、DDC(DDC1、DDC2)を、また出力する画像表示装置との通信手段としてDDC(DDC3)を示しているが、これはVESAの標準(現在DDCver.3.0 1997.12.15発行)が、現在ディスプレイの情報をPCに通信する手段として最も普及しているため、例示してあるだけであり、USBやIEEE1394、従来のシリアル通信、パラレル通信手段など画像処理機器間で情報を通信できる手段であれば任意のものでよい。特にVESAの標準に関しては、逐次改定されているが、現在のところ、本発明のような複数のホスト機器(信号発生器やPC)と表示機器の接続は前提とされておらず、アドレス間の調停などの観念もない。また、通信時期もホスト(PC)側の起動時に限られているため、このままでは本発明に利用できない。本実施例では、通信手段の実現方法の例として、通信線の形態をDDCと同じI2Cの2線式シリアルバスを3系統DDC1,DDC2,DDC3用意して、データ形式(フォーマット)もDDCの用いている標準EDID(現在EDIDver.3.0 1997.11.13発行)などに準じた形式にしている。これにより、複数の入力機器はホストとして、本実施例の画像処理装置をディスプレイとして扱いDDC情報を通信する。また、本実施例の画像処理装置は、接続される表示装置には、自身がホストとして表示装置をディスプレイとして扱い、DDC情報を通信する。これらの複数の入力機器と表示装置のアドレス間の調停やホスト役の切替えは、本来のDDCでは規定されていないので、本実施例の図21のマイコン9が制御する。また、ホストの起動時のみではなく、機器の接続切替え時にも通信を行なえるような検出と制御も、DDCでは規定されていないので、本実施例の図21のマイコン9で対応する。このようにして、本発明を実現している。他の実施例においても同様である。

【0155】

ここでは、使用頻度の高い垂直周波数帯域を同期を一致させ、それ以外の周波数をダブルバッファリングさせたが、ダブルバッファリングは、メモリ領域を倍必要とすること、またそのための制御回路部分が必要となるため、入力系統数が多くなると高価になるため、機能として省くことも考えられる。特定の垂直周波数帯域のみ同期を一致させる方法やダブルブァッファする方法をとる一方で、その帯域以外の使用頻度は低いと判断し、動画質は改善しない単なる非同期な動作に切り換えることを行ない、複数の入力系のうち動画を優先する系統のみ選択切り替えて動画質を確保する方法も安価な製品を提供する意味で本実施例の一つの形態である。

【0156】

また、本実施例では、入力信号の垂直周波数により、出力系を入力系と同期させるか非同期とするかを選択したが、本実施形態は複数の入力系の動作モードや画質特性から最適な出力系の動作モードや画質特性を選択する回路を有すること、および表示部を含む出力系の動作モードや画質特性と複数の入力系の動作モードや画質特性から、システム全体の動作モードや画質特性を決定する回路を有すること、またその決定にしたがって任意の入力系の動作モードや画質特性の変更を要求する回路を有することが特徴であり、切り換える基準は入力信号の垂直周波数以外にも、入力信号のフォーマットの他の項目でや、入力画像から抽出した画像情報、入力画像の信号の内容、システムの動作モード、画面の表示割合や配置条件、ユーザー設定、省電力モードなどによる場合も含んでいる。

【0157】

また、切り替える対象として、本実施例は動画質に着目して垂直周波数を例示したが、他の画質特性に対しても、入力信号のフォーマットの他の項目、例えば解像度や画像の表示位置、画像の大きさ、色相、色度、ホワイトバランス、明るさ(ブライト)、明暗(コントラスト)、階調性(ガンマ特性)、ダイナミックレンジ等に関しても、同様である。

第4の実施例において、この例の一つとして階調性の例を示す。

【0158】

(実施例4)

第3の実施例と同じ図21を用いて、第4の実施例を示す。ここで、図21における各部の構成および動作は第3の実施例と同じである。

本実施例においては、10−3の画像比較部において、各入力系の画質の比較を行ない、マイコンが出力系と各入力系の画質制御を行なうための情報の出力を行なう。入力系画像処理部1および入力系画像処理部2から出力される画像信号から比較用に抽出された比較信号20−REF−1、20−REF−2から得られた比較情報の演算結果がマイコンバス19−1を経由してマイコンに伝達される。

【0159】

本実施例において、画像比較部から得られる各入力系の画質特性の比較結果に加えて、DDC3やほかの通信経路、初期情報等で与えられる表示部の特性や条件との比較を行ない、内部の各画像処理部(入力系画像処理部1、入力系画像処理部2、出力系画像処理部)を制御するとともに、DDC1、DDC2を介して入力信号源の画質制御を行なう。

【0160】

ここで、本実施例での画質の主要な調整部は出力系画像処理部6に存在し、入力画像処理部3−1、3−2の画質調整部は補助的に存在する。これは、画像のビット誤差の増大を避けるためであり、画質を優先する系は入力の画像処理部の画質調整部をバイパスする構成として、出力系の調整部のみにより、画像表示部に適した特性に変換される。また、もう一方の系は、補助的に入力画像処理部の画質調整も行ない、優先した系と同様の画質になるように調整される。あるいは、優先しない方の系は、入力画像処理部での画質調整を行なうかわりに、DDCを介して入力信号源に、入力信号の画質を変更する要求を出すことで、優先した系と同様の画質になるように調整される。

【0161】

これにより、複数の入力系の様々な画質特性の入力画像を1画面上に合成してマルチ画面表示を行なう際に、各入力系と出力表示部の画質特性に応じて、システム全体の画質が最適化される。

【0162】

図27から図29を用いて、本実施例の動作を説明する。

図27は、本実施例による画質の最適化が行なわれる第一段階の状態を示している。このとき、表示部の表示特性は図15の15−1である。図27において、16−1A、16−1Bは2系統の入力IDATA1およびIDATA2から入力する信号レベルを示し、16−3A、16−3Bは出力画像処理部6の通過後の各信号レベルをあらわす。また、16−4A、16−4Bはこのときの表示部の輝度レベルを示す。

【0163】

第一段階として、マイコン部は、入力系画像処理部1(3−1)と入力系画像処理部2(3−2)からの画質情報(20−REF−1、20−REF−2)を比較して得られた画像比較部(10−3)の結果と、DDC3経由や、あらかじめマイコン部付随のメモリ上に記憶されたテーブル等から得られる画像表示部の入出力特性から、画質を優先する入力系を決定する。ここでは、入力系2(IDATA2)を優先させると判断している。ここで、従来例と異なり、優先する系の入力信号の表示部に対する特性の変換は、入力系の画質処理部ではなく出力系の画質処理部で一括して行なわれる。変換係数は、あらかじめマイコン上で入力系2の特性と出力系の特性を合成して出力系画像処理部に適用することにより、デジタル処理の通過回数を半分にして、ビット誤差を少なくしている。また、このとき入力系1の画像に対しても同じ合成した変換係数が適用されるため、16−3Aのように、入力系1の画質の最適化は行なわれていない。

【0164】

次に、第2段階として、マイコン部は優先しない入力1の系に対しても、画質の最適化を行なった様子を図28に示す。図28において、16−1A、16−1Bは2系統の入力IDATA1およびIDATA2から入力する各信号レベルを示し、16−2A、16−2Bは入力画像処理部1(3−1)と入力系画像処理部2(3−2)の通過後の各信号レベルを示す。16−3A、16−3Bは出力画像処理部6の通過後の各信号レベルをあらわす。また、16−4A、16−4Bは、このときの表示部の輝度レベルを示す。

【0165】

第一段階で調整されたIDATA2の系(16−1B〜16−4B)に対して、第二段階ではIDATA1の系を調整する。このとき、出力画像処理部6の変換特性は入力2(IDATA2)で決定されているので、この特性に対する、入力1(IDATA1)の入力補正の差分を入力画像処理部1(3−1)に適用する。この結果、入力画像処理部1(3−1)通過後の信号レベル16−2Aは、入力画像処理部2(3−2)通過後の信号レベル16−2Bにほぼ等しくなり、出力画像処理部上では、16−3Bとほぼ同じ信号レベル16−3Aで出力され、また、16−4Bとほぼ同じ輝度レベル16−4Aで表示が行なわれる。

このように、優先しない系に対しては、ビット誤差は大きくなるものの、優先した系と同様の特性に調整を行なうことができる。

【0166】

さらに、第三段階として、図15の15−2の特性のものに画像表示部7を変更した場合を図29に示す。図29において、16−1A、16−1Bは2系統の入力IDATA1およびIDATA2から入力する各信号レベルを示し、16−3A、16−3Bは出力画像処理部6の通過後の各信号レベルをあらわす。また、16−4A、16−4Bは、このときの表示部の輝度レベルを示す。

【0167】

画像表示部の変更に伴ない、マイコン部は、DDC3経由や、あらかじめマイコン部付随のメモリ上に記憶されたテーブル等から得られる変更後の画像表示部の出力特性を読み込み直す。この情報と、各入力系の画質情報から画質を優先する入力系を再度決定する。

【0168】

ここでは、再び入力2(IDATA2)を優先すると判断したとする。変換係数は、マイコン上で入力系2の特性と新しい出力系の特性を合成して出力系画像処理部に適用され、16−3Bが出力される。この結果、画像表示部の表示特性に最適化が行なわれた輝度レベルが選られる(16−4B)。また、第三段階では、さらに、入力系1に対しても画質のビット誤差を少なくするため、第二段階のような入力系1に対しての入力信号処理部での変換を行なわず、DDC1を介して入力信号源1に対して、信号振幅とレベルを入力信号源2に一致させるように要求を出して、16−1Aのように入力系1の入力信号の特性を、16−1Bの入力系2の入力信号の特性に等しくなるようにする。入力信号の段階で二つの入力系の信号レベルを一致させることにより、両方の系ともデジタル処理の通過回数を半分にして、ビット誤差を少なくしている。

【0169】

以上に述べたように、画像比較部から得られる各入力系の画質特性の比較結果に加えて、DDCや他の通信経路、初期情報等で与えられる表示部の特性や条件との比較を行ない、内部の各画像処理部(入力系画像処理部1、入力系画像処理部2、出力系画像処理部)を制御するとともに、DDCなどの通信手段を介して入力信号源の画質制御を行なうことにより、複数の入力信号を一つの画面に表示するマルチ画面表示においても、安価で簡単な回路構成でありながら、優先する系の高画質表示を実現するとともに、他の系の画質も一定の水準を満たすシステムが実現できる。

【0170】

本実施例においては、簡単化のため、グレースケール信号を用いて、画質として信号のDCレベルと振幅の最適化を行なう例を述べたが、実際には、表示素子の特性を補正するガンマ補正や、CRT用に映像信号に掛けられているガンマ補正をキャンセルする逆ガンマ補正などの非線型な補正に対しても同様に適用できる。また、赤、青、緑毎にこれらの特性が異なることにより生じるホワイトバランスのずれ、色の特性についても、本実施例を適用することにより、優先する入力系を選択して、出力系の特性と合わせて、各色のバランスを合わせ込み、他の系は補助的な手段を用いて、あるいは入力信号源に制御信号を送ることにより一定の水準を満たすように調整してシステムの最適化を図ることができるのは同様である。色毎の特性がばらつく原因としては、赤、青、緑毎に異なる液晶パネルを用いる3板式のプロジェクタなどに見られるような各色ごとの液晶素子のガンマ特性のばらつきや、色を光学系で3原色に分解するための各光学素子の色毎の特性のばらつき、バックライトやLED、ランプなどの発光体の特性、各色ごとの信号処理系のばらつきなどがある。

【0171】

特に、信号処理系のばらつきは、各信号源やその信号源に信号データが送られてくる以前の処理系でも意外と大きいことがあり、これがその装置特有の色味になっていたりすることも少なくない。これは、ディスプレイとして、ある色を強くした方が、鮮やかにみえるというメーカーの故意の調整であったり、製造上での各色での信号処理系の調整工数を減らしてコスト削減を行なうため省略されたためのばらつきであったりする。

【0172】

さらに、こうした故意の調整や工数削減によるばらつきなどは色だけに限られることではない。特にPCのグラフィック画面やデジタルテレビ、通信を介して受信されたテレビ会議の映像、インターネットを経由してきた画像情報、テレビゲームのグラフィック画像、USBやIEEE1394を介して受信したデジタルビデオカメラの映像など信号源や伝送形態の種類の多様化に伴ない、機器間のこうした特性差は広がりつつある。また、解像度や画面のリフレッシュレートなどの表示動作の差も多様化している。一方、表示装置はこれらの多様な入力ソースを同じ画面で表示する方向に動いており、こうした意味で本実施形態の有効性も広がっている。

【0173】

第3および第4の実施例においては、複数の入力信号源としてPCを2系統接続した例を挙げたが、第5の実施例としてはこうした多様化した機器間での適用例を示している。

【0174】

(実施例5)

第5の実施例として多様化した機器間での適用例として、PC(パーソナルコンピュータ)上に画像処理の入出力基板を備えて、表示装置を表示させるシステムの例を図30に示す。入力としては、画像処理基板に直接他のPC等を接続する2系統のデジタル入力の他に、PC本体のCPUで実行されるアプリケーションにより描画されるグラフィック画像および、通信IFを介して受信されるTV会議などの画像情報、IEEE1394を介して入力されるDVDやデジタルビデオ、デジタルテレビ等の信号が扱える。また、出力信号は、画像処理基板に直接接続する表示装置の他に、IEEE1394を介して外部のデジタルテレビやビデオ記録用のサーバーなどに送ることができる。

【0175】

図30において、9−1はPCのCPU(中央演算処理部)であり、9−2はチップセットと呼ばれるCPU周辺のメモリや周辺機器の制御するバスを制御するメモリ・バスコントローラであり、9−3はPC本体のメインメモリである。9−4はPCの通信インターフェース部であり、端子1−tを介して、外部の通信線に接続される。19−2、19−3はこのPCのシステム制御用バスであり、19−4はグラフィック部の制御用のバスである。25の一点鎖線で囲んだ領域が画像処理基板であり、PC本体とは端子1−4を介して、グラフィック制御バス19−4に接続される。

【0176】

1−1aは1系統目の入力としてのqビットのデジタルの画像信号(IDATA1)の入力端子である。1−1bは入力信号の水平同期信号(IHD1)入力端子であり、1−1cは入力信号の垂直同期信号(IVD1)入力端子である。1−1dは画像信号のクロック(ICK1)入力端子であり、1−1eはDDC信号(DDC1)の入出力端子である。20−1a−1、20−1a−2は各部へnビットのデジタルの画像信号を伝送するデータバスである。また、20−1bcdはIHD1、IVD1、ICK1信号線群である。20−1eはDDC1の信号線である。

【0177】

1−2aは2系統目の入力としてのnビットのデジタル画像信号(IDATA2)の入力端子である。1−2bは入力信号の水平同期信号(IHD2)入力端子であり、1−2cは入力信号の垂直同期信号(IVD2)入力端子である。1−2dは画像信号のクロック(ICK2)入力端子であり、1−2eはDDC信号(DDC2)の入出力端子である。20−2a−1、20−2a−2は各部へnビットのデジタルの画像信号を伝送するデータバスである。また、20−2bcdはIHD2、IVD2、ICK2信号線群である。20−2eはDDC2の信号線である。

【0178】

3−1は入力系1の画像処理部Aであり、3−2は入力系2の画像処理部Bである。

【0179】

1−3は、3系統目の入力かつ外部出力として機能するIEEE1394の入出力端子である。23はIEEE1394の処理ブロックであり、24はIEEE1394信号を内部で扱う映像信号と同期信号に変換および逆変換するためのエンコーダ兼デコーダである。また、3−3は入力したIEEE1394画像の画像処理部Cであり、6−3はIEEE1394信号として出力する前の出力系の画像処理部Bである。

【0180】

20−3はIEEE1394の信号線であり、20−3a−1は変換後のrビットのデジタル画像信号である。また、20−3bcdは、IEEE1394信号から再生された同期信号、CLKなどの信号線群である。

【0181】

また、4系統目の入力として1−4の端子を介して、19−4のグラフィック制御用バスからPCのアプリケーションプログラムにより生成されるグラフィック情報と、外部機器から通信線を介してPCに入力される画像情報が入力される。9−6はこれらの情報からグラフィックデータを出力するグラフィック生成・制御部Dであり、20−4a−1がvビットのグラフィックデータの信号線群である。また、20−4bcdはこのグラフィック画像の同期信号とクロックの信号線群である。また、19−5は端子1−4を介して外部バス19−4に接続されるグラフィック制御用の内部バスであり、この画像処理ボードの全体の制御はこのバスを介して、PC本体のCPUとグラフィック生成・制御部が分担して行なう。

【0182】

4は3つの入力画像処理部3−1、3−2、3−3とグラフィック生成・制御部9−6のあわせて4系統から入力した画像信号を、一旦メモリに記憶し、マルチ画面として出力するために、画像を合成して、出力系の画像処理部に出力する制御を行なうメモリ制御部である。5−1、5−2、5−3、5−4は入力系1、入力系2、入力系3およびグラフィック生成部にそれぞれ対応したフレームメモリ(メモリA、メモリB、メモリC、メモリD)である。21−1、21−2、21−3、21−4はそれぞれメモリA、B、C、Dの制御バスであり、22−1、22−2、22−3、22−4はそれぞれメモリA、B、C、Dのデータバスである。

6−1は出力系の画像処理部Aであり、7は液晶やプラズマディスプレイ、CRTなどの画像表示部である。

【0183】

1−fは画像表示部のkビットのデジタルデータ(ODATA)の画像表示部の入力端子であり、1−gは出力信号の水平同期信号(OHD)の画像表示部の入力端子であり、1−hは出力信号の垂直同期信号(OVD)の画像表示部の入力端子である。1−iは出力画像信号のクロック(OCK)の画像表示部の入力端子である。20−f−1、20−f−2、20−f−3はkビットのデジタルの画像データ(ODATA)の信号線である。また、20−g−2、20−h−2、20−i−2は、外部表示装置への水平同期信号、垂直同期信号、クロックの各信号線である。また、1−sは、画像表示部に対するDDC信号(DDC3)の入出力端子であり、20−s−1、20−s−2は、このDDC3の信号線である。

【0184】

12は発振部であり、出力系のクロック(OCK)を発生する。20−i−1はOCKの信号線である。発振部12は水晶などの発振回路やPLL(Phase−Locked−Loop)回路などで構成される。

【0185】

10−4が内部および外部の同期制御部であり、20−WEはメモリA〜Dの書込みフィールドの制御信号群、20−REはメモリA〜Dの読み出しフィールド制御信号群である。20−ghiは出力系の水平同期信号、垂直同期信号、クロックの各信号線群である。また、20−CNT−6はIEEE1394信号処理ブロック23の同期信号とクロックを制御するための制御線である。

【0186】

また、10−5が画像比較部および内部、外部の画質制御部であり、20−CNT−1および20−CNT−2は入力系画像処理部AとBからの画像抽出情報のデータ線および、入力系画像処理部AとBの画質を制御するための制御線からなる信号線群である。20−CNT−3はIEEE1394信号処理ブロック23内の入力画像処理部Cと出力系画像処理部Bからの画像抽出情報のデータ線および、入力系画像処理部Cと出力系画像処理部Bの画質を制御するための制御線からなる信号線群である。20−CNT−4はグラフィック生成・制御部からの画像抽出情報のデータ線および、グラフィック生成・制御部の画質を制御するための制御線からなる信号線群である。20−CNT−5は出力系画像処理部Aからの画像抽出情報のデータ線および、出力系画像処理部Aの画質を制御するための制御線からなる信号線群である。

【0187】

さらに、9−5は内部・外部同期制御部(10−4)と内部・外部画質制御部(10−5)との連携をとり、入力信号のDDC信号DDC1およびDDC2と、画像表示部のDDC信号DDC3を送受信するためのDDC用のインターフェース部である。また、20−u−1、20−u−2は、それぞれ内部・外部同期制御部(10−4)および内部・外部画質制御部(10−5)とこのDDC用インターフェース部間のデータ線および制御線である。

【0188】

画像の入力端子1−1aから入力したデジタル画像信号は、5−1のメモリ部Aに格納される前に3−1の入力系画像処理部Aで画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。また、入力系画像処理部Aから画質を比較するための信号が、画像比較部に送出される。また、同期信号およびクロックは内部・外部同期制御部10−4に伝送される。

【0189】

画像の入力端子1−2aから入力したデジタル画像信号は、5−2のメモリ部Bに格納される前に3−2の入力系画像処理部Bで画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。また、入力系画像処理部Bから画質を比較するための信号が、画像比較部に送出される。また、同期信号およびクロックは内部・外部同期制御部10−4に伝送される。

【0190】

IEEE1394入出力端子1−3から入力したIEEE1394信号は、内部で扱える画像信号と同期信号に変換される。5−3のメモリ部Cに格納される前に3−3の入力系画像処理部Cで画質の調整や画像の縮小変換等の処理を行なわれてから、4のメモリ制御部に転送される。また、入力系画像処理部Cから画質を比較するための信号が、画像比較部に送出される。

さらに、IEEE1394として外部出力する場合は、この出力画像処理部Bでの画像情報も画像比較部に送出される。また、同期信号およびクロックは内部・外部同期制御部10−4に伝送される。

【0191】

また、グラフィック生成・制御部9−6では、アプリケーションソフトやグラフィックドライバーソフトの指示に従って、内部・外部同期制御部(10−4)で作成した同期信号とクロックが入力するとともに、グラフィック信号を生成して5−4のメモリ部Dに格納されるために4のメモリ制御部に転送される。このとき、画質の制御は内部・外部画質制御部(10−5)によって行なわれる。

【0192】

メモリ制御部では、内部・外部同期制御部(10−4)で作成した出力系の同期信号とクロックにしたがって各メモリA〜Dより信号が読み出され、合成される。このとき、出力系画像処理部Aでの画像情報も画像比較部(10−5)に送出される。

本実施例では、このメモリ部A〜Dのいずれもダブルバッファリング可能なメモリ領域を確保し、同期制御部のメモリ書き込み信号と読み出し信号の制御線群(20−WE、20−RE)で書き込みと読み出すメモリ領域を切替え制御する。

【0193】

さらに、内部・外部同期制御部からの出力系のクロックOCKと水平同期信号OHD、垂直同期信号OVDに同期して所定の画像の大きさ、表示位置の関係にあったタイミングで4系統の画像データをメモリ部から読み出して、6−1の出力系画像部にデータを転送する。

6−1の画像処理部では、画質の調整や、画像の拡大変換などが行なわれる。最後に画像表示部7にこれらの画像データと同期信号、クロックが伝送され画像表示が行なわれる。

【0194】

本実施例においても、10−4の内部・外部同期制御部において、実施例3同様、動画像を優先する入力系を選択して、システム全体の動作の最適化を行なうことができる。ここには入力系1、入力系2、入力系3の同期信号とクロックが入力する。また、DDCインターフェース部を介して、画像表示部と入力系1および入力系2のDDCが接続されている。また、内部バス19−5を介してグラフィック作成・制御部が実行するアプリケーションソフトや通信からの画像表示の動作の要求内容が入力される。さらに、10−5の画質比較部により入力系1〜3の画像抽出情報で画像の特性情報が得られる。これらの情報から、内部・外部同期制御部は入力4系統の動作タイミングと画像の動画質特性および、画像表示部の動作特性を判断して、優先させるべき入力系の動画像に適した出力系動作となるように、メモリの制御信号と出力系の同期信号とクロックを作成する。また、グラフィック作成・制御部の同期信号およびクロックには、出力と同期したタイミングの信号を送出する。さらに、それ以外の入力系に対しても、動作の最適化を行なう必要がある場合は、入力系1および2に対してはDDCなどの通信手段を介して、入力信号源の動作を変更する要求を行なう。また入力系3の場合は制御線20−CNT−6を通じてエンコーダ・デコーダ部24で要求信号をIEEE1394信号に変換して、さらにこの信号がIEEE1394を通じて信号源の装置の制御を行なうことにより、入力信号源の動作を変更する。

【0195】

また、本実施例においても、10−5の内部・外部画質制御部において、実施例4同様、画質を優先する入力系を選択して、システム全体の画質の最適化を行なうことができる。ここには入力系画像処理部A〜Cから抽出された画像情報が入力するとともに、グラフィック生成・制御部から抽出された画像情報も入力される。また、出力系画像処理部Aからの画像抽出情報と、画像表示部7からDDCインターフェースを介して得られる表示特性が入力される。また、出力系画像処理部Bからの画像抽出情報と、IEEE1394を介して得られるIEEE1394で接続された別の表示装置の表示特性も入力される。これらの情報から、内部・外部画質制御部は入力4系統の画質特性および、画像表示部7の画質表示特性とIEEE1394経由で接続される別の表示装置の画質表示特性を判断して、優先させるべき入力系に適した画質特性となるように、出力系画像処理部Aもしくは出力系画像処理部Bを制御する。さらに、それ以外の入力系に対しても、画質の最適化を行なう必要がある場合は、各入力系の画像処理部により画質の調整を行なう。あるいは、入力系1および2に対してはDDCなどの通信手段を介して、入力信号源に対して画質を変更する要求を行なう。また入力系3の場合は制御線20−CNT−6を通じてエンコーダ・デコーダ部24で要求信号をIEEE1394信号に変換して、さらにこの信号がIEEE1394を通じて信号源の装置の制御を行なうことにより、入力信号源からの信号の画質を変更する。

【0196】

本実施例において、優先する入力系を選択して、最適化を行なうシステム全体の最適化の判断は、10−4の内部・外部同期制御部や、10−5の内部・外部画質制御部のブロックでハード的に処理される場合以外に、9−6のグラフィック生成・制御部あるいは9−1のCPUにおいて、アプリケーションソフトあるいはグラフィック制御用のドライバーソフト等によりソフト的に実行される場合もあることはいうまでもない。

【0197】

これにより、複数の入力系の様々なフォーマットと画質特性の入力画像を1画面上に合成してマルチ画面表示を行なう際に、各入力系と出力表示部の画質や動画の特性に応じて、システム全体の動作タイミングと画質が最適化される。

【0198】

ここでは、各入力系毎の整合性を考えたが、実際には各信号源からの信号は一種類の信号源からの出力のみとは限らない。例えば、IEEE1394にはDVDとデジタルビデオ、衛星放送やケーブルテレビ、地上波放送等のセットトップボックスなどの複数の機器が接続される。本実施例は、こうした1入力において混合された複数の画像情報も各入力信号源の一つ一つと考えて適用可能であり、IEEE1394端子等から入力するこうした複数の機器からの信号と、他の入力系の信号とを同列にならべた上で、優先する信号を選択して、動画質および画質特性のシステム全体の最適化を行なうことができる。

【0199】

また、優先する入力画像の選択は、画像抽出情報や画像信号のフォーマットだけではなく、入力する画像の用途や種類および自動設定あるいはユーザー設定される表示画面上の各画像の配置条件によっても行なわれる。例えば、本実施例において図31および、表4のように各入力映像信号が合成表示される画面を考える。

【0200】

【表4】

【0201】

表4において、各列は各信号入力源の信号の用途や種類を示す。ここでは、例として▲1▼IEEE1394を介してデジタルTV信号と、また、▲2▼通信IFを介してTV電話と、さらに▲3▼外部PC入力からインターネットの画像が入力してきた場合を挙げている。また、表4の行には、用途により自動設定されたり、その表示装置を見ているユーザーが用途に応じて最も注目する画面として、例えば最前面に配置するなどの配置条件により選択された画像が示されている。表4の(a)〜(d)が図31の(a)〜(d)に対応している。そして、○印が、その入力源の信号の用途や種類と配置条件において、本実施例の回路が優先して選択する入力信号源である。

【0202】

図31および表4において、まず、(a)の表示画面では、最前面にデジタルテレビ画面が配置されている。このとき、画像表示部には、他にインターネット画面は子画面で表示されているが、それは最も注目される表示物ではなく、また静止画が主体である。また、TV電話の画像も入力しているが、現在は受信していない状態である。したがって、同期制御部および画質制御部は優先する入力系としてデジタルテレビの信号を選択して、システム動作を最適化する。

【0203】

また、(b)の表示画面では、最前面にTV電話の画面が配置されている。このとき、画像表示部には、他にインターネット画面は子画面で表示されているが、それは最も注目される表示物ではなく、また静止画が主体である。また、デジタルテレビ画面の画像も入力しているが、現在は小さく表示されている状態である。したがって、同期制御部および画質制御部は優先する入力系としてTV電話の画面の信号を選択して、システム動作を最適化する。

【0204】

また、(c)の表示画面では、最前面にインターネット画面が配置されている。このとき、画像表示部には、他にデジタルテレビの画像が子画面で表示されている。また、TV電話の画像も入力しているが、現在は小さく表示されている状態である。ここで、同期制御部および画質制御部は優先する入力系として、デジタルテレビの画像の信号を選択して、システム動作を最適化する。これは、配置条件としてはインターネット画面が最前面であるが内容が静止画主体のため、デジタルテレビを最優先する入力と判断したためである。

【0205】

一方、(d)の表示画面でも、最前面にインターネット画面が配置されており、画像表示部には、他にデジタルテレビの画像と、TV電話の画像も入力している。(c)と比較して違う点は、インターネット画面上で配信される動画情報の映像が小さなウインドウ▲4▼で表示されている点である。ここで、同期制御部および画質制御部は優先する入力系として、インターネット画面の信号を選択して、システム動作を最適化する。これは、配置条件としてはインターネット画面が最前面であり、また内容が動画主体になったため、デジタルテレビよりもインターネット画面が最優先する入力と判断したためである。

【0206】

このようにして、ユーザーが見る主体を変化させた配置条件やその信号の内容により、信号源の優先したシステム動作の最適化を図る。また、ユーザーは図30のシステムメモリ部に、これらの入力信号と配置条件における設定状態を保存できるようになっており、これによりユーザーの各種の映像機器と画像表示部の最適化関係を本実施形態の画像処理装置に記憶することができる。

【0207】

【発明の効果】

以上説明したように、本発明によれば、出力系を入力系の垂直同期信号に対して同期、非同期にすることを切換可能として、垂直周波数などの入力信号のフォーマットによって選択することにより、システムの全体を動画に強い構成として、特に使用頻度の高い垂直周波数帯で動画の問題のない動作を実現し、また、その他の垂直周波数帯では簡易的に動画に強くかつ画質上の問題の解決と動作マージンを確保し安定な動作を行なうことを両立する画像処理装置を簡素で安価に実現することができる。また、将来的にもUXGA等、現状よりも更に数倍画素数の多い信号処理用途で、容易に同様の構成で安価で動画に強い回路を実現できる。また、複数の異なる周期の入力信号が混在するシステムにおいても、複数の入力系の垂直同期信号に対して出力系を同期、非同期にすることを切換可能として、また、その結果を用いて任意の入力信号源の垂直周波数の設定を行なえるように構成することにより、出力系の構成は1系統のクロックで動作させながら、複数の入力系統間と出力の同期関係を最適化して、システム全体を動画に強い構成でかつ簡単で安価な回路構成にすることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施例に係る画像処理装置のブロック図である。

【図2】図1の装置における同期制御部の構成図である。

【図3】図1の装置の動作を説明するためのタイミングチャートである。

【図4】本発明の第2の実施例に係る画像処理装置のブロック図である。

【図5】図4の装置における画像表示例である。

【図6】従来例を説明するための、画像処理装置のブロック図である。

【図7】図6の従来例における画像処理装置の動作を示したタイミングチャートである。

【図8】図6の従来例における動画での問題点の説明図である。

【図9】ダブルバッファリングを行なう時のメモリ領域を示す図である。

【図10】ダブルバッファリングにおける画像処理装置の動作を示したタイミングチャートである。

【図11】ダブルバッファリングにおける動画での問題点の説明図である。

【図12】ダブルバッファリングにおける動画での問題点の説明図である。

【図13】第2の従来例を説明するための、画像処理装置のブロック図である。

【図14】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図15】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図16】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図17】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図18】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図19】第2の従来例における画質の階調性に関わる問題点を説明するための図である。

【図20】第2の従来例における階調性のビット誤差を説明するための概念図である。

【図21】本発明の第3および第4の実施例に係る画像処理装置のブロック図である。

【図22】図20の装置における同期制御部の構成図である。

【図23】本発明の第3の実施例の動作を説明するためのタイミングチャートである。

【図24】本発明の第3の実施例の動作を説明するためのタイミングチャートである。

【図25】本発明の第3の実施例の動作を説明するためのタイミングチャートである。

【図26】本発明の第3の実施例の動作を説明するためのタイミングチャートである。

【図27】本発明の第4の実施例の画質の階調性に対する動作を説明するための図である。

【図28】本発明の第4の実施例の画質の階調性に対する動作を説明するための図である。

【図29】本発明の第4の実施例の画質の階調性に対する動作を説明するための図である。

【図30】本発明の第5の実施例としての画像処理装置のブロック図である。

【図31】本発明の第5の実施例の動作を説明するための概念図である。

【符号の説明】

3,3−1,3−2:入力系画像処理部、4:メモリ制御部、5:メモリ部、6:出力系画像処理部、7:画像表示部、8:PLL、9:マイコン、10:同期制御部、12:発振器(第2クロック発生部)、ICK,ICK1,ICK2:入力系クロック(第1のクロック)、IHD,IHD1,IHD2:入力系水平同期信号(第1の画像同期信号)、IVD,IVD1,IVD2:入力系垂直同期信号(第1の画像同期信号)、OCK:出力系クロック(第2のクロック)、OHD:出力系水平同期信号(第2の画像同期信号)、OVD:出力系垂直同期信号(第2の画像同期信号)、RE:読み出しフィールド制御信号、WE:書込みフィールド制御信号。

Claims (5)

- 少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、第1のクロックと第1の画像同期信号により、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部とからなる画像処理装置において、 前記同期制御部は、第2のクロックを分周して、第1の画像同期信号とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号を同期化して作成した第4の画像同期信号を作成するとともに、出力する画像の使用目的に応じて、前記第3の画像同期信号と前記第4の画像同期信号の一方を選択し、前記第2の画像同期信号として出力することを特徴とする画像処理装置。

- 複数の入力系信号処理部と、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、前記複数の入力系信号処理部に入力される複数の入力信号に同期した複数の第1のクロック群と第1の画像同期信号群を用いて、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部からなる画像処理装置において、 前記同期制御部は、第2のクロックから分周され、第1の画像同期信号群とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号群をそれぞれ同期化して作成した第4の画像同期信号群を作成するとともに、出力する画像の使用目的に応じて、前記第3の画像同期信号と前記第4の画像同期信号群の中から一つの画像同期信号を選択し、前記第2の画像同期信号として出力することを特徴とする画像処理装置。

- 複数の入力系信号処理部と、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、前記複数の入力系信号処理部に入力される複数の入力信号に同期した複数の第1のクロック群と第1の画像同期信号群を用いて、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部からなる画像処理装置において、 前記同期制御部は、第2のクロックから分周され、第1の画像同期信号群とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号群をそれぞれ同期化して作成した第4の画像同期信号群を作成するとともに、前記複数の入力系信号処理部に入力する信号の動画の有無や割合に応じて、前記第3の画像同期信号と前記第4の画像同期信号群の中から一つの画像同期信号を選択し、前記第2の画像同期信号として出力することを特徴とする画像処理装置。

- 複数の入力系信号処理部と、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、前記複数の入力系信号処理部に入力される複数の入力信号に同期した複数の第1のクロック群と第1の画像同期信号群を用いて、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部からなる画像処理装置において、 前記同期制御部は、第2のクロックから分周され、第1の画像同期信号群とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号群をそれぞれ同期化して作成した第4の画像同期信号群を作成するとともに、前記複数の入力系信号の用途や種類に応じて、前記第3の画像同期信号と前記第4の画像同期信号群の中から一つの同期信号を選択し、第2の画像同期信号として出力することを特徴とする画像処理装置。

- 前記画像処理装置は、前記複数の入力系信号処理部に入力する信号源に対して、入力す る画像信号を設定、あるいは再設定する要求を出力するとともに、前記第3の画像同期信号と前記第4の画像同期信号群の中から選択して出力する第2の画像同期信号に同期していない任意の入力信号源に対して、第2の画像同期信号に同期する要求を出力する手段を有することを特徴とする請求項2〜4のいずれか1項に記載の画像処理装置。 【請求項6】 複数の入力系信号処理部と、少なくとも1画面分の画像を記憶する記憶領域を有するメモリ部と、前記複数の入力系信号処理部に入力される複数の入力信号に同期した複数の第1のクロック群と第1の画像同期信号群を用いて、このメモリ部へ画像データを書き込むための入力系の動作を行ない、第2のクロックと第2の画像同期信号により、このメモリ部から読み出した画像データを出力する出力系の動作を行なうメモリ制御部と、前記第2のクロックを作成するクロック発生部と、第2のクロックを入力し前記第2の画像同期信号を出力する同期制御部からなる画像処理装置において、 前記同期制御部は、第2のクロックから分周され、第1の画像同期信号群とは非同期の第3の画像同期信号と、第2のクロックにより、第1の画像同期信号群をそれぞれ同期化して作成した第4の画像同期信号群を作成するとともに、前記第3の画像同期信号と前記第4の画像同期信号群の中から一つの画像同期信号を選択して、前記第2の画像同期信号として出力し、 前記画像処理装置は、前記複数の入力系信号処理部に入力する信号源に対して、入力する画像信号を設定、あるいは再設定する要求を出力するとともに、前記第3の画像同期信号と前記第4の画像同期信号群の中から選択して出力する第2の画像同期信号に同期していない任意の入力信号源に対して、第2の画像同期信号に同期する要求を出力する手段を有することを特徴とする画像処理装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP31078599A JP3595745B2 (ja) | 1999-01-29 | 1999-11-01 | 画像処理装置 |

| US09/493,270 US6831634B1 (en) | 1999-01-29 | 2000-01-28 | Image processing device |

| DE60019828T DE60019828D1 (de) | 1999-01-29 | 2000-01-28 | Bildverarbeitungsvorrichtung |

| EP00300635A EP1024663B1 (en) | 1999-01-29 | 2000-01-28 | Image processing device |

| US10/948,343 US7079129B2 (en) | 1999-01-29 | 2004-09-24 | Image processing device |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP11-22751 | 1999-01-29 | ||

| JP2275199 | 1999-01-29 | ||

| JP31078599A JP3595745B2 (ja) | 1999-01-29 | 1999-11-01 | 画像処理装置 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004117076A Division JP3919766B2 (ja) | 1999-01-29 | 2004-04-12 | 画像処理装置 |

| JP2004117085A Division JP3919767B2 (ja) | 1999-01-29 | 2004-04-12 | 画像処理装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000284744A JP2000284744A (ja) | 2000-10-13 |

| JP3595745B2 true JP3595745B2 (ja) | 2004-12-02 |

Family

ID=26360018

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31078599A Expired - Fee Related JP3595745B2 (ja) | 1999-01-29 | 1999-11-01 | 画像処理装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6831634B1 (ja) |

| EP (1) | EP1024663B1 (ja) |

| JP (1) | JP3595745B2 (ja) |

| DE (1) | DE60019828D1 (ja) |

Families Citing this family (67)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3501722B2 (ja) | 2000-04-12 | 2004-03-02 | Necパーソナルプロダクツ株式会社 | 画像表示装置 |

| JP4859154B2 (ja) * | 2000-06-09 | 2012-01-25 | キヤノン株式会社 | 表示制御装置、表示制御システム、表示制御方法および記憶媒体 |

| IL156210A0 (en) * | 2000-12-01 | 2003-12-23 | Ginganet Corp | Video terminal, video terminal communication system, and video conferencing system |

| US7003147B2 (en) * | 2001-01-12 | 2006-02-21 | Canon Kabushiki Kaisha | Image processing apparatus |

| US20020103821A1 (en) * | 2001-01-26 | 2002-08-01 | Philips Electronics North America Corporation | System and method for providing a user interface for a deja video system |

| JP3556915B2 (ja) | 2001-03-09 | 2004-08-25 | 松下電器産業株式会社 | 動画像復号表示装置及び動画像復号表示方法 |

| US7495640B2 (en) * | 2001-03-12 | 2009-02-24 | Thomson Licensing | Reducing sparkle artifacts with post gamma correction slew rate limiting |

| US7061540B2 (en) * | 2001-12-19 | 2006-06-13 | Texas Instruments Incorporated | Programmable display timing generator |

| JP2003263140A (ja) * | 2001-12-27 | 2003-09-19 | Hitachi Ltd | 表示駆動制御回路 |

| JP3826159B2 (ja) * | 2001-12-27 | 2006-09-27 | 株式会社ルネサステクノロジ | 表示駆動制御回路 |

| JP2003304560A (ja) * | 2002-04-10 | 2003-10-24 | Sony Corp | デジタルビデオエンコーダ |

| JP2003324644A (ja) | 2002-05-07 | 2003-11-14 | Canon Inc | 映像信号処理装置、画像表示制御方法、記憶媒体、及びプログラム |

| JP3704121B2 (ja) * | 2002-11-28 | 2005-10-05 | Necディスプレイソリューションズ株式会社 | 画像信号中継装置、画像信号中継機能つき画像表示装置およびそれら装置の制御方法 |

| US7256797B2 (en) * | 2003-01-31 | 2007-08-14 | Yamaha Corporation | Image processing device with synchronized sprite rendering and sprite buffer |

| JP4326242B2 (ja) * | 2003-03-13 | 2009-09-02 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| TW591595B (en) * | 2003-05-23 | 2004-06-11 | Toppoly Optoelectronics Corp | LCD driving circuit |

| US7353284B2 (en) * | 2003-06-13 | 2008-04-01 | Apple Inc. | Synchronized transmission of audio and video data from a computer to a client via an interface |

| KR100540228B1 (ko) * | 2003-09-04 | 2006-01-10 | 엘지전자 주식회사 | 플라즈마 디스플레이 패널의 구동방법 |

| EP1921595A3 (en) * | 2003-09-30 | 2008-08-06 | LG Electronics Inc. | Method and apparatus of driving a plasma display panel |

| GB0323284D0 (en) * | 2003-10-04 | 2003-11-05 | Koninkl Philips Electronics Nv | Method and apparatus for processing image data |

| JP4617085B2 (ja) * | 2004-02-16 | 2011-01-19 | キヤノン株式会社 | 画像表示装置および画像表示方法 |

| KR100745035B1 (ko) * | 2004-03-05 | 2007-08-01 | 마쯔시다덴기산교 가부시키가이샤 | 화상 신호 처리 방법, 화상 신호 처리 장치, 및 화상 표시장치 |

| KR100604907B1 (ko) * | 2004-10-05 | 2006-07-28 | 삼성전자주식회사 | 데이터 인에이블 신호로부터 발생되는 수평/수직 동기신호로부터 신호의 안정성 여부를 판별하는 평판 표시장치의 싱크 프로세서 |

| JP2006178403A (ja) * | 2004-11-29 | 2006-07-06 | Nec Electronics Corp | 表示装置 |

| JP2006221514A (ja) * | 2005-02-14 | 2006-08-24 | Canon Inc | 生体認証装置及び画像取得方法 |

| JP4627672B2 (ja) * | 2005-03-23 | 2011-02-09 | シャープ株式会社 | 表示装置の駆動方法 |

| KR20070012972A (ko) * | 2005-07-25 | 2007-01-30 | 삼성전자주식회사 | 표시 장치, 그 구동 장치 및 방법 |

| CN100590688C (zh) * | 2006-02-23 | 2010-02-17 | 深圳迈瑞生物医疗电子股份有限公司 | 显示控制设备的显示时序参数自适应调整方法 |

| JP2007271848A (ja) * | 2006-03-31 | 2007-10-18 | Casio Comput Co Ltd | 映像出力装置、及び映像出力方法 |

| JP2007286449A (ja) * | 2006-04-19 | 2007-11-01 | Sharp Corp | 映像表示装置、映像表示方法および映像表示プログラム |

| JP2007304325A (ja) * | 2006-05-11 | 2007-11-22 | Necディスプレイソリューションズ株式会社 | 液晶表示装置および液晶パネル駆動方法 |

| KR101246568B1 (ko) * | 2006-06-09 | 2013-03-25 | 삼성전자주식회사 | 모바일 디스플레이 장치에서 가로 화면을 디스플레이하는방법과 장치 및 이를 포함하는 모바일 액정 표시 장치 |

| CN102750932B (zh) * | 2006-07-31 | 2014-12-03 | 夏普株式会社 | 显示控制器、显示装置、显示系统以及显示装置的控制方法 |

| CN102426826B (zh) | 2006-09-05 | 2016-03-02 | 夏普株式会社 | 显示控制器、显示装置、显示系统及显示装置的控制方法 |

| JP4983179B2 (ja) * | 2006-09-20 | 2012-07-25 | カシオ計算機株式会社 | 撮像装置、画像表示制御プログラム及び画像表示制御方法 |

| JP2008276067A (ja) * | 2007-05-02 | 2008-11-13 | Canon Inc | 映像表示装置及びその制御方法 |

| JP4922091B2 (ja) * | 2007-07-23 | 2012-04-25 | ルネサスエレクトロニクス株式会社 | 映像信号処理装置、映像信号処理方法及び表示装置 |

| JP2009044328A (ja) | 2007-08-07 | 2009-02-26 | Seiko Epson Corp | 会議システム、サーバ、画像表示方法、コンピュータプログラム及び記録媒体 |

| KR101437868B1 (ko) * | 2007-11-14 | 2014-09-05 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP2009009155A (ja) * | 2008-09-12 | 2009-01-15 | Hitachi Ltd | 表示装置および表示方法 |

| US10075670B2 (en) * | 2008-09-30 | 2018-09-11 | Entropic Communications, Llc | Profile for frame rate conversion |

| WO2010109598A1 (ja) * | 2009-03-25 | 2010-09-30 | Necディスプレイソリューションズ株式会社 | 映像表示装置 |

| JP5245984B2 (ja) * | 2009-03-30 | 2013-07-24 | ソニー株式会社 | 撮像素子、読み出し信号の変換方法およびカメラ |

| JP5272921B2 (ja) * | 2009-06-24 | 2013-08-28 | 富士通株式会社 | 表示装置 |

| CN102484680A (zh) * | 2009-09-29 | 2012-05-30 | 夏普株式会社 | 视频输出装置和视频的合成方法 |

| US8717474B2 (en) * | 2009-12-04 | 2014-05-06 | Canon Kabushiki Kaisha | Imaging apparatus and method for driving the same |

| US8692937B2 (en) * | 2010-02-25 | 2014-04-08 | Silicon Image, Inc. | Video frame synchronization |

| JP5522381B2 (ja) * | 2010-03-15 | 2014-06-18 | セイコーエプソン株式会社 | 表示装置、端末装置、表示システム、プログラム、情報記憶媒体、表示方法および画像変更方法 |

| JP5874178B2 (ja) * | 2010-04-09 | 2016-03-02 | ソニー株式会社 | カメラシステム、カメラ装置、カメラ制御装置、および中継装置 |

| JP2012083484A (ja) | 2010-10-08 | 2012-04-26 | Seiko Epson Corp | 表示装置、表示装置の制御方法、及び、プログラム |

| JP2013109026A (ja) * | 2011-11-17 | 2013-06-06 | Canon Inc | 映像出力装置およびその制御方法、プログラム |

| JP5488624B2 (ja) * | 2012-02-03 | 2014-05-14 | カシオ計算機株式会社 | 映像出力装置、及び映像出力方法 |

| US20140104242A1 (en) * | 2012-10-12 | 2014-04-17 | Nvidia Corporation | System and method for concurrent display of a video signal on a plurality of display devices |

| TWI536862B (zh) * | 2012-11-06 | 2016-06-01 | 聯詠科技股份有限公司 | 資料傳送系統及方法 |

| KR102081087B1 (ko) | 2013-06-17 | 2020-02-25 | 삼성전자주식회사 | 동기적 영상과 비동기적 영상을 위한 영상 정합 장치 및 이미지 센서 |

| US11549827B1 (en) | 2014-02-28 | 2023-01-10 | Infrared Cameras, Inc. | System and method for automated condition value reporting |

| US9745059B2 (en) * | 2014-02-28 | 2017-08-29 | Infrared Cameras, Inc. | System to adapt an optical device to calculate a condition value |

| JP6355409B2 (ja) * | 2014-04-25 | 2018-07-11 | キヤノン株式会社 | 映像受信装置、映像受信方法、及びプログラム |

| JP2016161753A (ja) * | 2015-03-02 | 2016-09-05 | セイコーエプソン株式会社 | 映像処理装置、表示装置、及び、映像処理方法 |

| US9880552B1 (en) | 2015-04-08 | 2018-01-30 | Gary Eugene Strahan | Wireless remote control to operate a radiometric camera mounted to an aerial vehicle |

| JP6552351B2 (ja) * | 2015-09-11 | 2019-07-31 | キヤノン株式会社 | 画像処理装置、撮像装置、画像処理方法、プログラム、および、記憶媒体 |

| CN106027942A (zh) * | 2016-05-20 | 2016-10-12 | 广东欧珀移动通信有限公司 | 一种帧率控制方法及装置 |

| US10128783B2 (en) * | 2016-05-31 | 2018-11-13 | Infineon Technologies Ag | Synchronization of internal oscillators of components sharing a communications bus |

| JP7016068B2 (ja) * | 2017-01-13 | 2022-02-04 | ディーブイエックス株式会社 | 映像統合システム |

| KR102429559B1 (ko) * | 2017-12-08 | 2022-08-04 | 삼성전자주식회사 | 디스플레이 장치, 및 그 제어 방법 |

| CN108924261B (zh) * | 2018-08-16 | 2021-01-12 | 成都掩码科技有限公司 | 一种高速帧精确内容馈送显示系统 |

| CN110310600B (zh) * | 2019-08-16 | 2021-03-05 | 上海天马有机发光显示技术有限公司 | 显示面板的驱动方法、显示驱动装置和电子设备 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4989039A (en) * | 1987-01-19 | 1991-01-29 | Canon Kabushiki Kaisha | Image forming apparatus responsive to environmental conditions |

| DE69033782T2 (de) * | 1989-10-14 | 2002-06-20 | Sony Corp., Tokio/Tokyo | Verfahren und Anordnung zum Kodieren/Dekodieren eines Videosignales |

| KR950010570B1 (ko) * | 1990-09-03 | 1995-09-19 | 마쯔시다덴기산교 가부시기가이샤 | 멀티포오트메모리 |

| EP0523299A1 (en) | 1991-07-18 | 1993-01-20 | International Business Machines Corporation | System and method for combining multiple composite video signals |

| US5519449A (en) * | 1991-09-17 | 1996-05-21 | Hitachi, Ltd. | Image composing and displaying method and apparatus for displaying a composite image of video signals and computer graphics |

| US5398078A (en) * | 1991-10-31 | 1995-03-14 | Kabushiki Kaisha Toshiba | Method of detecting a motion vector in an image coding apparatus |

| JPH05336503A (ja) * | 1992-05-29 | 1993-12-17 | Sony Corp | 映像付加情報判別装置 |

| US5298905A (en) * | 1992-06-12 | 1994-03-29 | Motorola, Inc. | Visible light detection and ranging apparatus and method |

| TW335241U (en) | 1992-11-30 | 1998-06-21 | Thomson Consumer Electronics | A video display system |

| US5389078A (en) * | 1993-10-06 | 1995-02-14 | Sims Deltec, Inc. | Programmable infusion pump for administering medication to patients |

| JP3579461B2 (ja) * | 1993-10-15 | 2004-10-20 | 株式会社ルネサステクノロジ | データ処理システム及びデータ処理装置 |

| US5812210A (en) | 1994-02-01 | 1998-09-22 | Hitachi, Ltd. | Display apparatus |

| JPH07319436A (ja) * | 1994-03-31 | 1995-12-08 | Mitsubishi Electric Corp | 半導体集積回路装置およびそれを用いた画像データ処理システム |

| US5731799A (en) | 1994-06-17 | 1998-03-24 | Motorola Inc. | Pixel-wise video registration system |

| JPH08137427A (ja) * | 1994-11-14 | 1996-05-31 | Matsushita Electric Ind Co Ltd | カラーフラットパネルを使用した表示装置の映像出力回路 |

| KR960020415A (ko) | 1994-11-23 | 1996-06-17 | 윌리엄 이. 힐러 | 디지탈 텔레비젼을 위한 특수 기능 |

| CN1135140A (zh) | 1995-02-27 | 1996-11-06 | 松下电器产业株式会社 | 用于多重图像显示的补偿电压发生装置及其视频显示装置 |

| JP3673303B2 (ja) * | 1995-07-27 | 2005-07-20 | 株式会社日立製作所 | 映像信号処理装置 |

| US6430363B2 (en) * | 1995-09-11 | 2002-08-06 | Matsushita Electric Industrial Co., Ltd. | Video signal recording and reproducing apparatus |

| JPH09182743A (ja) * | 1995-12-28 | 1997-07-15 | Shimadzu Corp | パルスx線透視装置 |

| US5828402A (en) * | 1996-06-19 | 1998-10-27 | Canadian V-Chip Design Inc. | Method and apparatus for selectively blocking audio and video signals |

| JP3384809B2 (ja) * | 1997-03-31 | 2003-03-10 | 三菱電機株式会社 | 平面表示パネルとその製造方法 |

| US6177922B1 (en) * | 1997-04-15 | 2001-01-23 | Genesis Microship, Inc. | Multi-scan video timing generator for format conversion |

| WO1998048571A1 (en) * | 1997-04-23 | 1998-10-29 | Thomson Consumer Electronics, Inc. | Control of video level by region and content of information displayed |

| EP0881834B1 (en) * | 1997-05-27 | 2006-03-22 | Pentax Corporation | Video signal switching device for endoscope system |

-

1999

- 1999-11-01 JP JP31078599A patent/JP3595745B2/ja not_active Expired - Fee Related

-

2000

- 2000-01-28 EP EP00300635A patent/EP1024663B1/en not_active Expired - Lifetime

- 2000-01-28 US US09/493,270 patent/US6831634B1/en not_active Expired - Fee Related

- 2000-01-28 DE DE60019828T patent/DE60019828D1/de not_active Expired - Lifetime

-

2004

- 2004-09-24 US US10/948,343 patent/US7079129B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000284744A (ja) | 2000-10-13 |

| US6831634B1 (en) | 2004-12-14 |

| EP1024663A2 (en) | 2000-08-02 |

| DE60019828D1 (de) | 2005-06-09 |

| EP1024663B1 (en) | 2005-05-04 |

| US20050078101A1 (en) | 2005-04-14 |

| EP1024663A3 (en) | 2003-07-23 |

| US7079129B2 (en) | 2006-07-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3595745B2 (ja) | 画像処理装置 | |

| JP3257788B2 (ja) | 画像表示装置 | |

| KR19980071592A (ko) | 이미지 업스케일 방법 및 장치 | |

| KR20020007707A (ko) | 멀티 소스용 포맷 변환 장치 | |

| JP2002006395A (ja) | 画像表示装置 | |

| JP3919766B2 (ja) | 画像処理装置 | |

| US20010035870A1 (en) | Overlay of plural images | |

| US5880741A (en) | Method and apparatus for transferring video data using mask data | |

| JP3483465B2 (ja) | 画像表示システム | |

| JP3919767B2 (ja) | 画像処理装置 | |

| US6005630A (en) | Method and apparatus for displaying images representing network application data along with interlaced images encoded in television signals. | |

| CA2316234C (en) | Flicker filter and interlacer implemented in a television system displaying network application data | |

| JP2004317928A (ja) | 液晶表示装置 | |

| JPH08137439A (ja) | 液晶表示装置及び液晶表示方法 | |

| JPH07255026A (ja) | テレビジョン信号表示装置 | |

| WO2021064801A1 (ja) | 表示装置及び表示装置の制御方法 | |

| JPH08317311A (ja) | 表示制御装置及びその制御方法 | |

| JP4019636B2 (ja) | 表示装置および表示方法 | |

| JPH08314408A (ja) | 液晶表示装置用画像出力装置及び液晶表示装置 | |

| JP2007293360A (ja) | 表示装置および表示方法 | |

| JP2588433B2 (ja) | カラー液晶表示装置の16色発生回路 | |

| JP2549029B2 (ja) | 映像信号表示装置 | |

| JP2025103124A (ja) | 回路装置及び表示システム | |

| CN117174041A (zh) | 一种过驱动装置、方法和显示装置 | |

| JPH06326937A (ja) | 画像信号変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040412 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040825 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040906 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20070910 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080910 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090910 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090910 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100910 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100910 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110910 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110910 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120910 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120910 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |