JP2011098435A5 - - Google Patents

Download PDFInfo

- Publication number

- JP2011098435A5 JP2011098435A5 JP2010266941A JP2010266941A JP2011098435A5 JP 2011098435 A5 JP2011098435 A5 JP 2011098435A5 JP 2010266941 A JP2010266941 A JP 2010266941A JP 2010266941 A JP2010266941 A JP 2010266941A JP 2011098435 A5 JP2011098435 A5 JP 2011098435A5

- Authority

- JP

- Japan

- Prior art keywords

- surface layer

- support

- layer

- semiconductor

- etch rate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000463 material Substances 0.000 claims description 32

- 238000005530 etching Methods 0.000 claims description 7

- 239000002344 surface layer Substances 0.000 claims 20

- 239000010410 layer Substances 0.000 claims 11

- 239000004065 semiconductor Substances 0.000 claims 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims 6

- 239000000377 silicon dioxide Substances 0.000 claims 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims 2

- 150000001875 compounds Chemical class 0.000 claims 2

- 229910052732 germanium Inorganic materials 0.000 claims 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims 2

- 239000000696 magnetic material Substances 0.000 claims 2

- 229910052710 silicon Inorganic materials 0.000 claims 2

- 239000010703 silicon Substances 0.000 claims 2

- 235000012239 silicon dioxide Nutrition 0.000 claims 2

- 229910052581 Si3N4 Inorganic materials 0.000 claims 1

- 229910004298 SiO 2 Inorganic materials 0.000 claims 1

- 229910021417 amorphous silicon Inorganic materials 0.000 claims 1

- 239000005380 borophosphosilicate glass Substances 0.000 claims 1

- 238000004377 microelectronic Methods 0.000 claims 1

- 239000000615 nonconductor Substances 0.000 claims 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims 1

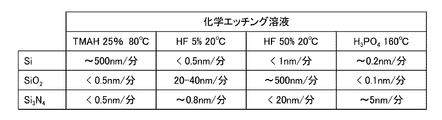

- 238000003486 chemical etching Methods 0.000 description 1

Images

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR0452217A FR2875947B1 (fr) | 2004-09-30 | 2004-09-30 | Nouvelle structure pour microelectronique et microsysteme et procede de realisation |

| US67380105P | 2005-04-22 | 2005-04-22 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007534016A Division JP2008514441A (ja) | 2004-09-30 | 2005-09-27 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011098435A JP2011098435A (ja) | 2011-05-19 |

| JP2011098435A5 true JP2011098435A5 (enExample) | 2013-04-11 |

Family

ID=34952707

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007534016A Pending JP2008514441A (ja) | 2004-09-30 | 2005-09-27 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

| JP2010266941A Pending JP2011098435A (ja) | 2004-09-30 | 2010-11-30 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

| JP2010266922A Pending JP2011098434A (ja) | 2004-09-30 | 2010-11-30 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007534016A Pending JP2008514441A (ja) | 2004-09-30 | 2005-09-27 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010266922A Pending JP2011098434A (ja) | 2004-09-30 | 2010-11-30 | マイクロエレクトロニクス及びマイクロシステムの新規構造、及びその製造方法 |

Country Status (9)

| Country | Link |

|---|---|

| US (2) | US20080036039A1 (enExample) |

| EP (1) | EP1794789B1 (enExample) |

| JP (3) | JP2008514441A (enExample) |

| KR (1) | KR100860546B1 (enExample) |

| CN (2) | CN101032014A (enExample) |

| AT (1) | ATE492029T1 (enExample) |

| DE (1) | DE602005025375D1 (enExample) |

| FR (1) | FR2875947B1 (enExample) |

| WO (1) | WO2006035031A1 (enExample) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2876220B1 (fr) * | 2004-10-06 | 2007-09-28 | Commissariat Energie Atomique | Procede d'elaboration de structures empilees mixtes, a zones isolantes diverses et/ou zones de conduction electrique verticale localisees. |

| US20060276008A1 (en) * | 2005-06-02 | 2006-12-07 | Vesa-Pekka Lempinen | Thinning |

| FR2897982B1 (fr) * | 2006-02-27 | 2008-07-11 | Tracit Technologies Sa | Procede de fabrication des structures de type partiellement soi, comportant des zones reliant une couche superficielle et un substrat |

| FR2932923B1 (fr) | 2008-06-23 | 2011-03-25 | Commissariat Energie Atomique | Substrat heterogene comportant une couche sacrificielle et son procede de realisation. |

| FR2932788A1 (fr) | 2008-06-23 | 2009-12-25 | Commissariat Energie Atomique | Procede de fabrication d'un composant electromecanique mems / nems. |

| FR2932789B1 (fr) | 2008-06-23 | 2011-04-15 | Commissariat Energie Atomique | Procede de fabrication d'une structure electromecanique comportant au moins un pilier de renfort mecanique. |

| US7927975B2 (en) * | 2009-02-04 | 2011-04-19 | Micron Technology, Inc. | Semiconductor material manufacture |

| US8637381B2 (en) * | 2011-10-17 | 2014-01-28 | International Business Machines Corporation | High-k dielectric and silicon nitride box region |

| WO2014020387A1 (en) | 2012-07-31 | 2014-02-06 | Soitec | Methods of forming semiconductor structures including mems devices and integrated circuits on opposing sides of substrates, and related structures and devices |

| WO2014064873A1 (ja) * | 2012-10-22 | 2014-05-01 | シャープ株式会社 | 半導体装置の製造方法 |

| CN104944361B (zh) * | 2014-03-25 | 2016-05-18 | 中芯国际集成电路制造(北京)有限公司 | 一种mems器件的制作方法 |

| CN106348245B (zh) * | 2015-07-23 | 2018-02-06 | 中芯国际集成电路制造(上海)有限公司 | 一种mems器件及其制备方法、电子装置 |

| CN105895575B (zh) * | 2016-05-09 | 2018-09-25 | 中国科学院上海微系统与信息技术研究所 | 一种图形化绝缘体上硅衬底材料及其制备方法 |

| CN108190828B (zh) * | 2018-02-07 | 2024-08-13 | 北京先通康桥医药科技有限公司 | Mems传感器线阵、触诊探头及其制造方法 |

| CN108682661A (zh) * | 2018-04-17 | 2018-10-19 | 中芯集成电路(宁波)有限公司 | 一种soi基底及soi基底的形成方法 |

| FR3086096B1 (fr) | 2018-09-14 | 2021-08-27 | Soitec Silicon On Insulator | Procede de realisation d'un substrat avance pour une integration hybride |

| FR3091032B1 (fr) * | 2018-12-20 | 2020-12-11 | Soitec Silicon On Insulator | Procédé de transfert d’une couche superficielle sur des cavités |

| US10981780B2 (en) * | 2019-08-19 | 2021-04-20 | Infineon Technologies Ag | Membrane support for dual backplate transducers |

| DE102021213259A1 (de) | 2021-11-25 | 2023-05-25 | Robert Bosch Gesellschaft mit beschränkter Haftung | Verfahren zur Herstellung eines Cavity SOI Substrats und mikromechanischen Strukturen darin |

Family Cites Families (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61184843A (ja) | 1985-02-13 | 1986-08-18 | Toshiba Corp | 複合半導体装置とその製造方法 |

| FR2579809B1 (fr) * | 1985-04-02 | 1987-05-15 | Thomson Csf | Procede de realisation de matrices decommande a diodes pour ecran plat de visualisation electro-optique et ecran plat realise par ce procede |

| NL8800847A (nl) * | 1988-04-05 | 1989-11-01 | Philips Nv | Werkwijze voor het vervaardigen van een halfgeleiderinrichting met een soi-struktuur. |

| US4956314A (en) * | 1989-05-30 | 1990-09-11 | Motorola, Inc. | Differential etching of silicon nitride |

| JPH088231B2 (ja) * | 1989-10-02 | 1996-01-29 | 大日本スクリーン製造株式会社 | 絶縁膜の選択的除去方法 |

| JPH0476951A (ja) * | 1990-07-18 | 1992-03-11 | Fujitsu Ltd | 半導体装置の製造方法および半導体装置 |

| US5376233A (en) * | 1992-02-10 | 1994-12-27 | Texas Instruments Incorporated | Method for selectively etching oxides |

| JP3367113B2 (ja) * | 1992-04-27 | 2003-01-14 | 株式会社デンソー | 加速度センサ |

| JPH06302834A (ja) * | 1993-04-09 | 1994-10-28 | Fujikura Ltd | 薄膜構造の製造方法 |

| US5393692A (en) * | 1993-07-28 | 1995-02-28 | Taiwan Semiconductor Manufacturing Company | Recessed side-wall poly plugged local oxidation |

| US5658698A (en) * | 1994-01-31 | 1997-08-19 | Canon Kabushiki Kaisha | Microstructure, process for manufacturing thereof and devices incorporating the same |

| JP3181174B2 (ja) * | 1994-06-08 | 2001-07-03 | キヤノン株式会社 | マイクロ構造体の形成方法 |

| US5466630A (en) * | 1994-03-21 | 1995-11-14 | United Microelectronics Corp. | Silicon-on-insulator technique with buried gap |

| JPH08105748A (ja) * | 1994-10-06 | 1996-04-23 | Murata Mfg Co Ltd | 角速度センサ、その共振周波数調整方法及びその製造方法 |

| JP3182301B2 (ja) * | 1994-11-07 | 2001-07-03 | キヤノン株式会社 | マイクロ構造体及びその形成法 |

| JP3430771B2 (ja) * | 1996-02-05 | 2003-07-28 | 株式会社デンソー | 半導体力学量センサの製造方法 |

| JPH10290036A (ja) * | 1997-04-11 | 1998-10-27 | Nissan Motor Co Ltd | 表面マイクロマシンの製造方法 |

| US6191007B1 (en) * | 1997-04-28 | 2001-02-20 | Denso Corporation | Method for manufacturing a semiconductor substrate |

| JPH1131825A (ja) * | 1997-07-10 | 1999-02-02 | Denso Corp | 半導体力学量センサの製造方法 |

| JP4144047B2 (ja) * | 1997-08-20 | 2008-09-03 | 株式会社デンソー | 半導体基板の製造方法 |

| US5976945A (en) * | 1997-11-20 | 1999-11-02 | Vanguard International Semiconductor Corporation | Method for fabricating a DRAM cell structure on an SOI wafer incorporating a two dimensional trench capacitor |

| US5972758A (en) * | 1997-12-04 | 1999-10-26 | Intel Corporation | Pedestal isolated junction structure and method of manufacture |

| JP4032476B2 (ja) * | 1997-12-25 | 2008-01-16 | 日産自動車株式会社 | 微小装置の製造方法 |

| JP3424550B2 (ja) * | 1998-04-13 | 2003-07-07 | 株式会社デンソー | 半導体力学量センサの製造方法 |

| JP4787412B2 (ja) * | 1999-03-30 | 2011-10-05 | シチズンホールディングス株式会社 | 薄膜基板の形成方法およびその方法によって形成された薄膜基板 |

| US6335292B1 (en) * | 1999-04-15 | 2002-01-01 | Micron Technology, Inc. | Method of controlling striations and CD loss in contact oxide etch |

| FR2795554B1 (fr) * | 1999-06-28 | 2003-08-22 | France Telecom | Procede de gravure laterale par trous pour fabriquer des dis positifs semi-conducteurs |

| WO2001006564A1 (fr) * | 1999-07-15 | 2001-01-25 | Shin-Etsu Handotai Co., Ltd. | Procede de production d'une plaquette encollee et plaquette encollee |

| FR2809867B1 (fr) * | 2000-05-30 | 2003-10-24 | Commissariat Energie Atomique | Substrat fragilise et procede de fabrication d'un tel substrat |

| US6372657B1 (en) * | 2000-08-31 | 2002-04-16 | Micron Technology, Inc. | Method for selective etching of oxides |

| DE10064494A1 (de) * | 2000-12-22 | 2002-07-04 | Bosch Gmbh Robert | Verfahren zur Herstellung eines Halbleiterbauelements sowie ein nach dem Verfahren hergestelltes Halbleiterbauelement, wobei das Halbleiterbauelement insbesondere eine bewegliche Masse aufweist |

| DE10124038A1 (de) * | 2001-05-16 | 2002-11-21 | Atmel Germany Gmbh | Verfahren zur Herstellung vergrabener Bereiche |

| US6835633B2 (en) * | 2002-07-24 | 2004-12-28 | International Business Machines Corporation | SOI wafers with 30-100 Å buried oxide (BOX) created by wafer bonding using 30-100 Å thin oxide as bonding layer |

| EP1535297B1 (en) * | 2002-08-26 | 2008-03-05 | International Business Machines Corporation | Diaphragm activated micro-electromechanical switch |

| EP1396883A3 (en) * | 2002-09-04 | 2005-11-30 | Canon Kabushiki Kaisha | Substrate and manufacturing method therefor |

| FR2847077B1 (fr) * | 2002-11-12 | 2006-02-17 | Soitec Silicon On Insulator | Composants semi-conducteurs, et notamment de type soi mixtes, et procede de realisation |

| JP4007172B2 (ja) * | 2002-12-03 | 2007-11-14 | ソニー株式会社 | マイクロマシンおよびその製造方法 |

| WO2004059725A1 (fr) * | 2002-12-20 | 2004-07-15 | S.O.I. Tec Silicon On Insulator Technologies | Procede de realisation de cavites dans une plaque de silicium |

| FR2849269B1 (fr) * | 2002-12-20 | 2005-07-29 | Soitec Silicon On Insulator | Procede de realisation de cavites dans une plaque de silicium |

| FR2850487B1 (fr) * | 2002-12-24 | 2005-12-09 | Commissariat Energie Atomique | Procede de realisation de substrats mixtes et structure ainsi obtenue |

| KR100546855B1 (ko) * | 2002-12-28 | 2006-01-25 | 동부아남반도체 주식회사 | 반도체 소자의 제조 방법 |

| JP4238724B2 (ja) * | 2003-03-27 | 2009-03-18 | 株式会社デンソー | 半導体装置 |

| JP2004319538A (ja) * | 2003-04-10 | 2004-11-11 | Seiko Epson Corp | 半導体装置の製造方法、集積回路、電子光学装置及び電子機器 |

| US6936491B2 (en) * | 2003-06-04 | 2005-08-30 | Robert Bosch Gmbh | Method of fabricating microelectromechanical systems and devices having trench isolated contacts |

| US6936522B2 (en) * | 2003-06-26 | 2005-08-30 | International Business Machines Corporation | Selective silicon-on-insulator isolation structure and method |

| FR2876220B1 (fr) * | 2004-10-06 | 2007-09-28 | Commissariat Energie Atomique | Procede d'elaboration de structures empilees mixtes, a zones isolantes diverses et/ou zones de conduction electrique verticale localisees. |

-

2004

- 2004-09-30 FR FR0452217A patent/FR2875947B1/fr not_active Expired - Fee Related

-

2005

- 2005-09-27 KR KR1020077006956A patent/KR100860546B1/ko not_active Expired - Lifetime

- 2005-09-27 DE DE602005025375T patent/DE602005025375D1/de active Active

- 2005-09-27 JP JP2007534016A patent/JP2008514441A/ja active Pending

- 2005-09-27 CN CNA200580033080XA patent/CN101032014A/zh active Pending

- 2005-09-27 AT AT05801275T patent/ATE492029T1/de not_active IP Right Cessation

- 2005-09-27 US US11/575,181 patent/US20080036039A1/en not_active Abandoned

- 2005-09-27 WO PCT/EP2005/054854 patent/WO2006035031A1/en not_active Ceased

- 2005-09-27 CN CN201210058695XA patent/CN102637626A/zh active Pending

- 2005-09-27 EP EP05801275A patent/EP1794789B1/en not_active Expired - Lifetime

-

2010

- 2010-11-30 JP JP2010266941A patent/JP2011098435A/ja active Pending

- 2010-11-30 JP JP2010266922A patent/JP2011098434A/ja active Pending

-

2012

- 2012-09-14 US US13/618,697 patent/US20130012024A1/en not_active Abandoned

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011098435A5 (enExample) | ||

| JP2011098434A5 (enExample) | ||

| US10573714B2 (en) | Sacrificial layer for channel surface retention and inner spacer formation in stacked-channel FETs | |

| US10658461B2 (en) | Nanowire with sacrificial top wire | |

| CN106847875B (zh) | 非平面栅极全包围器件及其制造方法 | |

| TWI280661B (en) | CMOS fabricated on different crystallographic orientation substrates | |

| US9859430B2 (en) | Local germanium condensation for suspended nanowire and finFET devices | |

| US10532925B2 (en) | Heater design for MEMS chamber pressure control | |

| US9716145B2 (en) | Strained stacked nanowire field-effect transistors (FETs) | |

| CN104249991B (zh) | Mems器件及其制作方法 | |

| TWI705040B (zh) | 由不同半導體材料組成之堆疊長條奈米形狀、結合該奈米形狀之結構及其形成之方法 | |

| US8852984B1 (en) | Technique for forming a MEMS device | |

| US20150008543A1 (en) | Mems capacitive pressure sensors and fabrication method thereof | |

| KR101654391B1 (ko) | 압전저항기를 갖춘 장치를 형성하는 방법 | |

| US20150008541A1 (en) | Mems pressure sensors and fabrication method thereof | |

| KR102465268B1 (ko) | 다양한 변형 상태를 갖는 핀 구조를 포함하는 반도체 구조를 제조하기 위한 방법, 및 관련 반도체 구조 | |

| CN107026127B (zh) | Fdsoi技术的外延分面高度一致性改进 | |

| TW201205802A (en) | Semiconductor device and method for forming the same | |

| JP2020505769A5 (enExample) | ||

| CN107004713B (zh) | 形成具有非对称外形的鳍状物结构的装置和方法 | |

| JP2007513517A5 (enExample) | ||

| JP2007513517A (ja) | 歪み半導体基板およびその製造プロセス | |

| US9947689B2 (en) | Semiconductor device structure with 110-PFET and 111-NFET current flow direction | |

| CN103917482A (zh) | 具有掩埋的导电区域的微机电器件及其制造工艺 | |

| CN103077921B (zh) | 互连线结构及互连线结构的形成方法 |