JP2005294833A - 回路基板及びその製法、それを使用した電気アセンブリ及びそれを使用した情報処理システム - Google Patents

回路基板及びその製法、それを使用した電気アセンブリ及びそれを使用した情報処理システム Download PDFInfo

- Publication number

- JP2005294833A JP2005294833A JP2005097961A JP2005097961A JP2005294833A JP 2005294833 A JP2005294833 A JP 2005294833A JP 2005097961 A JP2005097961 A JP 2005097961A JP 2005097961 A JP2005097961 A JP 2005097961A JP 2005294833 A JP2005294833 A JP 2005294833A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- circuit board

- circuit

- holes

- electrical

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/69—Insulating materials thereof

- H10W70/695—Organic materials

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0313—Organic insulating material

- H05K1/0353—Organic insulating material consisting of two or more materials, e.g. two or more polymers, polymer + filler, + reinforcement

- H05K1/0373—Organic insulating material consisting of two or more materials, e.g. two or more polymers, polymer + filler, + reinforcement containing additives, e.g. fillers

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/20—Conductive package substrates serving as an interconnection, e.g. metal plates

- H10W70/22—Conductive package substrates serving as an interconnection, e.g. metal plates having an heterogeneous or anisotropic structure

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/63—Vias, e.g. via plugs

- H10W70/635—Through-vias

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/02—Fillers; Particles; Fibers; Reinforcement materials

- H05K2201/0203—Fillers and particles

- H05K2201/0206—Materials

- H05K2201/0209—Inorganic, non-metallic particles

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/67—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their insulating layers or insulating parts

- H10W70/68—Shapes or dispositions thereof

- H10W70/685—Shapes or dispositions thereof comprising multiple insulating layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

Abstract

【解決手段】回路基板であって、定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維または同様のものを含まない電気的絶縁体を有する第1層を含み、少なくとも一つの回路層が電気的絶縁層上に置かれた回路基板。

【選択図】図6

Description

「回路基板であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを一部としても含まない電気的絶縁体を含む第1層を含み、前記第1層上に置かれた少なくとも一つの回路層を含むことを特徴とする回路基板」

であり、請求項2に係る発明の採った手段は、上記請求項1記載の回路基板について、

「前記第1層は複数のスルーホールを含み、前記回路基板の厚みに対する前記スルーホールそれぞれの直径の比率が約2:1から20:1の範囲内にある」

ものとしたことであり、請求項3に係る発明の採った手段は、上記請求項1記載の回路基板について、

「前記複数の粒子は、シリカもしくはセラミックの少なくともいずれか一方を含む」

ものとしたことであり、請求項4に係る発明の採った手段は、上記請求項3記載の回路基板について、

「前記粒子それぞれの大きさが、約200Åから35μmの範囲内にある」

ものとしたことであり、請求項5に係る発明の採った手段は、上記請求項3記載の回路基板について、

「前記少なくとも一つの回路層が、銅を含む」

ものとしたものであり、請求項6に係る発明の採った手段は、上記請求項1記載の回路基板について、

「さらに、前記少なくとも一つの回路層の反対側の前記第1層上に置かれた第2回路層を含む」

ものとしたものであり、請求項7に係る発明の採った手段は、上記請求項6記載の回路基板について、

「前記第1層の中に複数の導電性スルーホールを含み、前記伝導性スルーホールの選択されたいくつかは、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合する」

ものとしたものであり、請求項8に係る発明の採った手段は、上記請求項7記載の回路基板について、

「前記回路基板はチップキャリアを含む」

ものとしたものであり、請求項9に係る発明の採った手段は、上記請求項6記載の回路基板について、

「さらに、前記少なくとも一つの回路層及び前記第2回路層上にそれぞれに置かれた前記第2、第3の電気的絶縁体層を含み、第2、第3の電気的絶縁体層上にそれぞれに形成された第3、第四の回路層を含む」

ものとしたものであり、請求項10に係る発明の採った手段は、上記請求項1記載の回路基板について、

「前記粒子は、前記電気的絶縁体層の体積の約10〜80パーセントから成る」

なるものとしたことである。

「電気アセンブリであって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様なものを一部一部としても含まない電気的絶縁体を含む第1層を含み、

前記第1層上に少なくとも一つの回路層を含み、

前記回路基板の上に電気的に結合された少なくとも一つの電子部品を含む、回路基板を有する電気アセンブリ」

であり、請求項12に係る発明の採った手段は、上記請求項11記載の電気アセンブリについて、

「複数のスルーホールを含む前記回路基板の前記第1層を含み、前記回路基板の厚みの縦横比が2:1から20:1の範囲である」

ものとしたことであり、請求項13に係る発明の採った手段は、上記請求項11記載の電気アセンブリについて、

「前記複数の粒子が、シリカまたはセラミックの少なくともいずれか一方を含む」

ものとしたことであり、請求項14に係る発明の採った手段は、上記請求項13記載の電気アセンブリについて、

「前記粒子それぞれの大きさが、約200Åから35μmの範囲内にある」

ものとしたことであり、請求項15に係る発明の採った手段は、上記請求項14記載の電気アセンブリについて、

「前記少なくとも一つの回路層が、銅を含む」

ものとしたことであり、請求項16に係る発明の採った手段は、上記請求項11記載の電気アセンブリについて、

「さらに、前記第1層の少なくとも一つの回路層の反対側に前記第1層上に置かれた第2回路層を含む」

ものとしたことであり、請求項17に係る発明の採った手段は、上記請求項16記載の電気アセンブリについて、

「さらに、前記第1層の中に複数の導電性スルーホールを含み、前記伝導性スルーホールの選択されたいくつかは、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合する」

ものとしたことであり、請求項18に係る発明の採った手段は、上記請求項17記載の電気アセンブリについて、

「前記回路基板は、チップキャリアを含み、前記の少なくとも一つの回路層は、半導体チップを含む」

ものとしたことであり、請求項19に係る発明の採った手段は、上記請求項16記載の電気アセンブリについて、

「さらに、前記少なくとも一つの回路層及び前記第2回路層上にそれぞれに置かれた前記第2、第3の電気的絶縁体層を含み、第2、第3の電気的絶縁体層上にそれぞれに形成された第3、第4の回路層を含む」

ものとしたことであり、請求項20に係る発明の採った手段は、上記請求項16記載の電気アセンブリについて、

「前記粒子は、前記電気的絶縁体層の体積の約10〜80パーセントから成る」

ものとしたことである。

「回路基板を作る方法であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを、一部としても含まない電気的絶縁体を有する第1層を提供し、

前記電気的絶縁体の前記第1層上に、少なくとも一つの回路層を置くことを含む回路基板の製造方法」

であり、請求項22に係る発明の採った手段は、上記請求項21記載の回路基板の製造方法について、

「前記第1層の中に、前記回路基板の厚みの縦横比が2:1から20:1の範囲内である複数のスルーホールを提供する」

ものとしたことであり、請求項23に係る発明の採った手段は、上記請求項22記載の回路基板の製造方法について、

「前記複数のスルーホールを、レーザを使用することにより前記第1層の中に設ける」

ものとしたことであり、請求項24に係る発明の採った手段は、上記請求項21記載の回路基板の製造方法について、

「さらに、前記の少なくとも一つの回路層の反対側の前記第1層上に置かれた第2回路層を含む」

ものとしたことであり、請求項25に係る発明の採った手段は、上記請求項24記載の回路基板の製造方法について、

「前記第1層の中に複数の導電性スルーホールを提供することを含み、前記第1層は、前記伝導性スルーホールの選択されたいくつかが、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合するような層である」

ものとしたことであり、請求項26に係る発明の採った手段は、上記請求項19記載の回路基板の製造方法について、

「さらに、少なくとも一つの電気部品を、前記第1電気的絶縁体の前記第1層上に少なくとも一つの前記回路層を電気的に結合することを含む」

ものとしたことである。

「多層回路構造であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを、一部としても含まない電気的絶縁体を有する第1層を含む第1回路基板を含み、前記第1層上に少なくとも一つの回路基板が置かれており、前記回路基板が結合された伝導性スルーホールの第1密度の第1パターンを有し、

前記第1回路基板部の反対側に置かれた回路基板部を含み、その第2、第3の回路基板それぞれが、前記第1回路基板部の前記伝導スルーホール接続前記第1密度より低密度なスルーホール接続第2パターンを有し、前記第1回路基板部は、前記第2、第3回路基板部間の電気的接続を備えることを含む多層回路構造」

であり、請求項28に係る発明の採った手段は、上記請求項27記載の多層回路構造について、

「前記多層回路構造はプリント回路基板である」

としたものであり、請求項29に係る発明の採った手段は、上記請求項27記載の多層回路構造について、

「前記多層回路構造はチップキャリアである」

としたものであり、請求項30に係る発明の採った手段は、上記請求項29記載の多層回路構造について、

「前記チップキャリア及びその形成部上または内に少なくとも一つの半導体チップを有する」

請求項29記載の多層回路構造。

としたものである。

「情報処理システムであって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維または同様のものを、一部としても含まない電気的絶縁体を含む第1層を含み、

少なくとも一つの回路層が、前記第1層に置かれている回路基板と、

前記回路基板上に置かれ、電気的に結合された少なくとも一つの電気部品を一部として含むことを特徴とする情報処理システム」

であり、請求項32に係る発明の採った手段は、請求項31記載の情報処理システムについて、

「前記情報処理システムはパーソナルコンピュータを含む」

ものとしたものであり、請求項33に係る発明の採った手段は、上記請求項31記載の情報処理システムについて、

「前記情報処理システムは、メインフレームコンピュータを含む」

ものとしたものであり、請求項34に係る発明の採った手段は、上記請求項31記載の情報処理システムについて、

「前記情報処理システムは、コンピュータサーバーを含む」

ものとしたものである。

「回路基板であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを一部としても含まない電気的絶縁体を含む第1層を含み、前記第1層上に置かれた少なくとも一つの回路層を含むこと」

にその構成上の主たる特徴があり、これにより、回路基板技術を拡大することができて、新規で独自の回路基板及びその製法、それを使用した電気アセンブリ及びそれを使用した情報処理システムを提供することができるのである。

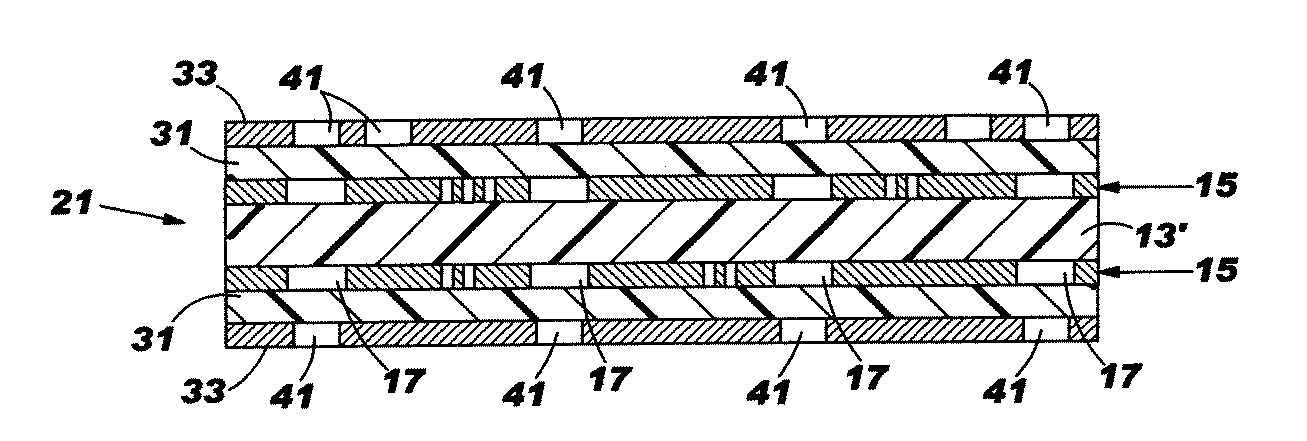

13、13′ (電気的絶縁)層

15 導電層

17 開口部

19ラインやパッド

21 基板

31、33 層

41 開口部

51 スルーホール

53 浅いスルーホール

71 回路基板

73 導電体層

81 電気的組み立て品

83 チップキャリア

85 PCB

87 半導体チップ

89、89′ ハンダ球

91 回路基板

Claims (34)

- 回路基板であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを一部としても含まない電気的絶縁体を含む第1層を含み、前記第1層上に置かれた少なくとも一つの回路層を含むことを特徴とする回路基板。 - 前記第1層は複数のスルーホールを含み、前記回路基板の厚みに対する前記スルーホールそれぞれの直径の比率が約2:1から20:1の範囲内にある請求項1記載の回路基板。

- 前記複数の粒子は、シリカもしくはセラミックの少なくともいずれか一方を含む請求項1の回路基板。

- 前記粒子それぞれの大きさが、約200Åから35μmの範囲内にある請求項3記載の回路基板。

- 前記少なくとも一つの回路層が、銅を含む請求項3記載の回路基板。

- さらに、前記少なくとも一つの回路層の反対側の前記第1層上に置かれた第2回路層を含む請求項1記載の回路基板。

- 前記第1層の中に複数の導電性スルーホールを含み、前記伝導性スルーホールの選択されたいくつかは、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合する、請求項6記載の回路基板。

- 前記回路基板はチップキャリアを含む請求項7記載の回路基板。

- さらに、前記少なくとも一つの回路層及び前記第2回路層上にそれぞれに置かれた前記第2、第3の電気的絶縁体層を含み、第2、第3の電気的絶縁体層上にそれぞれに形成された第3、第四の回路層を含む請求項6記載の回路基板。

- 前記粒子は、前記電気的絶縁体層の体積の約10〜80パーセントから成る請求項1記載の回路基板。

- 電気アセンブリであって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様なものを一部一部としても含まない電気的絶縁体を含む第1層を含み、

前記第1層上に少なくとも一つの回路層を含み、

前記回路基板の上に電気的に結合された少なくとも一つの電子部品を含む、回路基板を有する電気アセンブリ。 - 複数のスルーホールを含む前記回路基板の前記第1層を含み、前記回路基板の厚みの縦横比が2:1から20:1の範囲である請求項11記載の電気アセンブリ。

- 前記複数の粒子が、シリカまたはセラミックの少なくともいずれか一方を含む請求項11記載の電気アセンブリ。

- 前記粒子それぞれの大きさが、約200Åから35μmの範囲内にある請求項13記載の電気アセンブリ。

- 前記少なくとも一つの回路層が、銅を含む請求項14記載の電気アセンブリ。

- さらに、前記第1層の少なくとも一つの回路層の反対側に前記第1層上に置かれた第2回路層を含む請求項11記載の電気アセンブリ。

- さらに、前記第1層の中に複数の導電性スルーホールを含み、前記伝導性スルーホールの選択されたいくつかは、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合する、請求項16記載の電気アセンブリ。

- 前記回路基板は、チップキャリアを含み、前記の少なくとも一つの回路層は、半導体チップを含む請求項17記載の電気アセンブリ。

- さらに、前記少なくとも一つの回路層及び前記第2回路層上にそれぞれに置かれた前記第2、第3の電気的絶縁体層を含み、第2、第3の電気的絶縁体層上にそれぞれに形成された第3、第4の回路層を含む請求項16記載の電気アセンブリ。

- 前記粒子は、前記電気的絶縁体層の体積の約10〜80パーセントから成る請求項16記載の電気アセンブリ。

- 回路基板を作る方法であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを、一部としても含まない電気的絶縁体を有する第1層を提供し、

前記電気的絶縁体の前記第1層上に、少なくとも一つの回路層を置くことを含む回路基板の製造方法。 - 前記第1層の中に、前記回路基板の厚みの縦横比が2:1から20:1の範囲内である複数のスルーホールを提供する請求項21記載の回路基板の製造方法。

- 前記複数のスルーホールを、レーザを使用することにより前記第1層の中に設ける請求項22記載の回路基板の製造方法。

- さらに、前記の少なくとも一つの回路層の反対側の前記第1層上に置かれた第2回路層を含む請求項21記載の回路基板の製造方法。

- 前記第1層の中に複数の導電性スルーホールを提供することを含み、前記第1層は、前記伝導性スルーホールの選択されたいくつかが、前記少なくとも一つの回路層の選択された部分を前記第2回路層の選択された部分に電気的に結合するような層である請求項24記載の回路基板の製造方法。

- さらに、少なくとも一つの電気部品を、前記第1電気的絶縁体の前記第1層上に少なくとも一つの前記回路層を電気的に結合することを含む請求項19記載の回路基板の製造方法。

- 多層回路構造であって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維、または同様のものを、一部としても含まない電気的絶縁体を有する第1層を含む第1回路基板を含み、前記第1層上に少なくとも一つの回路基板が置かれており、前記回路基板が結合された伝導性スルーホールの第1密度の第1パターンを有し、

前記第1回路基板部の反対側に置かれた回路基板部を含み、その第2、第3の回路基板それぞれが、前記第1回路基板部の前記伝導スルーホール接続前記第1密度より低密度なスルーホール接続第2パターンを有し、前記第1回路基板部は、前記第2、第3回路基板部間の電気的接続を備えることを含む多層回路構造。 - 前記多層回路構造はプリント回路基板である請求項27記載の多層回路構造。

- 前記多層回路構造はチップキャリアである請求項27記載の多層回路構造。

- 前記チップキャリア及びその形成部上または内に少なくとも一つの半導体チップを有する請求項29記載の多層回路構造。

- 情報処理システムであって、

定量の粒子を有する樹脂材料を含み、連続的な繊維、半連続的な繊維または同様のものを、一部としても含まない電気的絶縁体を含む第1層を含み、

少なくとも一つの回路層が、前記第1層に置かれている回路基板と、

前記回路基板上に置かれ、電気的に結合された少なくとも一つの電気部品を一部として含むことを特徴とする情報処理システム。 - 前記情報処理システムはパーソナルコンピュータを含む請求項31記載の情報処理システム。

- 前記情報処理システムは、メインフレームコンピュータを含む請求項31記載の情報処理システム。

- 前記情報処理システムは、コンピュータサーバーを含む請求項31記載の情報処理システム。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/812,890 US7078816B2 (en) | 2004-03-31 | 2004-03-31 | Circuitized substrate |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294833A true JP2005294833A (ja) | 2005-10-20 |

Family

ID=34887688

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005097961A Pending JP2005294833A (ja) | 2004-03-31 | 2005-03-30 | 回路基板及びその製法、それを使用した電気アセンブリ及びそれを使用した情報処理システム |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US7078816B2 (ja) |

| EP (1) | EP1583405A3 (ja) |

| JP (1) | JP2005294833A (ja) |

| TW (1) | TW200603703A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011100734A (ja) * | 2009-11-09 | 2011-05-19 | Lg Innotek Co Ltd | 照明装置 |

Families Citing this family (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI242398B (en) * | 2000-06-14 | 2005-10-21 | Matsushita Electric Industrial Co Ltd | Printed circuit board and method of manufacturing the same |

| US7270845B2 (en) * | 2004-03-31 | 2007-09-18 | Endicott Interconnect Technologies, Inc. | Dielectric composition for forming dielectric layer for use in circuitized substrates |

| US20080136041A1 (en) * | 2006-01-24 | 2008-06-12 | Tessera Interconnect Materials, Inc. | Structure and method of making interconnect element having metal traces embedded in surface of dielectric |

| US8084863B2 (en) * | 2005-03-23 | 2011-12-27 | Endicott Interconnect Technologies, Inc. | Circuitized substrate with continuous thermoplastic support film dielectric layers |

| US7646098B2 (en) * | 2005-03-23 | 2010-01-12 | Endicott Interconnect Technologies, Inc. | Multilayered circuitized substrate with p-aramid dielectric layers and method of making same |

| US7627947B2 (en) * | 2005-04-21 | 2009-12-08 | Endicott Interconnect Technologies, Inc. | Method for making a multilayered circuitized substrate |

| US7602062B1 (en) * | 2005-08-10 | 2009-10-13 | Altera Corporation | Package substrate with dual material build-up layers |

| JP2007142333A (ja) * | 2005-11-22 | 2007-06-07 | Renesas Technology Corp | 半導体装置 |

| US20070141268A1 (en) * | 2005-12-19 | 2007-06-21 | Damon Brink | Composite meterial for printed circuit board applications |

| TWI298608B (en) * | 2006-05-19 | 2008-07-01 | Foxconn Advanced Tech Inc | Method for manufacturing stack via of hdi printed circuit board |

| SG139594A1 (en) * | 2006-08-04 | 2008-02-29 | Micron Technology Inc | Microelectronic devices and methods for manufacturing microelectronic devices |

| US7791437B2 (en) * | 2007-02-15 | 2010-09-07 | Motorola, Inc. | High frequency coplanar strip transmission line on a lossy substrate |

| CN101690434B (zh) * | 2007-06-26 | 2011-08-17 | 株式会社村田制作所 | 元器件内置基板的制造方法 |

| US7786944B2 (en) * | 2007-10-25 | 2010-08-31 | Motorola, Inc. | High frequency communication device on multilayered substrate |

| JP2011501473A (ja) | 2007-10-26 | 2011-01-06 | イー・アイ・デュポン・ドウ・ヌムール・アンド・カンパニー | 多層チップキャリアおよび製造方法 |

| US20090258161A1 (en) * | 2008-04-10 | 2009-10-15 | Japp Robert M | Circuitized substrate with P-aramid dielectric layers and method of making same |

| US7791897B2 (en) | 2008-09-09 | 2010-09-07 | Endicott Interconnect Technologies, Inc. | Multi-layer embedded capacitance and resistance substrate core |

| US8143532B2 (en) * | 2009-02-05 | 2012-03-27 | Xilinx, Inc. | Barrier layer to prevent conductive anodic filaments |

| US8955215B2 (en) | 2009-05-28 | 2015-02-17 | Hsio Technologies, Llc | High performance surface mount electrical interconnect |

| US9276336B2 (en) | 2009-05-28 | 2016-03-01 | Hsio Technologies, Llc | Metalized pad to electrical contact interface |

| WO2014011232A1 (en) | 2012-07-12 | 2014-01-16 | Hsio Technologies, Llc | Semiconductor socket with direct selective metalization |

| WO2011153298A1 (en) | 2010-06-03 | 2011-12-08 | Hsio Technologies, Llc | Electrical connector insulator housing |

| US9196980B2 (en) | 2009-06-02 | 2015-11-24 | Hsio Technologies, Llc | High performance surface mount electrical interconnect with external biased normal force loading |

| US9414500B2 (en) | 2009-06-02 | 2016-08-09 | Hsio Technologies, Llc | Compliant printed flexible circuit |

| US9136196B2 (en) | 2009-06-02 | 2015-09-15 | Hsio Technologies, Llc | Compliant printed circuit wafer level semiconductor package |

| US8987886B2 (en) | 2009-06-02 | 2015-03-24 | Hsio Technologies, Llc | Copper pillar full metal via electrical circuit structure |

| US9699906B2 (en) | 2009-06-02 | 2017-07-04 | Hsio Technologies, Llc | Hybrid printed circuit assembly with low density main core and embedded high density circuit regions |

| US9231328B2 (en) | 2009-06-02 | 2016-01-05 | Hsio Technologies, Llc | Resilient conductive electrical interconnect |

| WO2010141264A1 (en) | 2009-06-03 | 2010-12-09 | Hsio Technologies, Llc | Compliant wafer level probe assembly |

| WO2010141316A1 (en) | 2009-06-02 | 2010-12-09 | Hsio Technologies, Llc | Compliant printed circuit wafer probe diagnostic tool |

| WO2012061008A1 (en) | 2010-10-25 | 2012-05-10 | Hsio Technologies, Llc | High performance electrical circuit structure |

| US8525346B2 (en) | 2009-06-02 | 2013-09-03 | Hsio Technologies, Llc | Compliant conductive nano-particle electrical interconnect |

| WO2012074963A1 (en) | 2010-12-01 | 2012-06-07 | Hsio Technologies, Llc | High performance surface mount electrical interconnect |

| US8988093B2 (en) | 2009-06-02 | 2015-03-24 | Hsio Technologies, Llc | Bumped semiconductor wafer or die level electrical interconnect |

| US8610265B2 (en) | 2009-06-02 | 2013-12-17 | Hsio Technologies, Llc | Compliant core peripheral lead semiconductor test socket |

| US9613841B2 (en) | 2009-06-02 | 2017-04-04 | Hsio Technologies, Llc | Area array semiconductor device package interconnect structure with optional package-to-package or flexible circuit to package connection |

| WO2010141318A1 (en) | 2009-06-02 | 2010-12-09 | Hsio Technologies, Llc | Compliant printed circuit peripheral lead semiconductor test socket |

| US9603249B2 (en) | 2009-06-02 | 2017-03-21 | Hsio Technologies, Llc | Direct metalization of electrical circuit structures |

| WO2011002709A1 (en) | 2009-06-29 | 2011-01-06 | Hsio Technologies, Llc | Compliant printed circuit semiconductor tester interface |

| US9276339B2 (en) | 2009-06-02 | 2016-03-01 | Hsio Technologies, Llc | Electrical interconnect IC device socket |

| WO2012078493A1 (en) | 2010-12-06 | 2012-06-14 | Hsio Technologies, Llc | Electrical interconnect ic device socket |

| WO2010147934A1 (en) | 2009-06-16 | 2010-12-23 | Hsio Technologies, Llc | Semiconductor die terminal |

| US9277654B2 (en) | 2009-06-02 | 2016-03-01 | Hsio Technologies, Llc | Composite polymer-metal electrical contacts |

| WO2010141313A1 (en) | 2009-06-02 | 2010-12-09 | Hsio Technologies, Llc | Compliant printed circuit socket diagnostic tool |

| US8955216B2 (en) | 2009-06-02 | 2015-02-17 | Hsio Technologies, Llc | Method of making a compliant printed circuit peripheral lead semiconductor package |

| US8618649B2 (en) | 2009-06-02 | 2013-12-31 | Hsio Technologies, Llc | Compliant printed circuit semiconductor package |

| US9318862B2 (en) | 2009-06-02 | 2016-04-19 | Hsio Technologies, Llc | Method of making an electronic interconnect |

| US9930775B2 (en) | 2009-06-02 | 2018-03-27 | Hsio Technologies, Llc | Copper pillar full metal via electrical circuit structure |

| US9054097B2 (en) | 2009-06-02 | 2015-06-09 | Hsio Technologies, Llc | Compliant printed circuit area array semiconductor device package |

| US9184145B2 (en) | 2009-06-02 | 2015-11-10 | Hsio Technologies, Llc | Semiconductor device package adapter |

| WO2010147782A1 (en) | 2009-06-16 | 2010-12-23 | Hsio Technologies, Llc | Simulated wirebond semiconductor package |

| US9320144B2 (en) | 2009-06-17 | 2016-04-19 | Hsio Technologies, Llc | Method of forming a semiconductor socket |

| US8984748B2 (en) | 2009-06-29 | 2015-03-24 | Hsio Technologies, Llc | Singulated semiconductor device separable electrical interconnect |

| US20110017498A1 (en) * | 2009-07-27 | 2011-01-27 | Endicott Interconnect Technologies, Inc. | Photosensitive dielectric film |

| JP5331891B2 (ja) * | 2009-09-21 | 2013-10-30 | 株式会社東芝 | 半導体装置 |

| US20110146493A1 (en) * | 2009-12-22 | 2011-06-23 | General Electric Company | Filter bag and laminated filter media |

| US20110207866A1 (en) * | 2010-02-25 | 2011-08-25 | Japp Robert M | Halogen-Free Dielectric Composition For use As Dielectric Layer In Circuitized Substrates |

| US8198551B2 (en) | 2010-05-18 | 2012-06-12 | Endicott Interconnect Technologies, Inc. | Power core for use in circuitized substrate and method of making same |

| US9689897B2 (en) | 2010-06-03 | 2017-06-27 | Hsio Technologies, Llc | Performance enhanced semiconductor socket |

| US10159154B2 (en) | 2010-06-03 | 2018-12-18 | Hsio Technologies, Llc | Fusion bonded liquid crystal polymer circuit structure |

| US8758067B2 (en) | 2010-06-03 | 2014-06-24 | Hsio Technologies, Llc | Selective metalization of electrical connector or socket housing |

| US9350093B2 (en) | 2010-06-03 | 2016-05-24 | Hsio Technologies, Llc | Selective metalization of electrical connector or socket housing |

| CN102612266B (zh) * | 2011-01-21 | 2014-10-01 | 富葵精密组件(深圳)有限公司 | 电路板的制作方法 |

| KR101776322B1 (ko) * | 2011-09-02 | 2017-09-07 | 엘지이노텍 주식회사 | 칩 패키지 부재 제조 방법 |

| US8446707B1 (en) | 2011-10-10 | 2013-05-21 | Endicott Interconnect Technologies, Inc. | Circuitized substrate with low loss capacitive material and method of making same |

| CA2865425C (en) * | 2012-03-13 | 2016-11-29 | W.L. Gore & Associates, Inc. | Venting array and manufacturing method |

| US10370573B2 (en) * | 2012-05-21 | 2019-08-06 | Toyo Ink Sc Holdings Co., Ltd. | Easily deformable aggregate and method for manufacturing same, thermally conductive resin composition, thermally conductive member and method for manufacturing same, and thermally conductive adhesive sheet |

| US9761520B2 (en) | 2012-07-10 | 2017-09-12 | Hsio Technologies, Llc | Method of making an electrical connector having electrodeposited terminals |

| CN205584642U (zh) * | 2013-07-11 | 2016-09-14 | 株式会社村田制作所 | 树脂多层基板 |

| US10667410B2 (en) | 2013-07-11 | 2020-05-26 | Hsio Technologies, Llc | Method of making a fusion bonded circuit structure |

| US10506722B2 (en) | 2013-07-11 | 2019-12-10 | Hsio Technologies, Llc | Fusion bonded liquid crystal polymer electrical circuit structure |

| EP3058591B1 (fr) * | 2013-10-18 | 2020-11-18 | Griset | Support pour composants électroniques de puissance, module de puissance doté d'un tel support, et procédé de fabrication correspondant |

| TWI566659B (zh) * | 2014-09-18 | 2017-01-11 | 矽品精密工業股份有限公司 | 封裝基板及其製法 |

| US9559447B2 (en) | 2015-03-18 | 2017-01-31 | Hsio Technologies, Llc | Mechanical contact retention within an electrical connector |

| CN106550557A (zh) * | 2016-11-25 | 2017-03-29 | 湖北惠商电路科技有限公司 | 一种多层印制线路板及其制备方法 |

| CN113013131A (zh) * | 2019-12-20 | 2021-06-22 | 群创光电股份有限公司 | 发光装置及包含其的拼接式显示器 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11220262A (ja) * | 1997-11-25 | 1999-08-10 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュールおよびその製造方法 |

| JP2000138457A (ja) * | 1998-11-02 | 2000-05-16 | Kyocera Corp | 多層配線基板およびその製造方法 |

| JP2000165052A (ja) * | 1998-11-30 | 2000-06-16 | Kyocera Corp | 多層配線基板 |

| JP2001244638A (ja) * | 1999-12-20 | 2001-09-07 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュール及びその製造方法 |

| JP2002305364A (ja) * | 1997-11-25 | 2002-10-18 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュールおよびその製造方法 |

Family Cites Families (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE392582B (sv) | 1970-05-21 | 1977-04-04 | Gore & Ass | Forfarande vid framstellning av ett porost material, genom expandering och streckning av en tetrafluoretenpolymer framstelld i ett pastabildande strengsprutningsforfarande |

| US3853566A (en) * | 1972-12-21 | 1974-12-10 | Gen Electric | Hot pressed silicon carbide |

| FR2256582B1 (ja) * | 1973-12-27 | 1976-11-19 | Trt Telecom Radio Electr | |

| JPS5649271A (en) | 1979-09-28 | 1981-05-02 | Matsushita Electric Works Ltd | Phenol resin laminated board |

| US4482516A (en) * | 1982-09-10 | 1984-11-13 | W. L. Gore & Associates, Inc. | Process for producing a high strength porous polytetrafluoroethylene product having a coarse microstructure |

| US4579772A (en) * | 1983-12-19 | 1986-04-01 | International Business Machines Corporation | Glass cloth for printed circuits and method of manufacture wherein yarns have a substantially elliptical cross-section |

| JPH023631Y2 (ja) * | 1984-12-28 | 1990-01-29 | ||

| GB8519290D0 (en) * | 1985-07-31 | 1985-09-04 | Dow Chemical Rheinwerk Gmbh | Resin composition |

| US5246817A (en) * | 1985-08-02 | 1993-09-21 | Shipley Company, Inc. | Method for manufacture of multilayer circuit board |

| US4642160A (en) * | 1985-08-12 | 1987-02-10 | Interconnect Technology Inc. | Multilayer circuit board manufacturing |

| DE3776642D1 (de) * | 1986-12-15 | 1992-03-19 | Siemens Nixdorf Inf Syst | Verfahren zur herstellung von prepregs und deren verwendung. |

| US4864722A (en) * | 1988-03-16 | 1989-09-12 | International Business Machines Corporation | Low dielectric printed circuit boards |

| EP0384940B1 (de) * | 1989-03-03 | 1994-06-22 | Siemens Aktiengesellschaft | Epoxidharzmischungen |

| US5538789A (en) * | 1990-02-09 | 1996-07-23 | Toranaga Technologies, Inc. | Composite substrates for preparation of printed circuits |

| JP2993065B2 (ja) * | 1990-07-27 | 1999-12-20 | 三菱瓦斯化学株式会社 | 表面平滑金属箔張積層板 |

| JP2739726B2 (ja) * | 1990-09-27 | 1998-04-15 | インターナシヨナル・ビジネス・マシーンズ・コーポレーシヨン | 多層プリント回路板 |

| US5229550A (en) * | 1990-10-30 | 1993-07-20 | International Business Machines Corporation | Encapsulated circuitized power core alignment and lamination |

| US5129142A (en) * | 1990-10-30 | 1992-07-14 | International Business Machines Corporation | Encapsulated circuitized power core alignment and lamination |

| US5418689A (en) * | 1993-02-01 | 1995-05-23 | International Business Machines Corporation | Printed circuit board or card for direct chip attachment and fabrication thereof |

| DE4340834A1 (de) * | 1993-03-15 | 1994-09-22 | Siemens Ag | Phosphormodifizierte Epoxidharze, Verfahren zu ihrer Herstellung sowie ihre Verwendung |

| CA2119050C (en) * | 1993-03-18 | 1999-11-23 | Nayan H. Joshi | Self accelerating and replenishing non-formaldehyde immersion coating method and composition |

| US6710259B2 (en) * | 1993-05-17 | 2004-03-23 | Electrochemicals, Inc. | Printed wiring boards and methods for making them |

| US6140402A (en) * | 1993-07-30 | 2000-10-31 | Diemat, Inc. | Polymeric adhesive paste |

| JP3648750B2 (ja) | 1993-09-14 | 2005-05-18 | 株式会社日立製作所 | 積層板及び多層プリント回路板 |

| US5677045A (en) * | 1993-09-14 | 1997-10-14 | Hitachi, Ltd. | Laminate and multilayer printed circuit board |

| JPH0797466A (ja) | 1993-09-28 | 1995-04-11 | Dainippon Ink & Chem Inc | プリプレグ |

| JP2531464B2 (ja) * | 1993-12-10 | 1996-09-04 | 日本電気株式会社 | 半導体パッケ―ジ |

| US5652055A (en) * | 1994-07-20 | 1997-07-29 | W. L. Gore & Associates, Inc. | Matched low dielectric constant, dimensionally stable adhesive sheet |

| JPH0892394A (ja) | 1994-09-27 | 1996-04-09 | Shin Kobe Electric Mach Co Ltd | 積層板成形用プリプレグおよび積層板 |

| JP3199592B2 (ja) * | 1995-01-27 | 2001-08-20 | 株式会社日立製作所 | 多層印刷回路基板 |

| US5670250A (en) * | 1995-02-24 | 1997-09-23 | Polyclad Laminates, Inc. | Circuit board prepreg with reduced dielectric constant |

| US5670262A (en) * | 1995-05-09 | 1997-09-23 | The Dow Chemical Company | Printing wiring board(s) having polyimidebenzoxazole dielectric layer(s) and the manufacture thereof |

| JPH08321681A (ja) * | 1995-05-26 | 1996-12-03 | Hitachi Chem Co Ltd | マルチワイヤ配線板およびその製造法 |

| DE69610771T2 (de) * | 1995-06-27 | 2001-02-22 | Hitachi Chemical Co., Ltd. | Epoxidharzzusammensetzung für gedrückte leiterplatten und damit hergestellte schichtstoffplatten |

| US5814405A (en) * | 1995-08-04 | 1998-09-29 | W. L. Gore & Associates, Inc. | Strong, air permeable membranes of polytetrafluoroethylene |

| US6405431B1 (en) * | 1996-06-27 | 2002-06-18 | Samsung Electro-Mechanics Co., Ltd. | Method for manufacturing build-up multi-layer printed circuit board by using yag laser |

| US5822856A (en) * | 1996-06-28 | 1998-10-20 | International Business Machines Corporation | Manufacturing circuit board assemblies having filled vias |

| US5679444A (en) * | 1996-07-15 | 1997-10-21 | International Business Machines Corporation | Method for producing multi-layer circuit board and resulting article of manufacture |

| US5981880A (en) * | 1996-08-20 | 1999-11-09 | International Business Machines Corporation | Electronic device packages having glass free non conductive layers |

| US5837355A (en) * | 1996-11-07 | 1998-11-17 | Sumitomo Bakelite Company Limited | Multilayer printed circuit board and process for producing and using the same |

| JP2001525120A (ja) * | 1996-11-08 | 2001-12-04 | ダブリュ.エル.ゴア アンド アソシエイツ,インコーポレイティド | ブラインドおよびスルーの両マイクロ―ヴァイアの入口の品質を向上するために吸光コーティングを用いる方法 |

| US5900312A (en) * | 1996-11-08 | 1999-05-04 | W. L. Gore & Associates, Inc. | Integrated circuit chip package assembly |

| WO1998020528A1 (en) * | 1996-11-08 | 1998-05-14 | W.L. Gore & Associates, Inc. | METHOD FOR IMPROVING RELIABILITY OF THIN CIRCUIT SUBSTRATES BY INCREASING THE Tg OF THE SUBSTRATE |

| US6323436B1 (en) * | 1997-04-08 | 2001-11-27 | International Business Machines Corporation | High density printed wiring board possessing controlled coefficient of thermal expansion with thin film redistribution layer |

| US6038133A (en) * | 1997-11-25 | 2000-03-14 | Matsushita Electric Industrial Co., Ltd. | Circuit component built-in module and method for producing the same |

| US6207595B1 (en) * | 1998-03-02 | 2001-03-27 | International Business Machines Corporation | Laminate and method of manufacture thereof |

| US6119338A (en) * | 1998-03-19 | 2000-09-19 | Industrial Technology Research Institute | Method for manufacturing high-density multilayer printed circuit boards |

| US6207259B1 (en) * | 1998-11-02 | 2001-03-27 | Kyocera Corporation | Wiring board |

| US6212769B1 (en) * | 1999-06-29 | 2001-04-10 | International Business Machines Corporation | Process for manufacturing a printed wiring board |

| US6291779B1 (en) * | 1999-06-30 | 2001-09-18 | International Business Machines Corporation | Fine pitch circuitization with filled plated through holes |

| JP4282161B2 (ja) | 1999-07-02 | 2009-06-17 | イビデン株式会社 | 多層プリント配線板及び多層プリント配線板の製造方法 |

| US6538210B2 (en) * | 1999-12-20 | 2003-03-25 | Matsushita Electric Industrial Co., Ltd. | Circuit component built-in module, radio device having the same, and method for producing the same |

| US6506979B1 (en) * | 2000-05-12 | 2003-01-14 | Shipley Company, L.L.C. | Sequential build circuit board |

| JP2002223070A (ja) | 2001-01-29 | 2002-08-09 | Hitachi Metals Ltd | メタルコアプリント配線板用金属板の製造方法及びメタルコアプリント配線板の製造方法 |

| US6669805B2 (en) * | 2001-02-16 | 2003-12-30 | International Business Machines Corporation | Drill stack formation |

| JP2003046250A (ja) * | 2001-02-28 | 2003-02-14 | Furukawa Electric Co Ltd:The | ビア付きビルドアップ用多層基板及びその製造方法 |

| KR100492498B1 (ko) * | 2001-05-21 | 2005-05-30 | 마츠시다 덴코 가부시키가이샤 | 프린트 배선판의 제조 방법 |

| TW583348B (en) * | 2001-06-19 | 2004-04-11 | Phoenix Prec Technology Corp | A method for electroplating Ni/Au layer substrate without using electroplating wire |

| KR100557554B1 (ko) | 2001-06-21 | 2006-03-03 | 주식회사 하이닉스반도체 | 불소가 치환된 벤질 카르복실레이트 그룹을 포함하는단량체 및 이를 함유한 포토레지스트 중합체 |

| US6586687B2 (en) * | 2001-09-10 | 2003-07-01 | Ttm Technologies, Inc. | Printed wiring board with high density inner layer structure |

| US6541589B1 (en) * | 2001-10-15 | 2003-04-01 | Gore Enterprise Holdings, Inc. | Tetrafluoroethylene copolymer |

| US7164197B2 (en) * | 2003-06-19 | 2007-01-16 | 3M Innovative Properties Company | Dielectric composite material |

| US7795744B2 (en) * | 2003-12-19 | 2010-09-14 | Henkel Corporation | Cationically curable epoxy resin composition |

-

2004

- 2004-03-31 US US10/812,890 patent/US7078816B2/en not_active Expired - Lifetime

-

2005

- 2005-03-18 TW TW094108414A patent/TW200603703A/zh unknown

- 2005-03-22 EP EP05251748A patent/EP1583405A3/en not_active Withdrawn

- 2005-03-30 JP JP2005097961A patent/JP2005294833A/ja active Pending

-

2006

- 2006-02-09 US US11/349,990 patent/US7416996B2/en not_active Expired - Lifetime

- 2006-02-10 US US11/350,777 patent/US7508076B2/en not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11220262A (ja) * | 1997-11-25 | 1999-08-10 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュールおよびその製造方法 |

| JP2002305364A (ja) * | 1997-11-25 | 2002-10-18 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュールおよびその製造方法 |

| JP2000138457A (ja) * | 1998-11-02 | 2000-05-16 | Kyocera Corp | 多層配線基板およびその製造方法 |

| JP2000165052A (ja) * | 1998-11-30 | 2000-06-16 | Kyocera Corp | 多層配線基板 |

| JP2001244638A (ja) * | 1999-12-20 | 2001-09-07 | Matsushita Electric Ind Co Ltd | 回路部品内蔵モジュール及びその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011100734A (ja) * | 2009-11-09 | 2011-05-19 | Lg Innotek Co Ltd | 照明装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7078816B2 (en) | 2006-07-18 |

| EP1583405A2 (en) | 2005-10-05 |

| EP1583405A3 (en) | 2007-11-07 |

| US20060125103A1 (en) | 2006-06-15 |

| US7508076B2 (en) | 2009-03-24 |

| US20050224985A1 (en) | 2005-10-13 |

| TW200603703A (en) | 2006-01-16 |

| US7416996B2 (en) | 2008-08-26 |

| US20060131755A1 (en) | 2006-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005294833A (ja) | 回路基板及びその製法、それを使用した電気アセンブリ及びそれを使用した情報処理システム | |

| JP2005294829A (ja) | 回路基板に用いる電気的絶縁層を形成するための電気的絶縁構造体 | |

| US7416972B2 (en) | Method of making same low moisture absorptive circuitized substrave with reduced thermal expansion | |

| US7429789B2 (en) | Fluoropolymer dielectric composition for use in circuitized substrates and circuitized substrate including same | |

| CN100477891C (zh) | 多层布线基板及其制造方法、纤维强化树脂基板制造方法 | |

| CN101175369A (zh) | 电路化衬底,其制造方法及衬底结构和信息处理系统 | |

| TWI407850B (zh) | 具有一作為部份電路之核心層的積層式印刷佈線板基材 | |

| US8198551B2 (en) | Power core for use in circuitized substrate and method of making same | |

| US8211790B2 (en) | Multilayered circuitized substrate with P-aramid dielectric layers and method of making same | |

| US20100224397A1 (en) | Wiring board and method for manufacturing the same | |

| JP2007266606A (ja) | 回路基板用のフルオロポリマー絶縁性組成物およびこれから成る回路基板 | |

| JP2004087856A (ja) | 多層配線基板 | |

| US8084863B2 (en) | Circuitized substrate with continuous thermoplastic support film dielectric layers | |

| US7145221B2 (en) | Low moisture absorptive circuitized substrate, method of making same, electrical assembly utilizing same, and information handling system utilizing same | |

| US20090258161A1 (en) | Circuitized substrate with P-aramid dielectric layers and method of making same | |

| US20110207866A1 (en) | Halogen-Free Dielectric Composition For use As Dielectric Layer In Circuitized Substrates | |

| US7931830B2 (en) | Dielectric composition for use in circuitized substrates and circuitized substrate including same | |

| JP2007129215A (ja) | 回路基板において使用される絶縁組成物、およびこの絶縁組成物を使用して形成した回路基板 | |

| KR100703023B1 (ko) | 다층 배선 기판, 그 제조 방법, 및 파이버 강화 수지기판의 제조 방법 | |

| JP2006203142A (ja) | 半導体パッケージ用多層プリント配線板 | |

| JP2009188363A (ja) | 多層プリント配線板及びその製造方法 | |

| JP2000165000A (ja) | プリント配線板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080305 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20080305 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20091104 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100628 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101214 |