CN1877448A - 蚀刻剂及使用蚀刻剂制造布线及薄膜晶体管基板的方法 - Google Patents

蚀刻剂及使用蚀刻剂制造布线及薄膜晶体管基板的方法 Download PDFInfo

- Publication number

- CN1877448A CN1877448A CNA2006100674071A CN200610067407A CN1877448A CN 1877448 A CN1877448 A CN 1877448A CN A2006100674071 A CNA2006100674071 A CN A2006100674071A CN 200610067407 A CN200610067407 A CN 200610067407A CN 1877448 A CN1877448 A CN 1877448A

- Authority

- CN

- China

- Prior art keywords

- layer

- etchant

- conductive oxide

- scope

- oxide layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 72

- 239000010409 thin film Substances 0.000 title claims abstract description 12

- 239000000758 substrate Substances 0.000 title claims description 62

- 238000005530 etching Methods 0.000 claims abstract description 63

- 239000000463 material Substances 0.000 claims abstract description 38

- USFZMSVCRYTOJT-UHFFFAOYSA-N Ammonium acetate Chemical compound N.CC(O)=O USFZMSVCRYTOJT-UHFFFAOYSA-N 0.000 claims abstract description 17

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims abstract description 13

- 239000008367 deionised water Substances 0.000 claims abstract description 11

- 229910021641 deionized water Inorganic materials 0.000 claims abstract description 11

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 8

- 229910052710 silicon Inorganic materials 0.000 claims abstract description 8

- 125000000217 alkyl group Chemical group 0.000 claims abstract description 7

- 229910052782 aluminium Inorganic materials 0.000 claims abstract description 7

- 229910052788 barium Inorganic materials 0.000 claims abstract description 7

- 229910052796 boron Inorganic materials 0.000 claims abstract description 7

- 229910052804 chromium Inorganic materials 0.000 claims abstract description 7

- 229910052742 iron Inorganic materials 0.000 claims abstract description 7

- 229910052718 tin Inorganic materials 0.000 claims abstract description 7

- 229910052719 titanium Inorganic materials 0.000 claims abstract description 7

- 229910052725 zinc Inorganic materials 0.000 claims abstract description 7

- 239000004065 semiconductor Substances 0.000 claims description 33

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 claims description 26

- 239000012212 insulator Substances 0.000 claims description 24

- 238000004519 manufacturing process Methods 0.000 claims description 20

- 238000010276 construction Methods 0.000 claims description 17

- 229910001316 Ag alloy Inorganic materials 0.000 claims description 16

- 239000005695 Ammonium acetate Substances 0.000 claims description 15

- 229940043376 ammonium acetate Drugs 0.000 claims description 15

- 235000019257 ammonium acetate Nutrition 0.000 claims description 15

- 230000015572 biosynthetic process Effects 0.000 claims description 15

- 229910052709 silver Inorganic materials 0.000 claims description 15

- 229910000147 aluminium phosphate Inorganic materials 0.000 claims description 13

- QTBSBXVTEAMEQO-UHFFFAOYSA-M Acetate Chemical compound CC([O-])=O QTBSBXVTEAMEQO-UHFFFAOYSA-M 0.000 claims description 10

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 claims description 9

- 229910017604 nitric acid Inorganic materials 0.000 claims description 9

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 claims description 8

- 238000000151 deposition Methods 0.000 claims description 7

- 239000011701 zinc Substances 0.000 claims description 6

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 claims description 5

- 238000002347 injection Methods 0.000 claims 2

- 239000007924 injection Substances 0.000 claims 2

- 239000003795 chemical substances by application Substances 0.000 abstract description 4

- 239000010410 layer Substances 0.000 description 324

- 229920002120 photoresistant polymer Polymers 0.000 description 60

- 229910021417 amorphous silicon Inorganic materials 0.000 description 38

- 238000002161 passivation Methods 0.000 description 25

- 238000001259 photo etching Methods 0.000 description 17

- 235000019593 adhesiveness Nutrition 0.000 description 15

- 230000008569 process Effects 0.000 description 12

- 230000003647 oxidation Effects 0.000 description 10

- 238000007254 oxidation reaction Methods 0.000 description 10

- 229960004838 phosphoric acid Drugs 0.000 description 10

- 235000011007 phosphoric acid Nutrition 0.000 description 10

- 239000004005 microsphere Substances 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- 239000004973 liquid crystal related substance Substances 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000011368 organic material Substances 0.000 description 7

- 230000005540 biological transmission Effects 0.000 description 6

- 239000007789 gas Substances 0.000 description 6

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 206010034972 Photosensitivity reaction Diseases 0.000 description 4

- 230000001154 acute effect Effects 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 230000036211 photosensitivity Effects 0.000 description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- 229910004205 SiNX Inorganic materials 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000001914 filtration Methods 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 239000011147 inorganic material Substances 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 239000004094 surface-active agent Substances 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 108010022579 ATP dependent 26S protease Proteins 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000005984 hydrogenation reaction Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 230000000717 retained effect Effects 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- SYSZENVIJHPFNL-UHFFFAOYSA-N (alpha-D-mannosyl)7-beta-D-mannosyl-diacetylchitobiosyl-L-asparagine, isoform B (protein) Chemical compound COC1=CC=C(I)C=C1 SYSZENVIJHPFNL-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229940022663 acetate Drugs 0.000 description 1

- YBCVMFKXIKNREZ-UHFFFAOYSA-N acoh acetic acid Chemical compound CC(O)=O.CC(O)=O YBCVMFKXIKNREZ-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 239000002671 adjuvant Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 239000003945 anionic surfactant Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 239000003093 cationic surfactant Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000006056 electrooxidation reaction Methods 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 238000001566 impedance spectroscopy Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000012774 insulation material Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- LFLZOWIFJOBEPN-UHFFFAOYSA-N nitrate, nitrate Chemical compound O[N+]([O-])=O.O[N+]([O-])=O LFLZOWIFJOBEPN-UHFFFAOYSA-N 0.000 description 1

- 229940074355 nitric acid Drugs 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- 239000012044 organic layer Substances 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000012797 qualification Methods 0.000 description 1

- 238000010992 reflux Methods 0.000 description 1

- 238000004062 sedimentation Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 239000003381 stabilizer Substances 0.000 description 1

- 238000005728 strengthening Methods 0.000 description 1

- 229910021642 ultra pure water Inorganic materials 0.000 description 1

- 239000012498 ultrapure water Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23F—NON-MECHANICAL REMOVAL OF METALLIC MATERIAL FROM SURFACE; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL; MULTI-STEP PROCESSES FOR SURFACE TREATMENT OF METALLIC MATERIAL INVOLVING AT LEAST ONE PROCESS PROVIDED FOR IN CLASS C23 AND AT LEAST ONE PROCESS COVERED BY SUBCLASS C21D OR C22F OR CLASS C25

- C23F1/00—Etching metallic material by chemical means

- C23F1/10—Etching compositions

- C23F1/14—Aqueous compositions

- C23F1/16—Acidic compositions

- C23F1/30—Acidic compositions for etching other metallic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Weting (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- ing And Chemical Polishing (AREA)

Abstract

本发明提供一种蚀刻剂,一种使用该蚀刻剂制造布线的方法,以及使用该蚀刻剂制造薄膜晶体管(TFT)基板的方法。该蚀刻剂包括具有分子式1的材料、乙酸铵和余量的去离子水,其中,所述分子式1表示为:M(OH) XLY…(1),M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,以及R表示烷基。

Description

本申请要求2005年6月9日在韩国知识产权局提交的韩国专利申请第10-2005-0049453号的优先权,其全部内容结合于此作为参考。

技术领域

本发明涉及一种蚀刻剂,更具体而言,涉及一种用于Ag布线的蚀刻剂,一种使用该蚀刻剂制造Ag布线的方法,以及一种使用该蚀刻剂制造薄膜晶体管(TFT)基板的方法。

背景技术

液晶显示器(“LCD”)是使用最为广泛的平板显示器之一,其包括具有多个电极的两个面板和插入在两面板之间的液晶层。LCD向电极施加电压以重新排列液晶分子,从而调整入射光的透光量。

在各个面板上具有电极、并且使用薄膜晶体管(“TFT”)切换施加至电极的电压的LCD在各种LCD中应用最为广泛。TFT通常设置在两个面板的其中一个上。在LCD中,多个像素电极呈矩阵排列在一个面板上,共电极则布满另一面板的整个表面。通过向各个像素电极施加单独的电压在LCD上显示图像。为了施加单独的电压,多个三端子薄膜晶体管(TFT)连接至各个像素电极,并且面板上设置有多条传输用于控制TFT的信号的栅极线以及多条传输用于施加至像素电极的电压的数据线。

随着LCD显示区域的增大,连接至TFT的栅极线和数据线也随之更长,从而导致布线间的阻抗增大。为解决阻抗增大带来的信号延迟的问题,栅极线和数据线应该由尽可能低阻抗的材料制成。

在众多用于布线的材料中,Ag的阻抗最低。众所周知,Ag的阻抗为约1.59μΩcm。因此,在实用工艺中使用由Ag制成的栅极线和数据线可以减轻信号延迟的问题。

但是,由于Ag与诸如玻璃制成的下部基板或诸如本征非晶硅或掺杂非晶硅制成的半导体基板之间的粘附度较差,Ag不易被沉积并且有可能引起布线的翘起或脱落。此外,即使Ag导电层恰当地沉积在基板上,仍需要使用蚀刻剂对Ag导电层进行图样化。当使用传统蚀刻剂用于图样化时,Ag被过蚀刻或者无法被均匀蚀刻,从而引起布线的翘起或脱落以及布线侧面轮廓的剥蚀。

因此,在对沉积在基板上的Ag导电层进行图样化的过程中,就需要这样一种蚀刻剂,其能够在保持Ag导电层与基板的粘附度的同时改善布线的侧面轮廓。

发明内容

本发明提供一种用于Ag布线的蚀刻剂。

本发明还提供一种使用该蚀刻剂制造Ag布线的方法。

本发明还提供一种使用该蚀刻剂制造薄膜晶体管(TFT)的方法。

参照下面的描述,本发明以上所述的目标以及其他目标、特征和优点对于本领域的技术人员将变得显而易见。

根据本发明的一个方面,提供了这样一种蚀刻剂,其包含一种具有分子式1的材料、乙酸铵(ammonium acetic acid)、余量的去离子水(remainder of deionized water),其中,分子式1表示为:

M(OH)XLY ...(1)

其中,M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,R表示烷基。

根据本发明的另一方面,提供一种制造布线的方法,其包括:在基板上形成多个层(包括导电氧化层和由Ag或Ag合金制成的Ag导电层),使用一种蚀刻剂蚀刻该多个层,该蚀刻剂包括一种具有分子式1的材料、乙酸铵、余量的去离子水(remainder ofdeionizedwater),其中,分子式1表示为:

M(OH)XLY ...(1)

其中M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、、2或3,R表示烷基。

附图说明

通过参照附图并详细描述本发明的优选实施例,本发明的上述特征以及其他特征和优点将是显而易见的,附图中:

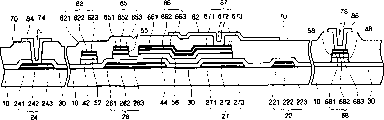

图1至图3是说明根据本发明实施例的金属布线制造方法的加工步骤的横截面图;

图4是说明根据本发明实施例的金属布线的轮廓的横截面图;

图5A是使用根据本发明实施例的TFT基板制造方法而制造的薄膜晶体管(TFT)基板的布局图;

图5B是沿图5A所示B-B’线截取的横截面图;

图6A、7A、8A和9A为布局图,依次说明了根据本发明实施例的TFT基板的制造方法;

图6B、7B、8B和9B是沿图6A、7A、8A和9A所示的线B-B’截取的横截面图;

图10A是使用根据本发明另一实施例的TFT基板制造方法制造的TFT基板的布局图;

图10B是沿图10A所示B-B’线截取的横截面图;

图11A、13A和19A为布局图,依次说明了根据本发明另一实施例的TFT基板的制造方法;

图11B和12是沿图11A所示B-B’线截取的说明加工步骤的横截面图;

图13B至18是沿图13A所示B-B’线截取的说明加工步骤的横截面图;以及

图19B是沿图19A所示B-B’线截取的横截面图。

具体实施方式

参照附图和以下优选实施例的具体描述,本发明的优点和特征及其实现方法将是更加容易理解。然而,本发明也可涵盖多种不同的形式,而并不局限于在此所述的实施例。提供这些实施例,以便公开内容是彻底和完整的,并且向本领域的技术人员充分地传达本发明的思想,本发明仅受所附权利要求限定。整个说明书中,相同的附图标号表示相同的元件。

下面将参照附图描述根据本发明实施例的金属布线的制造方法。图1至3是说明根据本发明实施例的金属布线制造方法的工艺步骤的横截面图。

参照图1,依次在基板1上沉积导电层2a(以下称下部导电氧化层)、导电层2b(以下称Ag导电层)和导电层2c(以下称上部导电氧化层),从而形成三层结构2,其中导电层2a由诸如氧化铟锡(ITO)或氧化铟锌(IZO)的导电氧化材料形成,导电层2b包括Ag或Ag合金,导电层2c由诸如氧化铟锡(ITO)或氧化铟锌(IZO)的导电材料形成。这里,基板1可以是例如玻璃制成的绝缘基板,或者是由本征非晶硅或掺杂的非晶硅形成的半导体基板。

下部导电氧化层2a、Ag导电层2b和上部导电氧化层2c通过诸如溅射的方法来形成。下面将描述使用ITO和Ag作为溅射靶来形成三层结构2的溅射方法。

首先,通过仅向ITO靶供电而不向Ag靶供电,在基板1上形成由ITO形成的下部导电氧化层2a。形成的下部导电氧化层2a的厚度为约30-300。当下部导电氧化层2a的厚度大于30时,可以通过有效防止基板1与Ag导电层2b彼此部分接触来保证基板1与Ag导电层2b之间具有足够的粘附度。下部导电氧化层2a的厚度优选小于300,以达到理想的接触阻抗。更优选地,所形成的下部导电氧化层2a的厚度为50-100。

溅射可以在例如约150℃或者更低的温度下进行,优选地在室温下进行。在这样的温度下,包括ITO的导电氧化物材料无法结晶,即,可表现为非晶形式。在这样的条件下沉积ITO会形成非晶ITO。这时,可以供给氢气(H2)或水蒸气(H2O)。此外,在溅射过程中,可以通过将ITO暴露于诸如氮气(N2)、氨气(NH3)或一氧化二氮(N2O)等含氮气体中来形成ITO氮化物(ITON)。ITO氮化物(ITON)通过防止Ag在其与ITO接触的区域发生氧化而抑制布线阻抗的剧增。

将提供至ITO靶的电关闭后,向Ag靶供电以形成Ag导电层2b。所形成的Ag导电层2b的厚度在约1000-3000,优选1500-2000。

这里,由非晶ITO形成的下部导电氧化层2a被插入在Ag导电层2b与基板1之间。非晶ITO是一种表面粗糙度较大的材料并且其表面上具有许多突起或凹陷的部分。由于具有突起和凹陷的部分,基板1与下部导电氧化层2a之间以及下部导电氧化层2a与Ag导电层2b之间的接触面积增大了,从而提高了粘附度。

将施加至Ag靶的电力关闭后,向ITO靶施加电力以形成上部导电氧化层2c。由于上部导电氧化层2c由非晶ITO形成,三层结构2上的待形成层诸如绝缘层与Ag导电层2b之间粘附度增强。上部导电氧化层2c同样防止Ag导电层2b中的Ag扩散至三层结构2的上部。所形成的上部导电层2c的厚度为约30-300,优选50-100,正如下部导电氧化层2a。

接下来,如图2所示,光刻胶层被涂布在三层结构2上并被曝光和显影,从而形成用于确定布线图样的光刻胶图样3。

如图3所示,使用光刻胶图样3作为蚀刻掩模蚀刻三层结构2,然后去除光刻胶图样3,以形成三层布线2。对于三层结构2的蚀刻可以是利用蚀刻剂的湿刻法。

此处,用于湿刻工艺的根据本发明实施例的蚀刻剂包含一种具有分子式1的材料、乙酸铵、余量的去离子水(remainder of deionizedwater),其中,分子式1的表达式为:

M(OH)XLY ...(1)

其中M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,R表示烷基。

分子式1所代表的材料起到稳定剂的作用,其提高蚀刻剂的稳定性并通过增强蚀刻的均匀性来改善被蚀刻材料的轮廓。相对于蚀刻剂总量,蚀刻剂中所包含的材料的量可以为例如0.1-5wt%。蚀刻剂中所含材料的量大于0.1wt%提供了理想的均匀度,众所周知,当蚀刻剂中材料的量达到5wt%时,可实现理想的蚀刻均匀度和蚀刻剂稳定性。蚀刻剂中材料的量优选在0.5-2wt%之间。

乙酸铵以微量和分子式1所代表的材料一起用于蚀刻剂中,以提高蚀刻均匀度并改善所得的蚀刻轮廓。相对于蚀刻剂的总量,乙酸铵的量可以例如在0.001-0.1wt%之间。当蚀刻剂中的乙酸铵在这样的范围内时,提供了所期望的蚀刻均匀度和蚀刻轮廓的改善,乙酸铵的量优选在0.002-0.005wt%之间。

但是,分子式1所代表的材料的量与乙酸铵的量并不受上述范围的限定,而可随蚀刻靶(etching target)、蚀刻温度、蚀刻时间、蚀刻方法和添加剂类型的不同而有所变化,所有这些都属于本发明的范围中。

根据本发明实施例的蚀刻剂可进一步地包括磷酸(phosphoricacid)、硝酸(nitric acid)和乙酸(acetic acid)。

这里,磷酸加速蚀刻速度。磷酸相对于蚀刻剂总量的量可在50-80wt%的范围内。当磷酸的量超过50wt%时,可以保证足够快的蚀刻速度。当磷酸的量超过80wt%时,可观察到由于粘度增加带来的蚀刻剂喷射困难。这种困难可通过将磷酸的量限制在80wt%以下来解决。磷酸的量在60-70wt%的范围内是优选的。

硝酸提高蚀刻速度。硝酸相对于蚀刻剂总量的量可在0.1-10wt%的范围内。当硝酸的量大于0.1wt%时,蚀刻速度可显著提高。当硝酸的量大于10wt%时,有可能破坏光刻胶层。蚀刻剂中磷酸小于10wt%可有效防止光刻胶层受到破坏。硝酸的量优选在0.5-5wt%的范围内。

乙酸提高相对于光刻胶层的可湿性。乙酸的量可在1-25wt%的范围内。当乙酸的量大于1wt%时,有可能有效避免由于蚀刻剂相对于光刻胶层的可湿性下降而导致的不完全蚀刻。当乙酸的量小于25wt%时,可通过抑制乙酸挥发来防止蚀刻剂由于其成分剧变引起的寿命缩短。乙酸的量优选在2-10wt%的范围内。

此外,为了改善蚀刻剂的特性,蚀刻剂可进一步包括诸如表面活性剂的添加剂。表面活性剂可以为阴离子表面活性剂、阳离子表面活性剂或者非离子型表面活性剂。蚀刻剂中所包含的表面活性剂的量可以在0.001-1wt%的范围内,优选地为0.005-0.1wt%。

除了该材料外,余量的蚀刻剂还可包括去离子水。

蚀刻剂可通过(但不限定于此)将分子式1所表示的材料、乙酸铵、磷酸、硝酸和乙酸混合于去离子水来制成,或者通过将前面制备的这些材料的溶液混合于超纯水(ultra-super water)中制成。另外,混合的顺序没有特定限制。

当蚀刻剂中存在微球体(microspheres)时,可能无法正确蚀刻细致的图样。因此,在使用蚀刻剂前,需要去除蚀刻剂中的微球体,以便直径0.5μm或者更大的微球体的数量可以小于1000/mL。通过纤细的过滤器过滤蚀刻剂可去除微球体。过滤的过程可以为一次过滤,优选进行循环过滤,可快速地去除微球体。

该蚀刻剂对于三层结构2具有很高的蚀刻选择性,并保持三层结构2与基板1之间的粘附度,并且使得三层布线2的侧面轮廓具有良好的锥形锐角。

接下来详细描述使用根据本发明实施例的蚀刻剂来蚀刻三层结构2的方法。

三层结构2的蚀刻过程可以在上部导电氧化层2c、Ag导电层2b和下部导电氧化层2a的每一层上分别完成。但是,由于包含在上部导电氧化层2c和下部导电氧化层2a中的ITO以及包含在Ag导电层2b中的Ag或者Ag合金具有相同的蚀刻速度,上部导电氧化层2c、Ag导电层2b和下部导电氧化层2a可以通过分次的方式进行蚀刻,从而形成三层布线2的良好侧面轮廓。

蚀刻可通过将蚀刻剂喷射在其中形成有光刻胶图样3的三层结构2的表面上来进行。这时,蚀刻的温度可保持在约30-50℃之间。蚀刻时间可一直持续至额外地经过了终点检测器(EPD)检测到的时间的一半(在该期间基板1被暴露于蚀刻剂)。例如,蚀刻时间可为约30-100秒。

下面将参照图4描述根据本发明实施例使用该蚀刻剂制造的金属布线的轮廓。图4是横截面图,示出了使用根据本发明实施例的蚀刻剂对形成于基板之上的包括ITO、Ag导电层以及的ITO的三层布线进行图样化后的金属布线的轮廓。

通常,三层结构2中包括的Ag导电层2b与基板1之间的粘附度很差。为了增强与基板1之间的粘附度,在本发明的本实施例中,由ITO形成的下部导电氧化层2a和上部导电氧化层2c分别形成在Ag导电层2b的下方和上方。但是,当采用传统布线图样化所用的现有技术的传统蚀刻剂形成三层布线2时,随着蚀刻的进行,三层结构2与基板1之间的粘附度也随之降低,从而导致三层布线2翘起或脱落。此外,三层布线2的侧面轮廓也不会均匀并且可能具有倒锥形倾角。

另一方面,在使用根据本发明实施例的蚀刻剂时,由于该蚀刻剂对于三层结构2具有很高的蚀刻选择性并且表现出优秀的蚀刻均匀度,就可以在不降低三层布线2与基板1之间的粘附度的情况下形成具有较好的锥形锐角的侧面轮廓,如图4所示。

虽然在本发明的本实施例中采用在基板上的包括下部导电氧化层、Ag导电层和上部导电氧化层的三层结构作为实例,也可以形成与Ag导电层上方或者下方的导电氧化层等同的多层导电层。

该蚀刻剂和使用该蚀刻剂制作Ag布线的方法也可以应用到制造薄膜晶体管(TFT)基板的方法中。

下面将参照附图描述根据本发明实施例的TFT基板的制造方法。

首先参照图5A和5B描述使用该方法制造的TFT基板的结构。图5A是使用根据本发明实施例制造TFT基板的方法制造的薄膜晶体管(TFT)基板的布局图,图5B是沿图5A所示B-B’线截取的横截面图。

用于传输栅极信号的多条栅极布线在绝缘基板10(图5B)上形成。栅极布线包括:栅极线22,如图5A所示水平延伸;栅极端部24,连接至栅极线22的端部,以接受来自外部的栅极信号并将该栅极信号传输至栅极线22;栅电极26,作为突起的TFT的一部分连接至栅极线22;以及维持电极(sustain electrode)27和维持电极线28,其平行于栅极线22。维持电极线28水平延伸穿过像素区域并连接至比维持电极线28宽的维持电极27。维持电极27重叠于与像素电极82相连的漏电极扩展部67(但由电介质30分离,图5A中未示出),以形成维持电容器,该维持电容器提高像素的电荷保存能力。维持电极27和维持电极线28的形状和排列可以有所变化,如果可以肯定通过像素电极82与栅极线22之间重叠而产生的保持能力(sustain capability)足够高,那么也可以不形成维持电极27和维持电极线28。

栅极布线由三层(结构层)22、24、26、27和28组成。三层结构栅极线22包括导电层221、222和223。三层结构层24包括导电层241、242和243。三层结构层26包括导电层261、262和263。三层结构层27包括导电层271、272和273。导电层221、241、261和271由导电氧化材料形成,例如氧化铟锡(ITO)或氧化铟锌(IZO)(以下称为“下部导电氧化层”)。导电层222、242、262和272由Ag或者Ag合金形成。导电层223、243、263和273由诸如ITO或IZO的导电氧化材料形成(以下称为“上部导电氧化层”)。虽然图5B中未示出,维持电极线28也具有与三层结构层22、24、26和27相同的三层结构。以下对于三层结构的栅极布线的描述中包括维持电极线28。

三层(结构层)22、24、26和27的结构和功能与上述根据本发明实施例制作Ag布线的方法中的三层结构层是相同的。

栅极绝缘层30形成在基板10和三层结构层22、24、26、27和28上,由氮化硅形成。

半导体层40形成在栅电极26上的栅极绝缘层30上,其由非晶硅氢化物或者多晶硅形成岛状。阻抗接触层(resistive contactlayer)55和56形成在半导体层40上,由硅化物或者重掺杂n型杂质的n+非晶硅氢化物形成。

数据布线形成在阻抗接触层55、56和栅极绝缘层30上。数据布线包括:数据线62,如图5A所示垂直形成并与栅极线22交叉以确定像素;源电极65,其是数据线62的分支并延伸至阻抗接触层55之上;数据端部68,连接至数据线62的端部并接受来自外界的图像信号;漏电极66,与源电极65分开并在阻抗接触层56上形成,从栅电极26或者TFT的一个沟槽部分来看,与源电极65相对;以及漏电极扩展部67,其具有从漏电极66延伸并与维持电极27重叠的大区域,但是它们之间被电介质30所分离。

数据布线由三层(结构层)62、65、66、67和68组成。三层结构的数据线62包括导电层621、622和623。三层结构的源电极65包括导电层651、652和653。三层结构的漏电极66包括导电层661、662和663。三层结构层67包括导电层671、672和673。三层结构层68包括导电层681、682和683。导电层621、651、661、671和681由诸如ITO的导电氧化材料形成(以下称“下部导电氧化层”)。导电层622、652、662、672和682由Ag或Ag合金形成(以下称“Ag导电层”)。导电层623、653、663、673和683由诸如ITO的导电氧化材料形成(以下称为“上部导电氧化层”)。这里,由于下部导电氧化层621、651、661、671和681以及上部导电氧化层623、653、663、673和683的结构和功能与栅极布线中的相同,所以对其未给以解释。

源电极65至少具有一部分与半导体层40重叠。漏电极66与源电极对置并如图5B所示位于栅电极26的一部分的上方,并且至少具有一部分与半导体层40重叠。这里,阻抗层55和56分别存在于半导体层40与源电极65之间以及半导体层40与漏电极66之间,以降低其间的接触阻抗。

漏电极扩展部67与维持电极27重叠,以便一方面在维持电极27与栅极绝缘层30之间形成保持能力(即由漏电极扩展部67、栅极绝缘层30和维持电极27形成的电容器保持电荷的能力),另一方面在与漏电极扩展部67之间形成保持能力。当不形成维持电极27时,也不形成漏电极扩展部67。

钝化层70形成在数据布线以及未被数据布线覆盖的半导体层部分40之上。钝化层70可由以下材料形成,例如具有优良平面特性和光敏性的有机材料、通过等离子体增强化学气相沉积法(PECVD)形成的诸如a-Si:C:O和a-Si:O:F的具有低介电常数的绝缘材料或者诸如氮化硅的无机材料。当钝化层70由有机材料形成时,可进一步地在钝化层70下方形成由氮化硅(SiNx)或氧化硅(SiOx)或二氧化硅(SiO2)形成的的绝缘层(未示出),以防止钝化层70的有机材料接触位于源电极65和漏电极66之间的半导体层40部分。

接触孔77和78形成在钝化层70中,露出漏电极扩展部67和数据线端部68。接触孔74形成在钝化层70和栅极绝缘层30中,露出栅极线端部24。位于像素中并通过接触孔77电连接至漏电极66的像素电极82形成在钝化层70上。施加以数据电压的像素电极82与上部显示面板(未示出)上的共电极一起产生电场,以确定像素电极与共电极之间的液晶层中的液晶(“LC”)微球体的排列。

通过接触孔74连接至栅极端部24的辅助栅极端部84以及通过接触孔78连接至数据端部68的辅助数据端部88形成在钝化层70之上。像素电极82、辅助栅极端部84以及辅助数据端部88由ITO形成。

下面将参照附图5A和5B以及图6A至9B具体描述根据本发明实施例的TFT基板的制造方法。

如图6A和6B所示,在绝缘基板10上依次沉积由诸如ITO或IZO等导电氧化材料形成的导电层、由Ag形成的导电层以及由诸如ITO或IZO等导电氧化材料形成的导电层,由此形成栅极三层结构层22、24、26、27和28(图6B未示出),其包括下部导电氧化层221、241、261和271、导电层222、242、262和272以及上部导电氧化层223、243、263和273。

栅极三层结构层22、24、26、27和28通过使用根据本发明实施例制造Ag布线的方法中的形成三级结构层的方法来形成。

接下来在栅极三层结构层上进行光刻。光刻处理使用蚀刻剂通过湿刻来进行。蚀刻剂与图1至4所述蚀刻剂相同,因此对其将不作解释。

在使用根据本发明实施例的蚀刻剂进行蚀刻时,由于蚀刻剂对于三层结构层具有很高的蚀刻选择性并且表现出优秀的蚀刻均匀度,就可以在不影响三层结构栅极布线22、24、26、27和28与基板10之间的粘附度的情况下获得具有较好锥形锐角的侧面轮廓。

因此,如图6A和6B所示,形成了包括栅极线22、栅电极26、栅极端部24、维持电极27和维持电极线28的栅极布线。

接下来,如图7A和7B所示,通过诸如化学气相沉积(CVD)依次沉积厚度为1500-5000的由氮化硅形成的栅极绝缘层30(在本文中有时也称电介质30)、厚度为500-2000的本征非晶硅层(将形成硅层40)以及厚度为300-600的掺杂的非晶硅层(将形成阻抗接触体55和56)。在本征非晶硅层40和掺杂的非晶硅层上进行光刻,以形成岛状半导体层40,并在覆盖栅电极24的栅极绝缘层30上形成阻抗接触层55和56。

这里,由于栅极绝缘层30、本征非晶硅层40与掺杂的非晶硅层是在约200℃或更高的温度下形成的,所以栅极布线中包含的非晶ITO转化为结晶ITO。结果,提高了导电氧化层221、241、261、271、223、243、263和273与Ag导电层222、242、262和272之间的粘附度。

接下来,如图8A和8B所示,在栅极绝缘层30、半导体层40的暴露部分以及阻抗接触层55、56上通过溅射依次沉积数据三层结构层62、65、66、67和68,其中下部导电氧化层621、651、661、671和681由ITO形成,Ag导电层622、652、662、672和682由Ag或Ag合金形成,上部导电氧化层623、653、663、673和683由ITO形成。这里,由于沉积下部导电氧化层621、651、661、671和681、Ag导电层622、652、662、672和682以及上部导电氧化层623、653、663、673和683的方法与上述形成栅极布线的处理中沉积下部导电氧化层221、241、261和271、Ag导电层222、242、262和272以及上部导电氧化层223、243、263和273的方法相同,所以不再给出重复的说明。

在数据三层结构层上进行光刻。光刻处理是使用蚀刻剂通过湿刻来进行的。该蚀刻剂与图1至4所述蚀刻剂相同,因此对其将不作进一步的说明。

在使用根据本发明实施例的蚀刻剂进行蚀刻时,由于蚀刻剂对于数据三层结构层具有很高的蚀刻选择性并且表现出较好的蚀刻均匀度,就可以在不影响三层结构数据布线62、65、66、67和68与栅极绝缘层30和阻抗接触层55、56之间的粘附度的情况下形成具有较好锥形锐角的侧面轮廓。

因此,形成了数据布线62、65、66、67和68,其包括与栅极线22交叉的数据线62、连接至数据线62并延伸至栅电极26上的源电极62、连接至数据线62端部的数据端部68、与源电极65分离并且从栅电极26看与源电极65对置的漏电极66、以及漏电极扩展部67,其具有从漏电极66延伸并重叠于(但通过电介质30分离于)维持电极27的较大区域。

通过蚀刻除去未被数据布线覆盖的掺杂非晶硅层的部分以便露出阻抗接触层55与56之间的半导体层部分40,数据布线62、65、66、67和68被分离,但是其中的65和66部分仍保留在如图5B所示的栅电极26两侧的上方。这时,最好进行氧等离子体工艺来稳定半导体层40的外露部分的表面。

接下来,如图9A和9B所示,所形成的钝化层70可以是单层结构或是包括具有优良平面特性和光敏性的有机材料的多层结构。例如,钝化层70可以由通过PECVD形成的Si:C:O,具有低介电常数的绝缘材料诸如Si:O:F,或者由诸如SiNx的无机材料形成。

接下来,栅极绝缘层30和钝化层70通过光刻被图样化,从而形成露出栅极端部24、漏电极扩展突出部(漏电极扩展部)67和数据端部68的接触孔74、77和78。这时,当钝化层70为具有光敏性的有机层时,接触孔74、77和78只能通过光刻形成。最好使用对栅极绝缘层30和钝化层70具有相同选择性的蚀刻剂和蚀刻工艺来形成接触孔74、77和78。

最后,如图5A和5B所示,沉积ITO层并进行光刻,以形成通过接触孔77连接至漏电极66的像素电极82,形成通过接触孔74连接至栅极端部24的辅助栅极端部84,并形成通过接触孔78连接至数据端部68的辅助数据端部88。

虽然在本发明的本实施例中,在基板上形成了包括下部导电氧化层、Ag导电层和上部导电氧化层的三层结构的栅极布线和数据布线,但是可以只有栅极布线或者数据布线通过三层结构来形成。此外,虽然栅极布线和数据布线是在基板上由包括下部导电氧化层、Ag导电层和上部导电氧化层的三层结构形成,导电氧化层也可以是形成在Ag导电层下方或上方的多层结构的导电层。

在上述描述中,通过使用不同的掩模进行光刻形成了半导体层和数据布线,但是也可如下所述,通过使用单一的光刻胶图样进行光刻来形成半导体层和数据布线。

下面将参照图10A至19B描述使用根据本发明另一实施例的TFT基板制造方法制造的TFT基板的单元像素的结构。

图10A示出了使用根据本发明另一实施例的TFT基板制造方法制造的TFT基板的布局图,图10B是沿图10A所示B-B线截取的横截面图。

在本发明的实施例中,首先在绝缘基板10上形成多条传输栅极信号的栅极布线。该栅极布线包括:栅极线22,如图10A所示水平延伸;栅极端部24,连接至栅极线22的端部,用于接收来自外部的栅极信号并将该栅极信号传输至栅极线22;栅电极26,作为突起的TFT的一部分连接至栅极线22;以及维持电极(sustainelectrode)27和平行于栅极线22的维持电极线28。在图10A中维持电极线28水平延伸穿过像素区域并连接至比维持电极线28宽的维持电极27。如图10B所示,维持电极27部分位于(但被电介质30、内部硅层44的一部分以及掺杂非晶硅层56的一部分所分离)与像素电极82相连的漏电极扩展部67的一部分下方,以形成维持电容器来提高像素的电荷保存能力。维持电极27和维持电极线28的形状和排列可以变化,当通过像素电极82与栅极线22之间的重叠而产生的保持能力足够高,则可以不形成维持电极27和维持电极线28。

如同图5A至9B所示的本发明实施例中那样,栅极布线由三层结构层22、24、26、27和28组成,其包括由ITO或IZO形成的下部导电氧化层221、241、261和271、由Ag或Ag合金形成的导电层222、242、262和272以及由ITO或IZO形成的上部导电氧化层223、243、263和273。

栅极绝缘层30形成在基板10和栅极布线22、24、26、27和28之上。

半导体图样42、44和48形成在栅极绝缘层30之上。阻抗接触层52、55、56和58形成在半导体图样42、44和48之上。

数据布线62、65、66、67和68形成在阻抗接触层52、55、56和58上。数据布线包括:数据线62,如图10A所示垂直并与栅极线22交叉以确定像素;源电极65,其作为数据线62的一个分支并延伸至阻抗接触层55a之上;数据端部68,连接至数据线62的端部并接受来自外界的图像信号,漏电极66,与源电极65相分离,形成在阻抗接触层56上并与源电极65相对,同时覆盖栅电极26的一部分,其决定了TFT的一个沟槽区域;以及漏电极扩展部67,其具有从漏电极66延伸并重叠于维持电极27的较大区域。

数据布线62、65、66、67和68由三层结构层组成,其包括由导电氧化材料形成的导电层621、651、661、671和681(以下称为“下部导电氧化层”)、由Ag和Ag合金形成的导电层622、652、662、672和682(以下称“Ag导电层”)、以及由导电氧化材料形成的导电层623、653、663、673和683(以下称为“上部导电氧化层”)。

源电极65具有至少一个与层44的一部分(通过包括半导体层40的图样化和蚀刻处理的初期光刻步骤形成)重叠的部分,并且漏电极66位于从栅极线26来看(以致覆盖一部分)与源电极65对置的位置,并且具有至少一个与半导体层44的一部分重叠的部分。这里,阻抗层55和56分别存在于半导体层44与源电极65之间以及半导体层44与漏电极66之间,以降低其间的接触阻抗。

漏电极扩展部67重叠于维持电极27以便在维持电极27与67之间形成保持能力,栅极绝缘层30起到位于电极27与67之间的电介质的作用。不形成维持电极27时,也就不形成漏电极扩展部67。

阻抗接触层52、55、56和58降低了半导体图样42、44和48与数据布线62、65、66、67和68之间的接触阻抗,并且具有与数据布线62、65、66、67和68相同的平面形状。

同时,除了TFT的沟槽部分外,半导体图样42、44和48具有与数据布线62、65、66、67和68以及阻抗接触层52、55、56和58相同的形状。也就是说,在TFT的沟槽部分中,源电极65和漏电极66彼此分离并且在源电极65下的阻抗接触层55与漏电极66下的阻抗接触层56也彼此分离。但是,用于TFT的半导体图样44在TFT的沟槽部分是连续的,由此形成了TFT的一个沟槽。

钝化层70形成在数据布线62、65、66、67和68以及未被数据线62、65、66、67和68覆盖的半导体图样44部分之上。钝化层70可由以下材料形成,例如具有优良平面特性和光敏性的有机材料、通过等离子体增强化学气相沉积法(PECVD)形成的诸如a-Si:C:O和a-Si:O:F的低介电绝缘材料或者诸如氮化硅的无机材料。当钝化层70由有机材料形成时,可进一步在钝化层70下方形成由氮化硅(SiNx)或氧化硅(SiOx)或二氧化硅(SiO2)形成的的绝缘层(未示出),以防止钝化层70的有机材料接触位于源电极65和漏电极66之间的半导体层40部分。

接触孔77和78形成在钝化层70中,分别露出漏电极扩展部67和数据线端部68。接触孔74形成在钝化层70中,以露出栅极绝缘层30的一部分。

像素电极82形成在钝化层70上,其通过接触孔77电连接至漏电极66并位于像素中。施加至像素电极82的数据电压与上部显示面板(未示出)的共电极产生电场,以确定像素电极与共电极之间的液晶层中的液晶(LC)微球体的排列。

此外,通过接触孔74连接至栅极端部24的辅助栅极端部84和通过接触孔78连接至数据端部68的辅助数据端部88形成在钝化层70之上。像素电极82、辅助栅极端部84以及辅助数据端部88由ITO形成。

下面将参照附图10A和10B以及图11A至19B描述根据本发明另一实施例的TFT基板的制造方法。

首先,如图11A和11B所示,通过依次沉积图5A至9B所示的本发明实施例中的由ITO或IZO形成的下部导电氧化层221、241、261和271、由Ag或Ag合金形成的导电层222、242、262和272以及由ITO或IZO形成的上部导电氧化层223、243、263和273来形成栅极三层结构层22、24、26、27和28。

接下来,在栅极三层结构层22、24、26、27和28上进行光刻。光刻处理通过使用蚀刻剂的湿刻进行。蚀刻剂与图1至4所述蚀刻剂相同,因此不再对其加以说明。

因此,如图11A和11B所示,形成了包括栅极线22、栅电极26、栅极端部24、维持电极27和维持电极线28的栅极布线。

接下来,如图12所示,通过化学气相沉积(CVD)分别连续沉积厚度例如为1500-5000的由氮化硅形成的栅极绝缘层30、厚度为500-2000的本征非晶硅层40以及厚度为300-600的掺杂非晶硅层50。通过溅射在掺杂的非晶硅层50上形成数据三层结构层60,该层中依次堆叠由ITO形成的下部导电氧化层601、由Ag或Ag合金形成的Ag导电层602以及由ITO形成的上部导电氧化层603。这里,数据三层结构层60的沉积方法与图5A至9B所示的本发明实施例的数据三层结构层相同。

光刻胶层110涂布在数据三层结构层60上。

参照图13A至图18,光线穿过掩模投射到光刻胶层110上并进行显影。这样形成如图13B所示的光刻胶图样112和114。这时,在光刻胶图样112和114中,待形成的TFT的沟槽部分,即位于光刻胶114(图13B)之下以及位于待形成的源电极65与待形成的漏电极66(图16、17、和18)之间的非晶硅层40的第一部分,被光刻胶114覆盖,光刻胶114的厚度比位于数据布线部分上方的光刻胶112(即待形成数据布线的区域上方的光刻胶112的第二部分)的厚度小。除光刻胶114的沟槽部分和光刻胶112的数据布线部分以外,光刻胶层110(图12)的剩余部分被去除。这时,残留在待形成的TFT晶体管的沟槽部分上方的光刻胶层114与残留在数据布线部分上的光刻胶层112之间的厚度比作为稍后将要描述的光刻过程的一个函数发生变化。第一光刻胶部分114的厚度优选地小于第二光刻胶部分112的厚度的一半(在一个实施例中大约为8000),也就是说,小于4000。这样,光刻胶层110的厚度可随位置的变化而以多种方式变化。一种方式是使用众所周知的光刻工艺改变在光刻胶层110的不同部分上的入射光量。为了调节透射的光量,可形成狭缝或者晶格图样或者使用半透明薄膜作为光刻胶层110图样化所用的掩模部分。

这时,掩模上狭缝之间图样的线条宽度或者掩模上图样之间的间隙,即狭缝的宽度,优选地小于曝光系统的分辨率。当使用半透明层作为掩模时,可使用透射比或厚度不同于半透明层的透射比或厚度的薄膜作为掩模的部分,以在制造掩模时控制掩模部分的透射比。

一旦光线通过掩模投射到光刻胶层110上,直接暴露于光线的光刻胶层110部分中的聚合物就被完全分解。但是,由于透过掩模的光线量小,位于形成有狭缝图样或半透明层的掩模部分之下的光刻胶110中的聚合物没有被完全分解,并且掩模遮光层下的光刻胶110中的聚合物也几乎未被分解。一旦光刻胶层110被显影,光刻胶层110中只有聚合物没有被分解的部分得以保留,有少量光线透射到其上的光刻胶110的部分的厚度比那些没有光线透射到其上的部分的厚度小。少量光线透射在光刻胶部分114上。这时,如果曝光时间过长,有可能光刻胶110的聚合物中所有的微球体都被分解,所以应该适当地调整曝光时间。聚合物材料可以为酚醛清漆树脂,并且曝光时间(表示为能量)可以为约36mmJ。

在一个实施例中,将由可回流材料制成的光刻胶层通过普通掩模(其分为可完全透光的部分和完全不透光的部分)加以曝光,对该光刻胶层显影并使光刻胶层回流,从而光刻胶层114的一部分流至无光刻胶层114的区域,这样就形成了厚度小于光刻胶部分112的光刻胶部分114。“回流工艺”可通过加热光刻胶层超过光刻胶转化温度并使光刻胶层向下流至沟槽区域来进行。现在使用上述蚀刻剂蚀刻具有上部导电氧化层603、Ag导电层602和下部导电氧化层601的数据三层结构层60和光刻胶图样114。由于本蚀刻过程与如图5A至9B所示的本发明实施例的形成数据布线的蚀刻过程以及形成栅极布线22、24、26、28和29的蚀刻过程大致相同,所以不再对其加以说明。

这样,如图14所示,只有待形成的沟槽部分的三层结构图样64以及数据线部分的62和68被保留。数据三层结构层60的其他部分被完全去除。结果,掺杂的非晶硅层50被暴露。图14和图15中除源电极65和漏电极66尚未分离(即限定)以外,残留的三层结构图样62、64和68与数据布线(图5B所示62、65、66、67和68)相同。

接下来,如图15所示,对暴露的掺杂的非晶硅层50和本征非晶硅层40进行干刻法,以去除除沟槽部分(图15中的层44)和数据布线部分(图15中的层42和48)以外的这些层的所有部分。同时,光刻胶层的第一部分114也通过该干刻法去除。干刻处理的结果如横截面图15所示。优选地,进行该蚀刻过程使得光刻胶图样112和114、掺杂的非晶硅层50以及本征非晶硅层40被同时蚀刻而栅极绝缘层30不被蚀刻。特别地,在对光刻胶图样112和114与本征非晶硅层40的蚀刻选择性彼此相似的情况下进行蚀刻是优选的。例如,使用SF6或HCl的混合气体或者SF6或O2的混合气体可以将两个层蚀刻至相似的厚度。当对光刻胶图样112和114与本征非晶硅层40的蚀刻选择性相同时,第一部分114的厚度等于或者小于本征非晶硅层40与掺杂的非晶硅层50的总厚度。在恰当的时间停止干刻,从而电介质层30和ITO层643实质上未被该干刻步骤蚀刻。在一个实施例中,包含诸如SF6和HCL的混合气体进入反应室,并且向反应室施加高频电场以引起辉光放电等离子体。通过使该等离子体与本征非晶硅层和掺杂的非晶硅层发生碰撞来进行干刻。这样,如图15所示,在去除沟槽区域的第一部分114后,源极/漏极三层结构图样64被暴露,在去除其他部分的掺杂的非晶硅层50和本征非晶硅层40后,栅极绝缘层30被暴露。由于覆盖数据布线部分的第二光刻胶部分112也被蚀刻,光刻胶部分112的厚度至少被减少了相当于光刻胶部分114的厚度。

留存在沟槽部分的源极/漏极三层结构图样64的表面上的光刻胶层110的残留部分通过灰化被去除。

接下来,如图16所示,图15中所示的包括沟槽部分的上部导电氧化层643、Ag导电层642以及下部导电氧化层641的三层结构图样64的一部分通过例如湿刻法去除,以露出掺杂的非晶硅层50的上表面。在本蚀刻步骤中使用了与参照图1至4所述的相同的蚀刻剂。因此不再描述该蚀刻步骤。

由掺杂的非晶硅50形成的阻抗接触层被蚀刻。这时,可采用干刻法。蚀刻气体可以是CF4和HCl的混合物或者是CF4和O2的混合物。当使用CF4和O2时,由本征非晶硅形成的半导体图样44的均匀厚度可以得到保留。这时,如图16所示,半导体层44的一部分被去除,因此可以减小层44被蚀刻部分的厚度。光刻胶图样的第二部分112也可被蚀刻,从而这部分光刻胶112的厚度将被减小。进行的蚀刻应该使得栅极绝缘层30不被蚀刻。本段中上述的特定蚀刻混合气体可以达到这样的效果。光刻胶图样112应该较厚,以便在蚀刻第二部分112后数据布线62、65、66、67和68不被露出,这也是优选的。

这样,源电极65和漏电极66被分离并确定下来,由此完整形成了数据布线65和66,其与阻抗接触层55和56组成这些电极。

接下来,如图17所示,留存在结构的数据布线部分上方的光刻胶层的第二部分112被去除。

接下来,如图18所示,钝化层70形成在结构的上表面的上方。该层典型地由氮化硅形成。如图19A和19B所示,在钝化层70和栅极绝缘层30上进行光刻,从而形成接触孔77、74和78,露出漏电极扩展部67、栅极端部24和数据端部68。

最后,如图10A和10B所示,沉积厚度在400-500之间的ITO层并且对其进行光刻,从而形成连接至漏电极扩展部67的像素电极82、连接至栅极端部24的辅助栅极端部84和连接至数据端部68的辅助数据端部88。

理想的是在沉积ITO之前使用氮气进行预加热处理,以防止通过接触孔74、77和78暴露在外的金属层24、67和68上形成金属氧化层。

在本发明的另一实施例中,可以得到根据本发明实施例的效果,并且只使用单一的掩模来形成数据布线62、65、66、67和68、阻抗接触层52、55、56和58、以及半导体图样42和48,其中漏电极66和源电极65被分离并确定下来,从而简化了制造过程。

虽然在本发明的本实施例中采用包括下部导电氧化层、Ag导电层和上部导电氧化层的三层结构作为实例,但是只有栅极布线或数据布线可具有三层结构。此外,虽然栅极布线和数据布线在基板上形成包括下部导电氧化层、Ag导电层和上部导电氧化层的三层结构,导电氧化层仍可以为形成在Ag导电层下方或上方的多层结构导电层。

根据本发明的TFT基板的制造方法可以很容易地运用到色彩滤镜矩阵(array on color filter,AOC,其中TFT矩阵形成在彩色滤光片上)中。

如上所述,通过使用根据本发明实施例的蚀刻剂蚀刻包括在Ag导电层上和/或在Ag导电层下的导电氧化层的多层结构,可以保持多层结构与基板之间的粘附度,并且可获得具有良好轮廓的导电布线。此外,通过使用根据本发明实施例的蚀刻剂蚀刻制造具有在Ag导电层上和/或在Ag导电层下的导电氧化层的多层结构的TFT基板,可以增强栅极布线和数据布线与TFT基板之间的粘附度,并且改善栅极布线和数据布线的轮廓,从而提高信号特征和图像质量。

本领域的技术人员将理解,在不违反本发明的精神和保护范围的前提下,前面所述的优选实施例可以有各种更改和变化。因此,本发明所公开的优选实施例仅用于一般地描述性用途,而并非用于限定本发明。

Claims (23)

1.一种蚀刻剂,其包括具有分子式1的材料、乙酸铵和余量的去离子水,其中,所述分子式1表示为:

M(OH)XLY ...(1)

其中M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,以及R表示烷基。

2.根据权利要求1所述的蚀刻剂,其中,所述材料的量在0.1-5wt%的范围内以及所述乙酸铵的量在0.001-0.1wt%的范围内。

3.根据权利要求1或2所述的蚀刻剂,进一步包括60-70wt%范围的磷酸、0.5-5wt%范围的硝酸和2-10wt%范围的乙酸。

4.一种制造布线的方法,所述方法包括:

在基板上形成多层结构,其包括导电氧化层和由Ag或Ag合金形成的Ag导电层;以及

使用蚀刻剂蚀刻所述多层结构,所述蚀刻剂包括具有分子式1的材料、乙酸铵和余量的去离子水,其中,所述分子式1表示为:

M(OH)XLY ...(1)

其中,M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,

X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,以及R表示烷基。

5.根据权利要求4所述的方法,其中,所述多层结构的形成包括在所述基板上依次沉积导电氧化层、由Ag或Ag合金形成的所述导电层、以及导电氧化层。

6.根据权利要求4所述的方法,其中,所述材料的量在0.1-5wt%的范围内以及所述乙酸铵的量在0.001-0.1wt%的范围内。

7.根据权利要求4或6所述的方法,进一步包括60-70wt%范围的磷酸、0.5-5wt%范围的硝酸和2-10wt%范围的乙酸。

8.根据权利要求4所述的方法,其中,所述基板由绝缘体或者半导体形成。

9.根据权利要求4所述的方法,其中,所述蚀刻在30-50℃的温度下进行。

10.根据权利要求4所述的方法,其中,所述蚀刻通过喷射进行。

11.根据权利要求4所述的方法,其中,所述蚀刻进行30-100秒。

12.根据权利要求4所述的方法,其中,所述蚀刻在形成所述多层结构的各个层上以分次的方式进行。

13.根据权利要求4所述的方法,其中,所述导电氧化层由氧化铟锡(ITO)或者氧化铟锌(IZO)形成。

14.一种用于制作薄膜晶体管(TFT)基板的方法,所述方法包括:

在基板上形成将要形成栅极的栅极多层结构,包括导电氧化层和由Ag或Ag合金形成的导电层;

通过使所述栅极多层结构图样化形成栅极布线;

在所述基板和栅极布线上形成栅极绝缘层和半导体层;

在所述半导体层上形成包括导电氧化层和由Ag或Ag合金形成的导电层的数据多层结构;以及

通过使所述数据多层结构图样化形成数据布线;

其中,所述栅极布线和/或所述数据布线的形成包括使用包含具有分子式1的材料、乙酸铵和余量的去离子水的蚀刻剂进行蚀刻,其中,所述分子式1表示为:

M(OH)XLY ...(1)

M表示Zn、Sn、Cr、Al、Ba、Fe、Ti、Si或B,X表示2或3,L表示H2O、NH3、CN、COR或NH2R,Y表示0、1、2或3,以及R表示烷基。

15.根据权利要求14所述的方法,其中,所述栅极多层结构的形成包括在所述基板上依次沉积导电氧化层、由Ag或Ag合金形成的导电层、以及导电氧化层。

16.根据权利要求14所述的方法,其中,所述数据多层结构的形成包括在所述基板上依次沉积导电氧化层、由Ag或Ag合金形成的导电层、以及导电氧化层。

17.根据权利要求14所述的方法,其中,所述材料的量在0.1-5wt%的范围内以及所述乙酸铵的量在0.001-0.1wt%的范围内。

18.根据权利要求14或17所述的方法,进一步包括60-70wt%范围的磷酸、0.5-5wt%范围的硝酸和2-10wt%范围的乙酸。

19.根据权利要求14所述的方法,其中,所述蚀刻在30-50℃的温度下进行。

20.根据权利要求14所述的方法,其中,所述蚀刻通过喷射进行。

21.根据权利要求14所述的方法,其中,所述蚀刻进行30-100秒。

22.根据权利要求14所述的方法,其中,所述蚀刻在形成所述多层结构的各个层上以分次的方式进行。

23.根据权利要求14所述的方法,其中,所述导电氧化层由氧化铟锡(ITO)或者氧化铟锌(IZO)形成。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050049453 | 2005-06-09 | ||

| KR1020050049453A KR101124569B1 (ko) | 2005-06-09 | 2005-06-09 | 식각액, 이를 이용하는 배선 형성 방법 및 박막 트랜지스터기판의 제조 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1877448A true CN1877448A (zh) | 2006-12-13 |

Family

ID=37509918

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2006100674071A Pending CN1877448A (zh) | 2005-06-09 | 2006-03-27 | 蚀刻剂及使用蚀刻剂制造布线及薄膜晶体管基板的方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7357878B2 (zh) |

| JP (1) | JP4988242B2 (zh) |

| KR (1) | KR101124569B1 (zh) |

| CN (1) | CN1877448A (zh) |

| TW (1) | TWI388062B (zh) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101542692B (zh) * | 2007-07-19 | 2011-04-13 | 林纯药工业株式会社 | 蚀刻液组合物 |

| CN104659035A (zh) * | 2013-11-25 | 2015-05-27 | 乐金显示有限公司 | 包括氧化物薄膜晶体管的阵列基板及其制造方法 |

| CN104893728A (zh) * | 2015-04-10 | 2015-09-09 | 深圳新宙邦科技股份有限公司 | 一种用于ITO/Ag/ITO薄膜的低张力的蚀刻液 |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7288444B2 (en) * | 2001-04-04 | 2007-10-30 | Samsung Sdi Co., Ltd. | Thin film transistor and method of manufacturing the same |

| KR20060097381A (ko) * | 2005-03-09 | 2006-09-14 | 삼성전자주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR100982395B1 (ko) * | 2007-04-25 | 2010-09-14 | 주식회사 엘지화학 | 박막 트랜지스터 및 이의 제조방법 |

| KR100987840B1 (ko) * | 2007-04-25 | 2010-10-13 | 주식회사 엘지화학 | 박막 트랜지스터 및 이의 제조방법 |

| JP2009194351A (ja) * | 2007-04-27 | 2009-08-27 | Canon Inc | 薄膜トランジスタおよびその製造方法 |

| KR20090095181A (ko) | 2008-03-05 | 2009-09-09 | 삼성전자주식회사 | 금속배선 형성용 식각액 조성물, 이 조성물을 이용한도전막의 패터닝 방법 및 평판 표시 장치의 제조방법 |

| KR101747391B1 (ko) * | 2009-07-07 | 2017-06-15 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 이의 제조 방법 |

| CN102655155B (zh) * | 2012-02-27 | 2015-03-11 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法和显示装置 |

| KR102290801B1 (ko) * | 2013-06-21 | 2021-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US20150069011A1 (en) * | 2013-09-11 | 2015-03-12 | Carestream Health, Inc. | Wet etching patterning compositions and methods |

| KR102091541B1 (ko) * | 2014-02-25 | 2020-03-20 | 동우 화인켐 주식회사 | 유기 발광 표시 장치의 제조 방법 |

| KR101972630B1 (ko) * | 2015-01-05 | 2019-04-26 | 동우 화인켐 주식회사 | 은 식각액 조성물 및 이를 이용한 표시 기판 |

| KR20160108944A (ko) * | 2015-03-09 | 2016-09-21 | 동우 화인켐 주식회사 | 은 함유 박막의 식각액 조성물 및 이를 이용한 표시 장치용 어레이 기판의 제조방법 |

| TWI631205B (zh) * | 2015-11-06 | 2018-08-01 | 東友精細化工有限公司 | 銀蝕刻液組合物和使用該組合物的顯示基板 |

| KR102433385B1 (ko) * | 2015-11-10 | 2022-08-17 | 동우 화인켐 주식회사 | 은 식각액 조성물 및 이를 이용한 표시 기판 |

| KR20190058758A (ko) | 2017-11-21 | 2019-05-30 | 삼성디스플레이 주식회사 | 식각액 조성물 및 이를 이용한 디스플레이 장치의 제조방법 |

| KR102554816B1 (ko) | 2018-04-23 | 2023-07-12 | 삼성디스플레이 주식회사 | 식각액 조성물 및 이를 이용한 금속 패턴의 제조 방법 |

| KR102661845B1 (ko) | 2018-10-11 | 2024-04-30 | 삼성디스플레이 주식회사 | 식각액 및 이를 이용한 표시 장치의 제조 방법 |

| KR102669119B1 (ko) | 2018-11-14 | 2024-05-24 | 삼성디스플레이 주식회사 | 식각 조성물, 이를 이용한 패턴 형성 방법 및 표시 장치의 제조 방법 |

| US11898081B2 (en) | 2019-11-21 | 2024-02-13 | Tokyo Ohka Kogyo Co., Ltd. | Ruthenium-etching solution, method for manufacturing ruthenium-etching solution, method for processing object to be processed, and method for manufacturing ruthenium-containing wiring |

| JP6895577B2 (ja) * | 2019-11-21 | 2021-06-30 | 東京応化工業株式会社 | エッチング液、エッチング液の製造方法、被処理体の処理方法、及びルテニウム含有配線の製造方法 |

| KR102676044B1 (ko) | 2020-04-29 | 2024-06-20 | 삼성디스플레이 주식회사 | 식각액 조성물 및 이를 이용한 표시 장치의 제조 방법 |

| KR102659176B1 (ko) | 2020-12-28 | 2024-04-23 | 삼성디스플레이 주식회사 | 은 함유 박막의 식각 조성물, 이를 이용한 패턴 형성 방법 및 표시장치의 제조 방법 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6132522A (en) * | 1996-07-19 | 2000-10-17 | Cfmt, Inc. | Wet processing methods for the manufacture of electronic components using sequential chemical processing |

| JP2000008184A (ja) * | 1998-06-24 | 2000-01-11 | Toppan Printing Co Ltd | 多層導電膜のエッチング方法 |

| US6387600B1 (en) * | 1999-08-25 | 2002-05-14 | Micron Technology, Inc. | Protective layer during lithography and etch |

| JP2002231706A (ja) | 2001-02-01 | 2002-08-16 | Matsushita Electric Ind Co Ltd | エッチング液及びこれを用いた薄膜トランジスタの製造方法 |

| KR100848109B1 (ko) | 2001-10-23 | 2008-07-24 | 삼성전자주식회사 | 배선용 식각액, 이를 이용한 배선의 제조 방법 및 이를포함하는 박막 트랜지스터 어레이 기판의 제조 방법 |

| WO2003005115A1 (en) * | 2001-07-06 | 2003-01-16 | Samsung Electronics Co., Ltd. | An etchant for a wire, a method for manufacturing the wire and a method for manufacturing a thin film transistor array panel including the method |

| US7179398B2 (en) * | 2001-10-23 | 2007-02-20 | Samsung Electronics Co., Ltd. | Etchant for wires, a method for manufacturing the wires using the etchant, a thin film transistor array substrate and a method for manufacturing the same including the method |

| KR100415617B1 (ko) * | 2001-12-06 | 2004-01-24 | 엘지.필립스 엘시디 주식회사 | 에천트와 이를 이용한 금속배선 제조방법 및박막트랜지스터의 제조방법 |

| US20030162398A1 (en) * | 2002-02-11 | 2003-08-28 | Small Robert J. | Catalytic composition for chemical-mechanical polishing, method of using same, and substrate treated with same |

| US20030168431A1 (en) * | 2002-02-25 | 2003-09-11 | Ritdisplay Corporation | Etchant composition for silver alloy |

| KR100853216B1 (ko) | 2002-06-25 | 2008-08-20 | 삼성전자주식회사 | 배선용 식각액, 이를 이용한 배선의 제조 방법, 그 배선을포함하는 박막 트랜지스터 어레이 기판 및 그의 제조 방법 |

| JP2004156070A (ja) * | 2002-11-01 | 2004-06-03 | Kanto Chem Co Inc | 透明導電膜を含む積層膜のエッチング液組成物 |

| JP2004356616A (ja) * | 2003-05-28 | 2004-12-16 | Samsung Electronics Co Ltd | 配線用エッチング液及びこれを利用した薄膜トランジスタ表示板の製造方法 |

| KR100960687B1 (ko) * | 2003-06-24 | 2010-06-01 | 엘지디스플레이 주식회사 | 구리(또는 구리합금층)를 포함하는 이중금속층을 일괄식각하기위한 식각액 |

| WO2005022592A2 (en) * | 2003-08-22 | 2005-03-10 | Fujifilm Electronic Materials U.S.A., Inc. | Novel aqueous based metal etchant |

-

2005

- 2005-06-09 KR KR1020050049453A patent/KR101124569B1/ko active IP Right Grant

-

2006

- 2006-02-09 US US11/351,015 patent/US7357878B2/en active Active

- 2006-03-16 TW TW095108951A patent/TWI388062B/zh active

- 2006-03-27 CN CNA2006100674071A patent/CN1877448A/zh active Pending

- 2006-04-25 JP JP2006121189A patent/JP4988242B2/ja active Active

-

2008

- 2008-02-21 US US12/035,316 patent/US7955521B2/en active Active

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101542692B (zh) * | 2007-07-19 | 2011-04-13 | 林纯药工业株式会社 | 蚀刻液组合物 |

| CN104659035A (zh) * | 2013-11-25 | 2015-05-27 | 乐金显示有限公司 | 包括氧化物薄膜晶体管的阵列基板及其制造方法 |

| CN104893728A (zh) * | 2015-04-10 | 2015-09-09 | 深圳新宙邦科技股份有限公司 | 一种用于ITO/Ag/ITO薄膜的低张力的蚀刻液 |

| CN104893728B (zh) * | 2015-04-10 | 2018-11-27 | 深圳新宙邦科技股份有限公司 | 一种用于ITO/Ag/ITO薄膜的低张力的蚀刻液 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006344939A (ja) | 2006-12-21 |

| KR101124569B1 (ko) | 2012-03-15 |

| KR20060128210A (ko) | 2006-12-14 |

| TW200701472A (en) | 2007-01-01 |

| TWI388062B (zh) | 2013-03-01 |

| JP4988242B2 (ja) | 2012-08-01 |

| US7955521B2 (en) | 2011-06-07 |

| US20060278606A1 (en) | 2006-12-14 |

| US7357878B2 (en) | 2008-04-15 |

| US20080142756A1 (en) | 2008-06-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1877448A (zh) | 蚀刻剂及使用蚀刻剂制造布线及薄膜晶体管基板的方法 | |

| US7586554B2 (en) | Liquid crystal display device and dielectric film usable in the liquid crystal display device | |

| CN1773341A (zh) | 制造柔性显示装置的方法 | |

| KR100433463B1 (ko) | 패턴형성방법 및 이 방법을 사용한 디스플레이제조방법 | |

| CN100346218C (zh) | 薄膜晶体管阵列面板及其制造方法 | |

| CN1752852A (zh) | 用于剥离光刻胶的组合物及薄膜晶体管阵列面板制造方法 | |

| CN101079429A (zh) | 薄膜晶体管阵列基板及其制造方法 | |

| CN1897269A (zh) | 布线结构、布线形成方法、薄膜晶体管基板及其制造方法 | |

| CN1655326A (zh) | 掺杂方法,制造半导体器件和施加电子仪器的方法 | |

| CN1917202A (zh) | 布线结构、布线制造方法、薄膜晶体管基板及其制造方法 | |

| CN1875488A (zh) | 液晶显示设备及其制造方法,以及液晶电视接收机 | |

| CN1884618A (zh) | 蚀刻剂及用其制造互连线和薄膜晶体管基板的方法 | |

| CN1801479A (zh) | 制造包括塑料基板的柔性薄膜晶体管阵列板的方法 | |

| CN1786801A (zh) | 薄膜晶体管阵列面板及其制造方法 | |

| CN1897270A (zh) | 布线结构、制造布线的方法、薄膜晶体管基板及其制造方法 | |

| CN1683980A (zh) | 显示装置 | |

| CN1945855A (zh) | 薄膜晶体管、tft阵列基板、液晶显示器及其制造方法 | |

| CN1790750A (zh) | 薄膜晶体管、其制造方法、显示设备及其制造方法 | |

| CN1819217A (zh) | 有源矩阵衬底及其制造方法 | |

| KR101278477B1 (ko) | 박막 트랜지스터 기판의 제조 방법 | |

| CN1913146A (zh) | 薄膜导体及其制造方法 | |

| CN1614483A (zh) | 液晶显示器件制造方法 | |

| CN1655056A (zh) | 光学掩模及利用该掩模的薄膜晶体管阵列面板的制造方法 | |

| CN1714431A (zh) | 用于液晶显示装置的薄膜晶体管基板及其制造方法 | |

| CN1606125A (zh) | 薄膜晶体管阵列基板的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C12 | Rejection of a patent application after its publication | ||

| RJ01 | Rejection of invention patent application after publication |

Open date: 20061213 |