JP6759578B2 - 異方導電性フィルム及び接続構造体 - Google Patents

異方導電性フィルム及び接続構造体 Download PDFInfo

- Publication number

- JP6759578B2 JP6759578B2 JP2015249132A JP2015249132A JP6759578B2 JP 6759578 B2 JP6759578 B2 JP 6759578B2 JP 2015249132 A JP2015249132 A JP 2015249132A JP 2015249132 A JP2015249132 A JP 2015249132A JP 6759578 B2 JP6759578 B2 JP 6759578B2

- Authority

- JP

- Japan

- Prior art keywords

- conductive film

- conductive

- anisotropic conductive

- particle arrangement

- arrangement region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000002245 particle Substances 0.000 claims description 427

- 239000012790 adhesive layer Substances 0.000 claims description 33

- 238000004519 manufacturing process Methods 0.000 claims description 13

- 238000000034 method Methods 0.000 claims description 9

- 229920005989 resin Polymers 0.000 description 33

- 239000011347 resin Substances 0.000 description 33

- 239000000758 substrate Substances 0.000 description 33

- 238000010586 diagram Methods 0.000 description 22

- 239000011521 glass Substances 0.000 description 21

- 230000000052 comparative effect Effects 0.000 description 17

- 238000011156 evaluation Methods 0.000 description 13

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 239000010410 layer Substances 0.000 description 10

- 230000015572 biosynthetic process Effects 0.000 description 6

- 239000000377 silicon dioxide Substances 0.000 description 5

- 229910002012 Aerosil® Inorganic materials 0.000 description 4

- 238000001723 curing Methods 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 229920002799 BoPET Polymers 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 239000010419 fine particle Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 239000003505 polymerization initiator Substances 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229910000831 Steel Inorganic materials 0.000 description 2

- -1 acrylate compound Chemical class 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 238000010539 anionic addition polymerization reaction Methods 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 238000005452 bending Methods 0.000 description 2

- 125000002091 cationic group Chemical group 0.000 description 2

- 238000010538 cationic polymerization reaction Methods 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000007373 indentation Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 239000008188 pellet Substances 0.000 description 2

- 229920006287 phenoxy resin Polymers 0.000 description 2

- 239000013034 phenoxy resin Substances 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000001568 sexual effect Effects 0.000 description 2

- 239000010959 steel Substances 0.000 description 2

- 229920005992 thermoplastic resin Polymers 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 244000126211 Hericium coralloides Species 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- WNROFYMDJYEPJX-UHFFFAOYSA-K aluminium hydroxide Chemical compound [OH-].[OH-].[OH-].[Al+3] WNROFYMDJYEPJX-UHFFFAOYSA-K 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000002452 interceptive effect Effects 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 239000002923 metal particle Substances 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 239000007870 radical polymerization initiator Substances 0.000 description 1

- 238000010526 radical polymerization reaction Methods 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R11/00—Individual connecting elements providing two or more spaced connecting locations for conductive members which are, or may be, thereby interconnected, e.g. end pieces for wires or cables supported by the wire or cable and having means for facilitating electrical connection to some other wire, terminal, or conductive member, blocks of binding posts

- H01R11/01—Individual connecting elements providing two or more spaced connecting locations for conductive members which are, or may be, thereby interconnected, e.g. end pieces for wires or cables supported by the wire or cable and having means for facilitating electrical connection to some other wire, terminal, or conductive member, blocks of binding posts characterised by the form or arrangement of the conductive interconnection between the connecting locations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01B—CABLES; CONDUCTORS; INSULATORS; SELECTION OF MATERIALS FOR THEIR CONDUCTIVE, INSULATING OR DIELECTRIC PROPERTIES

- H01B1/00—Conductors or conductive bodies characterised by the conductive materials; Selection of materials as conductors

- H01B1/20—Conductive material dispersed in non-conductive organic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01B—CABLES; CONDUCTORS; INSULATORS; SELECTION OF MATERIALS FOR THEIR CONDUCTIVE, INSULATING OR DIELECTRIC PROPERTIES

- H01B5/00—Non-insulated conductors or conductive bodies characterised by their form

- H01B5/14—Non-insulated conductors or conductive bodies characterised by their form comprising conductive layers or films on insulating-supports

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R13/00—Details of coupling devices of the kinds covered by groups H01R12/70 or H01R24/00 - H01R33/00

- H01R13/02—Contact members

- H01R13/22—Contacts for co-operating by abutting

- H01R13/24—Contacts for co-operating by abutting resilient; resiliently-mounted

- H01R13/2407—Contacts for co-operating by abutting resilient; resiliently-mounted characterized by the resilient means

- H01R13/2414—Contacts for co-operating by abutting resilient; resiliently-mounted characterized by the resilient means conductive elastomers

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/321—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by conductive adhesives

- H05K3/323—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by conductive adhesives by applying an anisotropic conductive adhesive layer over an array of pads

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Dispersion Chemistry (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Wire Bonding (AREA)

- Non-Insulated Conductors (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Manufacturing Of Electrical Connectors (AREA)

Description

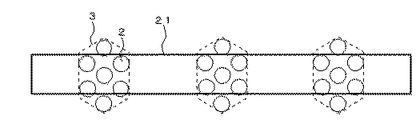

複数の導電粒子が配置されている第1の導電粒子配置領域、及び第1の導電粒子配置領域に対して導電粒子の配列態様、配列位置又は密度が異なる第2の導電粒子配置領域を有し、第1の導電粒子配置領域及び第2の導電粒子配列領域が異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルムを提供する。

異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された導電粒子配置領域(以下、接続用導電粒子配置領域ともいう)を有し、該導電粒子配置領域が、異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルムを提供する。

500〜5000Pa・sがより好ましく、特に好ましくは1000〜3000Pa・sである。この範囲であれば、絶縁接着剤層10に導電粒子を精密に配置することができ、且つ異方導電性接続時の押し込みにより樹脂流動が導電粒子の捕捉性に支障を来たすことを防止できる。最低溶融粘度の測定は、レオメータ(TA社製ARES)を用いて、昇温速度5℃/min、測定温度範囲50〜200℃、振動周波数1Hzの条件で求めることができる。

実施例1〜4、比較例1

(1)FOG接続用の異方導電性フィルムの製造

フェノキシ樹脂(熱可塑性樹脂)(新日鐵住金(株)、YP−50)60部、エポキシ樹脂(熱硬化性樹脂)(三菱化学(株)、jER828)40部、カチオン系硬化剤(三新化学工業(株)、SI−60L)2部を含む絶縁性樹脂の混合溶液を調製し、それを、フィルム厚さ50μmのPETフィルム上に塗布し、80℃のオーブンにて5分間乾燥させ、PETフィルム上に厚み20μmの粘着層を形成した。

ガラス基板はITOベタガラスを使用した。

実施例1〜4及び比較例1の異方導電性フィルムの(a)初期導通抵抗、(b)導通信頼性、(c)ショート発生率を、それぞれ次のように評価した。結果を表1に示す。

実施例1〜4及び比較例1の異方導電性フィルムを、上述のフレキシブルプリント基板とガラス基板との間に挟み、加熱加圧(180℃、5MPa、5秒)して各評価用接続物を得、その評価用接続物の導通抵抗を測定した。

(a)初期導通抵抗の評価用接続物を温度85℃、湿度85%RHの恒温槽に500時間おき、その導通抵抗を、(a)と同様に測定した。なお、この導通抵抗が5Ω以上であると、接続した電子部品の実用的な導通安定性の点から好ましくない。

ショート発生率の評価用ICとして次のIC(7.5μmスペースの櫛歯TEG(test element group))を用意した。

厚み 0.5mm

バンプ仕様 金メッキ、高さ15μm、サイズ25×140μm、バンプ間距離7.5μm

(1)COG接続用の異方導電性フィルムの製造

実施例1と同様にして、フェノキシ樹脂(熱可塑性樹脂)(新日鐵住金(株)、YP−50)60部、エポキシ樹脂(熱硬化性樹脂)(三菱化学(株)、jER828)40部、カチオン系硬化剤(三新化学工業(株)、SI−60L)2部を用いてPETフィルム上に厚み20μmの粘着層を形成した。

外形 0.7×20mm

厚み 0.2mm

バンプ仕様 金メッキ、高さ12μm、サイズ15×100μm、バンプ間スペース13μm、バンプ個数 1300個(ICチップの長手の対向する辺にそれぞれ650個)

ガラス材質 コーニング社製

外径 30×50mm

厚み 0.5mm

電極 ITO配線

実施例5〜9及び比較例2の異方導電性フィルムの(a)初期導通抵抗、(b)導通信頼性、(c)ショート発生率を、それぞれ次のように評価した。結果を表2に示す。

実施例5〜9及び比較例2の異方導電性フィルムを、上述のICチップとそれに対応するガラス基板との間に挟み、加熱加圧(180℃、80MPa、5秒)して各評価用接続物を得、その評価用接続物の導通抵抗を測定した。

実施例1と同様にしてショート導通信頼性を測定した。この導通抵抗が5Ω以上であると、接続した電子部品の実用的な導通安定性の点から好ましくない。

実施例1と同様にしてショート発生率を評価した。ショート発生率が50ppm以上であると実用上の接続構造体を製造する点から好ましくない。

実施例5〜9において、絶縁性樹脂100部にシリカフィラー(シリカ微粒子、アエロジルRY200、日本アエロジル(株))20部を追加し、実施例5〜9と同様に異方導電性フィルムを製造し、導通評価を行った。その結果、いずれも良好であった。

実施例5〜9において、アライメントマークの形成を省略する以外は、実施例5〜9と同様に異方導電性フィルムを製造し、導通評価を行った。その結果、実施例5〜9に比してアライメントに時間を要したが、導通評価は良好であった。

実施例5〜9において、初期導通抵抗の評価時に、異方導電性フィルムの導電粒子配置領域とICチップのバンプ形成領域とが僅かにずれて重ね合わさったものを加熱加圧することにより評価用接続物を得た。この評価用接続物の導通抵抗の評価から次のことを確認できた。即ち、実施例20(実施例5の導電粒子配置)において、導電粒子群が矩形のバンプの幅方向に粒子径1個分ずれても接続できることがわかった。

実施例15において、1つのバンプに対応する導電粒子の配置を図8A〜図8D及び図10に示した粒子配列群3の配列とし、実施例15と同様に導通評価を行った。この場合、バンプの大きさは実施例15と同様に15μm×100μm、バンプ間スペースは13μmであり、バンプ1個あたりの導電粒子の捕捉数は、図8Aの態様では12個、図8Bの態様では16個、図8Cの態様では12個、図8Dの態様では15個、図10の態様で16個である。これらのいずれにおいても良好な接続状態を得られた。

2 導電粒子

3、3a、3b、3c、3e、3m、3p、3q 粒子配列群

4a、4b、4c、4e 接続用導電粒子配置領域

4d 位置合わせ用導電粒子配置領域

5 導電粒子が配置されていない中央部領域

6 導電粒子が配置されていないバッファー領域

7、7a、7b スリット線

10 絶縁接着剤層

20 ICチップ

21 出力側バンプ

21a 出力側バンプの配列領域

22 入力側バンプ

22a 入力側バンプの配列領域

23 サイドバンプ

23a サイドバンプの配列領域

24 アライメントマーク

30 基板の電極端子

31 基板のアライメントマーク

F1 異方導電性フィルムの長手方向

F2 異方導電性フィルムの短手方向

Claims (21)

- 絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであって、

異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域を有し、該接続用導電粒子配置領域が、異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。 - 隣り合う接続用導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項1記載の異方導電性フィルム。

- 異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域を有する請求項1又は2記載の異方導電性フィルム。

- 位置合わせ用導電粒子配置領域が接続用導電粒子配置領域と別個に形成されている請求項3記載の異方導電性フィルム。

- 位置合わせ用導電粒子配置領域が、接続用導電粒子配置領域と重複して形成されている請求項3記載の異方導電性フィルム。

- 接続用導電粒子配置領域に、複数の導電粒子で形成された粒子配列群が配列している請求項1〜5のいずれかに記載の異方導電性フィルム。

- 接続用導電粒子配置領域において、異方導電性フィルムで接続する電子部品の一つのバンプあたり3個以上の導電粒子が配置されている請求項1〜6のいずれかに記載の異方導電性フィルム。

- 複数の接続用導電粒子配置領域がそれぞれ異方導電性フィルムの長手方向に周期的に形成されている請求項1〜7のいずれかに記載の異方導電性フィルム。

- 異方導電性フィルムの長手方向に沿って接続用導電粒子配置領域が並列して形成されている請求項1〜8のいずれかに記載の異方導電性フィルム。

- 絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであって、

複数の導電粒子が配置されている第1の導電粒子配置領域、及び第1の導電粒子配置領域に対して導電粒子の配列態様、配列位置又は密度が異なる第2の導電粒子配置領域を有し、第1の導電粒子配置領域及び第2の導電粒子配置領域が単一の絶縁接着剤層に配置され且つ異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。 - 異方導電性フィルムの長手方向に隣り合う第2の導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項10記載の異方導電性フィルム。

- 第1の導電粒子配置領域が、異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域である請求項10又は11記載の異方導電性フィルム。

- 第2の導電粒子配置領域が、異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域である請求項10〜12のいずれかに記載の異方導電性フィルム。

- 位置合わせ用導電粒子配置領域が、位置合わせ用導電粒子から形成されている請求項12記載の異方導電性フィルム。

- 絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであって、

複数の導電粒子が配置されている第1の導電粒子配置領域、及び第1の導電粒子配置領域に対して導電粒子の配列態様、配列位置又は密度が異なる第2の導電粒子配置領域を有し、各導電粒子配置領域が導電粒子の集合からなり且つ導電粒子が各導電粒子配置領域の輪郭を形成しており、第1の導電粒子配置領域及び第2の導電粒子配置領域が異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。 - 異方導電性フィルムの長手方向に隣り合う第2の導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項15記載の異方導電性フィルム。

- 第1の導電粒子配置領域が、異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域である請求項15又は16記載の異方導電性フィルム。

- 第2の導電粒子配置領域が、異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域である請求項15〜17のいずれかに記載の異方導電性フィルム。

- 位置合わせ用導電粒子配置領域が、位置合わせ用導電粒子から形成されている請求項17記載の異方導電性フィルム。

- 請求項1〜19のいずれかに記載の異方導電性フィルムで第1電子部品と第2電子部品が異方導電性接続されている接続構造体。

- 請求項1〜19のいずれかに記載の異方導電性フィルムで第1電子部品と第2電子部品とを異方導電性接続する接続構造体の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014259509 | 2014-12-22 | ||

| JP2014259509 | 2014-12-22 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020112766A Division JP7176550B2 (ja) | 2014-12-22 | 2020-06-30 | 異方導電性フィルム及び接続構造体 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016119306A JP2016119306A (ja) | 2016-06-30 |

| JP6759578B2 true JP6759578B2 (ja) | 2020-09-23 |

Family

ID=56150481

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015249132A Active JP6759578B2 (ja) | 2014-12-22 | 2015-12-21 | 異方導電性フィルム及び接続構造体 |

| JP2020112766A Active JP7176550B2 (ja) | 2014-12-22 | 2020-06-30 | 異方導電性フィルム及び接続構造体 |

| JP2022180551A Active JP7541249B2 (ja) | 2014-12-22 | 2022-11-10 | 異方導電性フィルム及び接続構造体 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020112766A Active JP7176550B2 (ja) | 2014-12-22 | 2020-06-30 | 異方導電性フィルム及び接続構造体 |

| JP2022180551A Active JP7541249B2 (ja) | 2014-12-22 | 2022-11-10 | 異方導電性フィルム及び接続構造体 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9991614B2 (ja) |

| JP (3) | JP6759578B2 (ja) |

| KR (1) | KR101929697B1 (ja) |

| CN (1) | CN107004974B (ja) |

| TW (1) | TWI686014B (ja) |

| WO (1) | WO2016104463A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102535557B1 (ko) | 2016-03-07 | 2023-05-24 | 삼성디스플레이 주식회사 | 표시 장치 및 전자 디바이스 |

| WO2018101106A1 (ja) * | 2016-12-01 | 2018-06-07 | デクセリアルズ株式会社 | 異方性導電フィルム |

| JP7274815B2 (ja) * | 2016-12-01 | 2023-05-17 | デクセリアルズ株式会社 | 異方性導電フィルム |

| TWI763750B (zh) * | 2016-12-01 | 2022-05-11 | 日商迪睿合股份有限公司 | 異向性導電膜 |

| CN107452438B (zh) * | 2017-07-27 | 2019-10-11 | 京东方科技集团股份有限公司 | 一种各向异性导电胶带及胶带卷、绑定结构及显示装置 |

| TWI845515B (zh) * | 2018-06-06 | 2024-06-21 | 日商迪睿合股份有限公司 | 連接體、連接體之製造方法、連接方法 |

| JP7321792B2 (ja) * | 2019-06-26 | 2023-08-07 | 株式会社ジャパンディスプレイ | 異方性導電膜及び表示装置 |

| KR20210018700A (ko) | 2019-08-09 | 2021-02-18 | 삼성디스플레이 주식회사 | 접착 부재 및 이를 포함한 표시장치 |

| CN111303795A (zh) * | 2020-02-14 | 2020-06-19 | 维沃移动通信有限公司 | 一种异方性导电胶膜及其制备方法和显示装置 |

| KR20210122359A (ko) | 2020-03-30 | 2021-10-12 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치 제조 방법 |

| KR20210138332A (ko) * | 2020-05-12 | 2021-11-19 | 안성룡 | 전도체 본딩 방법 |

| WO2022202987A1 (ja) * | 2021-03-26 | 2022-09-29 | デクセリアルズ株式会社 | フィラー配列フィルム |

| WO2022202988A1 (ja) * | 2021-03-26 | 2022-09-29 | デクセリアルズ株式会社 | フィラー配列フィルム |

| JP2024146277A (ja) * | 2023-03-31 | 2024-10-15 | デクセリアルズ株式会社 | フィラー配列フィルム及びその製造方法並びに接続構造体及びその製造方法 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0660979B2 (ja) * | 1985-08-30 | 1994-08-10 | 松下電器産業株式会社 | 電気的接続方法 |

| JPH09320345A (ja) | 1996-05-31 | 1997-12-12 | Whitaker Corp:The | 異方導電性フィルム |

| JPH10209210A (ja) * | 1997-01-20 | 1998-08-07 | Sharp Corp | 半導体装置及びその製造方法並びにその検査方法 |

| JP3506003B2 (ja) * | 1998-05-19 | 2004-03-15 | ソニーケミカル株式会社 | 異方性導電接着材 |

| JP2002094222A (ja) | 2000-09-19 | 2002-03-29 | Matsushita Electric Ind Co Ltd | 電子部品接合用シート、電子部品実装方法、及び電子部品実装装置 |

| JP2004071857A (ja) | 2002-08-07 | 2004-03-04 | Sharp Corp | 基板接続部の構造、並びに該構造を有する電子部品及び液晶表示装置 |

| JP3994335B2 (ja) | 2002-10-04 | 2007-10-17 | 日立化成工業株式会社 | 接続部材の製造方法 |

| JP4887700B2 (ja) | 2005-09-09 | 2012-02-29 | 住友ベークライト株式会社 | 異方導電性フィルムおよび電子・電機機器 |

| JP2007115560A (ja) | 2005-10-21 | 2007-05-10 | Sumitomo Bakelite Co Ltd | 異方導電フィルム及びその製造方法 |

| KR100803433B1 (ko) * | 2006-01-23 | 2008-02-13 | 엘에스전선 주식회사 | 접속 신뢰성이 개선된 이방성 도전 필름 및 이를 이용한회로 접속 구조체 |

| EP2058903A1 (en) | 2006-08-29 | 2009-05-13 | Hitachi Chemical Company, Ltd. | Anisotropic conductive tape and method of manufacturing it, connected structure and method of connecting circuit member by use of the tape |

| CN101512840A (zh) * | 2006-08-29 | 2009-08-19 | 日立化成工业株式会社 | 各向异性导电带及其制造方法以及使用其的连接结构体和电路部件的连接方法 |

| WO2008146793A1 (ja) * | 2007-05-24 | 2008-12-04 | Sony Chemical & Information Device Corporation | 電気装置、接続方法及び接着フィルム |

| CN101556838B (zh) * | 2008-04-09 | 2011-06-01 | 北京京东方光电科技有限公司 | 各向异性导电膜 |

| JP5543267B2 (ja) | 2010-05-07 | 2014-07-09 | デクセリアルズ株式会社 | 異方性導電フィルム及びその製造方法、並びに実装体及びその製造方法 |

| JP5690648B2 (ja) * | 2011-04-28 | 2015-03-25 | デクセリアルズ株式会社 | 異方性導電フィルム、接続方法及び接続構造体 |

| JP5293843B2 (ja) * | 2012-01-24 | 2013-09-18 | デクセリアルズ株式会社 | 透明導電性素子、入力装置、電子機器および透明導電性素子作製用原盤 |

| WO2014021424A1 (ja) * | 2012-08-01 | 2014-02-06 | デクセリアルズ株式会社 | 異方性導電フィルムの製造方法、異方性導電フィルム、及び接続構造体 |

| TWI675382B (zh) | 2012-08-01 | 2019-10-21 | 日商迪睿合股份有限公司 | 異向性導電膜之製造方法、異向性導電膜、及連接結構體 |

| JP6476747B2 (ja) * | 2014-10-28 | 2019-03-06 | デクセリアルズ株式会社 | 異方性導電フィルム及び接続構造体 |

-

2015

- 2015-12-21 JP JP2015249132A patent/JP6759578B2/ja active Active

- 2015-12-22 TW TW104143326A patent/TWI686014B/zh active

- 2015-12-22 US US15/538,525 patent/US9991614B2/en active Active

- 2015-12-22 KR KR1020177015109A patent/KR101929697B1/ko active IP Right Grant

- 2015-12-22 WO PCT/JP2015/085744 patent/WO2016104463A1/ja active Application Filing

- 2015-12-22 CN CN201580066924.4A patent/CN107004974B/zh active Active

-

2020

- 2020-06-30 JP JP2020112766A patent/JP7176550B2/ja active Active

-

2022

- 2022-11-10 JP JP2022180551A patent/JP7541249B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2023001341A (ja) | 2023-01-04 |

| JP2020177916A (ja) | 2020-10-29 |

| CN107004974A (zh) | 2017-08-01 |

| JP7176550B2 (ja) | 2022-11-22 |

| US9991614B2 (en) | 2018-06-05 |

| JP2016119306A (ja) | 2016-06-30 |

| CN107004974B (zh) | 2020-09-01 |

| TWI686014B (zh) | 2020-02-21 |

| KR101929697B1 (ko) | 2018-12-14 |

| WO2016104463A1 (ja) | 2016-06-30 |

| KR20170076783A (ko) | 2017-07-04 |

| TW201635648A (zh) | 2016-10-01 |

| US20170352967A1 (en) | 2017-12-07 |

| JP7541249B2 (ja) | 2024-08-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6759578B2 (ja) | 異方導電性フィルム及び接続構造体 | |

| JP7004058B2 (ja) | 異方導電性フィルム及び接続構造体 | |

| JP6932110B2 (ja) | 異方導電性フィルム及び接続構造体 | |

| JP6690184B2 (ja) | 異方導電性フィルム及び接続構造体 | |

| CN110499119B (zh) | 各向异性导电性膜及连接构造体 | |

| TWI671954B (zh) | 異向導電性膜及連接結構體 | |

| US20170367195A1 (en) | Printed circuit board and manufacturing method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190711 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190730 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190927 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191126 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200421 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200630 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20200710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200804 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200817 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6759578 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |