JP6520085B2 - 薄膜キャパシタ - Google Patents

薄膜キャパシタ Download PDFInfo

- Publication number

- JP6520085B2 JP6520085B2 JP2014246925A JP2014246925A JP6520085B2 JP 6520085 B2 JP6520085 B2 JP 6520085B2 JP 2014246925 A JP2014246925 A JP 2014246925A JP 2014246925 A JP2014246925 A JP 2014246925A JP 6520085 B2 JP6520085 B2 JP 6520085B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- layer

- thin film

- protective layer

- film capacitor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/33—Thin- or thick-film capacitors (thin- or thick-film circuits; capacitors without a potential-jump or surface barrier specially adapted for integrated circuits, details thereof, multistep manufacturing processes therefor)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/008—Selection of materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/224—Housing; Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

- H01G4/306—Stacked capacitors made by thin film techniques

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Ceramic Capacitors (AREA)

Description

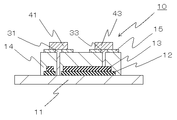

下地電極11として厚み100μmのNi箔を用意し、その片面に誘電体層12であるBT層を誘電率1000、膜厚900nmとなるようにスパッタリング法で形成した。誘電体層12上には、上部電極層13(下層、誘電体層12側)であるNi層をスパッタリング法で形成し、Ni層上に上部電極層13(上層)であるCu層をスパッタリング法で形成した。その際、容量が約8000pF(8nF)となるように、上部電極層13の面積及びパターン形状と、誘電体層12の厚みと、を設定した(図4(a)参照)。

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15を保護層14の全域被覆としたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.05nF,標準偏差は0.17nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15のヤング率を1.0GPa、2.8GPaの二水準としたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.05nF,標準偏差は0.18nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.01nF,標準偏差は0.21nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPa、膜厚を5.0μmの一水準に固定したこと、絶縁層15については、それぞれ第一の端子電極41ならびに第二の端子電極43の周辺のみとしてヤング率を3.0GPaとした(実施例22)、保護層14の全域被覆としてヤング率を3.0GPaとした(実施例23)、第一の端子電極41ならびに第二の端子電極43の周辺のみとしてヤング率を2.8GPaとした(実施例24)、こと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.06nF,標準偏差は0.14nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPa、膜厚を5.0μmの一水準に固定したこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.02nF,標準偏差は0.14nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.04nF,標準偏差は0.23nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15のヤング率を2.8GPaの一水準に固定したこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.04nF,標準偏差は0.22nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.01nF,標準偏差は0.22nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1〜9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は7.99nF,標準偏差は0.21nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

保護層14のヤング率を0.05GPa(比較例1)、2.5GPa(比較例2)、3.0GPa(比較例3)とし、保護層14の膜厚を5.0μmの一水準に固定したこと以外は、実施例1〜9と同様に薄膜キャパシタ10を作製し、実施例1〜9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.00nF,標準偏差は0.15nFとなった。また、絶縁抵抗値を測定したところ、1.0〜2.0×1011Ωの範囲内であった。

Claims (4)

- 下地電極上に誘電体層および上部電極層を順次積層した積層体と、

少なくとも前記下地電極の一部、前記誘電体層および前記上部電極層を被覆するとともに、前記下地電極に達する第一の貫通孔と、前記上部電極層に達する第二の貫通孔とを、それぞれ備えた保護層と、

前記下地電極上の前記保護層にある前記第一の貫通孔を通して前記下地電極と電気的に接続する第一の引出電極と、

前記上部電極層上の前記保護層にある前記第二の貫通孔を通して前記上部電極層と電気的に接続する第二の引出電極と、

前記第一の引出電極を介して前記下地電極を外部回路と接続する第一の端子電極と、

前記第二の引出電極を介して前記上部電極層を外部回路と接続する第二の端子電極と、

を備え、

前記保護層と前記第一の端子電極との間、および前記保護層と前記第二の端子電極との間に、それぞれ開口部を備えた絶縁層を有し、

前記第一の端子電極は前記第一の引出電極と、前記第二の端子電極は前記第二の引出電極と、それぞれの前記絶縁層に設けられた前記開口部を通じて接続されており、

前記絶縁層の成膜領域が、前記第一の端子電極および前記第二の端子電極の面積よりも広く、

前記保護層の縦弾性係数(ヤング率)が、0.1GPa以上2.0GPa以下であることを特徴とする薄膜キャパシタ。 - 前記保護層は、前記上部電極層上端からの膜厚が3.0μm以上7.0μm以下であることを特徴とする請求項1に記載の薄膜キャパシタ。

- 前記絶縁層の縦弾性係数(ヤング率)が、3.0GPa以上であることを特徴とする請求項1又は2に記載の薄膜キャパシタ。

- 前記下地電極は、Ni箔であることを特徴とする請求項1から3のいずれか一項に記載の薄膜キャパシタ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014246925A JP6520085B2 (ja) | 2014-12-05 | 2014-12-05 | 薄膜キャパシタ |

| US14/953,807 US9831039B2 (en) | 2014-12-05 | 2015-11-30 | Thin film capacitor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014246925A JP6520085B2 (ja) | 2014-12-05 | 2014-12-05 | 薄膜キャパシタ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016111182A JP2016111182A (ja) | 2016-06-20 |

| JP6520085B2 true JP6520085B2 (ja) | 2019-05-29 |

Family

ID=56094922

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014246925A Active JP6520085B2 (ja) | 2014-12-05 | 2014-12-05 | 薄膜キャパシタ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9831039B2 (ja) |

| JP (1) | JP6520085B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10057767B2 (en) * | 2014-12-19 | 2018-08-21 | Apple Inc. | Methods and apparatus to support location specific control of access to services through untrusted wireless networks |

| EP3151599A1 (en) | 2015-09-30 | 2017-04-05 | Apple Inc. | Authentication failure handling for cellular network access through wlan |

| JPWO2018003445A1 (ja) * | 2016-06-28 | 2019-03-07 | 株式会社村田製作所 | キャパシタ |

| KR102632352B1 (ko) * | 2016-09-08 | 2024-02-02 | 삼성전기주식회사 | 커패시터 부품 |

| WO2018083961A1 (ja) | 2016-11-01 | 2018-05-11 | 信越化学工業株式会社 | デバイス層を転写基板に転写する方法および高熱伝導性基板 |

| KR102762892B1 (ko) * | 2016-12-15 | 2025-02-07 | 삼성전기주식회사 | 박막 커패시터 |

| JP2018137311A (ja) * | 2017-02-21 | 2018-08-30 | Tdk株式会社 | 薄膜キャパシタ |

| KR102427926B1 (ko) * | 2017-05-29 | 2022-08-02 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그의 제조 방법 |

| CN110800098B (zh) * | 2017-07-31 | 2023-09-22 | 株式会社村田制作所 | 薄膜电容器及其制造方法 |

| KR102404320B1 (ko) | 2017-08-31 | 2022-06-07 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 그 제조방법 |

| JP7056290B2 (ja) * | 2018-03-23 | 2022-04-19 | Tdk株式会社 | 薄膜キャパシタ、及び薄膜キャパシタの製造方法 |

| DE112019007838T5 (de) * | 2019-10-23 | 2022-07-07 | Mitsubishi Electric Corporation | Halbleitervorrichtung |

| KR102836879B1 (ko) * | 2019-12-04 | 2025-07-21 | 더블유. 엘. 고어 앤드 어소시에이트스, 인코포레이티드 | 높은 열 안정성을 갖는 적어도 하나의 중합체로 캡슐화된 커패시터 |

| JP2024516585A (ja) | 2021-04-27 | 2024-04-16 | キョーセラ・エーブイエックス・コンポーネンツ・コーポレーション | 伝送線路コンデンサおよび伝送線路コンデンサを内部に埋め込んだ回路板 |

| US12080809B2 (en) | 2021-05-03 | 2024-09-03 | KYOCERA AVX Components Corporation | Metal-oxide-semiconductor capacitor and circuit board including the same embedded therein |

Family Cites Families (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4811162A (en) | 1987-04-27 | 1989-03-07 | Engelhard Corporation | Capacitor end termination composition and method of terminating |

| JPH0793236B2 (ja) | 1988-11-16 | 1995-10-09 | 松下電器産業株式会社 | フイルムコンデンサおよびその製造方法 |

| JP3121119B2 (ja) | 1992-06-16 | 2000-12-25 | ローム株式会社 | 積層セラミックコンデンサの外部電極の形成方法 |

| JPH097877A (ja) | 1995-04-18 | 1997-01-10 | Rohm Co Ltd | 多層セラミックチップ型コンデンサ及びその製造方法 |

| US5774326A (en) | 1995-08-25 | 1998-06-30 | General Electric Company | Multilayer capacitors using amorphous hydrogenated carbon |

| US6254971B1 (en) | 1996-06-07 | 2001-07-03 | Asahi Kasei Kabushiki Kaisha | Resin-having metal foil for multilayered wiring board, process for producing the same, multilayered wiring board, and electronic device |

| JP4310647B2 (ja) * | 1997-01-17 | 2009-08-12 | セイコーエプソン株式会社 | 半導体装置及びその製造方法 |

| JP3067698B2 (ja) | 1997-06-27 | 2000-07-17 | 松下電器産業株式会社 | 積層セラミック電子部品の製造方法 |

| JPH11220069A (ja) * | 1998-02-02 | 1999-08-10 | Seiko Epson Corp | 半導体装置及びその製造方法、回路基板並びに電子機器 |

| JP2002505812A (ja) * | 1998-04-20 | 2002-02-19 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 薄膜キャパシタ |

| EP1048042A1 (en) | 1998-09-02 | 2000-11-02 | Koninklijke Philips Electronics N.V. | Thin-film capacitor |

| JP4009078B2 (ja) | 2001-09-27 | 2007-11-14 | 京セラ株式会社 | 薄膜電子部品 |

| JP4166013B2 (ja) * | 2001-12-26 | 2008-10-15 | 富士通株式会社 | 薄膜キャパシタ製造方法 |

| JP3967964B2 (ja) | 2002-05-30 | 2007-08-29 | 京セラ株式会社 | 薄膜電子部品 |

| JP3910908B2 (ja) * | 2002-10-29 | 2007-04-25 | 新光電気工業株式会社 | 半導体装置用基板及びこの製造方法、並びに半導体装置 |

| JP4523299B2 (ja) | 2003-10-31 | 2010-08-11 | 学校法人早稲田大学 | 薄膜コンデンサの製造方法 |

| JP4512497B2 (ja) * | 2005-01-31 | 2010-07-28 | イビデン株式会社 | コンデンサ内蔵パッケージ基板及びその製法 |

| JP2006310744A (ja) * | 2005-03-28 | 2006-11-09 | Fujitsu Ltd | 薄膜キャパシタ及び半導体装置 |

| EP1876610B1 (en) * | 2005-04-27 | 2015-09-09 | Murata Manufacturing Co., Ltd. | Thin film capacitor and method for manufacturing same |

| JP4757587B2 (ja) | 2005-09-21 | 2011-08-24 | Tdk株式会社 | 積層コンデンサ、及び、その製造方法 |

| JP4267614B2 (ja) | 2005-09-30 | 2009-05-27 | Tdk株式会社 | 積層型セラミック電子部品の製造方法 |

| JP4674606B2 (ja) * | 2005-10-18 | 2011-04-20 | 株式会社村田製作所 | 薄膜キャパシタ |

| JP2008153497A (ja) * | 2006-12-19 | 2008-07-03 | Murata Mfg Co Ltd | 誘電体薄膜キャパシタの製造方法 |

| JP2008213199A (ja) * | 2007-03-01 | 2008-09-18 | Matsushita Electric Ind Co Ltd | 熱収縮性積層フィルム、熱収縮性積層フィルムの製造方法、容器、容器の製造方法 |

| JP4954824B2 (ja) * | 2007-08-02 | 2012-06-20 | 日本特殊陶業株式会社 | 部品内蔵配線基板、配線基板内蔵用コンデンサ |

| JP5407775B2 (ja) * | 2009-03-31 | 2014-02-05 | Tdk株式会社 | 薄膜コンデンサの製造方法及び薄膜コンデンサ |

| JP5482062B2 (ja) | 2009-09-29 | 2014-04-23 | Tdk株式会社 | 薄膜コンデンサ及び薄膜コンデンサの製造方法 |

| JP5407792B2 (ja) * | 2009-11-18 | 2014-02-05 | Tdk株式会社 | 薄膜コンデンサ及び薄膜コンデンサの製造方法 |

| JP5803731B2 (ja) * | 2012-02-22 | 2015-11-04 | 株式会社村田製作所 | 薄膜素子 |

-

2014

- 2014-12-05 JP JP2014246925A patent/JP6520085B2/ja active Active

-

2015

- 2015-11-30 US US14/953,807 patent/US9831039B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9831039B2 (en) | 2017-11-28 |

| US20160163463A1 (en) | 2016-06-09 |

| JP2016111182A (ja) | 2016-06-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6520085B2 (ja) | 薄膜キャパシタ | |

| US9773614B2 (en) | Thin film capacitor | |

| JP6357856B2 (ja) | 薄膜キャパシタ | |

| JP5482062B2 (ja) | 薄膜コンデンサ及び薄膜コンデンサの製造方法 | |

| JP6102376B2 (ja) | 薄膜コンデンサ | |

| JP6274044B2 (ja) | セラミック電子部品 | |

| JP5287644B2 (ja) | 薄膜コンデンサ | |

| JP3966208B2 (ja) | 薄膜キャパシタおよびその製造方法 | |

| US8760842B2 (en) | Flexible multilayer type thin film capacitor and embedded printed circuit board using the same | |

| JP5924461B1 (ja) | 複合電子部品 | |

| JP6115213B2 (ja) | 薄膜コンデンサ | |

| US10085344B2 (en) | Electronic component and electronic component built-in board | |

| JP5299158B2 (ja) | 誘電体薄膜素子 | |

| US20130076203A1 (en) | Ceramic body and method for producing the same | |

| US10340088B2 (en) | Thin-film capacitor | |

| JP2009010114A (ja) | 誘電体薄膜キャパシタ | |

| US10395842B2 (en) | Thin film capacitor and manufacturing method thereof | |

| US11430611B2 (en) | Thin film capacitor, circuit board incorporating the same, and thin film capacitor manufacturing method | |

| CN110246693A (zh) | 薄膜电容器的制造方法及薄膜电容器 | |

| JP6610159B2 (ja) | 薄膜キャパシタ | |

| JP6350144B2 (ja) | 薄膜キャパシタ | |

| SG188757A1 (en) | A method for forming a piezoelectric device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170802 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180727 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180814 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181011 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190415 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6520085 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |